,-

Изобретение относится к технике связи и может быть использовано в системах автоматической коммутации.

Цель изобретения - повышение надежности коммутации путем выявления и отключения неисправного блока.

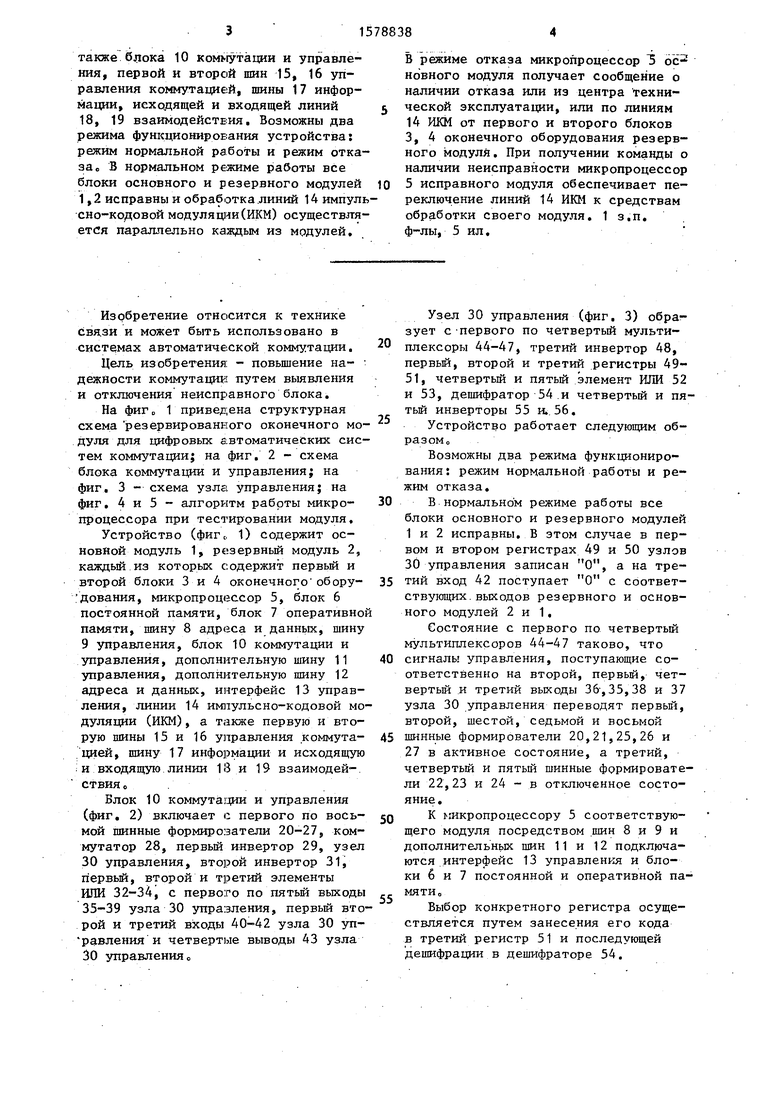

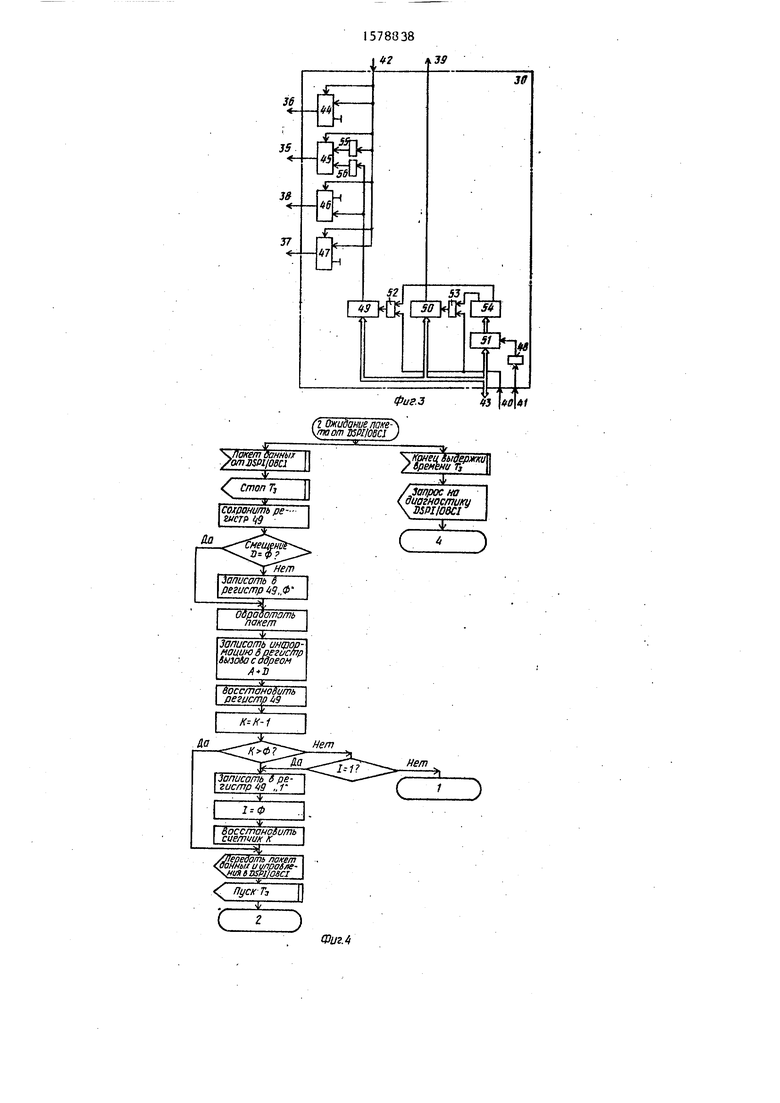

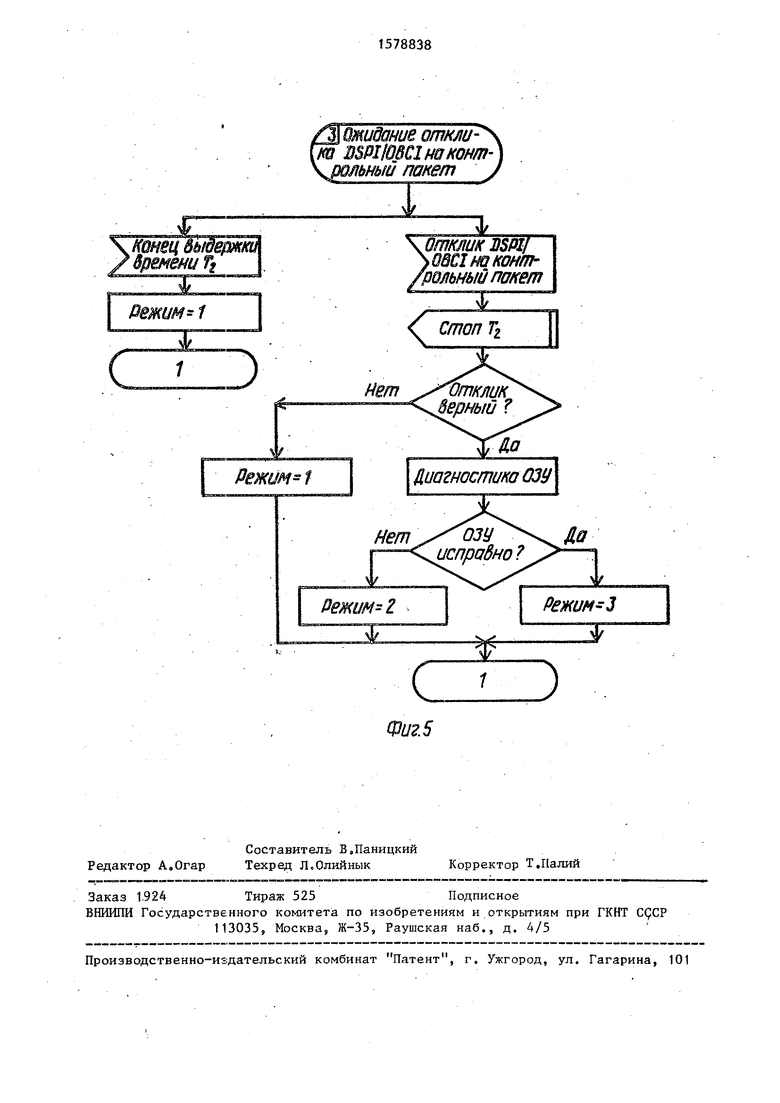

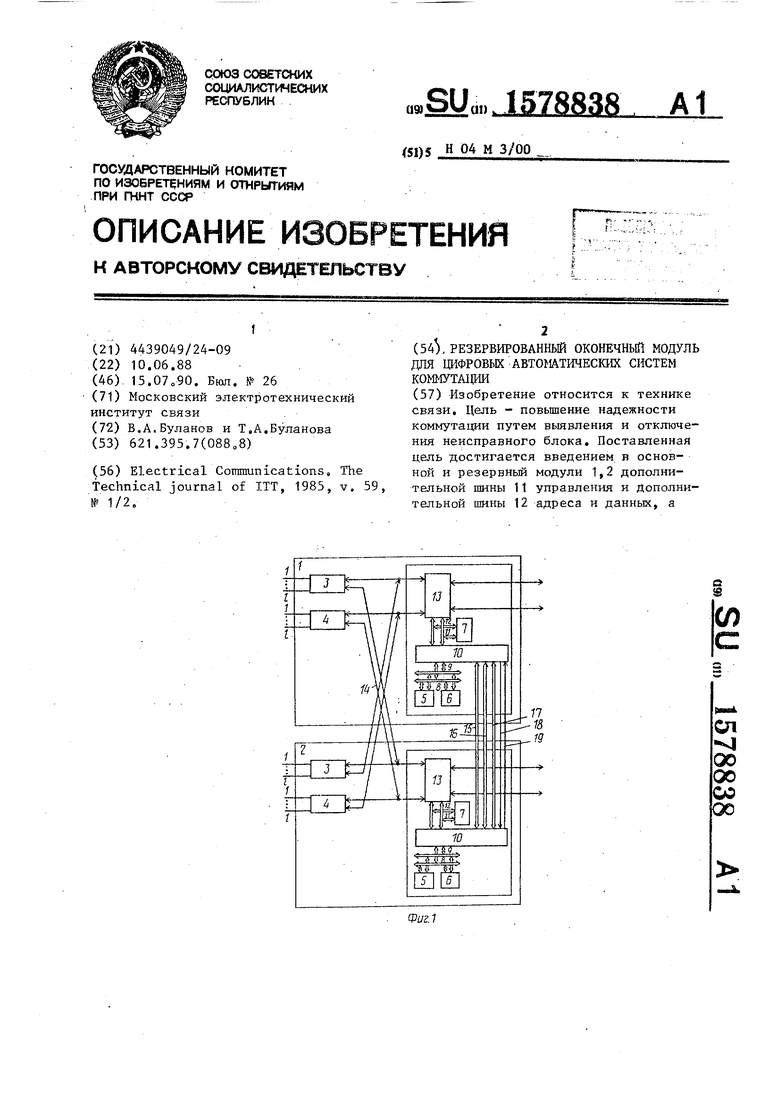

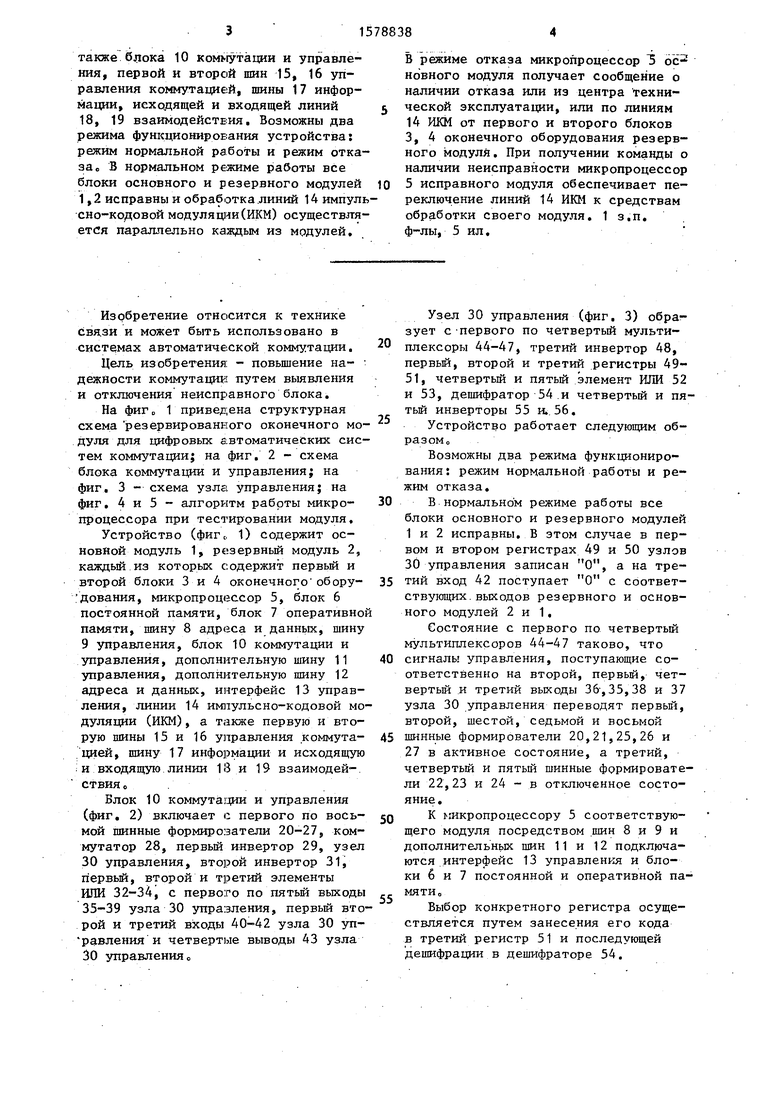

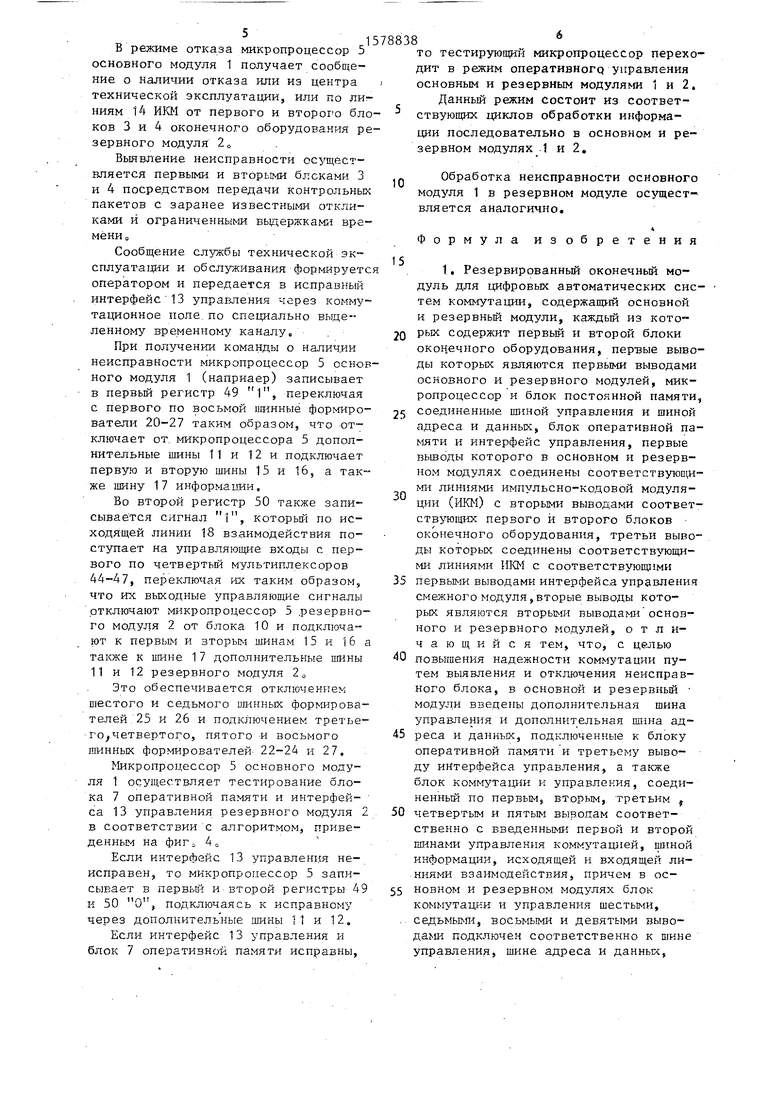

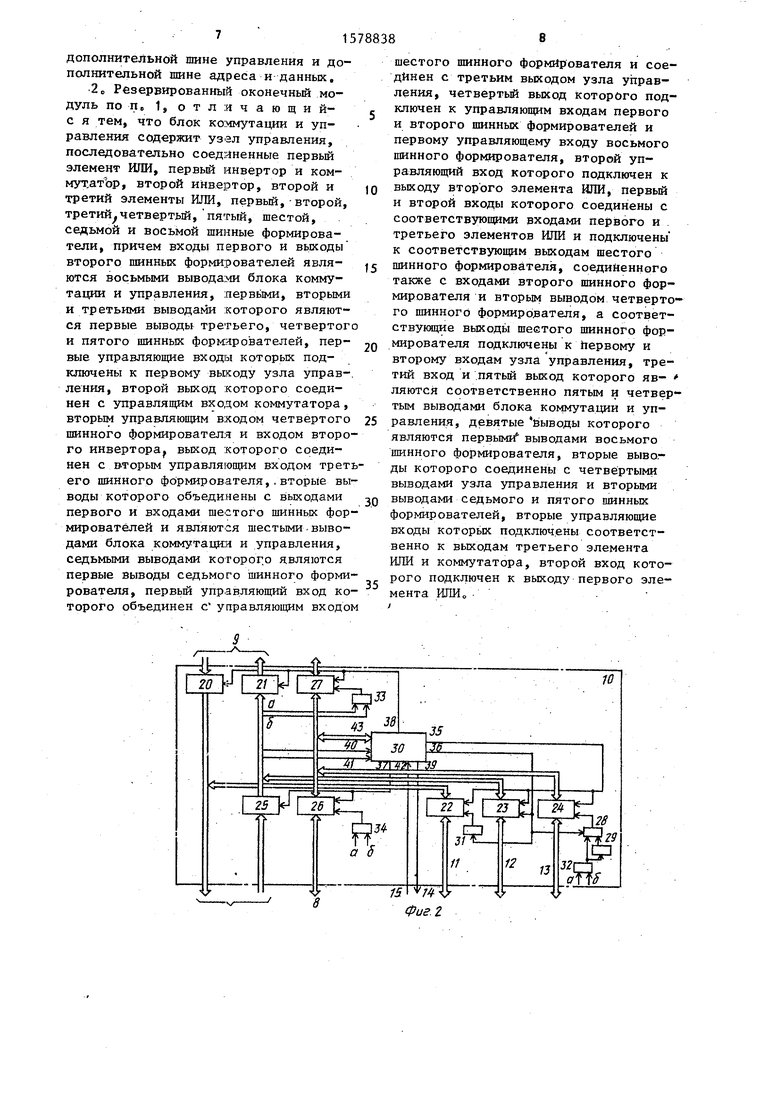

На фиг„ 1 приведена структурная схема резервированного оконечного модуля для цифровых автоматических систем коммутации; на фиг. 2 - схема блока коммутации и управления; на фиг. 3 - схема узла управления; на фиг. 4 и 5 - алгоритм работы микро- процессора при тестировании модуля.

Устройство (фиг с 1) содержит основной модуль 1, резервный модуль 2, каждый из которых содержит первый и второй блоки 3 и 4 оконечного обору- дования, микропроцессор 5, блок 6 постоянной памяти, блок 7 оперативной памяти, шину 8 адреса и данных, шину 9 управления, блок 10 коммутации и управления, дополнительную шину 11 управления, дополнительную шину 12 адреса и данных, интерфейс 13 управления, линии 14 импульсно-кодовой модуляции (ИКМ), а также первую и вторую шины 15 и 16 управления коммута- цией, шину 17 информации и исходящую и входящую линии 18 и 19 взаимодействия о

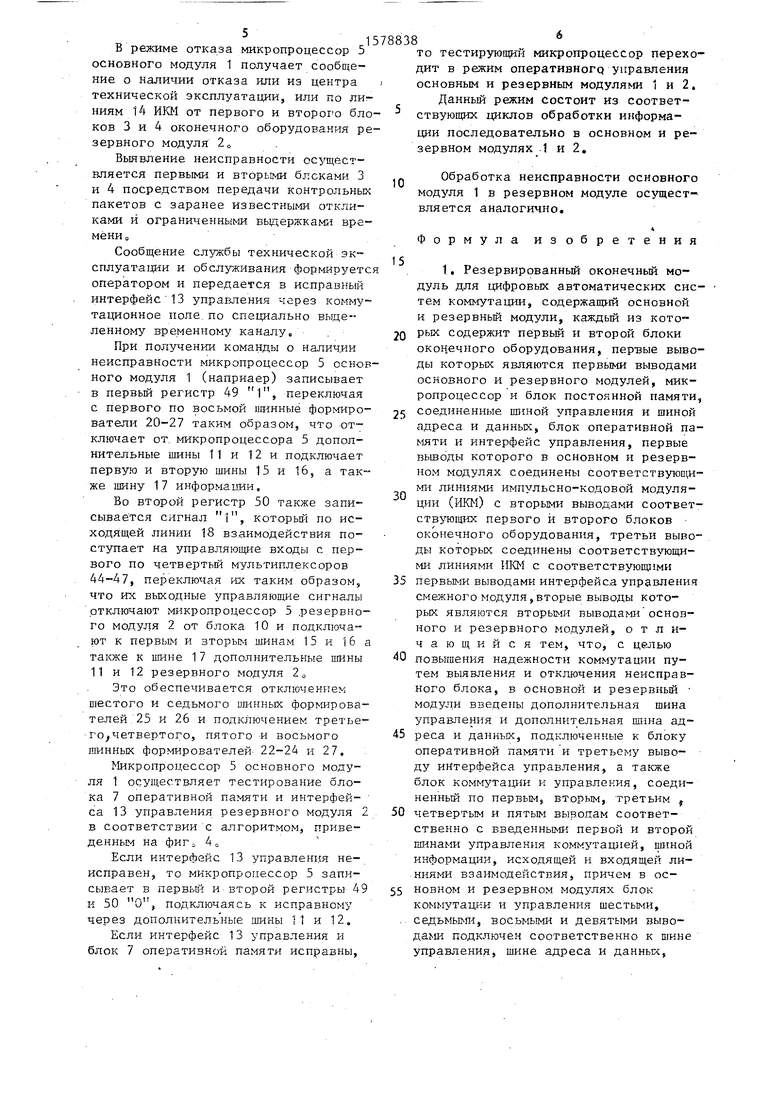

Блок 10 коммутадай и управления (фиг. 2) включает с первого по вось- мой шинные формирователи 20-27, коммутатор 28, первый инвертор 29, узел 30 управления, второй инвертор 31, первьй, второй и третий элементы ИЛИ 32-34, с первого по пятый выходы 35-39 узла 30 управления, первьй второй и третий входы 40-42 узла 30 уп- равления и четвертые выводы 43 узла 30 управления о

25

20

30

35 40 45

JQ „

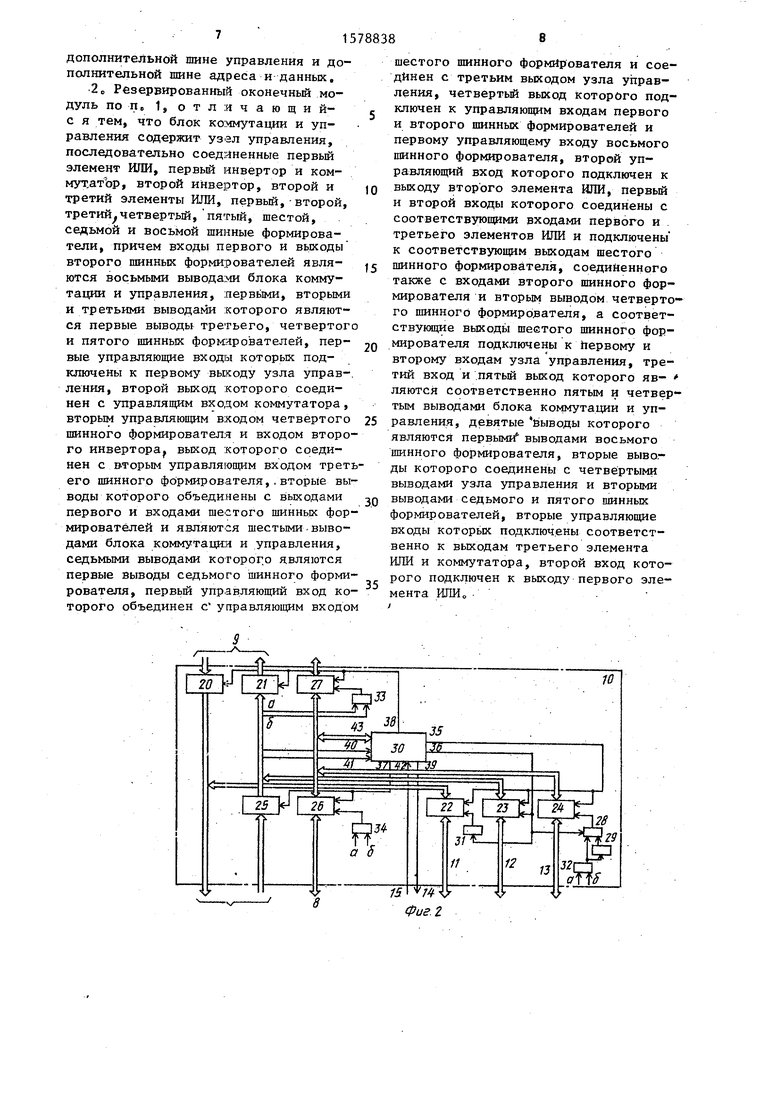

Узел 30 управления (фиг. 3) образует с первого по четвертый мультиплексоры 44-47, третий инвертор 48, первьй, второй и третий регистры 49- 51, четвертый и пятьй элемент ИЛИ 52 и 53, дешифратор 54 и четвертый и пятьй инверторы 55 и. 56.

Устройство работает следующим образом

Возможны два режима функционирования: режим нормальной работы и режим отказа.

В нормальном режиме работы все блоки основного и резервного модулей 1 и 2 исправны. В этом случае в первом и втором регистрах 49 и 50 узлов 30 управления записан О, а на третий вход 42 поступает О с соответствующих выходов резервного и основного модулей 2 и 1.

Состояние с первого по четвертый мультиплексоров 44-47 таково, что сигналы управления, поступающие соответственно на второй, первьй, четвертый и третий выходы 36,35,38 и 37 узла 30 управления переводят первьй, второй, шестой, седьмой и восьмой шинные формирователи 20,21,25,26 и 27 в активное состояние, а третий, четвертый и пятьй шинные формирователи 22,23 и 24 - в отключенное состояние.

К микропроцессору 5 соответствующего модуля посредством шин 8 и 9 и дополнительных шин 11 и 12 подключаются интерфейс 13 управления и блоки 6 и 7 постоянной и оперативной памяти

Выбор конкретного регистра осуществляется путем занесения его кода в третий регистр 51 и последующей дешифрации в дешифраторе 54.

В режиме отказа микропроцессор 5 основного модуля 1 получает сообщение о наличии отказа или из центра технической эксплуатации, или по линиям 14 ИКМ от первого и второго блоков 3 и 4 оконечного оборудования резервного модуля 2 о

Выявление неисправности осуществляется первыми и вторхми блоками 3 и 4 посредством передачи контрольных пакетов с заранее известными откликами и ограниченными выдержками времени о

Сообщение службы технической эксплуатации и обслуживания формируетс оператором и передается в исправный интерфейс 13 управления через коммутационное поле по специально выделенному временному каналу.

При Получении команды о наличии неисправности микропроцессор 5 основного модуля 1 (наприаер) записывает в первый регистр 49 1, переключая с первого по восьмой шинные формирователи 20-27 таким образом, что отключает от микропроцессора 5 дополнительные шины 11 и 12 и подключает первую и вторую шины 15 и 16, а также шину 17 информации.

Во второй регистр 50 также записывается сигнал |, который по исходящей линии 18 взаимодействия поступает на управляющие входы с первого по четвертый мультиплексоров 44-47, переключая их таким образом, что их выходные управляющие сигналы отключают микропроцессор 5 резервного модуля 2 от блока 10 и подключают к первым и вторым шинам 15 и 16 а также к шине 17 дополнительные шины 11 и 12 резервного модуля 20

Это обеспечивается отключением шестого и седьмого шинных формирователей 25 и 26 и подключением третье- го четвертого, пятого и восьмого шинных формирователей 22-24 и 27.

Микропроцессор 5 основного модуля 1 осуществляет тестирование блока 7 оперативной памяти и интерфейса 13 управления резервного модуля 2 в соответствии с алгоритмом, приведенным на фига 4 о

Если интерфейс 13 управления неисправен, то микропроцессор 5 записывает в первьй и второй регистры 49 и 50 О, подключаясь к исправному через дополнительные шины 11 и 12.

Если интерфейс 13 управления и блок 7 оперативной памяти исправны,

/ 578838

то тестирующий микропроцессор переходит в режим оперативного управления основным и резервным модулями 1 и 2. Данный режим состоит из соответствующих циклов обработки информации последовательно в основном и резервном модулях 1 и 2.

Обработка неисправности основного модуля 1 в резервном модуле осуществляется аналогично.

V

Формула изобретения

5

0

1. Резервированный оконечный модуль для цифровых автоматических систем коммутации, содержащий основной и резервный модули, каждый из котоо рых содержит первьй и второй блоки оконечного оборудования, перовые выводы которых являются первыми выводами основного и резервного модулей, микропроцессор и блок постоянной памяти,

5 соединенные шиной управления и шиной адреса и данных, блок оперативной памяти и интерфейс управления, первые выводы которого в основном и резервном модулях соединены соответствующими линиями импульсно-кодовой модуляции (ИКМ) с вторыми выводами соответствующих первого и второго блоков оконечного оборудования, третьи выводы которых соединены соответствующими линиями ИКМ с соответствующими

5 первыми выводами интерфейса управления смежного модуля,вторые выводы которых являются вторыми выводами основного и резервного модулей, отличающийся тем, что, с целью

0 повышения надежности коммутации путем выявления и отключения неисправного блока, в основной и резервный модули введены дополнительная шина управления и дополнительная шина ад5 реса и данных, подключенные к блоку оперативной памяти и третьему выводу интерфейса управления, а также блок коммутации и управления, соединенный по первым, вторым, третьим f

0 четвертым и пятым выводам соответственно с введенными первой и второй шинами управления коммутацией, шиной информации, исходящей и входящей линиями взаимодействия, причем в ос5 новном и резервном модулях блок коммутации и управления шестыми, седьмыми, восьмыми и девятыми выводами подключен соответственно к шине управления, шине адреса и данных,

дополнительной шине управления и дополнительной шине адреса и данных.

2„ Резервированный оконечньй модуль по п„ 1, отлячающий- с я тем, что блок коммутации и управления содержит узел управления, последовательно соединенные первый элемент ИЛИ, первый инвертор и ком- мут.ат ор, второй инвертор, второй и третий элементы ИЛИ, первый, второй, третий четвертый, пятый, шестой, седьмой и восьмой шинные формирователи, причем входы первого и выходы второго шинных формирователей являются восьмыми выводами блока коммутации и управления, первыми, вторыми и третьими выводами которого являются первые выводы третьего, четвертого и пятого шинных формирователей, первые управляющие входы которых подключены к первому выходу узла управления, второй выход которого соединен с управлящим входом коммутатора, вторым управляющим вкодом четвертого шинного формирователя и входом второго инвертора выход которого соединен с вторым управляющим входом третьего шинного формирователя,.вторые выводы которого объединены с выходами первого и входами шестого шинных формирователей и являются шестыми выводами блока коммутация и управления, седьмыми выводами которого являются первые выводы седьмого шинного формирователя, первый управляющий вход которого объединен с управляющим входом

0

5

0

5

шестого шинного формирователя и соединен с третьим выходом узла управления, четвертьй выход которого подключен к управляющим входам первого и второго шинных формирователей и первому управляющему входу восьмого шинного формирователя, второй управляющий вход которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого соединены с соответствующими входами первого и третьего элементов ИЛИ и подключены к соответствующим выходам шестого шинного формирователя, соединенного также с входами второго шинного формирователя и вторым выводом четвертого шинного формирозателя, а соответствующие выходы шестого шинного формирователя подключены к первому и второму входам узла управления, третий вход и пятый выход которого яв- ляются соответственно пятым и четвертым выводами блока коммутации и управления, девятые выводы которого являются первыми выводами восьмого шинного формирователя, вторые выводы которого соединены с четвертыми выводами узла управления и вторыми выводами седьмого и пятого шинных формирователей, вторые управляющие входы которых подключены соответственно к выходам третьего элемента ИЛИ и коммутатора, второй вход которого подключен к выходу первого элемента ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ И СВЯЗИ | 2008 |

|

RU2400805C2 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| КОМАНДНО-СТРЕЛЬБОВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА | 2001 |

|

RU2191430C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2533688C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА КОРАБЕЛЬНОГО КОМПЛЕКСА РАДИОЭЛЕКТРОННОГО ПРОТИВОДЕЙСТВИЯ | 2001 |

|

RU2209463C2 |

| Устройство для управления переключением резерва | 1980 |

|

SU1010734A1 |

| АВТОМАТИЧЕСКАЯ ТЕЛЕФОННАЯ СТАНЦИЯ С ФУНКЦИЯМИ ЦИФРОВОЙ СЕТИ ИНТЕГРАЛЬНОГО ОБСЛУЖИВАНИЯ | 2018 |

|

RU2676262C1 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| УНИФИЦИРОВАННЫЙ ПУЛЬТОВОЙ ПРИБОР | 2004 |

|

RU2276401C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ГАРАНТИРОВАННОГО ЭЛЕКТРОСНАБЖЕНИЯ МОБИЛЬНОГО КОМПЛЕКСА | 2006 |

|

RU2318282C1 |

Изобретение относится к технике связи. Цель - повышение надежности коммутации путем выявления и отключения неисправного блока. Поставленная цель достигается введением в основной и резервный модули 1, 2 дополнительной шины 11 управления и дополнительной шины 12 адреса и данных, а также блока 10 коммутации и управления, первой и второй шин 15, 16 управления коммутацией, шины 17 информации, исходящей и входящей линий 18, 19 взаимодействия. Возможны два режима функционирования у-ва: режим нормальной работы и режим отказа. В нормальном режиме работы все блоки основного и резервного модулей 1, 2 исправны и обработка линий импульсно-кодовой модуляции 14 (ИКМ) осуществляется параллельно каждым из модулей. В режиме отказа микропроцессор 5 основного модуля получает сообщение о наличии отказа или из центра технической эксплуатации или по линиям ИКМ 14 от первого и второго блоков 3, 4 оконечного оборудования резервного модуля. При получении команды о наличии неисправности микропроцессор 5 исправного модуля обеспечивает переключение линий ИКМ 14 к средствам обработки своего модуля. 1 з.п. ф-лы, 5 ил.

8

Фиг 2

(г Ожидание паке тют Ш10ВС1

На

Фаг. 4

С

}

шидание отнли iff тРИОЩнаконт-} чьный пакет J

1

ж

3

отклик язя/ OBC1наконт- /рольный пакет

±

cmonTi

№т

Ла

Диагностика ОЗУ

Нет

исправно

г

W

С

)

Фиг. 5

| Electrical Communications The Technical journal of TTT, 1985, v | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

Авторы

Даты

1990-07-15—Публикация

1988-06-10—Подача