Изобретение относится к средствам обработки цифровых данных, области защиты от несанкционированного доступа к информации и может быть использовано для обработки и преобразования информации.

Известно устройство управления и связи (Флорес А., Организация вычислительных машин. М., «Мир», 1972, раздел 9.4), содержащее блок управления, постоянное запоминающее устройство команд, арифметический блок, блок регистров общего назначения, оперативный запоминающий блок, счетчик сдвигов, регистр промежуточного результата, дешифратор нуля счетчика сдвигов, регистр результата.

Недостатками известного устройства являются низкое быстродействие в связи с морально устаревшей элементной базой и ограниченные функциональные возможности, а именно невозможность преобразования цифровой информации из-за ограниченного набора алгоритмов обработки и операций над цифровыми данными, отсутствие в устройстве технической возможности приема и выдачи цифровой информации по двухпроводным последовательным линиям связи.

Наиболее близким по совокупности существенных признаков к предлагаемому изобретению является устройство управления и связи (см. А.С. СССР №682890 от 20.12.76, МКИ: G06F 13/00, «Процессор связи» авторов В.В.Моргунова, С.Е.Иванова и B.C.Исаевой, опубл. 30.08.79. Бюл. №32), содержащее блок управления (процессорное устройство), постоянный запоминающий блок, арифметический блок, оперативный запоминающий блок, блок регистров общего назначения, счетчик сдвигов, дешифратор нуля счетчика сдвигов, регистр промежуточного результата, регистр результата, коммутатор, блок сумматоров по модулю два. Первые вход и выход блока управления соединены соответственно с выходом и входом постоянного запоминающего устройства команд, а вторые вход и выход подключены соответственно к первым выходу и входу арифметического блока. Блок регистров общего назначения соединен первым входом с третьим выходом блока управления, четвертый выход которого подключен к первому входу оперативного запоминающего блока. Выход регистра результата соединен со вторыми входами блока регистров общего назначения, выход которого подключен ко второму входу арифметического блока и первому входу счетчика сдвигов. Выход оперативного запоминающего блока соединен с третьим входом арифметического блока и первым входом регистра промежуточного результата. Вход и выход дешифратора нуля счетчика сдвигов соединены соответственно с выходом счетчика сдвигов и третьим входом блока управления, пятый, шестой и седьмой выходы которого подключены соответственно ко вторым входам счетчика сдвигов и регистра промежуточного результата и первому входу регистра результата, соединенного вторым входом со вторым выходом арифметического блока. Счетный вход регистра результата подключен к первому выходу регистра промежуточного результата, второй выход которого соединен с адресным входом оперативного запоминающего блока. Первый вход и выход блока сумматоров по модулю два подключены соответственно к выходу блока регистров общего назначения и первому входу коммутатора, выход которого соединен с третьим входом регистра результата. Вторые входы блока сумматоров по модулю два и коммутатора подключены к первому выходу старших разрядов регистра промежуточного результата, второй выход старших разрядов которого соединен с третьим входом коммутатора, а выход младших разрядов - с входом младших разрядов регистра результата.

Недостатками известного устройства являются ограниченные функциональные возможности, низкое быстродействие, а также невозможность преобразования цифровой информации из-за ограниченного набора алгоритмов обработки и операций над цифровыми данными, отсутствие в устройстве технической возможности ее приема и выдачи по линиям связи с внешними устройствами.

Задачей, решаемой предлагаемым изобретением, является создание быстродействующего устройства управления и связи, которое может использоваться для зашиты информации от несанкционированного доступа посторонних лиц, обладающего возможностью приема, преобразования и выдачи преобразованной цифровой информации.

Технический результат заключается в обеспечении возможности приема, преобразования и выдачи преобразованной цифровой информации, высокого быстродействия и расширении функциональных возможностей.

Данный технический результат достигается тем, что в устройстве управления и связи, содержащем первое процессорное устройство и устройство коммутации, новым является то, что дополнительно введены источник питания, первый и второй блоки долговременной энергонезависимой памяти, второе, третье и четвертое процессорные устройства, первый, второй и третий приемо-передатчики, первое, второе, третье и четвертое устройства связи, блок самоконтроля, первая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов первого устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов первого процессорного устройства, вторая группа входов-выходов которого соединена с группой входов-выходов первого блока долговременной энергонезависимой памяти, вторая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов второго устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов второго процессорного устройства, вторая группа входов-выходов которого соединена с группой входов-выходов второго блока долговременной энергонезависимой памяти, третья группа входов-выходов устройства коммутации соединена с первой группой входов-выходов третьего устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов третьего процессорного устройства, вторая группа входов-выходов которого соединена с первой группой входов-выходов первого приемо-передатчика, вторая группа входов-выходов которого является первой группой входов-выходов устройства управления и связи, четвертая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов четвертого устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов четвертого процессорного устройства, вторая группа входов-выходов которого соединена с первой группой входов-выходов второго приемопередатчика, вторая группа входов-выходов является второй группой входов-выходов устройства управления и связи, пятая, шестая, седьмая, восьмая и девятая группы входов-выходов устройства коммутации являются третьей, четвертой, пятой, шестой и седьмой группами входов-выходов устройства контроля и связи соответственно, первая группа входов-выходов третьего приемо-передатчика является восьмой группой входов-выходов устройства управления и связи, а вторая группа входов-выходов соединена с третьей группой входов-выходов первого процессорного устройства, четвертая группа входов-выходов которого соединена с первой группой входов-выходов блока самоконтроля, вторая группа входов-выходов которого является девятой группой входов-выходов устройства управления и связи, при этом каждые устройства, блоки и приемо-передатчики соответствующими выводами соединены с соответствующими выводами источника питания.

Введение первого блока связи, содержащего первый приемопередатчик, третье процессорное устройство и третье устройство связи, и второго блока связи, содержащего второй приемо-передатчик, четвертое процессорное устройство и четвертое устройство связи, позволяет обеспечить прием команд управления от внешних устройств и систем.

Блок-преобразователь, содержащий второе процессорное устройство, второе устройство связи и второй блок долговременной энергонезависимой памяти, обеспечивает выполнение преобразований поступающей в устройство управления и связи информации.

Центральное процессорное устройство, содержащее первое процессорное устройство, первое устройство связи, первый блок долговременной энергонезависимой памяти, третий приемо-передатчик, устройство коммутации и блок самоконтроля, обеспечивает прием и обработку поступающей информации, функциональное взаимодействие всех блоков устройства управления и связи, взаимодействие устройства управления и связи с внешними устройствами, системами и блоками.

Взаимодействие всех вышеуказанных блоков и устройств позволяет обеспечивать необходимые преобразования принятой информации и выдачу преобразованной информации во внешние устройства и блоки. Кроме того, использование новой элементной базы позволяет обеспечить высокое быстродействие устройства управления и связи.

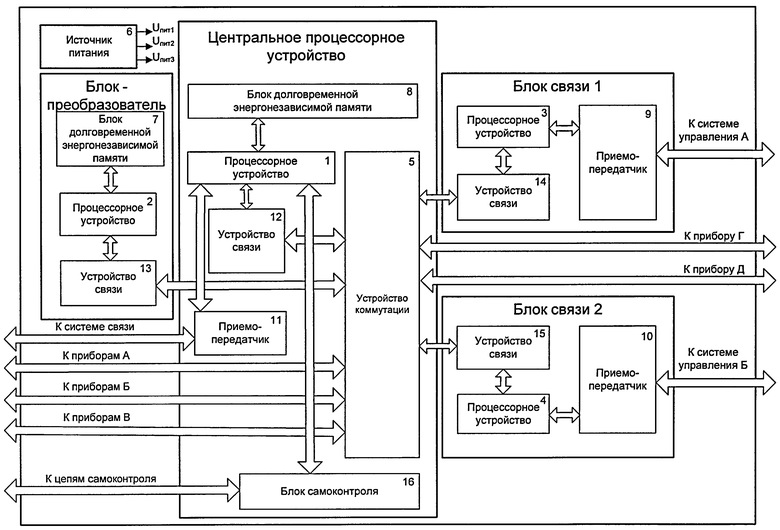

На чертеже представлена функциональная схема устройства управления и связи.

Устройство управления и связи содержит (первое 1, второе 2, третье 3 и четвертое 4 процессорные устройства, устройство 5 коммутации, источник 6 питания, первый 7 и второй 8 блоки долговременной энергонезависимой памяти, первый 9, второй 10 и третий 11 приемопередатчики, первое 12, второе 13, третье 14 и четвертое 15 устройства связи, блок 16 самоконтроля.

Первая группа входов-выходов устройства 5 коммутации соединена с первой группой входов-выходов устройства 12 связи. Вторая группа входов-выходов устройства 12 связи соединена с первой группой входов-выходов процессорного устройства 1. Вторая группа входов-выходов процессорного устройства 1 соединена с группой входов-выходов блока 8 долговременной энергонезависимой памяти. Вторая группа входов-выходов устройства 5 коммутации соединена с первой группой входов-выходов устройства 13 связи. Вторая группа входов-выходов устройства 13 связи соединена с первой группой входов-выходов процессорного устройства 2. Вторая группа входов-выходов процессорного устройства 2 соединена с группой входов-выходов блока 7 долговременной энергонезависимой памяти. Третья группа входов-выходов устройства 5 коммутации соединена с первой группой входов-выходов устройства 14 связи. Вторая группа входов-выходов устройства 14 связи соединена с первой группой входов-выходов процессорного устройства 3. Вторая группа входов-выходов процессорного устройства 3 соединена с первой группой входов-выходов приемо-передатчика 9. Вторая группа входов- выходов приемо-передатчика 9 является первой группой входов-выходов устройства управления и связи. Четвертая группа входов-выходов устройства 5 коммутации соединена с первой группой входов-выходов устройства 15 связи. Вторая группа входов-выходов устройства 15 связи соединена с первой группой входов-выходов процессорного устройства 4. Вторая группа входов-выходов процессорного устройства 4 соединена с первой группой входов-выходов приемопередатчика 10. Вторая группа входов-выходов приемо-передатчика 10 является второй группой входов-выходов устройства управления и связи. Пятая, шестая, седьмая, восьмая и девятая группы входов-выходов устройства 5 коммутации являются третьей, четвертой, пятой, шестой и седьмой группами входов-выходов устройства управления и связи, соответственно. Первая группа входов-выходов приемо-передатчика 11 является восьмой группой входов-выходов устройства управления и связи. Вторая группа входов-выходов приемо-передатчика 11 соединена с третьей группой входов-выходов процессорного устройства 1. Четвертая группа входов-выходов процессорного устройства 1 соединена с первой группой входов-выходов блока 16 самоконтроля. Вторая группа входов-выходов блока 16 самоконтроля является девятой группой входов-выходов устройства управления и связи.

Источник питания подключен к вышеуказанным устройствам, блокам и приемо-передатчикам устройства управления и связи (на чертеже не показано).

Процессорное устройство 1 обеспечивает взаимное функционирование всех устройств и блоков центрального процессорного устройства. Схемотехнически процессорное устройство 1 построено на микропроцессорной элементной базе, имеющей гибкую систему команд и позволяющей реализовать широкие функциональные возможности. Процессорное устройство 1 реализовано на микропроцессоре 1880ВЕ31У. В качестве постоянного запоминающего устройства (ПЗУ) для хранения управляющей программы микропроцессора выбраны микросхемы памяти 1623РТ2А. В качестве оперативного запоминающего устройства (ОЗУ) применяется микросхема 537РУ16А. Адресная шина и шина данных построены на регистре и двух буферах серии 1554ТБМ. Для выработки разрешающих сигналов управления для микросхем центрального процессорного устройства путем комбинирования старших адресов в процессорном устройстве 1 применены три дешифратора и четыре микросхемы 4И-НЕ серии 1554ТБМ. Схема для выработки сбросного импульса для приведения в исходное состояние микропроцессора и защиты от помех при включении питания устройства управления и связи реализована на двух триггерах Шмитта - инверторах и транзисторе из сборки 1НТ251А. Первая группа входов-выходов процессорного устройства 1 содержит обычную и буферизированную шины данных, сигналы управления и вызова. Вторая группа входов-выходов процессорного устройства 1 содержит буферизированную шину данных, сигналы управления и сигналы чтения-записи. Третья группа входов-выходов процессорного устройства 1 содержит обычную и буферизированную шины данных, сигналы управления и сигналы чтения-записи. Четвертая группа входов-выходов процессорного устройства 1 содержит сигналы управления.

Процессорное устройство 2 предназначено для преобразования цифровой информации, полученной от центрального процессорного устройства, а также для управления блоком 7 долговременной энергонезависимой памяти. Схемотехнически процессорное устройство 2 построено на микропроцессорной элементной базе, имеющей гибкую систему команд и позволяющей реализовать широкие функциональные возможности. Процессорное устройство 2 реализовано на микропроцессоре 1880ВЕ31У. В качестве ПЗУ для хранения управляющей программы микропроцессора выбрана микросхема памяти 1623РТ2А. В качестве ОЗУ применяется микросхема 537РУ16А. Адресная шина и шина данных построены на регистрах серии 1554ТБМ. Для выработки разрешающих сигналов управления для микросхем блока преобразователя путем комбинирования старших адресов в процессорном устройстве 2 применены дешифратор и микросхема 4И-НЕ серии 1554ТБМ. Схема для выработки сбросного импульса для приведения в исходное состояние микропроцессора и защиты от помех при включении питания блока преобразователя реализована на двух триггерах Шмитта - инверторах серии 1554ТБМ и транзисторе 2Т3130Б9. Первая группа входов-выходов процессорного устройства 2 содержит последовательную шину данных. Вторая группа входов-выходов процессорного устройства 2 содержит шину данных, сигналы управления и сигналы чтения-записи.

Процессорное устройство 3 обеспечивает взаимное функционирование всех устройств блока связи 1. Схемотехнически процессорное устройство 3 построено на микропроцессорной элементной базе, имеющей гибкую систему команд и позволяющей реализовать широкие функциональные возможности. Процессорное устройство 3 реализовано на микропроцессоре 1880ВЕ31У. В качестве ПЗУ для хранения управляющей программы микропроцессора выбрана микросхема памяти 1623РТ2А. Адресная шина и шина данных построены на регистре и буфере серии 1554ТБМ. Инверторы управляющих сигналов чтения и записи процессора выполнены на элементах серии 1554ТБМ. Схема для выработки сбросного импульса, для приведения в исходное состояние микропроцессора и защиты от помех при включении питания блока связи реализована на двух триггерах Шмитта - инверторах и транзисторе из сборки 1НТ251А. Первая группа входов-выходов процессорного устройства 3 содержит последовательные линии передачи и приема. Вторая группа входов-выходов процессорного устройства 3 содержит буферизированную шину данных, сигналы управления, сигналы чтения-записи и сигнала сброса.

Процессорное устройство 4 обеспечивает взаимное функционирование всех устройств блока связи 2. Схемотехнически процессорное устройство 4 построено на микропроцессорной элементной базе, имеющей гибкую систему команд и позволяющей реализовать широкие функциональные возможности. Процессорное устройство 4 реализовано на микропроцессоре 1880ВЕ31У. В качестве ПЗУ для хранения управляющей программы микропроцессора выбрана микросхема памяти 1623РТ2А.

Адресная шина и шина данных построены на регистре и буфере серии 1554ТБМ. Инверторы управляющих сигналов чтения и записи процессора выполнены на элементах серии 1554ТБМ. Схема для выработки сбросного импульса, для приведения в исходное состояние микропроцессора и защиты от помех при включении питания блока связи реализована на двух триггерах Шмитта - инверторах и транзисторе из сборки 1НТ251А. Первая группа входов-выходов процессорного устройства 4 содержит последовательные линии передачи и приема. Вторая группа входов-выходов процессорного устройства 4 содержит буферизированную шину данных, сигналы управления, сигналы чтения-записи и сигнала сброса.

Устройство 5 коммутации предназначено для обеспечения информационного обмена процессорного устройства 1 через устройство 12 связи по последовательным двухпроводным линиям связи со всеми блоками устройства управления и связи: блоком связи 1, блоком связи 2, блоком-преобразователем, а также между устройством управления и связи и внешними приборами. Схема подключения линий приемо-передатчика из состава устройства 12 связи к каждому конкретному блоку устройства управления и связи, а также к внешним приборам реализована на трех регистрах 1554ИР23 ТБМ, пяти 4-канальных коммутаторах тока 1109КТ4Б, двадцати реле РЭК81. Вентили и инверторы управляющих сигналов выполнены на логических элементах серии 1554ТБМ. Источники тока для пятнадцати линий приемо-передатчика реализованы на транзисторах 2Т830Г, стабилитронах 2С133А и резисторах. Первая группа входов-выходов устройства 5 коммутации содержит сигналы дистанционного включения питания устройства управления и связи, сигналы дистанционного включения питания внешних приборов, сигналы чтения-записи. Вторая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Третья группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Четвертая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Пятая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Шестая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Седьмая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Восьмая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи. Девятая группа входов-выходов устройства 5 коммутации содержит сигналы чтения-записи.

Источник 6 питания предназначен для преобразования входного напряжения в напряжения, необходимые для питания устройства управления и связи. Для обеспечения электропитанием всех устройств и цепей устройства управления и связи выбраны модули питания промышленного изготовления серии СПН.

Блок 7 долговременной энергонезависимой памяти обеспечивает запись и хранение цифровой информации, полученной в результате преобразований в процессорном устройстве 2. Блок 7 долговременной энергонезависимой памяти реализован на двух микросхемах 558РР4. Адресная шина и шина данных построены на четырех регистрах серии 1554ТБМ. Управляемый ключ, обеспечивающий запись данных в микросхемы памяти серии 558, реализован на микросхеме-стабилизаторе Н142ЕН19 и транзисторе 2Т665А9. Управление ключом осуществляется через микросхему 2И-НЕ с открытым коллектором серии 564. Группа входов-выходов блока 7 долговременной энергонезависимой памяти содержит шину данных, сигналы управления и сигналы чтения-записи.

Блок 8 долговременной энергонезависимой памяти обеспечивает запись и хранение цифровой информации, необходимой при работе устройства управления и связи. Блок 8 долговременной энергонезависимой памяти реализован на микросхеме 558РР4. Адресная шина и шина данных построены на четырех регистрах серии 1554ТБМ. Управляемый ключ, обеспечивающий запись данных в микросхему памяти серии 558, реализован на микросхеме-стабилизаторе Н142ЕН19 и транзисторе из сборки 1НТ251А. Управление ключом осуществляется через микросхему 2И-НЕ с открытым коллектором серии 564. Группа входов-выходов блока 8 долговременной энергонезависимой памяти содержит буферизированную шину данных, сигналы управления и сигналы чтения-записи.

Приемо-передатчик 9 обеспечивает взаимодействие процессорного устройства 3 с внешней системой управления А. Обмен информацией производится в соответствии с требованиями ГОСТ Р 52070-2003 «Интерфейс магистральный последовательный системы электронных модулей». Преобразование параллельной шестнадцатиразрядной шины данных в последовательный высокоскоростной интерфейс осуществляет микросхема кодер-декодера 588ВГ9Т. Для управления режимами работы кодера-декодера служат микросхемы серии 1554ТБМ: две микросхемы буфера, пять регистров ввода-вывода, пять триггеров, а также двадцать два логических элемента И, ИЛИ, ИЛИ-НЕ. В качестве ПЗУ для хранения кодов команд, поступающих от внешней системы управления А, выбрана микросхема памяти 1623РТ2А. Сопряжение интерфейса кодер-декодера с магистральным каналом осуществляется двумя микросборками приемопередатчиков ПП40 через два согласующих трансформатора ТИЛ-3В и шесть согласующих резисторов. Первая группа входов-выходов приемопередатчика 9 содержит буферизированную параллельную шину данных, сигналы управления, сигналы чтения-записи и сигнал сброса. Вторая группа входов-выходов приемо-передатчика 9 обеспечивает взаимодействие с внешней системой управления А по основному и резервному магистральным каналам.

Приемо-передатчик 10 обеспечивает взаимодействие процессорного устройства 4 с внешней системой управления Б. Обмен информацией производится в соответствии с требованиями ГОСТ Р 52070-2003 «Интерфейс магистральный последовательный системы электронных модулей». Преобразование параллельной шестнадцатиразрядной шины данных в последовательный высокоскоростной интерфейс осуществляет микросхема кодер-декодера 588ВГ9Т. Для управления режимами работы кодера-декодера служат микросхемы серии 1554ТБМ: две микросхемы буфера, пять регистров ввода-вывода, пять триггеров, а также двадцать два логических элемента И, ИЛИ, ИЛИ-НЕ. В качестве ПЗУ для хранения кодов команд, поступающих от внешней системы управления Б, выбрана микросхема памяти 1623РТ2А. Сопряжение интерфейса кодер-декодера с магистральным каналом осуществляется двумя микросборками приемопередатчиков ПП40 через два согласующих трансформатора ТИЛ-3В и шесть согласующих резисторов. Первая группа входов-выходов приемопередатчика 10 содержит буферизированную параллельную шину данных, сигналы управления, сигналы чтения-записи и сигнал сброса. Вторая группа входов-выходов приемо-передатчика 10 обеспечивает взаимодействие с внешней системой управления Б по основному и резервному магистральным каналам.

Приемо-передатчик 11 обеспечивает обмен информацией между устройством управления и связи и внешней системой связи. Преобразование параллельной восьмиразрядной шины данных в последовательный интерфейс осуществляют две микросхемы приемо-передатчика 1002ХЛ1. Для выполнения операций чтения-записи данных и управления приемопередатчиками 1002ХЛ1 применены четыре регистра серии 1554ТБМ. Схема выработки тактовой частоты для приемо-передатчиков 1002ХЛ1 реализована на кварцевом резонаторе РК 386ММ-6ДС, двух элементах НЕ серии 533, трех 4-разрядных двоичных счетчиках 1554ИЕ10 ТБМ и трех элементах 2И-НЕ серии 1554. Дистанционное включение питания устройства управления и связи перед началом его обмена информацией с внешней системой связи обеспечивают два реле РЭК81 и регистр 1554ИР22 ТБМ. Гальваническую развязку по питанию при взаимодействии устройства управления и связи обеспечивают оптроны: шесть элементов 3ОТ123А и четыре элемента 249ЛП1А. Первая группа входов-выходов приемо-передатчика 11 обеспечивает взаимодействие устройства управления и связи с внешней системой связи по основному и резервному каналам. Вторая группа входов-выходов приемо-передатчика 11 содержит обычную и буферизированную шины данных, сигналы управления и сигналы чтения-записи.

Устройство 12 связи обеспечивает обмен цифровой информацией по последовательным двухпроводным линиям связи (старт-стопным кодом с восемью информационными битами) между процессорным устройством 1 и всеми блоками устройства управления и связи: блоком связи 1, блоком связи 2, блоком-преобразователем, а также между устройством управления и связи и внешними приборами. Схема дистанционного включения питания внешних приборов реализована на двух регистрах 1554ИР23 ТБМ, двух 4-канальных коммутаторах тока 1109КТ4Б и десяти реле РПС46. Управление 4-канальными коммутаторами тока 1109КТ4Б выполнено на 8-канальном двунаправленном приемо-передатчике 1554АП6 ТБМ и на элементах 2И-НЕ серии 1554 ТБМ. Схема дистанционного включения питания устройства управления и связи и определения инициатора обмена реализована на шести реле РЭК81 и регистре 1554ИР22 ТБМ. Схема приемо-передатчика для обмена цифровой информацией устройства управления и связи с внешними приборами выполнена на оптронах 3ОТ110Б и 249ЛП1А, трех транзисторах из сборки 1НТ251А. Первая группа входов-выходов устройства 12 связи содержит сигналы дистанционного включения питания устройства управления и связи, сигналы дистанционного включения питания внешних приборов, сигналы чтения-записи. Вторая группа входов-выходов устройства 12 связи содержит обычную и буферизированную шины данных, сигналы управления и вызова.

Устройство 13 связи обеспечивает обмен цифровой информацией между блоком-преобразователем и центральным процессорным устройством. Схемотехнически, для защиты от помех и разрядов статического электричества устройство 13 связи реализовано на четырех триггерах Шмитта - инверторах серии 1554ТБМ и резисторах. Первая группа входов-выходов устройства 13 связи содержит сигналы чтения-записи. Вторая группа входов-выходов устройства 13 связи содержит последовательную шину данных.

Устройство 14 связи обеспечивает обмен цифровой информацией между блоком связи 1 и центральным процессорным устройством. Схемотехнически для защиты от помех и статического напряжения устройство 14 связи реализовано на четырех триггерах Шмитта - инверторах серии 1554ТБМ и резисторах. Первая группа входов-выходов устройства 14 связи содержит сигналы чтения-записи. Вторая группа входов-выходов устройства 14 связи содержит последовательную шину данных.

Устройство 15 связи обеспечивает обмен цифровой информацией между блоком связи 2 и центральным процессорным устройством. Схемотехнически для защиты от помех и разрядов статического электричества устройство 15 связи реализовано на четырех триггерах Шмитта - инверторах серии 1554ТБМ и резисторах. Первая группа входов-выходов устройства 15 связи содержит сигналы чтения-записи. Вторая группа входов-выходов устройства 15 связи содержит последовательную шину данных.

Блок 16 самоконтроля обеспечивает автономную проверку функционирования устройства управления и связи при подключении специального жгута самоконтроля. В состав схемы блока 16 самоконтроля входят два регистра 1554ИР22 ТБМ, обеспечивающие прием и контроль информации при проведении самоконтроля устройства управления и связи. Для управления включением питания устройства 5 коммутации применены: регистр 1554ИР23 ТБМ, 4-канальный коммутатор тока 1109КТ4Б и два реле РЭК81. Первая группа входов-выходов блока 16 самоконтроля содержит сигналы управления. Вторая группа входов-выходов блока 16 самоконтроля содержит тестовые сигналы.

Устройство управления и связи работает следующим образом.

В выключенном состоянии устройство управления и связи находится в дежурном режиме. Источник 6 питания выдает питание на входные цепи устройства управления и связи, которые обеспечивают дистанционное включение питания устройства управления и связи.

Внешняя система связи выдает в устройство управления и связи команду на дистанционное включение питания, которая поступает в приемопередатчик 11, обеспечивающий включение питания устройства управления и связи. Одновременно приемо-передатчик 11 выдает в процессорное устройство 1 информацию об инициаторе обмена информацией с устройством управления и связи внешней системе связи. Получив от приемо-передатчика 11 сигнал о готовности устройства управления и связи к приему информации, внешняя система связи выдает в приемо-передатчик 11 пакет цифровой информации (ИНФОРМАЦИЯ), который затем поступает в процессорное устройство 1. Процессорное устройство 1 определяет тип и назначение принятой от внешней системы связи ИНФОРМАЦИИ и выдает через устройство 12 связи в устройство 5 коммутации команду для подключения двухпроводных линий связи к устройству 13 связи для обеспечения информационного обмена между центральным процессорным устройством и блоком-преобразователем. Затем процессорное устройство 1 через устройство 12 связи и устройство 5 коммутации выдает в устройство 13 связи ИНФОРМАЦИЮ, полученную от внешней системы связи. В свою очередь, устройство 13 выдает ИНФОРМАЦИЮ в процессорное устройство 2. Получив и проанализировав ИНФОРМАЦИЮ, процессорное устройство 2 через устройство 13 связи, устройство 5 коммутации и устройство 12 связи запрашивает у процессорного устройства 1 дополнительную цифровую информацию (ИНФОРМАЦИЯ Д), необходимую для преобразования полученных данных. Процессорное устройство 1 определяет вид необходимой для преобразований ИНФОРМАЦИИ Д. Затем процессорное устройство 1 через устройство 12 связи и устройство 5 коммутации выдает команду на выдачу необходимой ИНФОРМАЦИИ Д во внешний прибор Г (прибор Д). Прибор Г (прибор Д) выдает ИНФОРМАЦИЮ Д в процессорное устройство 1 через устройство 5 коммутации и устройство 12 связи. Процессорное устройство 1 передает ИНФОРМАЦИЮ Д в процессорное устройство 2 через устройство 12 связи, устройство 5 коммутации и устройство 13 связи. Процессорное устройство 2, используя полученную ИНФОРМАЦИЮ Д, выполняет преобразование ИНФОРМАЦИИ, полученной ранее от внешней системы связи. Выполнив необходимое преобразование ИНФОРМАЦИИ, процессорное устройство 2 записывает преобразованную информацию (ИНФОРМАЦИЯ П) в блок 7 долговременной энергонезависимой памяти и выдает сигнал о выполнении преобразования в процессорное устройство 1 через устройство 13 связи, устройство 5 коммутации и устройство 12 связи. Получив от процессорного устройства 2 сигнал о выполнении преобразования, процессорное устройство 1 записывает в блок 8 долговременной энергонезависимой памяти данные о проведенном преобразовании. Затем питание устройства управления и связи отключается.

Внешняя система управления А (система управления Б) выдает в устройство управления и связи команду на дистанционное включение питания, которая через блок связи 1 (блок связи 2) и устройство 5 коммутации поступает в устройство 12 связи, обеспечивающее включение питания устройства управления и связи. Одновременно устройство 12 связи выдает в процессорное устройство 1 информацию об инициаторе обмена информацией с устройством управления и связи внешней системе управления. Процессорное устройство 1, проанализировав информацию об инициаторе обмена с устройством управления и связи, выдает через устройство 12 связи в устройство 5 коммутации команду для подключения двухпроводных линий связи к устройству 14 связи (устройству 15 связи) для обеспечения информационного обмена между центральным процессорным устройством и блоком связи 1 (блоком связи 2). Получив от приемопередатчика 9 (приемо-передатчика 10) сигнал о готовности устройства управления и связи к приему информации, внешняя система управления А (система управления Б) выдает в приемо-передатчик 9 (приемопередатчик 10) пакет цифровой информации (ИНФОРМАЦИЯ У). Затем приемо-передатчик 9 (приемо-передатчик 10) передает полученную ИНФОРМАЦИЮ У в процессорное устройство 3 (процессорное устройство 4) и через устройство 14 связи (устройство 15 связи), устройство 5 коммутации и устройство 12 связи передается в процессорное устройство 1. Проанализировав полученную ИНФОРМАЦИЮ У, процессорное устройство 1 выдает в процессорное устройство 2 (через устройство 12 связи, устройство 5 коммутации и устройство 13 связи) команду на выдачу ИНФОРМАЦИИ П. Процессорное устройство 2 проверяет наличие необходимой ИНФОРМАЦИИ П в блоке 7 долговременной энергонезависимой памяти. При наличии требуемых данных процессорное устройство 2 передает их в процессорное устройство 1 (через устройство 13 связи, устройство 5 коммутации и устройство 12 связи). При отсутствии необходимой ИНФОРМАЦИИ П процессорное устройство 2 сообщает процессорному устройству 1 об отказе в выдаче ИНФОРМАЦИИ П. Получив ИНФОРМАЦИЮ П и обработав ИНФОРМАЦИЮ У, процессорное устройство 1 через устройство 12 связи и устройство 5 коммутации выдает пакет цифровой информации, содержащий управляющие команды и ИНФОРМАЦИЮ П, в приборы В. Результаты выполнения управляющих команд с использованием ИНФОРМАЦИИ П (РЕЗУЛЬТАТЫ) приборы В выдают в процессорное устройство 1 (через устройство 5 коммутации и устройство 12 связи), которое передает их через устройство 12 связи, устройство 5 коммутации и устройство 14 связи (устройство 15 связи) в процессорное устройство 3 (процессорное устройство 4). Затем внешняя система управления А (система управления Б) выдает в блок связи 1 (блок связи 2) команду на выдачу РЕЗУЛЬТАТОВ, которая поступает через приемо-передатчик 9 (приемо-передатчик 10) в процессорное устройство 3 (процессорное устройство 4). Обработав вышеуказанную команду, процессорное устройство 3 (процессорное устройство 4) выдает РЕЗУЛЬТАТЫ через приемо-передатчик 9 (приемо-передатчик 10) во внешнюю систему управления А (систему управления Б). Затем питание устройства управления и связи отключается.

Изготовлен лабораторный макет устройства управления и связи, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СВЯЗИ С ВНЕШНИМИ УСТРОЙСТВАМИ И СИСТЕМАМИ | 2014 |

|

RU2565013C1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1990 |

|

SU1839257A1 |

| УСТРОЙСТВО КОММУТАЦИИ И СВЯЗИ | 2010 |

|

RU2429562C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

Изобретение относится к средствам обработки цифровых данных, области защиты от несанкционированного доступа к информации и может быть использовано для обработки и преобразования информации. Техническим результатом является повышение быстродействия и расширение функциональных возможностей. Устройство связи с внешними устройствами и системами содержит четыре процессорных устройств, устройство коммутации, источник питания, два блока долговременной энергонезависимой памяти, три приемопередатчика, четыре устройства связи, блок самоконтроля. 1 ил.

Устройство связи с внешними устройствами и системами, содержащее первое процессорное устройство и устройство коммутации, отличающееся тем, что дополнительно введены источник питания, первый и второй блоки долговременной энергонезависимой памяти, второе, третье и четвертое процессорные устройства, первый, второй и третий приемопередатчики, первое, второе, третье и четвертое устройства связи, блок самоконтроля, первая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов первого устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов первого процессорного устройства, вторая группа входов-выходов которого соединена с группой входов-выходов первого блока долговременной энергонезависимой памяти, вторая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов второго устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов второго процессорного устройства, вторая группа входов-выходов которого соединена с группой входов-выходов второго блока долговременной энергонезависимой памяти, третья группа входов-выходов устройства коммутации соединена с первой группой входов-выходов третьего устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов третьего процессорного устройства, вторая группа входов-выходов которого соединена с первой группой входов-выходов первого приемопередатчика, вторая группа входов-выходов которого является первой группой входов-выходов устройства управления и связи, четвертая группа входов-выходов устройства коммутации соединена с первой группой входов-выходов четвертого устройства связи, вторая группа входов-выходов которого соединена с первой группой входов-выходов четвертого процессорного устройства, вторая группа входов-выходов которого соединена с первой группой входов-выходов второго приемопередатчика, вторая группа входов-выходов является второй группой входов-выходов устройства управления и связи, пятая, шестая, седьмая, восьмая и девятая группы входов-выходов устройства коммутации являются третьей, четвертой, пятой, шестой и седьмой группами входов-выходов устройства контроля и связи соответственно, первая группа входов-выходов третьего приемопередатчика является восьмой группой входов-выходов устройства управления и связи, а вторая группа входов-выходов соединена с третьей группой входов-выходов первого процессорного устройства, четвертая группа входов-выходов которого соединена с первой группой входов-выходов блока самоконтроля, вторая группа входов-выходов которого является девятой группой входов-выходов устройства управления и связи, при этом каждые устройства, блоки и приемопередатчики соответствующими выводами соединены с соответствующими выводами источника питания.

| Процессор связи | 1976 |

|

SU682890A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ С САМОКОНТРОЛЕМ | 1999 |

|

RU2161813C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МЕТАЛЛИЧЕСКИХ ОТЛИВОК | 1940 |

|

SU59284A1 |

| US 6233702 B1, 15.05.2001 | |||

| US 6157967 A, 05.12.2000 | |||

| US 6496940 B1, 17.12.2002. | |||

Авторы

Даты

2010-09-27—Публикация

2008-11-17—Подача