Изобретение модель относится к вычислительной технике и может быть использовано при построении многомашинных, многопроцессорных вычислительных систем (ВС) высокой производительности и надежности.

Известна резервированная двухпроцессорная вычислительная система [РФ №2264648 C1, G06F 11/20, 27.05.2005 г.], содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу коммутатора, системный генератор, выход которого подключен к первому входу процессора первого канала, схему начальной установки, выход которой подключен ко второму входу процессора первого канала, импульсный генератор, элемент ИЛИ, временной анализатор исправности, счетчик сбоев, триггер, элемент ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, второй выход процессора через элемент ИЛИ подключен к первому входу триггера и ко второму входу временного анализатора исправности, выход триггера подключен к первому входу элемента ИЛИ-НЕ, второй вход процессора соединен со вторым входом элемента ИЛИ и вторым входом счетчика сбоев, выход импульсного генератора через временной анализатор исправности подключен к первому входу счетчика сбоев и ко второму входу триггера, второй выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, а также введены системный генератор, выход которого подключен к первому входу процессора второго канала, схема начальной установки, выход которой подключен ко второму входу процессора второго канала, и схема сравнения, первый вход которой подключен к первому выходу счетчика сбоев первого канала, второй вход схемы сравнения подключен к первому выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы.

Недостатком известной системы является то, что она может использоваться только при построении надежных вычислительно систем за счет резервирования каналов.

Наиболее близкой к заявляемой является вычислительная система [АС №873804 А1, G06F 15/16, 15.06.19941, содержащая N цифровых вычислительных машин (ЦВМ), N каналов ввода-вывода, N блоков электропитания, N групп устройств сопряжения, N*M внешних абонентов (М - число внешних абонентов в группе) и блок управления, причем первый вход-выход ЦВМ соединен с соответствующим входом-выходом блока управления, второй вход-выход ЦВМ соединен с первым входом-выходом соответствующего канала ввода-вывода, первый выход ЦВМ соединен с входом соответствующего блока электропитания, второй вход-выход канала ввода-вывода соединен с первым входом-выходом устройств сопряжения соответствующей группы, второй вход-выход устройства сопряжения соединен с входами-выходами внешних абонентов соответствующей группы, отличающаяся тем, что с целью повышения быстродействия она содержит N адаптеров, N блоков приоритета и N коммутаторов, причем один вход-выход адаптера соединен со вторым входом-выходом соответствующего канала ввода-вывода, другие входы-выходы одного адаптера соединены с соответствующими входами-выходами других адаптеров, запускающий вход блока приоритета соединен с выходом соответствующего канала ввода-вывода, запросные входы блока приоритета соединены с выходами устройств сопряжения соответствующей группы, выходы блока приоритета соединены с первыми входами устройств сопряжения соответствующей группы, вторые входы которых соединены с выходами соответствующего коммутатора, выход блока электропитания и второй выход ЦВМ соединены с входами соответствующего коммутатора, а каждый вход-выход группы входов-выходов блока управления соединен со вторым входом-выходом соответствующего устройства сопряжения.

Недостатком данной системы являются отсутствие возможности управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

Техническим результатом является обеспечение возможности управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

Технический результат достигается тем, что в вычислительную систему, содержащую пять электронных вычислительных машин (ЭВМ), три канала ввода-вывода, три внешних абонента и устройство управления, причем соответствующие входы входы-выходы ЭВМ соединены шинами с соответствующими входами-выходами устройства управления, дополнительно введены блок основной общей памяти (ОП) и блок резервной ОП, соответствующие входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, первые три ЭВМ используются как универсальные, четвертая ЭВМ используется в качестве управляющей, а пятая ЭВМ является резервной, входы-выходы каждого соответствующего абонента соединены шинами входами-выходами соответствующего канала ввода-вывода, входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, причем устройство управления содержит два блока элементов ИЛИ, блок элементов ИЛИ, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок управления системой при возникновении неисправности одной из универсальных ЭВМ, блок связи всех ЭВМ системы с внешними абонентами, блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ, с первого по тридцать третий входы устройства соединены соответственно с первого по тридцать третий входы первого блока элементов ИЛИ, с тридцать четвертого по шестьдесят восьмой входы устройства соединены соответственно с первого по тридцать пятый входы второго блока элементов ИЛИ, с первого по четвертый выходы первого блока элементов ИЛИ соединены соответственно с первого по четвертый входами блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, пятый вход которого соединен с выходом блока элементов ИЛИ, второй вход блока управления системой при записи и считывания контрольной точки универсальных ЭВМ соединен с объединенными первыми входами, блока управления системой при возникновении неисправности одной из универсальных ЭВМ, блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ и четвертым входом блока связи всех ЭВМ системы с внешними абонентами, с пятого по двенадцатый входы первого блока элементов ИЛИ соединены соответственно с шестого по тринадцатый входами блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, с тринадцатого по пятнадцатый входы первого блока элементов ИЛИ соединены соответственно с третьего по пятый блока управления системой при возникновении неисправности одной из универсальных ЭВМ, с первого по пятый входы второго блока элементов ИЛИ соединены соответственно с десятого по четырнадцатый блока управления системой при возникновении неисправности одной из универсальных ЭВМ, второй вход которого соединен с третьим входом блока связи всех ЭВМ системы с внешними абонентами и седьмым выходом второго блока элементов ИЛИ, шестой выход которого соединен со вторым входом блока связи всех ЭВМ системы с внешними абонентами, первый вход которого соединен с третьим входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, четвертый вход которого соединен с шестым входом блока связи всех ЭВМ системы с внешними абонентами, пятый вход которого соединен с восьмым выходом второго блока элементов ИЛИ, с девятого по четырнадцатый выходы которого соединены соответственно с седьмого по двенадцатый входами блока связи всех ЭВМ системы с внешними абонентами, с тринадцатого по пятнадцатый входы которого соединены соответственно каждый с объединенными с первого по третий входами блока элементов ИЛИ, с пятого по седьмой входами блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, с четвертого по шестой входами блока управления системой при возникновении неисправности в ОП и с двадцать первого по двадцать третий выходами второго блока элементов ИЛИ, пятнадцатый и шестнадцатый выходы которого соединены каждый соответственно с третьим и четвертым входами блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, восьмой вход которого соединен с шестым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, восьмой вход которого соединен с пятнадцатым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, восьмой вход которого соединен с седьмым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, одиннадцатый вход которого соединен с седьмым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, девятый вход которого соединен с тринадцатым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, двенадцатый вход которого соединен с шестым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый вход которого соединен со вторым входом блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, девятый вход которого соединен с семнадцатым выходом второго блока элементов ИЛИ, с восемнадцатого по двадцатый выходы которого соединены соответственно с первого по третий входами блока управления системой при возникновении неисправности в ОП, седьмой и восьмой входы которого соединены соответственно с девятнадцать четвертым и двадцать пятым выходами второго блока элементов ИЛИ, с первого по десятый выходы блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ соединены соответственно с двадцать девятого по тридцать восьмой выходами устройства, с тридцать девятого по сорок пятый выходы которого соединены соответственно с первого по седьмой выходами блока управления системой при возникновении неисправности в ОП, с третьего по восьмой выходы блока управления системой при записи и считывания контрольной точки универсальных ЭВМ соединены соответственно со второго по седьмой выходами устройства, первый выход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен одиннадцатым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, первый выход которого соединен со вторым входом второго элемента ИЛИ, первый вход которого соединен со вторым выходом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, первый выход которого соединен с первым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с восьмым выходом устройства, девятый выход которого соединен со вторым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, с шестого по десятый выходы которого соединены соответственно с одиннадцатого по пятнадцатый выходами устройства, десятый выход которого соединен с четвертым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, третий выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым выходом блока связи всех ЭВМ системы с внешними абонентами, а выход соединен с семнадцатым выходом устройства, шестнадцатый выход которого соединен с двенадцатым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с восьмым выходом блока связи всех ЭВМ системы с внешними абонентами, а выход соединен с двадцать восьмым выходом устройства, с восемнадцатого по двадцать третий выходы которого соединены соответственно со второго по седьмой выходами блока связи всех ЭВМ системы с внешними абонентами, с девятого по двенадцатый выходы которого соединены соответственно с двадцать четвертого по двадцать седьмой выходами устройства, причем первый блок элементов ИЛИ содержит девять элементов ИЛИ, с первого по третий входы блока соединены соответственно с первого по третий входами первого элемента ИЛИ, выход которого соединен с первым выходом блока, второй выход которого соединен с четвертым входом блока, с пятого по седьмой входы которого соединены с первого по третий входами второго элемента ИЛИ, выход которого соединен с третьим выходом блока, с восьмого по десятый входы которого соединены с первого по третий входами третьего элемента ИЛИ, выход которого соединен с четвертым выходом блока, с одиннадцатого по тринадцатый входы которого соединены с первого по третий входами четвертого элемента ИЛИ, выход которого соединен с пятым выходом блока, четырнадцатый и пятнадцатый входы которого соединены соответственно с его шестым и седьмым выходами, с шестнадцатого по восемнадцатый входы которого соединены с первого по третий входами пятого элемента ИЛИ, выход которого соединен с восьмым выходом блока, с девятнадцатого по двадцать первый входы которого соединены с первого по третий входами шестого элемента ИЛИ, выход которого соединен с девятым выходом блока, двадцать второй, двадцать третий и двадцать четвертый входы которого соединены соответственно с десятым, одиннадцатым и двенадцатым выходами блока, с двадцать пятого по двадцать седьмой входы которого соединены с первого по третий входами седьмого элемента ИЛИ, выход которого соединен с тринадцатым выходом блока, с двадцать восьмого по тридцатый входы которого соединены с первого по третий входами восьмого элемента ИЛИ, выход которого соединен с четырнадцатым выходом блока, с тридцать первого по тридцать третий входы которого соединены с первого по третий входами девятого элемента ИЛИ, выход которого соединен с пятнадцатым выходом блока, причем второй блок элементов ИЛИ содержит пять элементов ИЛИ с первого по пятый входы блока соединены соответственно каждый с первого по пятый его выходами, с шестого по восьмой входы которого соединены с первого по третий входами первого элемента ИЛИ, выход которого соединен с шестым выходом блока, девятый вход которого соединен с седьмым выходом блока, с десятого по двенадцатый входы которого соединены с первого по третий входами второго элемента ИЛИ, выход которого соединен с восьмым выходом блока, с тринадцатого по пятнадцатый входы которого соединены с первого по третий входами третьего элемента ИЛИ, выход которого соединен с девятым выходом блока, с шестнадцатого по двадцатый входы блока соединены соответственно каждый с десятого по четырнадцатый его выходами, с двадцать первого по двадцать третий входы которого соединены с первого по третий входами четвертого элемента ИЛИ, выход которого соединен с пятнадцатым выходом блока, с двадцать четвертого по двадцать шестой входы которого соединены с первого по третий входами пятого элемента ИЛИ, выход которого соединен с шестнадцатым выходом блока, с двадцать седьмого по тридцать пятый входы блока соединены соответственно каждый с семнадцатого по двадцать пятый его выходами, причем блок управления системой при записи и считывания контрольной точки универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, четыре блока элементов И, состоящих из N элементов И каждый, два буферных запоминающих блока и три блока элементов И, состоящих из N элементов И каждый, выходы которых соединены соответственно с шестым, седьмым и восьмым выходами блока, первый вход которого соединен с его первым выходом, второй вход блока соединен с входом дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И и соответственно с первым, вторым и третьем входами формирователя адреса, выход которого соединен со вторым выходом блока, третий выход которого соединен с нулевым входом триггера и четвертым входом блока, третий вход которого соединен с единичным входом триггера, единичный выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с пятым входом блока, шестой вход которого соединен с первым входом четвертого блока элементов И и с третьим входом первого блока элементов И, выход которого соединен с входом первого буферного запоминающего блока, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с четвертым выходом блока, седьмой вход которого соединен с первым входом третьего блока элементов И и вторым входом второго блока элементов И, третий вход которого соединен с восьмым входом блока, девятый вход которого соединен с его пятым выходом, десятый вход блока соединен со вторым входом четвертого блока элементов И, третий вход которого соединен с выходом второго буферного запоминающего блока, вход которого соединен с выходом третьего блока элементов И, второй и третий входы которого соединены соответственно с одиннадцатым и двенадцатым входами блока, тринадцатый вход которого соединен с четвертым входом четвертого блока элементов И, выход которого соединен с объединенными вторыми входами первого второго и третьего блоков элементов И, причем блок управления системой при возникновении неисправности одной из универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, три блока элементов И, состоящих из N элементов И, четыре блока элементов И, состоящих из N элементов И каждый, блок элементов ИЛИ, состоящий из N элементов, буферный запоминающий блок и элемент И, выход которого соединен с четвертым выходом блока, первый вход которого соединен с входом дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И и соответственно с первым, вторым и третьем входами формирователя адреса, выход которого соединен с первым выходом блока, второй вход которого соединен с объединенными первыми входами первого и второго блоков элементов И, первым входом элемента И и вторым выходом блока, третий вход которого соединен с его третьим выходом, вторым входом элемента И и единичным входом триггера, единичный выход которого соединен с объединенными вторыми входами первого, второго, третьего и четвертого блоков элементов И, а нулевой вход триггера соединен с четвертым входом блока и объединенными его пятым и шестым выходами, пятый вход блока соединен с объединенными вторыми входами первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с седьмым, восьмым и девятым выходами блока, шестой и седьмой входы которого соединены соответственно с третьим и четвертым входами третьего блока элементов И, пятый вход которого соединен с четвертым входом четвертого блока элементов И и восьмым входом блока, девятый и десятый входы которого соединены соответственно с четвертым и пятым входами второго блока элементов И, шестой вход которого соединен с четвертым входом третьего блока элементов И и одиннадцатым входом блока, двенадцатый вход которого соединен с его одиннадцатым выходом, тринадцатый и четырнадцатый входы блока соединены соответственно с первым и третьим входами третьего блока элементов И, выход которого соединен со вторым входом блока элементов ИЛИ, первый вход которого соединен с выходом первого блока элементов И, а выход соединен с входом буферного запоминающего блока, выход которого соединен с объединенными третьим входом второго блока элементов И и первым входом четвертого блока элементов И, третий вход которого соединен с пятнадцатым входом блока, а выход соединен с двенадцатым выходом блока, десятый выход которого соединен с выходом второго блока элементов И, причем блок связи всех ЭВМ системы с внешними абонентами содержит два дешифратора, триггер, пять элементов ИЛИ, элемент НЕ, шестнадцать блоков элементов И, состоящих из N элементов И каждый, и пять блоков элементов ИЛИ, состоящих из N элементов И каждый, первый и второй входы блока соединены соответственно с его первым и вторым выходами и первым и вторым входами первого элемента ИЛИ, выход которого соединен с единичным входом триггера, единичный выход которого соединен с объединенными вторыми входами второго, третьего, десятого и одиннадцатого блоков элементов И, а нулевой выход триггера соединен с объединенными первыми входами седьмого И, восьмого И, девятого И, четырнадцатого И, пятнадцатого И и шестнадцатого И блоков элементов И, третий вход блока соединен с объединенными первым входом второго И, третьим входом десятого И блоков элементов И и входом элемента НЕ, выход которого соединен с объединенными первым входом третьего И, третьим входом одиннадцатого И блоков элементов И, четвертый вход блока соединен с входом первого дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно второго, третьего и четвертого элементов ИЛИ, вторые входы которых соединены с соответственно с первым, вторым и третьим выходами второго дешифратора, вход которого соединен с пятым входом блока, шестой и седьмой входы которого соединены соответственно с его восьмым и девятым выходами и соответственно с первым и вторым входами пятого элемента ИЛИ, выход которого соединен с нулевым входом триггера, восьмой, девятый и десятый входы блока соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены с соответствующими входами первого блока элементов ИЛИ, выход которого соединен с объединенными третьими входами второго и третьего блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, одиннадцатый и двенадцатый входы которого соединены с первыми входами соответственно десятого и одиннадцатого блоков элементов И, выходы которых соединены соответственно с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого, пятого и шестого блоков элементов И, выходы которых соединены с первыми входами соответственно третьего, четвертого и пятого блоков элементов ИЛИ, вторые входы которых соединены с выходами соответственно седьмого, восьмого и девятого блоков элементов И, вторые входы которых соединены соответственно с тринадцатым, четырнадцатым и пятнадцатым входами блока, десятый одиннадцатый и двенадцатый выходы которого соединены с выходами соответственно третьего, четвертого и пятого блоков элементов ИЛИ, пятый, шестой и седьмой выходы блока соединены с выходами соответственно четырнадцатого И, пятнадцатого И и шестнадцатого И блоков элементов И, вторые входы которых соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, первые входы которых соединены с выходами соответственно второго, третьего и четвертого элемента ИЛИ, причем блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, три элемента И, восемь блоков элементов И, состоящих из N элементов И каждый, и блок элементов ИЛИ, выход которого соединен со вторым входом четвертого блока элементов И, выход которого соединен с седьмым выходом блока, первый вход которого соединен с входом дешифратора, первый выход которого соединен с объединенными первыми входами первого элемента И, первого и шестого блоков элементов И и формирователя адреса, второй вход которого соединен с объединенными первыми входами второго элемента И, второго и седьмого блоков элементов И и вторым выходом дешифратора, третий выход которого соединен с объединенными первыми входами третьего элемента И, третьего и восьмого блоков элементов И и третьим входом формирователя адреса, выход которого соединен с первым выходом блока, второй, третий и четвертый выходы которого соединены с выходами соответственно первого, второго и третьего элементов И, вторые входы которых объединены и соединены со вторым входом блока, третий вход которого соединен с его пятым выходом и единичным входом триггера, единичный выход которого соединен с объединенными первыми входами четвертого и пятого элементов И, а нулевой вход триггера соединен с объединенными четвертым входом и шестым выходом блока, пятый, шестой и седьмой входы которого соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с первым, вторым, и третьим входами элемента ИЛИ, восьмой вход блока соединен с объединенными третьими входами четвертого и пятого элементов И, девятый вход блока соединен со вторым входом пятого элемента И, выход которого соединен с объединенными вторыми входами шестого, седьмого и восьмого блоков элементов И, выходы которых соединены соответственно с восьмым, девятым и десятым выходами блока, причем блок управления системой при возникновении неисправности в ОП содержит дешифратор, триггер, десять блоков элементов И, состоящих из N элементов И каждый, и два блока элементов ИЛИ, состоящие из N элементов ИЛИ, первый вход блока соединен с его первым выходом и единичным входом триггера, нулевой вход которого соединен со вторым входом блока и его вторым выходом, третий вход блока соединен с входом дешифратора, первый выход которого соединен с объединенными первыми входами первого и шестого блоков элементов И, второй выход дешифратора соединен с объединенными первыми входами второго и седьмого блоков элементов И, третий выход дешифратора соединен с объединенными первыми входами третьего и восьмого блоков элементов И, четвертый, пятый и шестой входы блока соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с первым, вторым и третьим входами первого блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого и пятого блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, пятый, шестой и седьмой выходы которого соединены с выходами соответственно шестого, седьмого и восьмого блоков элементов И, вторые входы которых объединены и соединены с выходом второго блока элементов ИЛИ, первый и второй входы которого соединены с выходами соответственно девятого и десятого блоков элементов И, вторые входы которых соединены соответственно с седьмым и восьмым входами блока, единичный выход триггера соединен с объединенными первыми входами четвертого и девятого блоков элементов И, а нулевой выход триггера соединен с объединенными первыми входами пятого и десятого блоков элементов И.

Введение указанных дополнительных элементов и последовательности их подключения позволяют обеспечить возможность управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

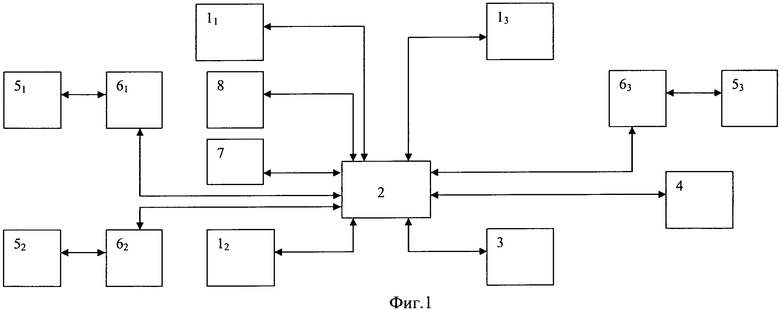

На фиг.1 - представлена функциональная схема вычислительной системы.

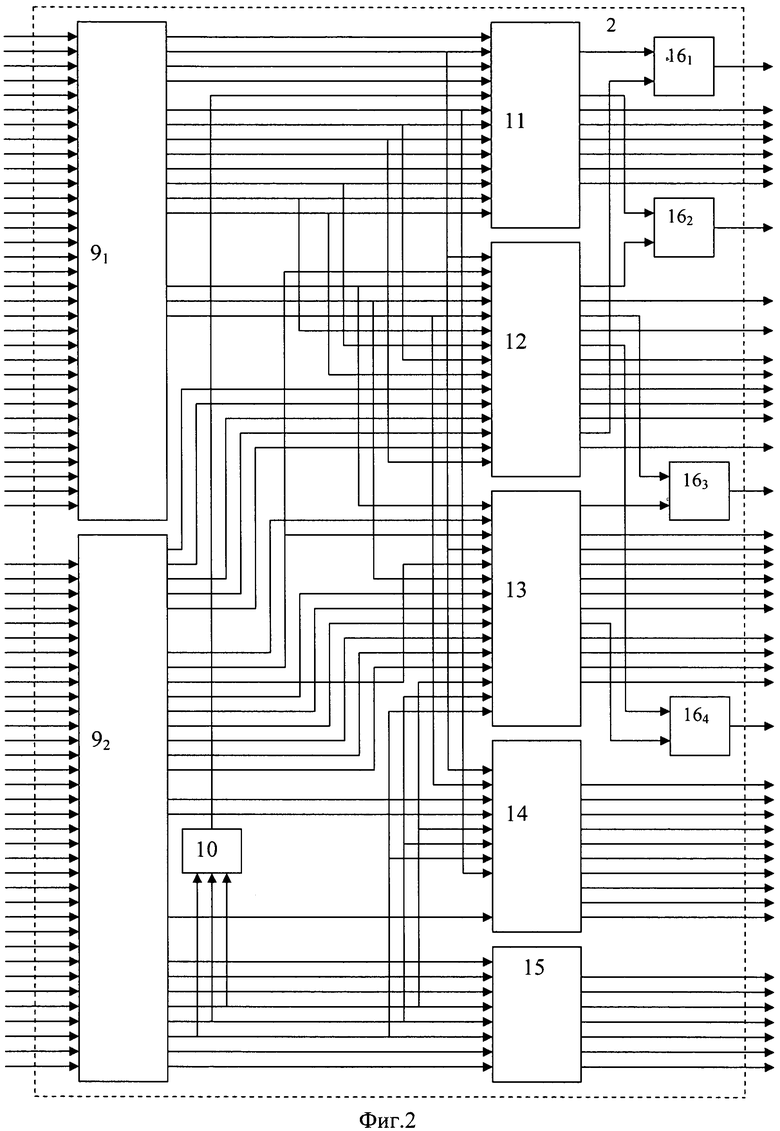

На фиг.2 - представлена функциональная схема устройства управления.

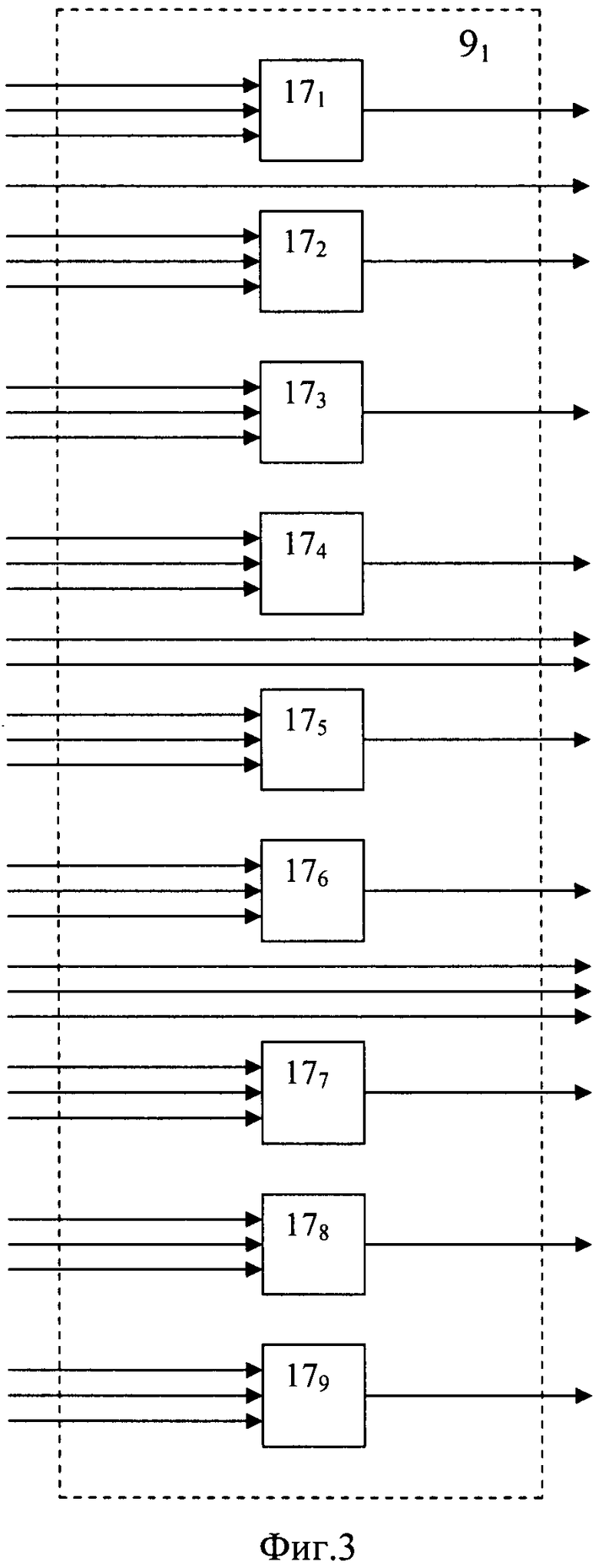

На фиг.3 - представлена функциональная схема первого блока элементов ИЛИ.

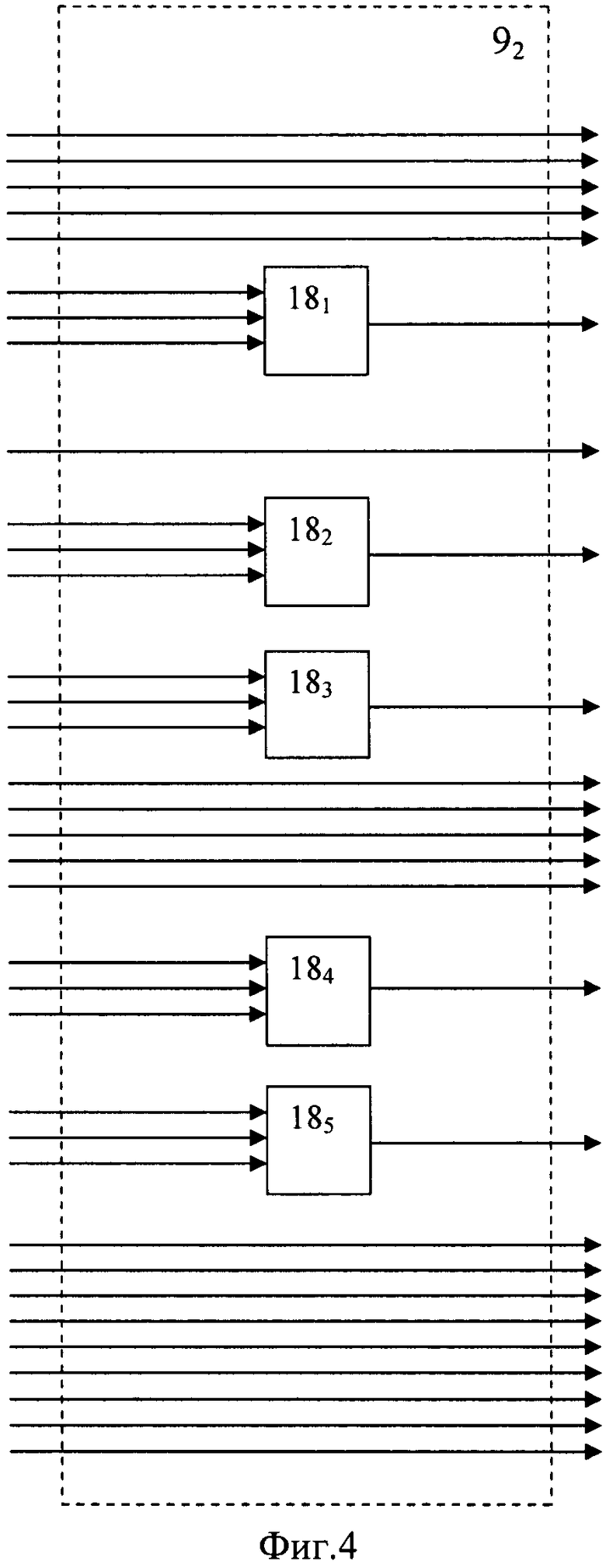

На фиг.4 - представлена функциональная схема второго блока элементов ИЛИ.

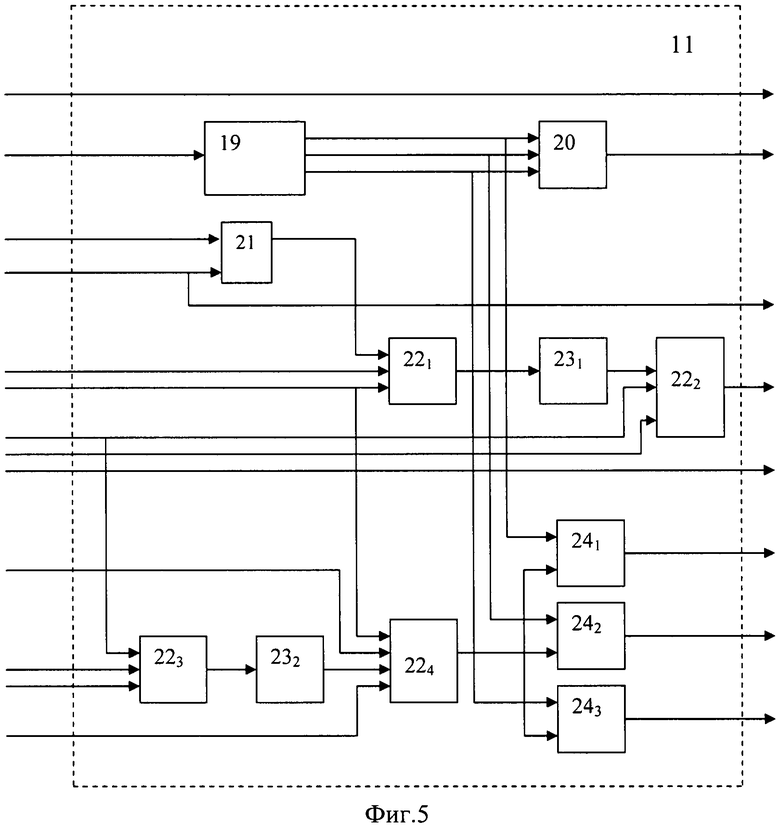

На фиг.5 - представлена функциональная схема блока управления системой при записи и считывания контрольной точки универсальных ЭВМ.

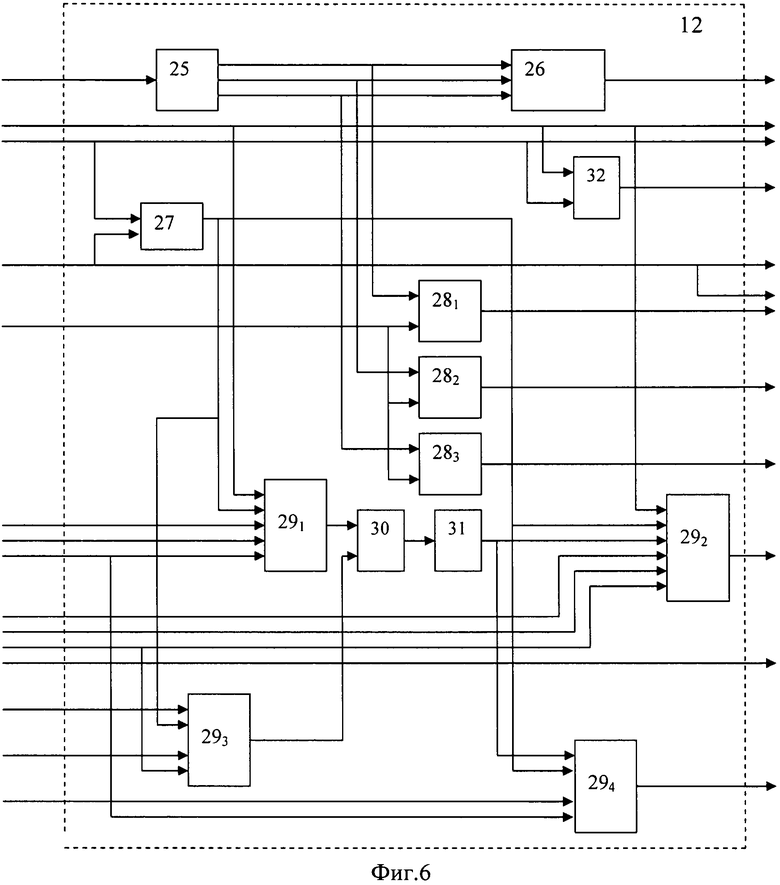

На фиг.6 - представлена функциональная схема блока управления системой при возникновении неисправности универсальных ЭВМ.

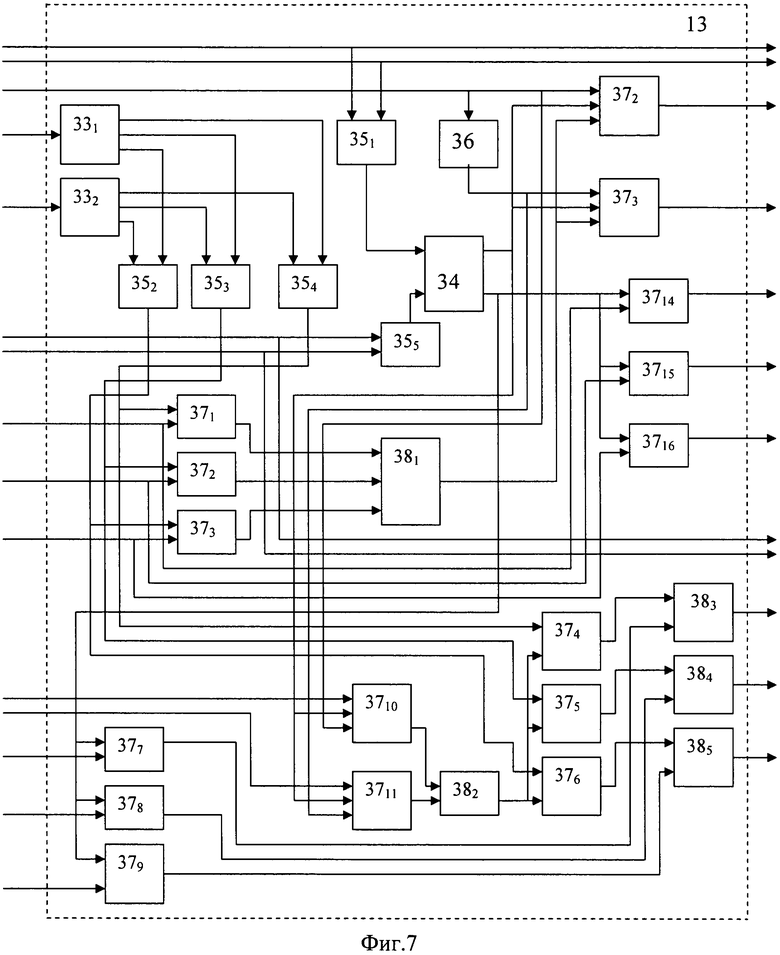

На фиг.7 - представлена функциональная схема блока связи всех ЭВМ системы с внешними абонентами.

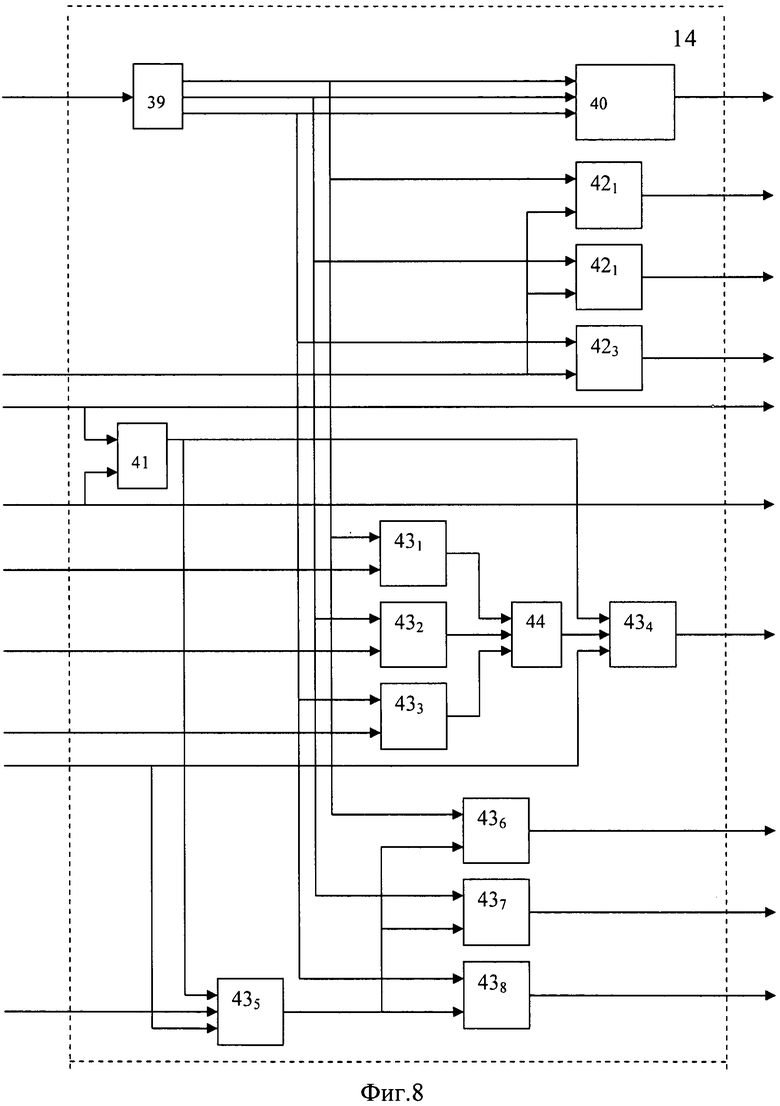

На фиг.8 - представлена функциональная схема блока управления системой при возникновении неисправности запоминающих устройств (ЗУ) универсальных ЭВМ.

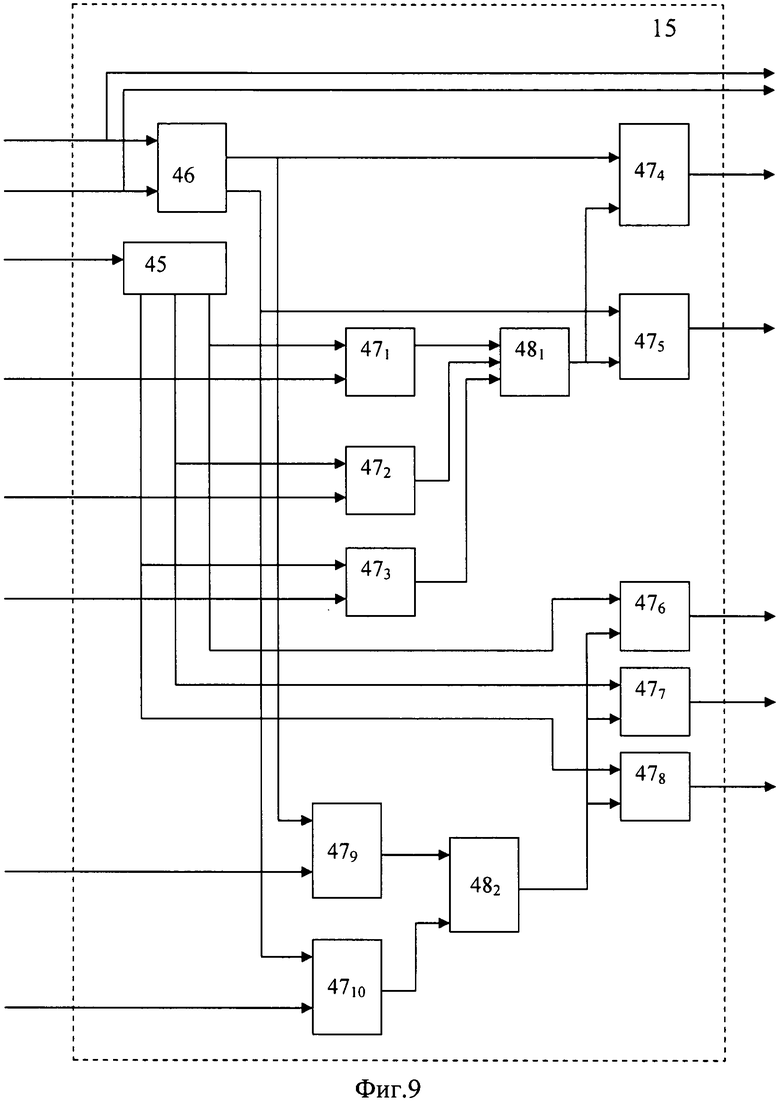

На фиг.9 - представлена функциональная схема блока управления системой при возникновении неисправности в общей памяти (ОП).

Система (фиг.1) содержит три 11-13 универсальных ЭВМ, устройство управления системой 2, универсальную резервную ЭВМ 3, управляющую ЭВМ 4, три внешних абонента 51-53, три устройства ввода-вывода 61-63, блок 7 основной ОП и блок 8 резервной ОП.

Устройство управления 2 (фиг.2) содержит два блока элементов ИЛИ 91-92, блок 10, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блок 13 связи всех ЭВМ системы с внешними абонентами, блок 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок 15 управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ 161-164.

Первый блок элементов ИЛИ 91 (фиг.3) содержит девять элементов ИЛИ 171-179.

Второй блок элементов ИЛИ 92 (фиг.4) содержит пять элементов ИЛИ 181-185.

Блок управления системой при записи и считывания контрольной точки универсальных ЭВМ 11 (фиг.5) содержит дешифратор 19, формирователь адреса 20, триггер 21, четыре блока элементов И 221-224, состоящих из N элементов И каждый, два буферных запоминающих блока 231-232 и три блока элементов И 241-243, состоящих из N элементов И каждый.

Блок управления системой при возникновении неисправности одной из универсальных ЭВМ 12 (фиг.6) содержит дешифратор 25, формирователь адреса 26, триггер 27, три блока элементов И 281-283, состоящих из N элементов И, четыре блока элементов И 291-294, состоящих из N элементов И каждый, блок элементов ИЛИ 30, состоящий из N элементов, буферный запоминающий блок 31 и элемент И 32.

Блок связи всех ЭВМ системы с внешними абонентами 13 (фиг.7) содержит два дешифратора 331-355, триггер 34, пять элементов ИЛИ 351-355, элемент НЕ 36, шестнадцать блоков элементов И 371-3716, состоящих из N элементов И каждый, и пять блоков элементов ИЛИ 381-385, состоящих из N элементов И каждый.

Блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ 14 (фиг.8) содержит дешифратор 39, формирователь адреса 40, триггер 41, три элемента И 421-423, восемь блоков элементов И 431-438, состоящих из N элементов И каждый, и блок элементов ИЛИ 44.

Блок управления системой при возникновении неисправности в ОП 15 (фиг.9) содержит дешифратор 45, триггер 46, десять блоков элементов И 471-4710, состоящих из N элементов И каждый, и два блока элементов ИЛИ 481-482, состоящие из N элементов ИЛИ.

Система (фиг.1 - Фиг.9) содержит пять электронных вычислительных машин (ЭВМ) 1, 3 и 4, три канала ввода-вывода 6, три внешних абонента 5 и устройство управления 2, причем соответствующие входы входы-выходы ЭВМ соединены шинами с соответствующими входами-выходами устройства управления, блок 7 основной общей памяти (ОП) и блок 8 резервной ОП, соответствующие входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, первые три ЭВМ используются как универсальные 11-13, четвертая ЭВМ используется в качестве управляющей 4, а пятая ЭВМ 5 является резервной, входы-выходы каждого соответствующего абонента соединены шинами входами-выходами соответствующего канала ввода-вывода, входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления 2, причем устройство управления 2 содержит два блока элементов ИЛИ 91-92, блок 10 элементов ИЛИ, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блок 13 связи всех ЭВМ системы с внешними абонентами, блок 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок 15 управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ 161-164, с первого по тридцать третий входы устройства соединены соответственно с первого по тридцать третий входы первого блока элементов ИЛИ 91, с тридцать четвертого по шестьдесят восьмой входы устройства соединены соответственно с первого по тридцать пятый входы второго блока элементов ИЛИ 92, с первого по четвертый выходы первого блока элементов ИЛИ 91 соединены соответственно с первого по четвертый входами блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, пятый вход которого соединен с выходом блока 10 элементов ИЛИ, второй вход блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ соединен с объединенными первыми входами, блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ и четвертым входом блока 13 связи всех ЭВМ системы с внешними абонентами, с пятого по двенадцатый входы первого блока элементов ИЛИ 91 соединены соответственно с шестого по тринадцатый входами блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, с тринадцатого по пятнадцатый входы первого блока элементов ИЛИ 91 соединены соответственно с третьего по пятый блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, с первого по пятый входы второго блока элементов ИЛИ 92 соединены соответственно с десятого по четырнадцатый блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, второй вход которого соединен с третьим входом блока 13 связи всех ЭВМ системы с внешними абонентами и седьмым выходом второго блока элементов ИЛИ 92, шестой выход которого соединен со вторым входом блока 13 связи всех ЭВМ системы с внешними абонентами, первый вход которого соединен с третьим входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, четвертый вход которого соединен с шестым входом блока 13 связи всех ЭВМ системы с внешними абонентами, пятый вход которого соединен с восьмым выходом второго блока элементов ИЛИ 92, с девятого по четырнадцатый выходы которого соединены соответственно с седьмого по двенадцатый входами блока 13 связи всех ЭВМ системы с внешними абонентами, с тринадцатого по пятнадцатый входы которого соединены соответственно каждый с объединенными с первого по третий входами блока 10 элементов ИЛИ, с пятого по седьмой входами блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, с четвертого по шестой входами блока 15 управления системой при возникновении неисправности в ОП и с двадцать первого по двадцать третий выходами второго блока элементов ИЛИ 92, пятнадцатый и шестнадцатый выходы которого соединены каждый соответственно с третьим и четвертым входами блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, восьмой вход которого соединен с шестым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, восьмой вход которого соединен с пятнадцатым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, восьмой вход которого соединен с седьмым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, одиннадцатый вход которого соединен с седьмым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, девятый вход которого соединен с тринадцатым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, двенадцатый вход которого соединен с шестым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый вход которого соединен со вторым входом блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, девятый вход которого соединен с семнадцатым выходом второго блока элементов ИЛИ 92, с восемнадцатого по двадцатый выходы которого соединены соответственно с первого по третий входами блока 15 управления системой при возникновении неисправности в ОП, седьмой и восьмой входы которого соединены соответственно с девятнадцать четвертым и двадцать пятым выходами второго блока элементов ИЛИ 92, с первого по десятый выходы блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ соединены соответственно с двадцать девятого по тридцать восьмой выходами устройства, с тридцать девятого по сорок пятый выходы которого соединены соответственно с первого по седьмой выходами блока 15 управления системой при возникновении неисправности в ОП, с третьего по восьмой выходы блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ соединены соответственно со второго по седьмой выходами устройства, первый выход которого соединен с выходом первого элемента ИЛИ 161, второй вход которого соединен одиннадцатым выходом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, первый выход которого соединен со вторым входом второго элемента ИЛИ 162, первый вход которого соединен со вторым выходом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, первый выход которого соединен с первым входом первого элемента ИЛИ 161, выход второго элемента ИЛИ 162 соединен с восьмым выходом устройства, девятый выход которого соединен со вторым выходом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, с шестого по десятый выходы которого соединены соответственно с одиннадцатого по пятнадцатый выходами устройства, десятый выход которого соединен с четвертым выходом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, третий выход которого соединен с первым входом третьего элемента ИЛИ 163, второй вход которого соединен с первым выходом блока 13 связи всех ЭВМ системы с внешними абонентами, а выход соединен с семнадцатым выходом устройства, шестнадцатый выход которого соединен с двенадцатым выходом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый выход которого соединен с первым входом четвертого элемента ИЛИ 164, второй вход которого соединен с восьмым выходом блока 13 связи всех ЭВМ системы с внешними абонентами, а выход соединен с двадцать восьмым выходом устройства, с восемнадцатого по двадцать третий выходы которого соединены соответственно со второго по седьмой выходами блока 13 связи всех ЭВМ системы с внешними абонентами, с девятого по двенадцатый выходы которого соединены соответственно с двадцать четвертого по двадцать седьмой выходами устройства, причем первый блок элементов ИЛИ 91 содержит девять элементов ИЛИ 171-179, с первого по третий входы блока соединены соответственно с первого по третий входами первого элемента ИЛИ 171, выход которого соединен с первым выходом блока, второй выход которого соединен с четвертым входом блока, с пятого по седьмой входы которого соединены с первого по третий входами второго элемента ИЛИ 172, выход которого соединен с третьим выходом блока, с восьмого по десятый входы которого соединены с первого по третий входами третьего элемента ИЛИ 173, выход которого соединен с четвертым выходом блока, с одиннадцатого по тринадцатый входы которого соединены с первого по третий входами четвертого элемента ИЛИ 174, выход которого соединен с пятым выходом блока, четырнадцатый и пятнадцатый входы которого соединены соответственно с его шестым и седьмым выходами, с шестнадцатого по восемнадцатый входы которого соединены с первого по третий входами пятого элемента ИЛИ 175, выход которого соединен с восьмым выходом блока, с девятнадцатого по двадцать первый входы которого соединены с первого по третий входами шестого элемента ИЛИ 176, выход которого соединен с девятым выходом блока, двадцать второй, двадцать третий и двадцать четвертый входы которого соединены соответственно с десятым, одиннадцатым и двенадцатым выходами блока, с двадцать пятого по двадцать седьмой входы которого соединены с первого по третий входами седьмого элемента ИЛИ 177, выход которого соединен с тринадцатым выходом блока, с двадцать восьмого по тридцатый входы которого соединены с первого по третий входами восьмого элемента ИЛИ 178, выход которого соединен с четырнадцатым выходом блока, с тридцать первого по тридцать третий входы которого соединены с первого по третий входами девятого элемента ИЛИ 179, выход которого соединен с пятнадцатым выходом блока, причем второй блок элементов ИЛИ 92 содержит пять элементов ИЛИ 181-185, с первого по пятый входы блока соединены соответственно каждый с первого по пятый его выходами, с шестого по восьмой входы которого соединены с первого по третий входами первого элемента ИЛИ 181, выход которого соединен с шестым выходом блока, девятый вход которого соединен с седьмым выходом блока, с десятого по двенадцатый входы которого соединены с первого по третий входами второго элемента ИЛИ 182, выход которого соединен с восьмым выходом блока, с тринадцатого по пятнадцатый входы которого соединены с первого по третий входами третьего элемента ИЛИ 183, выход которого соединен с девятым выходом блока, с шестнадцатого по двадцатый входы блока соединены соответственно каждый с десятого по четырнадцатый его выходами, с двадцать первого по двадцать третий входы которого соединены с первого по третий входами четвертого элемента ИЛИ 184, выход которого соединен с пятнадцатым выходом блока, с двадцать четвертого по двадцать шестой входы которого соединены с первого по третий входами пятого элемента ИЛИ 185, выход которого соединен с шестнадцатым выходом блока, с двадцать седьмого по тридцать пятый входы блока соединены соответственно каждый с семнадцатого по двадцать пятый его выходами, причем блок управления системой при записи и считывания контрольной точки универсальных ЭВМ 11 содержит дешифратор 19, формирователь адреса 20, триггер 21, четыре блока элементов И 221-224, состоящих из N элементов И каждый, два буферных запоминающих блока 231-232 и три блока элементов И 241-243, состоящих из N элементов И каждый, выходы которых соединены соответственно с шестым, седьмым и восьмым выходами блока, первый вход которого соединен с его первым выходом, второй вход блока соединен с входом дешифратора 19, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И 241-243 и соответственно с первым, вторым и третьем входами формирователя адреса 20, выход которого соединен со вторым выходом блока, третий выход которого соединен с нулевым входом триггера 21 и четвертым входом блока, третий вход которого соединен с единичным входом триггера 21, единичный выход которого соединен с первым входом первого блока элементов И 221, второй вход которого соединен с пятым входом блока, шестой вход которого соединен с первым входом четвертого блока элементов И 224 и с третьим входом первого блока элементов И 221, выход которого соединен с входом первого буферного запоминающего блока 231, выход которого соединен с первым входом второго блока элементов И 221, выход которого соединен с четвертым выходом блока, седьмой вход которого соединен с первым входом третьего блока элементов И 223 и вторым входом второго блока элементов И 222, третий вход которого соединен с восьмым входом блока, девятый вход которого соединен с его пятым выходом, десятый вход блока соединен с вторым входом четвертого блока элементов И 224, третий вход которого соединен с выходом второго буферного запоминающего блока 231, вход которого соединен с выходом третьего блока элементов И 223, второй и третий входы которого соединены соответственно с одиннадцатым и двенадцатым входами блока, тринадцатый вход которого соединен с четвертым входом четвертого блока элементов И 224, выход которого соединен с объединенными вторыми входами первого второго и третьего блоков элементов И 241-243, причем блок управления системой при возникновении неисправности одной из универсальных ЭВМ 12 содержит дешифратор 25, формирователь адреса 26, триггер 27, три блока элементов И 281-283, состоящих из N элементов И, четыре блока элементов И 291-294, состоящих из N элементов И каждый, блок элементов ИЛИ 30, состоящий из N элементов, буферный запоминающий блок 31 и элемент И 32, выход которого соединен с четвертым выходом блока, первый вход которого соединен с входом дешифратора 25, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И 281-283 и соответственно с первым, вторым и третьем входами формирователя адреса 26, выход которого соединен с первым выходом блока, второй вход которого соединен с объединенными первыми входами первого и второго блоков элементов И 291 и 292, первым входом элемента И 32 и вторым выходом блока, третий вход которого соединен с его третьим выходом, вторым входом элемента И 32 и единичным входом триггера 27, единичный выход которого соединен с объединенными вторыми входами первого 291, второго 292, третьего 293 и четвертого 294 блоков элементов И, а нулевой вход триггера 27 соединен с четвертым входом блока и объединенными его пятым и шестым выходами, пятый вход блока соединен с объединенными вторыми входами первого 281, второго 282 и третьего 283 блоков элементов И, выходы которых соединены соответственно с седьмым, восьмым и девятым выходами блока, шестой и седьмой входы которого соединены соответственно с третьим и четвертым входами третьего блока элементов И 293, пятый вход которого соединен с четвертым входом четвертого блока элементов И 293 и восьмым входом блока, девятый и десятый входы которого соединены соответственно с четвертым и пятым входами второго блока элементов И 292, шестой вход которого соединен с четвертым входом третьего блока элементов И 293 и одиннадцатым входом блока, двенадцатый вход которого соединен с его одиннадцатым выходом, тринадцатый и четырнадцатый входы блока соединены соответственно с первым и третьим входами третьего блока элементов И 293, выход которого соединен со вторым входом блока элементов ИЛИ 30, первый вход которого соединен с выходом первого блока элементов И 291, а выход соединен с входом буферного запоминающего блока 31, выход которого соединен с объединенными третьим входом второго блока элементов И 292 и первым входом четвертого блока элементов И 294, третий вход которого соединен с пятнадцатым входом блока, а выход соединен с двенадцатым выходом блока, десятый выход которого соединен с выходом второго блока элементов И 292, причем блок 13 связи всех ЭВМ системы с внешними абонентами содержит два дешифратора 331-332, триггер 34, пять элементов ИЛИ 351-355, элемент НЕ 36, шестнадцать блоков элементов И 371-3716, состоящих из N элементов И каждый, и пять блоков элементов ИЛИ 381-385, состоящих из N элементов И каждый, первый и второй входы блока соединены соответственно с его первым и вторым выходами и первым и вторым входами первого элемента ИЛИ 351, выход которого соединен с единичным входом триггера 34, единичный выход которого соединен с объединенными вторыми входами второго 372, третьего 373, десятого 3710 и одиннадцатого 371 блоков элементов И, а нулевой выход триггера 34 соединен с объединенными первыми входами седьмого И 377, восьмого И 378, девятого И 379, четырнадцатого И 3714, пятнадцатого И 3715 и шестнадцатого И 3716 блоков элементов И, третий вход блока соединен с объединенными первым входом второго И 372, третьим входом десятого И 3710 блоков элементов И и входом элемента НЕ 36, выход которого соединен с объединенными первым входом третьего И 373, третьим входом одиннадцатого И 3711 блоков элементов И, четвертый вход блока соединен с входом первого дешифратора 331, первый, второй и третий выходы которого соединены с первыми входами соответственно второго 352, третьего 353 и четвертого 354 элементов ИЛИ, вторые входы которых соединены с соответственно с первым, вторым и третьим выходами второго дешифратора 332, вход которого соединен с пятым входом блока, шестой и седьмой входы которого соединены соответственно с его восьмым и девятым выходами и соответственно с первым и вторым входами пятого 355 элемента ИЛИ, выход которого соединен с нулевым входом триггера 34, восьмой, девятый и десятый входы блока соединены со вторыми входами соответственно первого 371, второго 372 и третьего 373 блоков элементов И, выходы которых соединены с соответствующими входами первого 381 блока элементов ИЛИ, выход которого соединен с объединенными третьими входами второго 372 и третьего 373 блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, одиннадцатый и двенадцатый входы которого соединены с первыми входами соответственно десятого 3710 и одиннадцатого 3711 блоков элементов И, выходы которых соединены соответственно с первым и вторым входами второго 382 блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого 374, пятого 375 и шестого 376 блоков элементов И, выходы которых соединены с первыми входами соответственно третьего 383, четвертого 384 и пятого 385 блоков элементов ИЛИ, вторые входы которых соединены с выходами соответственно седьмого 377, восьмого 378 и девятого 379 блоков элементов И, вторые входы которых соединены соответственно с тринадцатым, четырнадцатым и пятнадцатым входами блока, десятый одиннадцатый и двенадцатый выходы которого соединены с выходами соответственно третьего 383, четвертого 384 и пятого 383 блоков элементов ИЛИ, пятый, шестой и седьмой выходы блока соединены с выходами соответственно четырнадцатого И 3714, пятнадцатого И 3715 и шестнадцатого И 3716 блоков элементов И, вторые входы которых соединены со вторыми входами соответственно первого 371, второго 372 и третьего 373 блоков элементов И, первые входы которых соединены с выходами соответственно второго 352, третьего 353 и четвертого 354 элемента ИЛИ, причем блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ 14 содержит дешифратор 39, формирователь адреса 40, триггер 41, три элемента И 421-423, восемь блоков элементов И 431-438, состоящих из N элементов И каждый, и блок элементов ИЛИ 44, выход которого соединен со вторым входом четвертого блока элементов И 434, выход которого соединен с седьмым выходом блока, первый вход которого соединен с входом дешифратора 39, первый выход которого соединен с объединенными первыми входами первого 421 элемента И, первого 431 и шестого 436 блоков элементов И и формирователя адреса 40, второй вход которого соединен с объединенными первыми входами второго 422 элемента И, второго 433 и седьмого 437 блоков элементов И и вторым выходом дешифратора 39, третий выход которого соединен с объединенными первыми входами третьего 423 элемента И, третьего 433 и восьмого 438 блоков элементов И и третьим входом формирователя адреса 40, выход которого соединен с первым выходом блока, второй, третий и четвертый выходы которого соединены с выходами соответственно первого 421, второго 422 и 423 третьего элементов И, вторые входы которых объединены и соединены со вторым входом блока, третий вход которого соединен с его пятым выходом и единичным входом триггера 41, единичный выход которого соединен с объединенными первыми входами четвертого 434 и пятого 435 элементов И, а нулевой вход триггера соединен с объединенными четвертым входом и шестым выходом блока, пятый, шестой и седьмой входы которого соединены со вторыми входами соответственно первого 431, второго 432 и третьего 433 блоков элементов И, выходы которых соединены соответственно с первым, вторым, и третьим входами элемента ИЛИ 44, восьмой вход блока соединен с объединенными третьими входами четвертого 434 и пятого 435 элементов И, девятый вход блока соединен со вторым входом пятого 435 элемента И, выход которого соединен с объединенными вторыми входами шестого 436, седьмого 437 и восьмого 438 блоков элементов И, выходы которых соединены соответственно с восьмым, девятым и десятым выходами блока, причем блок управления системой при возникновении неисправности в ОП 15 содержит дешифратор 45, триггер 46, десять блоков элементов И 471-4710, состоящих из N элементов И каждый, и два блока элементов ИЛИ 481-482, состоящие из N элементов ИЛИ, первый вход блока соединен с его первым выходом и единичным входом триггера 46, нулевой вход которого соединен со вторым входом блока и его вторым выходом, третий вход блока соединен с входом дешифратора 45, первый выход которого соединен с объединенными первыми входами первого 471 и шестого 476 блоков элементов И, второй выход дешифратора 45 соединен с объединенными первыми входами второго 472 и седьмого 477 блоков элементов И, третий выход дешифратора 45 соединен с объединенными первыми входами третьего 473 и восьмого 478 блоков элементов И, четвертый, пятый и шестой входы блока соединены со вторыми входами соответственно первого 471, второго 472 и третьего 473 блоков элементов И, выходы которых соединены соответственно с первым, вторым и третьим входами первого 481 блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого 474 и пятого 475 блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, пятый, шестой и седьмой выходы которого соединены с выходами соответственно шестого 476, седьмого 477 и восьмого 478 блоков элементов И, вторые входы которых объединены и соединены с выходом второго 482 блока элементов ИЛИ, первый и второй входы которого соединены с выходами соответственно девятого 479 и десятого 4710 блоков элементов И, вторые входы которых соединены соответственно с седьмым и восьмым входами блока, единичный выход триггера 46 соединен с объединенными первыми входами четвертого 474 и девятого 479 блоков элементов И, а нулевой выход триггера 46 соединен с объединенными первыми входами пятого 475 и десятого 4710 блоков элементов И.

В табл. 1 представлена информация о входных, а в табл.2 - о выходных сигналах устройства управления 2.

Во время работы ВС (фиг.1) каждая универсальная ЭВМ 1 выполняет независимую программу или независимый элемент одной программы, а управляющая ЭВМ 4 отслеживает работу универсальных. В каждой универсальной машине периодически запускается диагностическая (контрольная) задача, предназначенная для определения степени загрузки процессора и памяти с заранее известным интервалом времени для ее решения и необходимого объема памяти. При нормальной работе ЭВМ, т.е. получении правильного результата диагностической задачи в течение фиксированного интервала времени, процессор каждой машины формирует внутренние сигналы соответствия правильной работы. В случае сбоя в работе любой универсальной ЭВМ, например в первой ЭВМ 11, диагностическая задача не может быть решена в заданном интервале времени или отсутствии необходимого объема памяти, следовательно, с этой ЭВМ выдаются сигналы несоответствия правильной работы. Сигналы несоответствия поступают на вход управляющей ЭВМ 4. Для обращения к управляющей ЭВМ 4 в коды команд универсальных машин вводится дополнительная команда, при появлении которой выдается сигнал обращения к управляющей машине.

Если к моменту обращения к управляющей ЭВМ 4 она не выполнила подпрограмму предыдущего обращения, то обработка нового обращения будет приниматься для выполнения после окончания обработки предыдущего обращения.

Каждая подпрограмма управляющей ЭВМ 4 начинается с команды обмена, по которой из (ЗУ) выбирается соответствующая подпрограмма обмена. Набор таких подпрограмм хранится в памяти управляющей ЭВМ 4 и предназначен для гибкого управления обменом информацией между управляющей ЭВМ 4 и другими ЭВМ системы. После каждого цикла выполнения стандартной подпрограммы и обмена информацией управляющая ЭВМ 4 переходит в исходное состояние.

В управляющей ЭВМ 4 производится определение, какая из универсальных ЭВМ к ней обратилась, и определяется тип сигнала несоответствия, который имеет свой код. В зависимости от типа сигнала несоответствия в управляющей ЭВМ 4 выбирается соответствующая подпрограмма и начинается ее выполнение. Причины, по которым может быть выдан сигнал несоответствия, могут быть разные: это неисправность ЭВМ или ее элементов; невозможность процессора универсальной ЭВМ 1 выполнять программу за определенное время; высокая загруженность общей памяти ВС 7 или 8, или памяти универсальной ЭВМ 4.

В качестве примера рассмотрим работу ВС при возникновении сигнала несоответствия, который соответствует неисправности одной из трех универсальных ЭВМ 11-13.

В этом случае три универсальные ЭВМ 1 считаются основными и решают зависимые или независимые задачи. Четвертая ЭВМ.3 является универсальной резервной ЭВМ. Универсальная резервная ЭВМ, резервная ЭВМ 3, находится в режиме горячего резерва. В каждый момент времени все внешние абоненты 51-53 подключены к работающим ЭВМ 11-13.

В ходе работы системы по мере необходимости (необходимость определяется конкретным алгоритмом работы системы) в каждой универсальной ЭВМ 1 через определенные заданные промежутки времени выполняется контрольная точка (КТ), т.е. сохранение промежуточных результатов выполнения программы. Результаты выполнения программы на данный момент времени каждой универсальной ЭВМ 1 запоминаются и поступают через устройство управления 2 в память управляющей ЭВМ 4. Это позволяет в любой момент времени вернуться к выполнению прерванной программы на момент последнего запомненного в КТ.

Сигнал записи в КТ (Фиг.2…Фиг.5) с выхода, например, первой универсальной ЭВМ 11 поступает на первый вход устройства управления 2 и далее через блок элементов ИЛИ 91 на первый вход поступает сигнал запроса на запись КТ в память управляющей ЭВМ 4 блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ (Фиг.5). На его второй вход поступает номер универсальной ЭВМ (в данном случае первой универсальной ЭВМ 11), которая обратилась к управляющей ЭВМ для записи информации КТ, а на третий вход - сигнал готовности универсальной ЭВМ для передачи информации КТ. Сигнал запроса на запись КТ в память управляющей ЭВМ 4 поступает на первый выход блока и далее через первый выход устройства управления системой 2 на вход управляющей ЭВМ 4 для осуществления подготовки к приему информации по КТ. Номер первой универсальной ЭВМ 11 поступает со второго выхода блока на вход дешифратора 19, а с его выходов на входы формирователя адреса 20. В формирователе адреса 20 формируется начальный адрес в памяти управляющей ЭВМ 4, соответствующей номеру универсальной ЭВМ 11, который поступает через восьмой выход устройства управления системой 2 на вход управляющей ЭВМ 4. Сигнал готовности первой универсальной ЭВМ 11 для передачи информации КТ поступает на единичный вход триггера 21 и устанавливает его в единичное состояние. Сигнал с единичного выхода триггера 21 поступает на первые входы первого блока элементов И 221, на второй и третий входы которого поступают соответственно информация КТ с пятого входа и синхроимпульсы первой универсальной ЭВМ 11 с шестого входа. По сигналам синхроимпульсов первой универсальной ЭВМ 11 информация КТ записывается в первый буферный запоминающий блок 231.

По окончании записи информации КТ в первый буферный запоминающий блок 231 с четвертого входа блока поступает сигнал окончания передачи информации первой универсальной ЭВМ 11 для передачи информации КТ. Этот сигнал поступает на выход блока и устанавливает триггер 21 в нулевое состояние. Запись информации в первый буферный запоминающий блок 231 прекращается и по готовности управляющей ЭВМ 4 может быть передана в ее память. Сигнал готовности управляющей ЭВМ для приема информации КТ с с восьмого входа блока поступает на третий вход второго блока элементов И 222, на первый вход которого поступает информация КТ с выхода буферного запоминающего блока 231, а на его третий вход с седьмого входа синхроимпульсы управляющей ЭВМ 4. По сигналам синхроимпульсов управляющей ЭВМ 4 информация КТ через третий выход устройства управления системой 2 записывается по соответствующему адресу в память управляющей ЭВМ 4.

Сигнал сбоя, например, от первой универсальной ЭВМ 11, который поступает на шестнадцатый вход устройства управления системой 2 и далее через первый блок элементов ИЛИ 91 на девятый вход и пятый выход блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, поступает на четвертый выход устройства управления системой 2, а с него на вход управляющей ЭВМ 4. По сигналу готовности управляющей ЭВМ 4 к выдаче информации КТ, который через первый блок элементов ИЛИ 91 поступает на двенадцатый вход блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ и далее на третий вход третьего блока элементов И 223, на первый и второй входы которого поступают соответственно синхроимпульсы и информация КТ от управляющей ЭВМ 4. По сигналам синхроимпульсов управляющей ЭВМ 4 информация КТ записывается во второй буферный запоминающий блок 232.

Сигналы окончания выдачи информации управляющей ЭВМ 4 во второй буферный запоминающий блок 232 готовности первой универсальной ЭВМ 11 для приема информации КТ и ее синхроимпульсам, которые с соответствующих выходов первого блока элементов ИЛИ 91 устройства управления системой 2 поступают соответственно на тринадцатый, десятый и шестой входы блока и далее на соответственно четвертый, второй и первый входы четвертого блока элементов И 224. По этим сигналам информация с выхода второго буферного запоминающего блока 232 выдается через пятый выход устройства управления системой 2 на вход первой универсальной ЭВМ 11.

При записи информации КТ или ее выдаче для второй универсальной ЭВМ 12 или третьей универсальной ЭВМ 13 процесс в блоке 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ происходит одинаково. Отличием является только номер универсальной ЭВМ. Так при выдаче информации из памяти управляющей ЭВМ 4 на вход соответствующей универсальной ЭВМ определяется дешифратором 19 и блоками элементов И 241-243.

При возникновении неисправности одной из универсальных ЭВМ 1i сигнал несоответствия «неисправность_i», где i равно номеру ЭВМ, выдается с выхода этой ЭВМ на вход устройства управления системой 2. В устройства управления системой 2 производится определение неисправной ЭВМ, и сигнал несоответствия «неисправность_i» с его выхода поступает на вход управляющей ЭВМ 4.

При поступлении на вход управляющей ЭВМ 4 сигнала несоответствия «неисправность_i» управляющая ЭВМ 4 определяет факт неисправности i-й универсальной ЭВМ 1i и время поступления сигнала и приостанавливает ее работу.

Далее устройство управления системой 2, проверяет, занята или нет универсальная резервная ЭВМ 3. Если универсальная резервная ЭВМ 3 не занята выполнением программы, то управляющая ЭВМ 4 производит считывание из памяти данных последней КТ и через устройство управления системой 2 передает их в универсальную резервную ЭВМ 3 вместе с сигналом начала работы по выполнению программы.

Одновременно в устройстве управления системой 2 формируется сигналы, которые посредством управления каналом ввода-вывода переключают внешний абонент от неисправной ЭВМ 1i на универсальную резервную ЭВМ 3. После подключения универсальной резервной ЭВМ 3 канал ввода-вывода переходит в режим приема и передачи информации. Передача информации между универсальной резервной ЭВМ 3 и управляющей ЭВМ 4 происходит до тех пор, пока канал ввода-вывода не выдаст сигнал окончания обмена. Межмашинный обмен проходит, как правило, в монопольном режиме, начинается управляющей ЭВМ 4 по команде "Начать ввод-вывод". В этой команде указывается адрес одного из направлений канала ввода-вывода. После окончания обмена универсальная резервная ЭВМ 3 начинает работать с поступлением импульса пуска.

Если универсальная резервная ЭВМ 3 занята выполнением программы, то роль универсальной резервной ЭВМ 3 берет на себя управляющая ЭВМ 4. В этом случае межмашинный обмен не производится, а только осуществляется перенастройка каналов передачи информации с управляющей ЭВМ 4.

В дальнейшем универсальная резервная ЭВМ 3 или управляющая ЭВМ 4 работает как основная, а неисправная универсальная ЭВМ 1i переходит в режим поиска неисправности и ремонта.

Таким образом, несмотря на выход из строя одной ЭВМ 1i система продолжает выполнять свои функции, обмен информацией ведется между всеми необходимыми внешними абонентами 5i и ЭВМ 1i системы.

При возникновении неисправности одной из универсальных ЭВМ 1i управляющие и информационные сигналы в блоки 12 управления системой при возникновении неисправности одной из универсальных ЭВМ и 13 связи универсальных ЭВМ 1i системы с внешними абонентами (Фиг.6 и Фиг.7), поступающие через входы и выходы устройства управления системой 2 (Фиг.2…Фиг.4).

Сигнал неисправности и номер, например, первой универсальной ЭВМ 11, одновременно поступает соответственно на третий и первый входы блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ и на первый и четвертый входы блока 13 связи универсальных ЭВМ 1i системы с внешними абонентами. Сигнал номера первой универсальной ЭВМ 11, которая обратилась к управляющей ЭВМ 4 с первого входа блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ (Фиг.6), поступает на вход дешифратора 25, а с его выходов на входы формирователя адреса 26. В формирователе адреса 26 формируется начальный адрес в памяти управляющей ЭВМ 4, соответствующей номеру первой универсальной ЭВМ 11, который с первого выхода блока поступает на вход управляющей ЭВМ 4. Сигнал неисправности первой универсальной ЭВМ 11 поступает с третьего входа блока на его третий выход и далее на вход управляющей ЭВМ 4, а также на единичный вход триггера 27 и устанавливает его в единичное состояние. При поступлении сигнала неисправности на вход управляющей ЭВМ 4 с ее выхода на пятый вход блока выдается сигнал останов/пуск универсальной ЭВМ 1i, который поступает на вторые входы блоков элементов И 281-283, на первые входы которых поступают сигналы с выхода дешифратора 25. В зависимости от номера неисправной универсальной ЭВМ (в данном случае первой универсальной ЭВМ 11) сигнал останов/пуск выдается на седьмой выход блока и далее на вход первой универсальной ЭВМ 11. Первая универсальная ЭВМ 11 останавливается. Затем производится проверка, занята или нет универсальная резервная ЭВМ 3. Если универсальная резервная ЭВМ 3 не занята выполнением программы, то на второй вход и далее на второй выход блока выдается сигнал о том, что универсальная резервная ЭВМ 3 не занята выполнением программы. Этот сигнал со второго выхода поступает на вход управляющей ЭВМ 4, а также на первые входы элемент И 32 первого и второго блока элементов И 291 и 292. Для обеспечения выполнения программы неисправной первой универсальной ЭВМ 11 на универсальной резервной ЭВМ 3 необходимо в ее память загрузить информацию из памяти управляющей ЭВМ 4 по последней КТ. Информация из памяти управляющей ЭВМ 4 по последней КТ поступает с седьмого входа блока на четвертый вход первого блока элементов И 291, на второй вход которого поступает сигнал с единичного выхода триггера 27, а на пятый вход - синхроимпульсы управляющей ЭВМ 4. Как только управляющая ЭВМ 4 будет готова к выдаче информации, с шестого входа блока на третий вход первого блока элементов И 291 поступит сигнал готовности управляющей ЭВМ 4 для выдачи информации в буфер для универсальной резервной ЭВМ 3. По сигналам синхроимпульсов управляющей ЭВМ 4 информация КТ через блок элементов ИЛИ 30 записывается в буферный запоминающий блок 31. После окончания выдачи информация КТ на девятый вход блока поступает сигнал окончания выдачи информации в буфер из управляющей ЭВМ 4, который поступает на четвертый вход второго блока элементов И 292, на пятый и шестой входы которого поступают с входов блока соответственно сигналы готовности универсальной резервной ЭВМ 3 для приема информации КТ и синхроимпульсов универсальной резервной ЭВМ 3. На второй вход второго блока элементов И 292 поступает сигнал с единичного выхода триггера 27, а на его третий вход поступает информация с выхода буферный запоминающий блок 31. По этим сигналам информация с выхода буферного запоминающего блока 31 выдается на вход универсальной резервной ЭВМ 3. Так как на второй вход элемента И 32 с третьего входа блока поступает сигнал неисправности универсальной ЭВМ, то после приема информации КТ на четвертый выход блока выдается сигнал пуск универсальной резервной ЭВМ 3. Универсальная резервная ЭВМ 3 запускается на выполнение программы.

В процессе работы универсальной резервной ЭВМ 3 по мере необходимости через определенные заданные промежутки времени выполняется контрольная точка (КТ), т.е. сохранение промежуточных результатов выполнения программы. Результаты выполнения программы на данный момент времени универсальной резервной ЭВМ 3 запоминаются и аналогичным, как при работе универсальной ЭВМ 1i, через третий блок элементов И 293, блок элементов ИЛИ 30, буферный запоминающий блок 31 и четвертый блок элементов И 294 блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ (Фиг.6) поступают в память управляющей ЭВМ 4.

Кроме того, при возникновении неисправности универсальной ЭВМ 1i необходимо переключить внешний абонент 5i от неисправной ЭВМ 1i на универсальную резервную ЭВМ 3. Для осуществления возможности переключения внешнего абонента 5i сигнал неисправности и номер, например, первой универсальной ЭВМ 11 поступает соответственно на первый и четвертый входы блока 13 связи универсальных ЭВМ 1i системы с внешними абонентами (Фиг.7). При этом, если универсальная резервная ЭВМ 3 не занята выполнением программы, то на третий вход блока поступает сигнал о том, что резервная ЭВМ не занята выполнением программы. Сигнал номера первой универсальной ЭВМ 11, которая неисправна, с четвертого входа блока поступает на вход первого дешифратора 331, с выходов которого поступают на вторые входы соответственно второго 352, третьего 353 и четвертого 354 элементов ИЛИ, а с их выходов на первые входы соответственно с первого по третий 371-373 блоков элементов И. Вторые входы с первого по третий 371-373 блоков элементов И подключены к информационным входам с первого по третий внешних абонентов 51-53. Таким образом, в зависимости от того, какая универсальная ЭВМ 1i неисправна (в данном случае первая), информационный вход абонента с таким номером будет подключен к универсальной резервной ЭВМ 3. Информация от первого внешнего абонента 51 с восьмого входа блока поступает через открытый первый блок элементов И 371 и первый блок элементов ИЛИ 381 на третьи входы второго 372 и третьего 373 блоков элементов И, на вторые входы которых поступает сигнал с единичного выхода триггера 34. На единичный вход триггера 34 поступает через первый элемент ИЛИ 351 сигнал неисправности универсальной ЭВМ 11. На первый вход второго 372 блока элементов И с третьего входа блока поступает сигнал о том, что универсальная резервная ЭВМ 3 не занята выполнением программы, а на первый вход третьего 373 блоков элементов И поступает через элемент НЕ 36 инверсный сигнал о том, что универсальная резервная ЭВМ 3 не занята выполнением программы, т.е. универсальная резервная ЭВМ 3 занята выполнением программы. В этом случае информация от первого внешнего абонента 51 через открытый второй 372 блок элементов И поступает на третий выход блока и далее на вход универсальной резервной ЭВМ 3.

Если универсальная резервная ЭВМ 3 окажется занятой выполнением программы, то будет открыт по первому входу третий 373 блок элементов И и информация от первого внешнего абонента 51 будет поступать на четвертый выход блока и далее на вход управляющей ЭВМ 4.

Информация, полученная в результате выполнения программы в универсальной резервной ЭВМ 3 или управляющей ЭВМ 4, которая поступает соответственно с одиннадцатого и двенадцатого выходов блока, поступает на первые входы соответственно десятого 3710 и одиннадцатого 3711 блоков элементов И, вторые входы которых объединены и подключены к единичному выходу триггера 34. Если универсальная резервная ЭВМ 3 не занята, то по третьем входам оказывается открытым десятый 3710 блок элементов И, а одиннадцатый 3711 блок элементов И окажется закрытым. Информация от универсальной резервной ЭВМ 3 через открытый десятый 3710 блок элементов И и второй блок элементов ИЛИ 382 поступает на вторые входы с четвертого 374 по шестой 376 блоков элементов И, один из которых (в данном случае четвертый, так как неисправна первая универсальная ЭВМ 11) сигналом с первого выхода первого дешифратора 331 через второй элемент ИЛИ 352 оказывается открытым. С выхода четвертого 374 блока элементов И через третий блок элементов ИЛИ 383 информация поступает на десятый выход блока и далее на вход первого внешнего абонента 51.

Если универсальная резервная ЭВМ 3 занята, то оказывается открытым одиннадцатый 3711 блок элементов И, а десятый 3710 блок элементов И будет закрытым. Информация от управляющей ЭВМ 4 через открытый одиннадцатый 3711 блок элементов И поступает на второй блок элементов ИЛИ 382 и далее на десятый выход блока и на вход первого внешнего абонента 51.

После устранения неисправности сигналом исправности универсальной ЭВМ через пятый элемент ИЛИ 351 триггер 34 устанавливается в нулевое состояние. Второй 372, третий 373, десятый 3710 и одиннадцатый 3711 блоки элементов И окажутся закрытыми, с седьмого по девятый 377-379 и с четырнадцатого по шестнадцатый 3714-3716 будут открытыми. Через открытые блоки элементов И информационные входы внешних абонентов 51-53 будут соединены с информационными входами соответствующих универсальных ЭВМ 11-13.

Работа ВС при возникновении сигнала несоответствия, который соответствует нештатной ситуации в работе одной из универсальных ЭВМ 1i, которое наиболее вероятно может быть вызвано перегрузкой, связанной например с недостаточностью памяти или времени выполнения заданной программы

При уменьшении загрузки памяти сигнал «перегрузка» выдаваться не будет, аналогичным образом управляющая ЭВМ 4 через устройство управления 2 восстановит данные памяти i-й универсальной ЭВМ 1i и работа ее продолжится в штатном режиме.

Перегрузка универсальной ЭВМ 1i может определяться внешним абонентом 5i. Например, внешний абонент 5i в процессе функционирования подсчитывает время выполнения программы по его запросу или превышение предельно допустимого количества стоящих в очереди на выполнение запросов. Эти сигналы от внешних абонентов 5i поступают через устройство управления 2 на вход управляющей ЭВМ 4, которая контролирует состояние ВС.

В этом случае часть функций по обработке и получении результатов при выполнении программы универсальной ЭВМ 1i принимает универсальная резервная ЭВМ 3 или управляющая ЭВМ 4, если универсальная резервная ЭВМ 3 занята.

В любом случае сигнал перегрузки универсальной ЭВМ 1i поступает на второй вход блока 13 связи всех ЭВМ системы с внешними абонентами (Фиг.7), а на пятый вход - номер перегруженной универсальной ЭВМ 1i. Работа ВС в случае выдачи сигнала перегрузки универсальной ЭВМ 1 или устранения перегрузки универсальной ЭВМ 1i, поступающего на седьмой вход блока, выполняется аналогично выдаче сигналов неисправности универсальной ЭВМ и исправности универсальной ЭВМ. Отличие заключается в том, что при перегрузке задействуется второй дешифратор 332 и первый 351 и пятый 352 элементы ИЛИ (Фиг.7).

При работе одной из универсальных ЭВМ 1i может быть выдан сигнал несоответствия, который соответствует нештатной ситуации в работе ЗУ, которое наиболее вероятно может быть вызвано перегрузкой, связанной, например, с недостаточностью памяти или ее неисправностью.

Сигнал неисправность ЗУ универсальной ЭВМ поступает на третий вход и далее на пятый выход блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ (Фиг.8). Сигнал с пятого выхода блока поступает на вход управляющей ЭВМ 4. По этому сигналу управляющая ЭВМ 4 определяет факт нештатной ситуации в работе, время поступления сигнала, от какой универсальной ЭВМ 1i поступил сигнал и выдает команду проверки работоспособности блоком ЗУ путем их самоконтроля. Так как заранее в заданные промежутки времени выполняется КТ, то управляющая ЭВМ 4 производит считывание из памяти данных последней КТ и через устройство управления 2 передает их в ОП ВС. Устройство управления 2 переключает данную универсальную ЭВМ 1i на работу с ОП и осуществлять ее пуск, если при этом выполнение программы было приостановлено. На время проверки работоспособности ЗУ данная i-я универсальная ЭВМ 1i переключается на работу с общей памятью (ОП) ВС через буфер БУ (в ОП обычно предусматривается резервная зона для этого случая).

Самоконтроль отказавшего ЗУ осуществляется путем считывания одной и той же информации сначала в первом цикле из одной секции, а через некоторое время в другом цикле из другой секции. Считанная информация поступает в блок формирования сигнала ошибки памяти для сравнения.

В этом случае возможны два варианта функционирования системы. В первом варианте считанная в разное время и из разных секций информация совпадает (фактически произошел сбой). На выходе формируется сигнал «отсутствия ошибки», который поступает на вход управляющей ЭВМ 4.

Если же считанная в разное время и из разных секций информация не совпадает, то выдается сигнал «ошибка». Этот сигнал поступает на вход управляющей ЭВМ 4. Этот сигнал с выхода к управляющей ЭВМ 4 поступает на пятьдесят четвертый, пятьдесят пятый или пятьдесят шестой (в зависимости от того, в какой из универсальных ЭВМ 1i оказалось неисправным ЗУ) входы устройство управления системой 2 и далее на третий вход блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ.

Одновременно с сигналом неисправности ЗУ универсальной ЭВМ на первый вход блока поступает сигнал номера неисправности ЗУ универсальной ЭВМ 1i. Номер первой универсальной ЭВМ 11 (допустим, неисправность ЗУ произошла в первой универсальной ЭВМ 11) поступает с первого выхода блока на вход дешифратора 39, а с его выходов на входы формирователя адреса 40. В формирователе адреса 40 формируется начальный адрес в блоке 7 основной ОП, соответствующей номеру универсальной ЭВМ 11. Кроме того, выходы дешифратора 39 подключены к первым входам соответствующих с первого по третий блоков элементов И 431-433, вторые входы которых соединены с соответствующими информационными входам универсальной ЭВМ 1i. Первый блок элементов И 431 оказывается открытым по первому входу, и информация от первой универсальной ЭВМ 11 поступает через блок элементов ИЛИ 44 на вторые входы четвертого блока элементов И 431. Четвертый блок элементов И 431 оказывается открытым по первым входам с единичного выхода триггера 41, который был установлен в единичное состояние сигналом неисправности ЗУ универсальной ЭВМ с третьего входа блока. По синхросигналам первой универсальной ЭВМ 11, поступающим с восьмого входа блока на третьи входы четвертого блока элементов И 431, информация от нее передается на седьмой выход блока и далее на вход блока 7 основной ОП.

Передача информации с выхода блока 7 основной ОП в первую универсальной ЭВМ 11 осуществляется по синхроимпульсам через открытые пятый и шестой блоки элементов И 435 (Фиг.8).

После устранения неисправности на четвертый вход блока поступает сигнал исправности ЗУ универсальной ЭВМ, который устанавливает триггер 41 в нулевое состояние. Четвертый 434 и пятый 435 блоки элементов И будут закрыты по первым входам, и информация через них приниматься и выдаваться не будет, ВС будет работать в штатном режиме.

На время переключения на работу с блоком 7 основной ОП универсальная ЭВМ 1i останавливается по сигналу останов/пуск универсальной ЭВМ, который поступает на вторые входы с первого по третий элементов И 421-423, на первые входы которых поступают сигналы с соответствующих выходов дешифратора 39. После выполнения переключения аналогичным образом осуществляется пуск универсальной ЭВМ 1i.