чен к первым входам десятого, двенадцатого и четырнадцатого элементов И, выходы второго, четвертого и десятого элементов И подключены к входам третьего элемента ИЛИ, выход которого подключен к первому выходу устройства, выходы шестого и двенадцатого элементов И соединены с входами шестого элемента ИЛИ,выход которого подключен к второму выходу устройства, выходы восьмого и четырнадцатого элементов И подключены к входам девятого элемента ИЛИ, выход которого соединен с третьим выходом устройства.

2. Устройство по п. 1, отличающееся тем, что каждый узел контроля содержит второй, третий и четвертый регистры входы которых соединены с входом узла, выходы второго и третьего регистров подключены к первому и второму входам модульного

сумматора соответственно, выход которого подключен к первому входу элемента сравнения, к второму входу которого подключен выход четвертого регистра, выход элемен-

.та сравнения подключен к выходу узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2533688C1 |

| Процессор ввода-вывода | 1983 |

|

SU1149240A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| Процессор | 1981 |

|

SU962964A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| КОНТРОЛЛЕР | 1999 |

|

RU2166205C2 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для приема и передачи информации в кольцевом канале связи | 1990 |

|

SU1774363A1 |

| Устройство для синхронизации координатных пультов ввода информации | 1982 |

|

SU1045238A1 |

1. УСЛ-РОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ РЕЗЕРВА, содержащее три основных и один резервный блок, три узла контроля основных блоков , |узел контроля резервного блока и ком:мутатор, первые входы первого,второ- . го и третьего основных и резервного блоков соединены соответственно с входами узлов контроля первого, второхчэ и третьего основных и резервного блоков, вторые выходы - соответственно с первым, вторым, третьим и четвертым входами коммутатора, о т л и н а ю щ е а с я тем, что, с целью повышения надежности в него введены первый регистр, дешифратор, первый элемент ИЛИ, а коммутатор содержит с первого по четырнадцатый элементы И и со второго по одиннадцатый эле- менты ИЛИ, вьходы узлов контроля основных и резервного блоков подключены к входам первого регистраj выход которого соединен с входом дешифратора, нулевой - шестой выходы дешифратора соединены с входами второго элемента ИЛИ, выход которого подклю-чен к вторым входам первого и второго элементов И, девятый выход дешифратора подключен к вторым входам третьего и четвертого элементов И,нулевой - третий,: восьмой и десятый выхода дешифратора подключены к входам пятого элемента ИЛИ, выход которого подключен к вторым входам пятого и шестого элементов И, нулевой, первый, четвертый, пятый, восьмой, девятый и двенадцатый выходы дешифратора соединены с входами седьмого элемента ИЛИ, .выход которого подключен к вторым входам седьмого и восьмогоэлементов И, восьмой, десятый и двенадцатый выходы дешифратора подключены к входам восьмого элемента ИЛИ,- выход которого подключен к вторым входам девятого и десятого элементов И, четвертый и шестой выходы дешифратора соединены с входами одиннадцатого элемента ИЛИ, выход которого подключен к вторым входам одиннадцатого и двенадцатого элементов И, седьмой, одиннадцатый и тринадцатый - пятн дцатый выходы дешифратора подключены к входам первого элемента ИЛИ, выход которого соединен с 1Л1ной отказа, первый вход устройства подклк1чен к первым входам первого, третьего и девятого элементов И, второй вход к nepBiJM входам пятого и одиннадцатого элементов И, третий вход - к первым входам седьмого и тринадцатого элеMe.iToB И, выход первого элемента И 1 подключен к входу первого основного блока, второй выход которого подклюDO 4 чен к первому входу второго элемента И, выходы третьего и пятого элементов И подключены к входам четвертого элемента ИЛИ, ыход которого подключен к входу второго основного бло.ка, второй выход которого соединен с первыми входами четвертого и шестого элементов И, выход седьмого элемента И подключен к входу третьего основного, блока, второй выход которого подключен .к первому входу восьмого элемента И, Bfcixojuj девятого, одиннадцатого и тринадцатого элементов И подключены к входам десятого элемента ИЛИ, выход которого соединен с-входом резервного блока, второй выход которого подклю

1

Изобретение относится к автоматик и вычислительной технике и может найти применение при построении систем высокой надежности.

Известно устройство для управлени переключением резерва, содержащее блоки резервируемой системы, элементы ИЛИ,схемы несовпадения, входы которых подключены непосредственночерез элемент ИЛИ к выходам резервируемых блоков, а выходы - к входам элементов И, вторые входы которых подсоединены через переключатели к шинам питания соответствующих резервируемых блоков Cll.

Недостаток этого устройства невозможность одновременного использования работающей пары блоков для переработки различной информации.

Известно также устройство, содержащее устройство управления конфигуратором, соединенное с подсхемой конфигурационной коммутации, подключенные к выходам резервные и основные подсистемы, позволяйщее осуществлять резервирование основных подсистем СзНедостаток устройства состоит в отсутствии возможности поддержания работоспособности системы за счет перераспределения основных подсистем при полном использовании резервных подсистем.

Наиболее близким техническим решением к предлагаемому является устройство для управления переключением скользящего резерва, содержащее элементы контроля основных блоков, инверторы, элементы И-НЕ, элементы контроля резервных блоков, выходы которых подключены через инверторы или непосредственно к входам элементов И-НЕ столбцов матригцл. Выходы элементов контроля непосредственно или через инвертор подключены к входам элементов И-НЕ строк матрицы.

выходкаждого элемента И-НЕ соединен с коммутатором и входами всех элементов И-НЕ, состоящих вобщих с этим элементом строке и столбце матрицы, число входов каждого элемента И-НЕ равно сумматорному числу основных и резервных блоков

Недостаток данного устройства - низкая надежность резервированной системы.

Известно, что в резервированных системах, допускающих работу с пониженной эффективностью, с целью повышения надежности их функционирования отказавшие наиболее важные элементы системы заменяют после исчерпания резерва аналогичными исправными элементами, играющими менее важную роль (элементы, подлежащие замене, называ,ются приоритетными). Надежное функ.ционирование таких систем с пониженн эффективностью, позволяющей применят ИХ по целевому назначению, обеспечивается наличием в составе системы исправного приоритетного блока и минимальным количеством (не равным нулю) бесприоритетных блоков. Например в мультипроцессорных резервированных вычислительных системах с централизованным управлением для реализации управляющих программ операционной системы выделяется специальный процессор, являющийся для системы приортетным.

Цель изобретения - повышение надежности резервированной системы.

Поставленная цель достигается тем, что в устройство для управления переключением резерва, содержащее три основных и один резервный блок, три узла контроля основных блоков, узел контроля резервного блока и коммутатор, первые выходы первого, второго и третьего основных и резервного блоков соединены.соответственно с входами узлов контроля первого, второго и третьего основных и резервного Олоков, вторые выходи - соответственно с первым, вторым, третьим и четвертым входами коммутатора, дополнительно введены первый регистр, дешифратор, первый элемент ИЛИ, а коммутатор содержит четырнадцать элементов И и десять элементов ИЛИ, выходы узлов контроля основных и резервного блоков подключены к входам первого регистра, выход которого соединен с входом дешифратора, нулевой - шестой выходы дешифраторасоединены с входами второго элемента ИЛИ, выход которого подключен к вторьлм входам первого и второго элементов И, девятый выход дешифратора подключен к вторым входам третьего и четвертого элементов И, выходы с нулевого по третий, восьмой и десятый дешифратора подключены к входам пятого и шестого элементов И, нулевой, первый, четвертый, пятый, восьмой, девятый и двенадцатый выходы дешифратора соединены с входами седьмого элемента ИЛИ, выход которого подключен к вторым входам седьмого и восьмого элементов И, восьмой, десятый и двенадцатый выходы дешифратор подключены к входам восьмого элемента ИЛИ, выход которого подключен к вторым входам девятого и десятого эле.ментов И/ четвертый и шестой выходы дешифратора.соединены с входами одиннадцатого элемента ИЛИ, выход которог подключен к вторым входам одиннадцатого и двенадцатого элементов И, седьмой одиннадцатый, тринещцатый - пятнадцатый выходы дешифратора подключены к входам первого элемента ИЛИ, выход которого соединен с шиной отказа, первый вход устройства подключен к первым входам первого, третьего и девятого элементов И, второй вход к первьм входам пятого и одиннадцатого элементов И, третий вход - к первым входам седьмого и тринадцатого элег-юнтов И, выход первого элемента И подключен ко входу первого основного блока, второй выход которого .подключен к первому входу второго элемента И, выходы третьего и пятого элементов И подключены к входам четвертого элемента ИЛИ, выход которого подключен к входу второго основного блока, второй выход которого соединен с первыми входами четвертого и шестого элементов И, выход седьмого элемента И подключен к входу третьег основного блока, второй выход которого подключен к первому входу восьмого элемента И, выходы девятого, одиннадцатого и тринадцатого элементов И подключены к входам десятого элемента ИЛИ, выход которого соедине с входом резервного блока, второй выход которого подключен к первым входам десятого, двенадцатого и четырнадцатого элементов И, выходы второго, четвертого и десятого элементов И подключены к входам третьего элемента ИЛИ, выход которого подключен к первому выходу устройства, выходы шестого и двенадцатого элементов И соединены с входами шестого элемента ИЛИ, выход которого подключен к второму выходу устройства, выходы восьмого и четырнадцатого элементов И подключены к входам девятого элемента ИЛИ, выход которого соединен с третьим выходом устройства.

Кроме того, каждый узел контроля содержит второй, третий и четвертый регистры, входы которых соединены с входами узла, выходы второго, третьего регистров подключены к первому и второму входам модульного сумматора соответственно, выход которого подключен к первому входу элемента сравнения, к второму входу которого подключён выход четвертого регистра, выход элемента сравнения подключен к выходу узла.

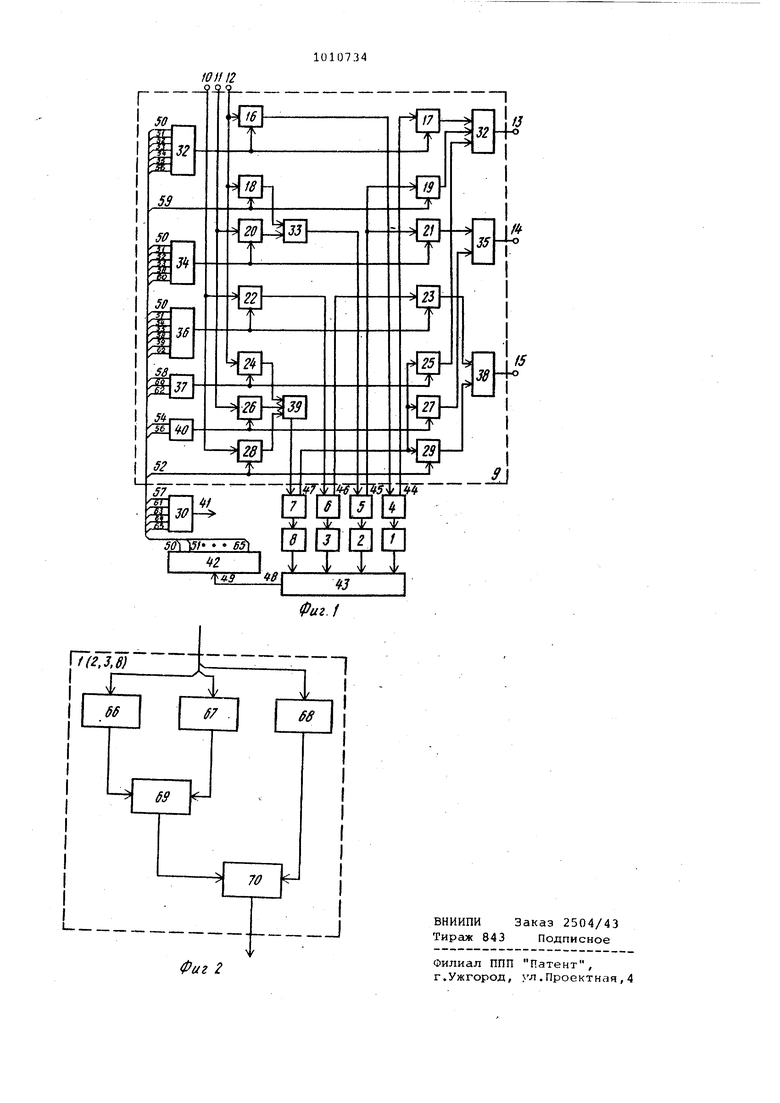

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - схема блока устройства.

Устройство {фиг.1) содержит пер- : вый - третий узлы контроля 1-3 основных блоков-, первый - третий основные блоки ,4-6 ,резервный блок 7,узел контроля 8 ре|эер.вного блок а, коммутатор 9, входы 10|12 устройства, выходы 13-15 устройства элементы первый - четырнадцатый И 1629, первый - десятый элементы ИЛИ 30-40, шину отказа 41, дешифратор 42, первый регистр 43, вторые выходы 4446 основных блоков и второй .выход 47 резервного блока, выход 48 первого регистра,вход 49 дешифратора,нулевой- пятнадцатый выходы 50-65 дешифратора.

Основные блоки 4-6 {фиг. 2) содержат второй - четвертый регистры 6668, модульный сумматор 69, элемент сравнения 70.

Принцип работы устройства состоит в том, что .ввeдej ныe регистр, дешифратор, элементы И и элементы ИЛИ обеспечивают замещение отказавшего приоритетного блока резервнь л или исправным основным после исчерпания резерва.

Устройство работает следующим об- разом.

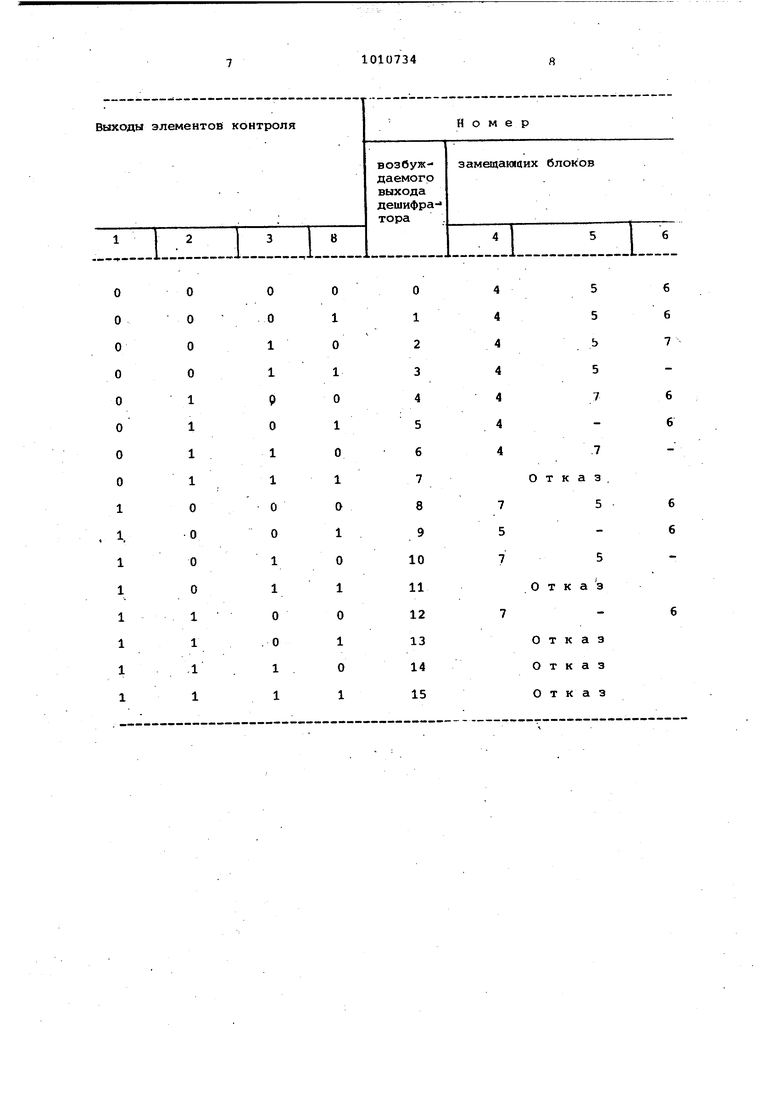

Пусть в начальный момент все ос новные блоки 4-6 и резервный блок 7 исправны. Основной блок 4 является приоритетным. При исправном состояни всех блоков на выходах узлов контрол 1-3 основных блоков и узла контроля резервного блока будут нулевые сигналы, вследствие чего регистр 43;будет находиться в нулевом состоянии. В этом случае на нулевом выходе 50 дв шифратора 42 будет единичньй сигнал, который через элементы ИЛИ 31, 34 и 36 поступает на вторые входы элемен тов и 16, 17, 20-23 и обеспечивает прохождение входных сигналов, посту пающих по входам 12, 11, 10 устройства соответственно через первый вход элемента И 16, через первый вх элемента И 20 и второй вход элемент ИЛИ 33, через первый вход.элемента И 22 на входы приоритетного блока 4 и основных 5 -и 6. Этот же сигнал с нулевого выхода 50 дешифратора 42 обеспечивает передачу сигналов с вторых выходов приоритетного блока и основных блоков 5 и б соответстве но через элементы И 17, 21, 23 и элементы ИЛИ 32, 35 и 38 на выходы 13, 14 и 15 устройства. Пусть вследствие неисправности основного блока 5 узел контроля 2 выдает единичный сигнал. Этот сигна вырабатывается, например, если блоки 4-7 являются узлами суммирования следующим образом. На регистры 66 и 67 (фиг. 2) пос тупают контрольные характеристики слагаемых, а на регистр 68. - контрольная характеристика суммы из блока 5. В результате суммирования контрольных характеристик слагаемых на модульном сумматоре получается контрольная характеристика, которая на элементе сравнения сравнивается контрольной характеристикой суммы, поступающей с,регистра 68. Вследствие неисправности блока 5 сложение в нем Проведено неправильно и контрольные xapakтepиcтики не совпадут, в результате чего на выходе элемента сравнения будет единичный сигнал который поступает на вход регистра 43. В этом случае состояние регистра 43 изменится и появится единичный еигнал на четвертом выходе 5 дешифратора 42, который через элементы ИЛИ 31, 36 и 40 поступает на вторые входы элементов И 16, 17, 22 23, 26, 27 и обеспечивает прохозвдение входных сигналов, поступающих по входам 12, 11, 10 устройства соотве ственно через первый вход элемента И 16, через первый вход элемента И 26 и второй вход элемента ИЛИ 39 через первый вход элемента И 22 на входы блоков 4,7 и 1б. Этот же сигнал с четвертого выхода 54 де .шифратора 42 обеспечивает передачу сигналов с вторых выходов приоритет ного блока 4, резервного блока 7 и основного блока 6 соответственно через элементы И 17, 27, 23 и элементы ИЛИ 32, 35 и 38 на выходы 13-15 устройства. В результате 3toro произошла замена отказавшего основного блока 5 резервным блоком 7, который теперь вьтолняет функции основного. При появлении единичного сигнала на выходе узла контроля 1 и наличии единичного сигнала на выходе узла контроля 2 регистр 43 переходит в. состояние, при котором на двенадцатом 62 выходе дешифратора 42 появляется единичныйсигнал, который поступает на вторые входы элементов ИЛИ 36 и 37, на вторые входы элементов И 22-25 и обеспечивает прохожде-. ние входных сигналов, поступающих по входам 12 и 10 устройства,/соответственно через первые входы элементов И 24 и ИЛИ 39,через первый вход элемента И 22 на входы блоков 7 и 6. Этот же сигнал с двенадцатого выхода 62 дешифратора 42 обеспечивает передачу сигналов с вторых выходов блоков 7 и 6 соответственно через элементы И 25, 23 и элементы ИЛИ 32 и 38 на выходы 13 и 15 устройства. В результате этого произошла замен.а отказавшего приоритетного блока 4 резервным блоком 7, который выполнял функции основного блока 5. Аналогичн1Ф1 образом устройство работает при отказах блоков 4 и 6, 5 и 7 и т. д. В этих случаях переключение блоков производится в соответствии с таблицей. Когда единичные сигналы появляются на выходах трех и более узлов контроля, то на одном из выходов дешифратора 42 (седьмом, одиннадцатом, тринадцатом, четырнадцатом или пятнадцатом) появляется единичный сигнал, который через элемент ИЛИ 30 поступает в шину отказа 41. Появление единичного сигнала в шине отказа 41 свидетельствует неисправности устррйства. Таким образом, устройство обеспечивает возможность перераспределения исправных основных и резервного блоков для замещения отказавшего приоритетного блока, что позволяет существенно повысить надежность резервированной системы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| С. С. КЛОПКОБ и Д. П. МельниковВСЕСОЮЗНАЯf^^TEHniO-ir;Xb/'.^--ff.^nЬИБЛИО''.--«,с ' "' | 0 |

|

SU357694A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Архитектура вычислительных комплексов | |||

| М | |||

| , Мир, 1974, с | |||

| Электрический прерыватель с воздушным охлаждением | 1923 |

|

SU566A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

Авторы

Даты

1983-04-07—Публикация

1980-10-17—Подача