второй вход которого подключен к выходу четвертого логического элемента, прямой выход третьего триггера соединен с вторым входом шестого логического элемента, выход которого подключен к первому входу тринадцатого логического элемента, второй вход которого соединен с выходом пятого логического элемента, а выход подключен к выходу Ь устройства, ин:версный выход третьего триггера соединен с вторыми входами десятого и пятого логических элементов и с К-входом первого триггера, инверсный выход четвертого триггера сое2005

динен с вторым входом первого логического элемента, третьим входом пятого логического элемента и первым входом седьмого логического элемента, выход которого подключен к .выходу а устройства, а второй вход :соединен с выходом восьмого логического элемента и подключен к выходу устройства, причем выход первого логического элемента подключен к 1-входу третьего триггера, выход второго логического элемента - к К-входу четвертого триггера и выход третьего логического элемента - к 1-входу четвертого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Счетчик импульсов с цифровой индикацией | 1987 |

|

SU1478325A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Декадный счетчик в семисегментном коде | 1987 |

|

SU1432767A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССОВ ФУНКЦИОНИРОВАНИЯ ЭКРАНОПЛАНА ПРИ ЭКСПЛУАТАЦИИ | 2016 |

|

RU2613850C1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

ДЕКАДНЫЙ СЧЕТЧИК ДЛЯ СЕМИСЕГМЕНТНЫХ ИНДИКАТОРОВ, содержащий десятичный счетчик на триггерах и первом, втором и третьем логических элементах, дешифратор, имеющий в своем составе инвертор и четвертый, пятый, шестой, седьмой, восьмой, девятый логические элементы, выходы дещифратора соединены с выходами а ,b,c,j,e,f, устройства, прямой выход первого триггера подключен к первым входам первого и второго логических элементов, прямой выход второго триггера соединен с вторым входом второго и первым входом третьего логических элементов, второй вход третьего логического элемента подключен к инверсному выходу третьего триггера, прямой выход которого соединен с первым входом четвертого логического элемента, прямой выход второго триггера подключен к второму входу четвертого и первому входу пятого логических элементов, прямой выход четвертого триггера соединен с первым входом шестого логического элемента, выходы седьмого, восьмого и девятого логических элементов подключены к выходам устройства, о тличающийся тем, что, с целью повышения надежности в работе и снижения потребляемой мощности за счет сокращения количества элементов в устройстве, в него введены десятый, одиннадцатый, двенадцатый и тринадцатый логические элементы, триггеры вьтолнены в виде IK-триггеров, тактовые входы которых подключены к входу устройства, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятьй и одиннадцатый логические элементы выполнены в виде логических элеменг тов И, двенадцатый и тринадцатый логические элементы выполнены в ви(Л де логических элементов ИЛИ, 1-вход первого триггера подключен к шине логической единицы, его прямой выход соединен с I- и К-входами второго триггера и подключен к первым входам восьмого и одиннадцатого логических элементов, инверсный выход первого триггера через инвертор соединен с выходом fi устройстт ва и подключен к первому входу девятого логического элемента, выход которого соединен с выходу -С устройства, а второй вход подключен , к выходу двенадцатого логического элемента и к .выходу f устройства, инверсный выход второго триггера соединен с К-входом третьего триггера с вторым входом восьмого логического элемента и с первым входом десятого логического элемента, выход которого подключен к выходу устройства и второму входу одиннадцатого логического элемента, выход которого соединен с первым входом двенадцатого логического элемента.

1

Изобретение относится к импульсной технике и может быть использовано п вычислительных и измерительных устройствах.

Цель изобретения - повышение надежности в работе и снижение потребляемой мощности за счет сокращения количества элементов в устройстве .

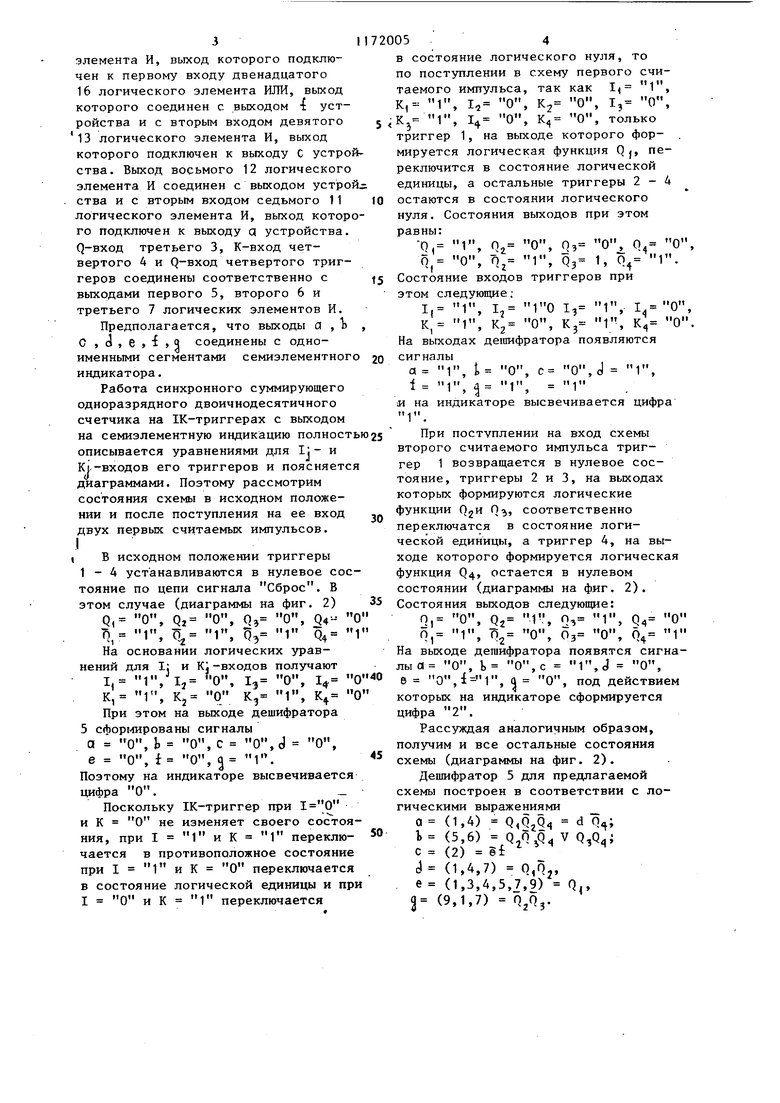

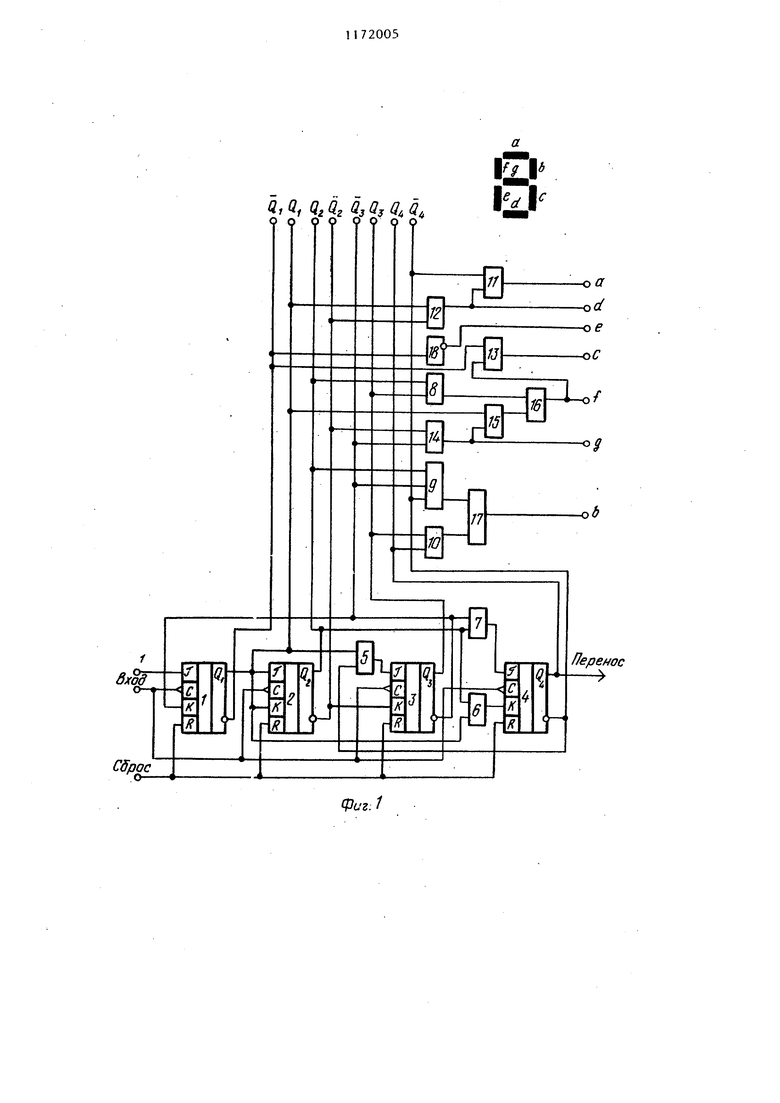

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 временные диаграммы, пояснянмцие его работу.

Устройство содержит счетчик, выполненный на первом 1, втором 2, третьем 3, четвертом 4 1К-триггерах первом 5, втором 6, третьем 7 элеметах И, и дешифратор, имеющий в своем составе четвертый 8, пятый 9, шестой 10, седьмой 11, восьмой 12, девятый 13, десятый 14, одиннадцатый 15 логические элементы И, двенадцатый 16, тринадцатьш 17 логические элементы ИЛИ и инвертор 18

Тактовые входы всех триггеров соединены с входом устройства, 1-вход первого триггера подключен к шине логической единицы, его прямой выход соединен с I- и К-входами второго триггера и подключен к первым входам первого 5, второго 6, восьмого 12 и одиннадцатого 15 логических элементов И. Инверсный выход первого триггера через инвертор 18 соединен с выходом е устройства и с первым входом девятого 13

логического элемента И. Прямой выход второго триггера 2 соединен с первым входом третьего 7, вторым входом вто рого 6, первым входом пятого 9 и вторым входом четвертого 8 логического элементов И.

Инверсный выход второго триггера соединен с К-входом третьего триггера, с первым входом десятого 14 и вторым ;входом ВОСЬМОГО 12 логических элементов И. Прямой вьгкод третьего триггера подключен к первому входу четвертого 8 и второму входу шестого 10 логических элементов И. Инверсный выход третьего триггера соединен с К-входом первого триггера, вторыми входами третьего 7, пятого 9 и десятого 14 логических элементов И.

Прямой выход четвертого 4 триггера подключен к первому входу шестого 10 логического элемента И, выход которого соединен с первым входом тринадцатого 17 логического элемента ИЖ, выход которого подключен к вькоду Ь устройства, а второй вход соединен с выходом пятого 9 логического элемента И. Инверсный выход четвертого 4 триггера соединен с вторым входом первого 5 логического элемента И, первым входом седьмого 11 и третьим входом пятого 9 логических элементов И. Выход десятого 14 логического элемента И соединен с выходом ft устройства и с вторым входом одиннадцатого 15 логического элемента И, выход которого подключен к первому входу двенадцатого 16 логического элемента ИЛИ, выход которого соединен с выходом { устройства и с вторым входом девятого 13 логического элемента И, выход которого подключен к выходу с устро ства. Выход восьмого 12 логического элемента И соединен с выходом устро ства и с вторым входом седьмого 11 логического элемента И, выход котор го подключен к выходу а устройства Q-вход третьего 3, К-вход четвертого 4 и Q-вход четвертого триггеров соединены соответственно с выходами первого 5, второго 6 и третьего 7 логических элементов И. Предполагается, что выходы d , Ь С ,о,е,4 соединены с одноименными сегментами семиэлементног индикатора. Работа синхронного суммирующего одноразрядного двоичнодесятичного счетчика на 1К-триггерах с выходом на семиэлементную индикацию полност описывается уравнениями для Ij- и К .-входов его триггеров и поясняетс диаграмма1«1. Поэтому рассмотрим состояния схемы в исходном положении и после поступления на ее вход двух первых считаемьк импульсов. В исходном положении триггеры 1 - 4 устанавливаются в нулевое сос тояние по цепи сигнала Сброс. В этом случае (диаграммы на фиг. 2) О, Qj О, Q, О, Q4-- , 1, - 1, (з 1 На основании логических уравнений для I: и К1-входовполучают т 1 т п т т 1-1 I -l-j - -1-3 «J (f V - II 4 11 К - Il V - iin V -ч 4II tr - Ч , 1 , Kj 0 K 1 , этом на выходе дешифратора 5 сфорг-шрованы сигналы а 0,Ь О, С 0,d О, е О, f О, 5 1. Поэтому на индикаторе высвечивается цифра О. Поскольку 1К-триггер при и К О не изменяет своего состоя ния, при I 1 и К 1 переключается в противоположное состояние при I 1 и К О переключается в состояние логической единицы и пр I О и К 1 переключается 054 в состояние логического нуля, то по поступлении в схему первого считаемого импульса, так как 1, 1, тг -. 41 т о V - П т : П 1 3 1, 1 О, К О, только триггер 1, на выходе которого фор- . мируется логическая функция Qj, переключится в состояние логической единицы, а остальные триггеры 2-4 остаются в состоянии логического нуля. Состояния выходов при этом равны: -Q, 1, 0 О, 0, О, 0. О 0, О, 0 1, Q3 1, Q 1. Состояние входов триггеров при этом следующие; т ч ч т - 1 (Л т - 1 т 1, 1 , 1, 1 о 1 , I к| 1, V - 1 К2 О, 1 На выходах дешифратора появляются сигналы а 1, {. О, с О, J 1, f ч 1 1 1 1 м ч i-1,-1,-1 и на индикаторе высвечивается цифра 11 II При поступлении на вход схемы второго считаемого импульса триггер 1 возвращается в нулевое состояние, триггеры 2 и 3, на выходах которых формируются логические функции 02И П, соответственно переключатся в состояние логической единицы, а триггер 4, на выходе которого формируется логическая функция Q, остается в нулевом состоянии (диаграммы на фиг. 2). Состояния выходов следующие: Ql О, Q2 1, 0, 1, Q4 О 0, 1, Q2 О, Оз О, 0 1 На выходе дешифратора появятся сигналы а О, Ь 0,с r,J О, 6 0,, О, под действием которых на индикаторе сформируется цифра 2. Рассуждая аналогичным образом, получим и все остальные состояния схемы (диаграммы на фиг. 2). Дешифратор 5 для предлагаемой схемы построен в соответствии с логическими выражениями а (1,4) ,, d Ь (5,6) ,p V Q, (1,A,7) Q,Qj, e (1,3,4,5,7,9) Q., 3 (9,1,7) Q Q .

Сраг. /

0123456783Ю Фиг.2

| Титце У.,Шенк К | |||

| Полупроводниковая схемотехника | |||

| М | |||

| Мир, 1982, с | |||

| Замкнутая радиосеть с несколькими контурами и с одной неподвижной точкой опоры | 1918 |

|

SU353A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Декадный интегральный счетчик для семисегментных индикаторов | 1975 |

|

SU544134A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-07—Публикация

1983-09-19—Подача