Изобретение относится к области микроэлектроники, в частности к технологии изготовления полупроводниковых приборов и ИС.

Цель изобретения - повышение выхода годных микросхем за счет повышения воспроизводимости параметров распределения примеси в р-n-р транзисторных структурах.

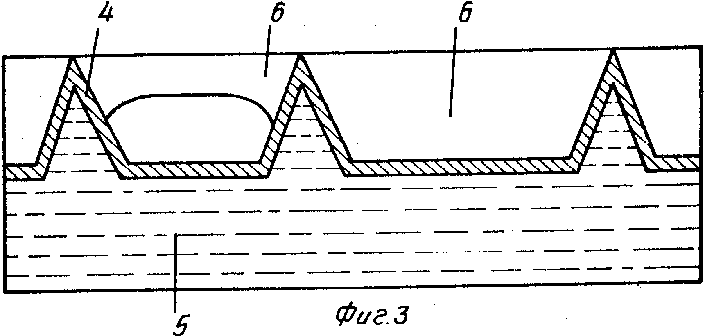

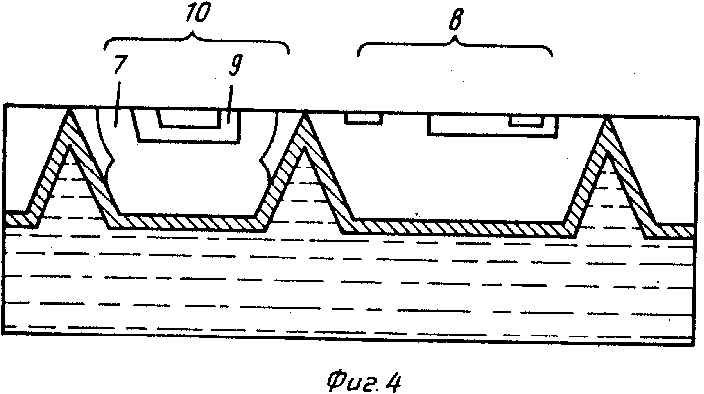

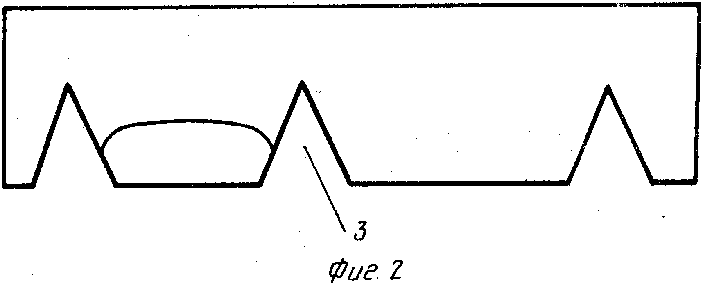

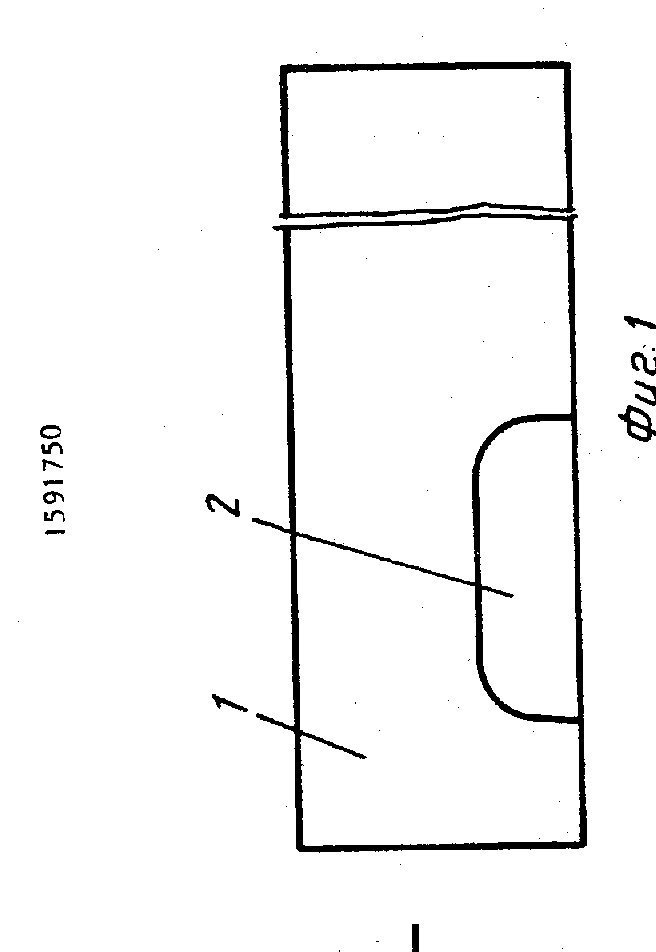

Фиг. 1-4 иллюстрируют технологический процесс изготовления микросхем. Приняты следующие обозначения: исходная подложка 1 n-типа проводимости, область 2, легированная бором, глубиной хр, разделительные канавки 3 глубиной хк, изолирующая пленка 4 оксида кремния, поликремний 5, изолированные области 6 карманов, область 7 подлегирования корректора р-n-р-транзистора, n-р-n-транзистор 8, базовая область 9 р-n-р-транзистора глубиной хб , р-n-р-транзистор 10.

П р и м е р. На кремниевой подложке 1, ориентированной в плоскости (100), с исходной концентрацией примеси n-типа, 1,5 ˙ 1014 см-3 выращивают маскирующий термический диодксид кремния. В сформированные фотолитографией окна проводят имплантацию ионов бора дозой 2,2 х 1015 см-2 и энергией 60 кэВ. Затем с помощью высокотемпературной обработки создают области 2 р-типа проводимости (фиг. 1) глубиной 40-42 мкм, которые служат коллекторами р-n-р-транзисторов. При получении глубины диффузии меньшей, чем 37 мкм в окончательно сформированной структуре возникает тиристорная р- n-p-n-структура с уменьшенным пробивным напряжением, катодом которой является нелегированная прослойка монокристаллического кремния n-типа проводимости, а при получении глубины диффузии больше чем 45 мкм уменьшаются пробивные напряжения коллектор-эмиттер р-n-транзистора и увеличивается разброс коэффициента усиления и пробивного напряжения коллектор - эмиттер р-n-р-транзистора.

Диэлектрическую изоляцию получают стандартными методами травления разделительных канавок 3 глубиной 60 ± 3 м км, создания термическим окислением или пиролитическим осаждением изолирующей пленки 4 диоксида кремния, газофазного осаждения поликремния 5, удаления шлифовкой с последующей подложки 1 n-типа проводимости до формирования изолированных областей 6 карманов, при этом точность вскрытия карманов составляет ± 5 мкм.

На полученной кремниевой структуре с диэлектрической изоляцией термическим окислением формируют маскирующий слой диоксида кремния. В сформированные фотолитографией окна проводят ионную имплантацию бора дозой 7,5 ˙ 1013 см-2 с последующей термической обработкой для создания областей 7 дополнительного легирования примесью р-типа проводимости глубиной 30 мкм (область подлегирования коллектора р-n-р-транзистора) (фиг. 4). Верхняя граница глубины диффузии подлегирования ограничивается топологическими зазорами и большими временами разгонки бора. За последующими операциями формирования фотолитографией окон проводят создание базы р-n-р-транзистора диффузией примеси n-типа проводимости с минимальной глубиной 6 мкм и максимальной глубиной 8 мкм. На полученной структуре с помощью метода планарной технологии формируют n-p-n-транзистор 8 и р-n-транзистор 10. (56) Ефимов И. Е. , Козырь И. Я. , Горбунов Ю. И. Микроэлектроника. Физические и технологические основы, надежность. - М. : Высшая школа, 1986, с. 299-303.

Патент США N 3818583, кл. 29-578, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ МОЩНЫХ ПОЛЕВЫХ LDMOS ТРАНЗИСТОРОВ | 2008 |

|

RU2364984C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1991 |

|

RU2024108C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1989 |

|

SU1702826A1 |

| МОЩНЫЙ СВЧ LDMOS ТРАНЗИСТОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2011 |

|

RU2473150C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

| ВЫСОКОВОЛЬТНЫЙ САМОСОВМЕЩЕННЫЙ ИНТЕГРАЛЬНЫЙ ДИОД | 2012 |

|

RU2492552C1 |

| САМОСОВМЕЩЕННЫЙ ВЫСОКОВОЛЬТНЫЙ ИНТЕГРАЛЬНЫЙ ТРАНЗИСТОР | 2012 |

|

RU2492551C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ С МОДЕРНИЗИРОВАННЫМ ЗАТВОРНЫМ УЗЛОМ ЭЛЕМЕНТАРНЫХ ЯЧЕЕК | 2016 |

|

RU2639579C2 |

Изобретение относится к области микроэлектроники, в частности к технологии изготовления полупроводниковых приборов и ИС. Цель изобретения - повышение выхода годных микросхем за счет повышения воспроизводимости параметров распределения примеси в p - n - p транзисторных структурах. Для этого при изготовлении микросхем в полупроводниковой кремниевой подложке n-типа проводимости формируют диффузионные области p-типа глубиной xp затем создают канавки глубиной xк изолирующие с боков эти области, а также области n-типа подложки. На поверхности канавок выращивают диэлектрическую пленку и осаждают поликремний. Полученную структуру утончают, удаляя материал подложки до вскрытия изолированных карманов. В изолированные карманы, содержащие области p-типа, проводят диффузию примеси p-типа на глубину x. В карманах n-типа создают транзисторные структуры n - p - n-типа, а в карманах p-типа - структуры p - n - p-типа с глубиной базовых областей xб Размерные параметры диффузонных областей p - n - p-транзисторов должны удовлетворять соотношению xк-x≅xp≅xк-xб Это обеспечивает стабильные и повышенные значения пробивных напряжений между коллектором и эмиттером транзисторов, а также их коэффициента усиления. 4 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ, включающий создание в кремниевой подложке n-типа первых диффузионных областей p-типа, формирование канавок, разделяющих p- и n-области в подложке, формирование диэлектрической пленки на поверхности канавок, осаждение поликремния, удаления материала подложки до вскрытия дна канавок и создание во вскрытых изолированных канавками участках кремниевой подложки диффузионных базовых и эмиттерных областей n-p-n- и p-n-p- транзисторных структур, отличающийся тем, что, с целью повышения выхода годных микросхем за счет повышения воспроизводимости параметров распределения примеси в p-n-p- транзисторных структурах, первые диффузионные области p-типа в кремниевой подложке создают глубиной, не превышающей разность между заранее выбранными глубиной канавок, разделяющих p- и n-области в подложке, и глубиной диффузии базы p-n-p- транзисторных структур, а после удаления материала подложки до вскрытия дна канавок во вскрытых изолированных канавками участках кремниевой подложки, содержащих первые диффузионные области p-типа, создают вторые диффузионные области p-типа, смыкающиеся с первыми.

Авторы

Даты

1994-02-15—Публикация

1989-01-13—Подача