Изобретение относится к вычислительной технике и может быть исползовано в системах обмена информацией

Целью изобретения является расширение функциональных возможностей шифратора за счет обеспечения скрем блирования поспедовательности позиционных кодов.

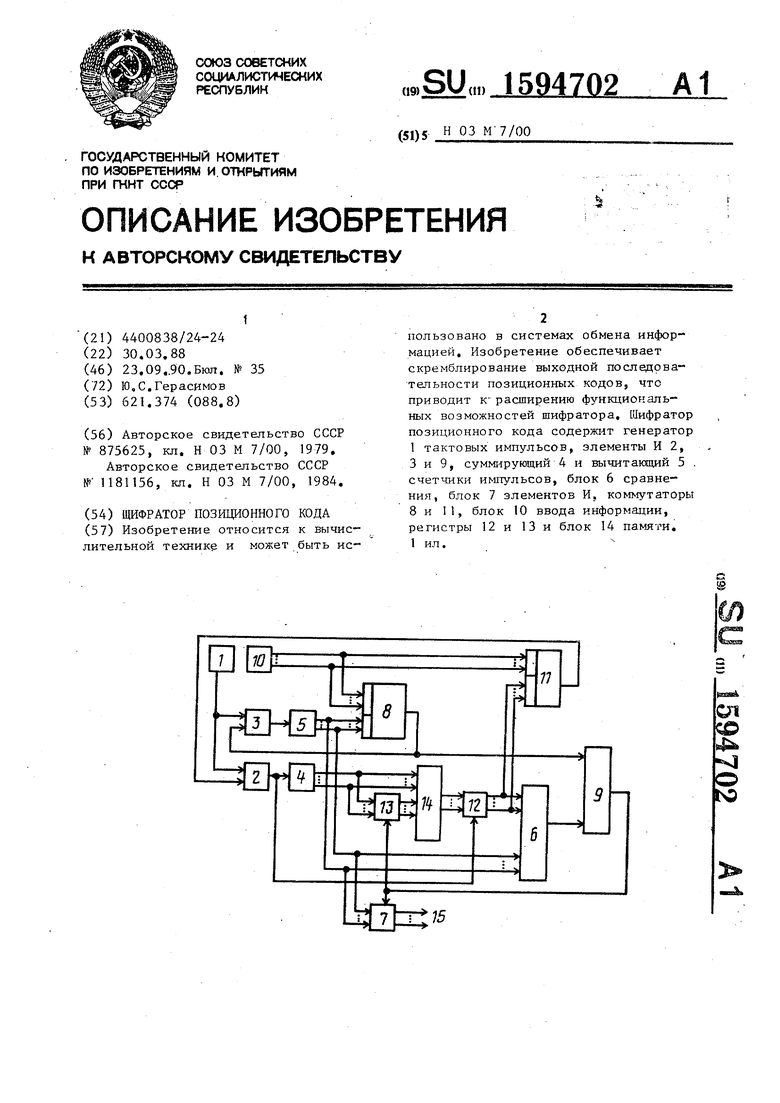

На чертеже представлена функцио гт нальная схема шифратора,,

Шифратор содержит генератор 1 тактовых импульсов, первый и второй элементы И 2 и 3, суммирующий и вычитающий счетчики 4 и 3 импульсов, блок 6 сравнения, .блок 7 элементов И первый коммутатор 8, третий элемент И 9, блок 10 ввода информации, второй коммутатор 11, первый и второй регистры 12 и 13 и блок 14 памяти. Позицией 15 обозначе;ны выходы шифратора

Генератор 1 работает.непрерывно, при этом на вход счетчика 4 через элемент И 2 и на вход счетчика 5 через элемент И 3 поступают так . овые импульсы, В исходном состоянии на все информационные вход1 ; коммутаторов 8 и 11 поступают сигналы ческого О с блока 10, На выходах коммутаторов 8 и 11 присутствуют сигналы логического которые,-поступая соответственно на входы элемен- - Тов И 2 И 3, разрешают прохождение импульсов тактовой частоты на входы счетчиков 4 и 5, Число возможных состояний последних равно числу информационных входов кoм ryтaтopoв 8 и 11, Каждое текущее состояния счетчиков 4 и 5 обусловливает трансляцию на выходы коммутаторов 8 и 11 сигнала с соотвегствующе1 о этому состоянию информационного входа. Причем порядок сле;: ования состояний счетчиков 4 и 5 взаимообратный, т,е, если поступление импульсов на счетчики 4 и 5 началось тогда, когда они находились в одинаковых состояниях, то эти состояния повторяются периодически и одновременно. Кроме того, содержание блока 14 таково, что при некотором начальном состоянии регистра 13 и одинаковости coc- f тояний регистра 12 и счетчика 5, непрерывная выработка импульсов генератором 1 обусловливает периодическое формирование блоком 6 сравнения

логической , Однако этот сигнал логической 1 с блока 6 не проходит

5

через элемент И 9 на блок 7 элементов И, поскольку вход элемента И 9 соединен с выходом коммутатора 8, у которого в этот момент присутствует сигнал логического О, Следовательно, через блок 7 позиционный код со счетчика 5 на входы шифратора не считывается,

10Разрядность регистров 13 и 12 одинакова с разрядностью счетчиков 4 и 5, Число кодовых комбинаций, каж- дая из которых соответствует одному из возможных состояний счетчика 4 15 или 5, заранее записывается для хранения в-блоке 14, Если условно представить эти кодовые комбинации в виде квадратной матрицы, адреса-строки и столбца которой задавать при счи- 0 тывании каждой комбинации соответственно посредством состояния счетчика 4 и состояния регистра 13, то в каждой строке и каждом столбце этой матрицы любая кодовая комби нация не - должна повторяться дважды. При дан- ном содержании блока 14 и при постоянном состоянии регистра 13 поступление тактовых импульсов на счетчик 4 и управляющий вход регистра 12 обеспе- 0 чивает последовательный и построчный опрос содержания, соответствующего столбца хранимой в блоке 14 матрицы, В каждый момент времени состояния счетчика 4 и регистра 12, как 5 правило, не одинаковы, хотя и однозначно связань: между собой через матрицу блока 14, Это значит, что, имея информацию о состояниях счетчика 4 и регистра 13, всегда можно однознач- 0 но определять состояние регистра 12, Шифратор позиционного кода работает следугацим образом.

При поступлении сигнала логической 1 с блока 10 вввода информации на 5 один из информационных входов коммутатора 11 и при совпадении кодовой комбинации, снимаемой; с регистра 12, с кодовой комбинацией, разрешающей прохождение сигнала логической 1 Q именно с данного информационного

входа коммутатора 11 на его выход, на последнем появляется сигнал логической 1, Этот сигнал запрещает прохождение импульсов тактовой частоты J с генератора 1 на вход счетчика 4, на входы блока 14 и регистра 12, В результате счетчик 4, блок 14 и регистр 12 останавливаются. По аналогии на выходе коммутатора 8 появляется сигнал логической 1, который также за- прещает прокождение через элемент И 3 импульсов тактовой частоты на счетчик 5, и тот останавливается в , том же состоянии, что и регистр 12 Причем остановка счетчика 5 по времени может и опередить и запоздать f относительно остановки счетчика , блока 14 и регистра 12,

Как только состояния счетчика 5 и регистра 12 совпадают, сигнал логического О на выходе блока 6 сравнения меняется на сигнал логической 1, который проходит через элемент И 9 на блок 7, и позиционный код состояние счетчика 4) считывается на выходы 15 шифратора. Одновременно под влиянием того же сигнала логической 1 тот же позиционный код считывается в регистр 13, стирая в последнем прежний код. Элемент И 9 в данном случае разблокирован сигналом логической 1 с выхода коммута- .тора 8,

При снятии сигнала логической 1 с выбранного первоначального информационного входа коммутатора II и соответствующего информационного входа коммутатора 8 снимаются сигналы запрета на выходах коммутаторов 8 и 11, Импульсы тактовой частоты вновь поступают на входы счетчиков 4 и 5, которые продолжают работать по взаи- мообразным циклам до моментов остано-ч вок вследствие подачи сигнала логической 1 на информационные входы коммутаторов 8 и 11,

Если случайно поданы сигналы логической 1 одновременно на два информационных входа коммутатора 11 и на два соответствующих информаци- онньк входа коммутатора 8, то происходит остановка счетчика 5 и регист- ра 12 в неодинаковых состояниях, т.е. в разных. Блок 6 сравнения соответственно не вырабатывает сигнал логической 1, а значит, позиционный код со счетчика 4 оказывается не считанным блоком 7, хотя элемент И 9 в этот момент разблокирован. Ошибку в работе шифратора позиционного кода можно исправить, исклю- чив ложный сигнал логической 1 на

оответствующих информационных входах 5 элемента И,

Шифратор жащий генер выход кото входами пе тов И, выхо входами соо щего и выч сов, выходы импульсов с ми блока ср ми блока эл входами пер которого со второго эле третьего эл соединен с ментов И, в выходом шиф мации, выхо информацион второго ком ды второго вторыми вхо ход которог дом третьег го коммутат входом перв чающий д)асширения тей шифрато скремблиров ти позицион введены рег ды которого ными входам ды которого дам блока с щего счетчи первыми вход формационным ра, выходы к рыми входами щие входы пе ров подключе венно первог

коммутаторов 8 и 11 / отпустив непра ВИЛЬНО нажатую клавишу блока 10) и .сохранив истинный сигнал логической 1 на других информационных входах каммутаторов 8 и II,

10

15

20

5

0

5

0

5

0

Формула изобретения

Шифратор позиционного кода, содер- жащий генератор тактовых импульсов, выход которого соединен с пери.1ми входами первого и второго эл емен- тов И, выходы которых соединены с входами соответственно суммирующего и вычитающего счетчиков импульсов, выходы вычитагацего счетчика импульсов соединены с входами блока сравнения, с первыми входами блока элементов И и с адресными входами первого коммутатора, выход которого соединен с вторым входом второго элемента И и первым входом третьего элемента И, выход которого соединен с вторым входом блока элементов И, выходы которого являются выходом шифратора, блок ввода инфор- - мации, выходы которого соединены с информационными входами первого и второго коммутаторов, адресные входы второго коммутатора объединены с вторыми входами блока сравнения, выход которого соединен с вторым входом третьего элемента И, выход второго коммутатора соединен с вторым входом первого элемента И, о т л и- чающийс.я тем, что, с целью д)асширения функциональных возможностей шифратора за счет обеспечения скремблирования последовательности позиционных кодов, в шифратор введены регистры и блок памяти, выходы которого соединены с информацион- ными входами первого регистра, выходы которого подключены к вторым входам блока сравнения, выходы суммирующего счетчика импульсов соединены с первыми входами блока памяти и с информационными входами второго регистра, выходы которого соединены с вторыми входами блока памяти, управляю щие входы первого и второго регист ров подключены к выходам соответственно первого элемента И и третьего

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор позиционного кода | 1989 |

|

SU1642588A1 |

| Шифратор позиционного кода | 1988 |

|

SU1520671A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Шифратор позиционного кода | 1984 |

|

SU1181156A2 |

| Шифратор позиционного кода | 1986 |

|

SU1349007A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| Шифратор позиционного кода | 1988 |

|

SU1683178A1 |

| Шифратор позиционного кода | 1980 |

|

SU875625A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для передачи и приема информации | 1985 |

|

SU1257688A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией. Изобретение обеспечивает скремблирование выходной последовательности позиционных кодов, что приводит к расширению функциональных возможностей шифратора. Шифратор позиционного кода содержит генератор 1 тактовых импульсов, элементы И 2,3 и 9, суммирующий 4 и вычитающий 5 счетчики импульсов, блок 6 сравнения, блок 7 элементов И, коммутаторы 8 и 11, блок 10 ввода информации, регистры 12 и 13 и блок 14 памяти. 1 ил.

| Шифратор позиционного кода | 1980 |

|

SU875625A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шифратор позиционного кода | 1984 |

|

SU1181156A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-23—Публикация

1988-03-30—Подача