Изобретение относится к вычисли -- тельной технике и может быть использовано в автоматизированных системах обмена информации.

Целью изобретения является повышение надежности шифратора.

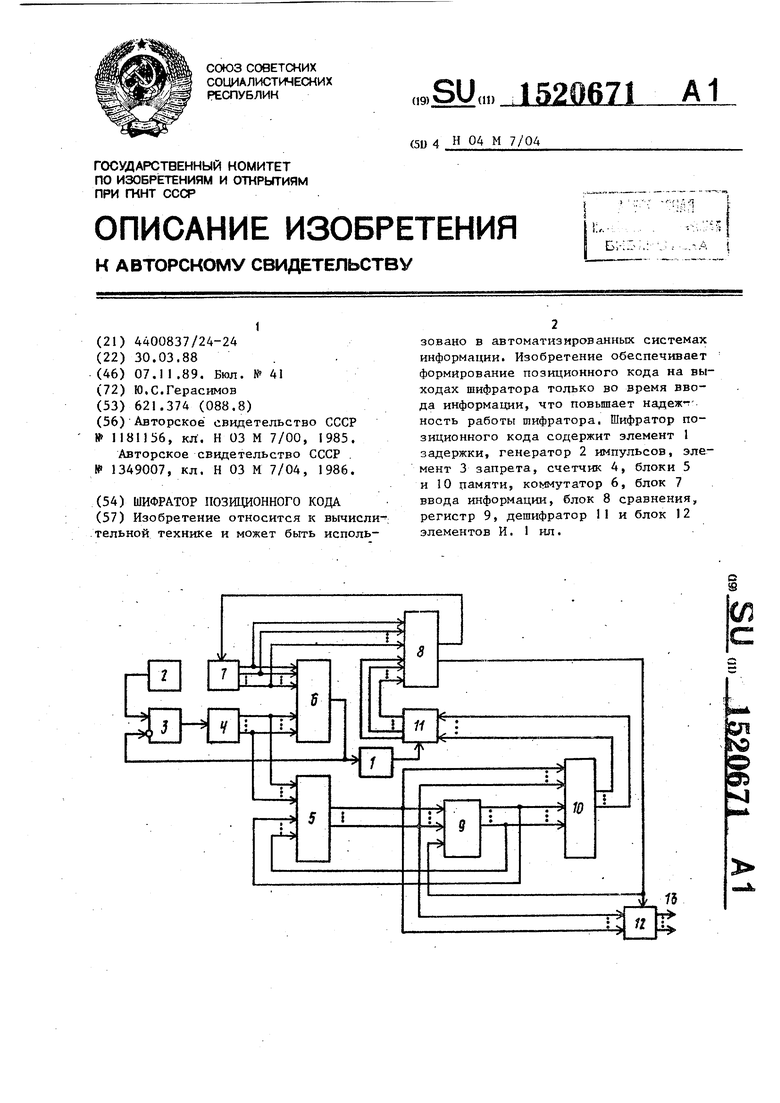

На чертеже представлена функциональная схема шифратора позиционного кода.

Шифратор содержит элемент 1 задержки, ренератор 2 импульсов, элемент 3 запрета,.счетчик 4 импульсов, первый блок 5.памяти, коммутатор 6, блок 7 ввода информации, блок 8 срав- ненияJ регистр 9, второй блок 10 памяти, дешифратор 1 и блок 12 элементов И и имеет выходы 13.

В блоке 5 заранее должна быть записана для хранения программа скремб- лирования в виде информации, некото- рой квадратной матрицы, адреса строк которой задаются возможными значениями позиционного кода в счетчике 4, а адреса столбцов - возможными знача- ниями позиционного кода в регистре 9. Инверсный вход считывания (не показан) блока 5 заземлен (на него подан на все время работы шифратора сигнал логического О), в пересе- чении указанных счетчиком 4 и регистром 9 соответственно строки и столб - да матршц 1 имеется значение позиционного кода, формируемого на выходах блока 5. Свойством такой матрицы явт ляется то, что в любых ее строке и., столбце расположены все возможные значения выбранного позиционного кода (весь алфавит значений).

Вместе; с тем, в блоке 10 должна быть записана для хранения программа дескремблирования в виде информации квадратной матрицы, адреса строк которой задаются возможными значениями позиционного кода, формируемыми на выходах блока 5, а адреса столбцов - возможными значениями позиционного кода в регистре 9. Свойством этой матрицы являетс то, что в любой ее ступени, строке и столбце расположены все возможные значения выбранного позиционного кода (весь алфавит значений), а ее содержание однозначно обусловлено содержанием матрицы, хранимой в блоке 5, так, что на выходах блока 10 формируется значение позиционного кода, идентичное в данный момент вре

5

0 5 Q

5

0

5

0

5

мени значению позиционного кода в счетч1же 4. Инверсньй вход-считывания (не показан) блока 10 также заземлен, поэтому на выходах блока 10 имеется значение позиционного кода согласно заданным блоком 10 и регистром 9 адресам соответственно строки и столбца. Число разрядов в регистре 9 равно числу разрядов в счетчике 4..

Дешифратор 11 при появлении разрешающего сигнала на управляющем входе преобразует значение позиционного кода в соответствующее значение унитарного кода, подаваемое на первые входы блока В, с вторых входов которого еще не снято исходное значение унитарного кода блока 7. Задержка в элементе 1 рассчитана на время завершения переходных процессов в цепи / блок 5 - регистр 9 - блок 12.

При равенстве двух значений унитарного кода на входах блока 8 выра батьгоается сигнал совпадения, который используется в качестве управляющего сигнала записи регистром 9. В результате значение позиционного кода с выходов блока 5 перезаписывается в регистр 9 вместо прежнего значения позиционного кода и одновременно, значение позиционного кода является выходным сигналом шифратора и поступает на его выходы 13 через блок 12.

При неравенстве двух значений унитарного кода на входах блока 8 вы-- рабатывается сигнал несовпадения, который является сигналом блокировки для блока 7. В результате предотвращается ввод в шифратор последующей информации, что сигнализирует о факте неправильной работы шифратора. Следует попытка ввести в шифратор ту же информацию вторично, а при повторном отказе следует анализ работы отдельных блоков шифратора на предмет поиска отказавшего.

Шифратор позиционного кода работает следующим образом.

Генератор: 2 работает непрерьшно, при этом на вход счетчика 4 через элемент 3 поступают импульсы. В исходном состоянии все разряды регистра 9 обнулены, а на все информационные входы коммутатора 6 поступают сигналы О. На выходе коммутатора 6 также присутствует сигнал О, который, поступая на вход элемента 3,

513

разрешает прохождение импульсов такТОБОЙ частоты на вход счетчика 4.

При вводе информации в шифратор на одном из выходов счетчика 4 возникает сигнал 1, что соответству ет появлению определенного значения унитарного кода на входах коммутатора 6. При совпадении кодовой комбинации, снимаемой со счетчика 4, с кодовой комбинацией, разрешающей прохождение сигнала 1 именно с данного информационного входа коммутатора 6 на его выход, на последнем появляется сигнал 1. Этот сигнал запрещает прохождение импульсов тактовой частоты с генератора 2 на вход счетчика 4, и последний останавливается, принимая значение позиционного кода.

В ответ на это блок. 5 выраб-атьшает значение z

t

F-(x- ,) позиционного кода, где - значение позиционного кода, подвергшееся скремблированию; х - значение позиционного кода вводимой информации соответствующее адресу строки и хранимое в момент времени t 1 в счет, -t-O

чике 4; Z - значение нулевой кодовой комбинации, хранящееся в момент времени t 1 в регистре 9; F: двухаргументная функция скремблиро- вания, осуществляемая согласно, j-й программе, хранимой в блоке 5 в виде информации матриць j . Появление

.значения z на выходах блока 5 обусловливает реализацию блоком 10 функции скремблирования вида х

- ( .

кое значение к

z .),после чего получен позиционного кода преобразуется в значение х унитарного кода и подается на первые входы блока 8. При этом Fо, обозначает двухаргументную функцию скремблирования согласно q-й программе, хранимой в блоке 10 в виде информации q, для которой адресом строки является значение позиционного кода из блока 5, а адресом столбца - значение позиционного кода из регистра 9.

06716

блока 8. При их рАвенстве сигнал совпадения, вырабатьгааемьй блоком 8, , обеспечивает запись z из блока 5 в регистр 9 вместо прежнего в нем значения . Одновременно значение г из блока 5 считывается через блок 12 на выходы 13 шифратора. Первый цикл (начавшийся в момент

to времени t 1) работы шифратора завершается после того, как снимается засечение блоком 7, т.е. пропадает сигнал 1 с соответствующего информационного входа коммутатора 6.

15 Это влечет снятие сигнала запрета для элемента 3, и импульсы тактовой частоты вновь начинают поступать на вход счетчика 4.

Счетчик 4 продолжает работать по

20 своему циклу до момента выдачи первого сигнала 1 на вход коммутатора 6, это приводит к очередной остановке счетчика 4. Тем самым начинается второй цикл (в момент вре25 мени t 2) в работе шифратора, заключающийся в последовательном прове4--

дении операций шифрации к из унитарного в позиционный код, скремблиi-i „ . -ь-г t-i .

ровании z Fj х ,2 J, де30,1 , -Ь-г t- ч

скремблировании х F-(.z ,z ;,

дешифрации х из позиционного, в

унитарный код, сравнении полученного и исходного значений уни- 35 тарных кодов между собой, записи

1 ir i

X позиционного кода из блока 5

в регистр 9 или блокировки блока 7. Третий и все полученные циклы ра- tf. боты шифратора происходят идентично двум первым так, что алгоритм работы при скремблировании описывается рек- курентной формулой

45

( , Z Fj ( «

a при дескремблировании - х

t F (z , z ), причем взаимо tQ связь, их программ обусловливается справедливостью формулы

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор позиционного кода | 1986 |

|

SU1349007A1 |

| Шифратор позиционного кода | 1988 |

|

SU1594702A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для поиска неисправных блоков и элементов | 1985 |

|

SU1309042A1 |

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обмена информации. Изобретение обеспечивает формирование позиционного кода на выходах шифратора только во время ввода информации, что повышает надежность работы шифратора. Шифратор позиционного кода содержит элемент 1 задержки, генератор 2 импульсов, элемент 3 запрета, счетчик 4, блоки 5 и 10 памяти, коммутатор 6, блок 7 ввода информации, блок 8 сравнения, регистр 9, дешифратор 11 и блок 12 элементов И. 1 ил.

В блоке 8 происходит сравнение X , являющегося результатом преобразований шифрация - скремблирова- ние - дескремблирование - дешифрация, с другим исходным значением X унитарного кода с выходов блока 7 подаваемого на вторые входы

, F,. - ).

i.;-t-j .

Формула изобретения,: Шифратор позиционного кода, содержащий элемент задержки, генератор импульсов, выход которого соединен

с прямым входом элемента запрета, выход которого соединен с входом счетчика импульсов, выходы которого соединены с первыми входами первого блока памяти и коммутатора, : выход которого соединен с инвертирующим входом элемента запрета, блок ввода информации, выходы которого соединены с вторьми входами коммутатора и с первыми входами блока сравнения, первый и второй выходы которого сое динены соответственно с входом уп- равления блока ввода информации и с входом записи регистра, выходы ко торого соединены с вторыми входами первого блока памяти и с первь1ми входами второго блока памяти, выходы

которого через дешифратор подключены к вторым входам блока сравнения, информационные входы регистра объединены с вторыми входами второго блока памяти, отличающийся тем, что, с целью повышения надежности шифратора, в него введен блок элементов И, первый вход которого подключен к второму выходу блока управления, выходы первого блока памяти сое- динены с соответствующими информационными входами регистра и с вторыми входами блока элементов И, выходы которого являются вькодами

шифратора, управляющий вход дешифратора через элемент задержки подклю - чен к выходу коммутатора.

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР | |||

| Шифратор позиционного кода | 1986 |

|

SU1349007A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-07—Публикация

1988-03-30—Подача