вателей импульсов группы, выходы которых соединены с входами шифратора, выход кот.орого соединен с адресным входом второго блока памяти группа информационных выходов которого соединена с второй группой информационных входов коммутатора. 0 информационные входы второго блока памяти соединены с выходами информационных разрядов первого блока памяти, выход второго разряда режима работы узла памяти программ блока управления соединен с входом режима работы второго блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля систем управления | 1979 |

|

SU789977A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ, содержащее блок ввода-вывода, первьй блок памяти, .коммутатор, счетчик, блок сравнения, блок индикации и блок управления, содержащий генератор тактовых имаульсов, элемент. И, регистр, шифратор, счетчик адреса и узел памяти программ, причем информационные входы-г выходы блока ввода-вывода являются информационными входами-выходами устройства, информационные входывыходы коммутатора соединены с входами-выходами объекта контроля, информащюнный выход коммутатора соединен с первой группой информационных входов блока сравнения, выход которого соединен с входом блока индикации, выход которого соединен с управляющим входом блока вводавывода, информационнь1Й выход которого соединен с информационным входом первого блока памяти, выходы разрядов типа информации которого соединены с управляющими входами коммутатора и блока сравнения. группа выходов информационных разрядов первого блока памяти соединена с первой группой информационных входов коммутатора и второй группой информационных входов блока сравнения, а блоке управления вькод регистра через шифратор соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом узла памяти программ, группа выходов разрядов очередного адреса программы которого соединена с первой группой информационных входов регистра, вторая группа информационных входов которого соединена с группой выходов разрядов очередного адреса програмСЛ С мы первого блока памяти, вход режима работы которого соединен с выходом первого разряда режима работы узла памяти программ блока управления, выход запуска которого соединен с счетным входом счетчика, выход, генератора тактовых импульсов соединен с первым входом элемен о та И выход которого соединен с счетным входом счетчика адреса, второй вход элемента И блока управления и третья группа информационных входов регистра блока управления соединены соответственно с выходом запуска и группой выходов начального адреса программы блока вводавывода , отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй блок памяти, шифратор и группа формирователей импульсов, причем выходы счетчика соединены с входами соответствующих формиро

Изобретение относится к контроль но-измерительной технике и может быть использовано для проверки функционирования и диагностики цифровых узлов. Известно устройство для испытания логических блоков, содержащее блок управления, генератор случайньк кодов, дешифратор, И -разрядный сумматор по модулю 2, коммутатор, эталонный и контролируемый блоки, блок сравнения Л. Недостатками этого устройства являются сложность коммутации сигна лов на эталонный и контролируемый блоки, малое быстродействие проведения проверки функционирования сложных цифровых узлов из-за отсутствия возможности дополнения их. проверки тестами по таблице истиннести. Наиболее близким к предлагаемому по технической сущности является устройство для автоматизированного контроля функционирования цифровых плат, содержащее блок ввода-вьгоода блок управления, блок памяти, счет чик, блок формирования кодовой последовательности, контактное поле два коммутатора, блок сравнения ц блок индикации, причем вход-вькод блока ввода-вывода является входомвыходом устройства, информационный выход блока ввода-вывода соединен с информационным входом блока памяти, информационный выход которого соединен с первым входом первого коммутатора, выход которого соедине с первым входом второго коммутатора первый выход которого соединен с первым входом блока сравнения, выход которого соединен с первым входом блока сравнения, выход которого соединен с входом блока индикации, выход которого соединен с управляющим входом блока ввода-вывода, выход запуска которого соединен с входом запуска блока управления, тактовый выход которого соединен с счетным входом счетчика выход которого соединен с входом блока формирования кодовой последовательности, выход которого через контактное поле соединен с вторым входом первого коммутатора, вторые вход и выход второго коммутатора соединены соответственно с входом и выходом объекта контроля, вьпсод режима работы блока управления соединен с входом режима работы блока памяти, выходы разрядов адреса программы которого соединены с адресным входом блока управления, второй вход схемы сравнения соединен с информационным выходом блока памяти 21. Недостатком известного устройства является низкое быстродействие, обусловленное ручным программированием сигналов входных последовательностей. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для контроля цифровых устройств, содержащее блок ввода-вьшода, первый блок памяти, коммутатор, счетчик, блок сравнения, блок индикации и блок управления, содержащий генератор тактовых импульсов, элемент И, регистр, шифратор, счетчик адреса команд и узел памяти программ, причем информационные входы-выходы блока ввода-вывода являются инфорj.aциoннь ми входами-выходами уст3

ройства, информационные входы-вы, ходы.коммутатора соединены с входами-выходами объекта контроля, информационный выход коммутатора соединен .с первой группой информационных бх.одов блока сравнения, выход которого соединен с входом блок индикации, выход которого соединен с управляющим входом блока вводавывода, информационный выход которого соединен с информационным входом первого блока памяти, выходы разрядов типа информации которого соединены с управляющими входами коммутатора и блока сравнения, группа выходов информационных разрядов первого блока памяти соединена с первой группой информационных входов коммутатора и второй группой информационных входов блока сравнения, в блоке управления выход регистра через шифратор соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом узла памяти программ, группа выходов разрядов очередного адреса программы которого соединена с первой группой информационных входов регистра, вторая группа информационных входов которого соединена с группой выходов разрдов очередного адреса программы первого блока памяти, выход режима работы которого соединен с выходом первого разряда режима работы узла памяти программ блока управления, выход запуска которого соединен с счетным входом счетчика, выход генератора тактовых импульсов соединен с первым входом злемента И, выход которого соединен с счетным входом счетчика адреса, второй вход элемента И блока управления и третья группа информационных входов регистра блока управления соег динены соответственно с выходом запуска и группой выходов начального адреса программы блока вводавывода, введены второй блок памяти, шифратор и группа формирователей импульсов, причем выходы счетчика соединены с входами соответствующих формирователей импульсов группы, выходы которых соединены со входами шифратора, выход которого соединен с адресным входом второго блока памяти., группа информационных выходов которого соединена с второй

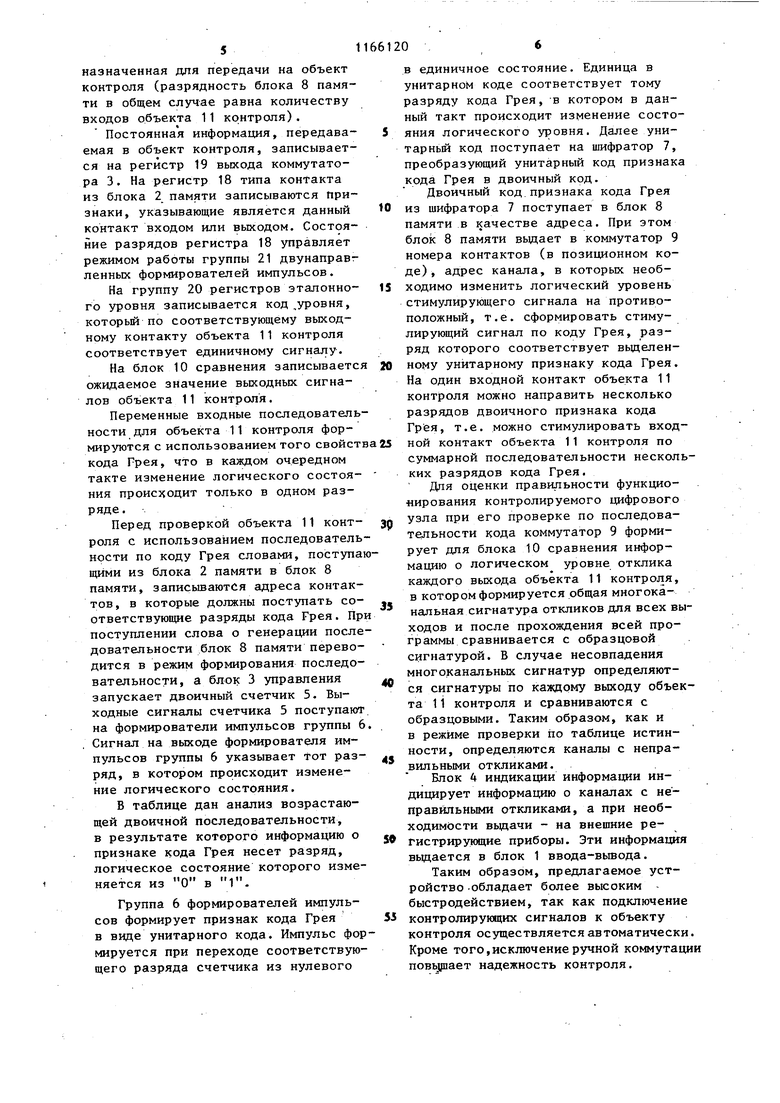

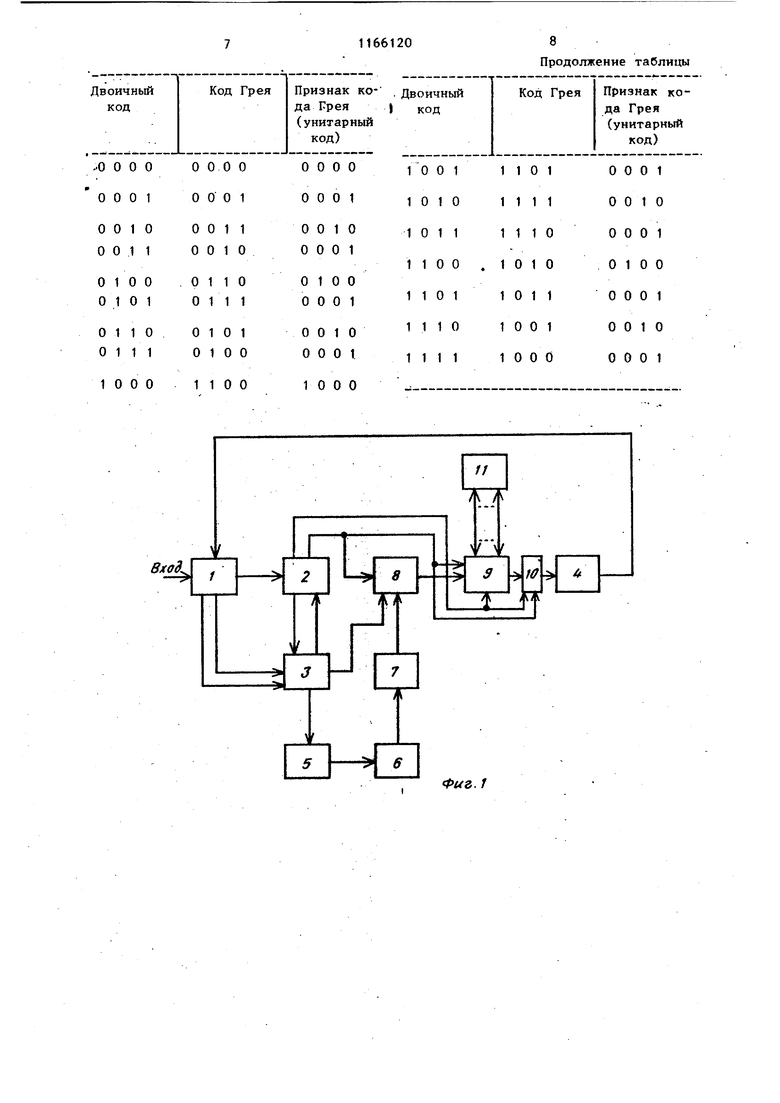

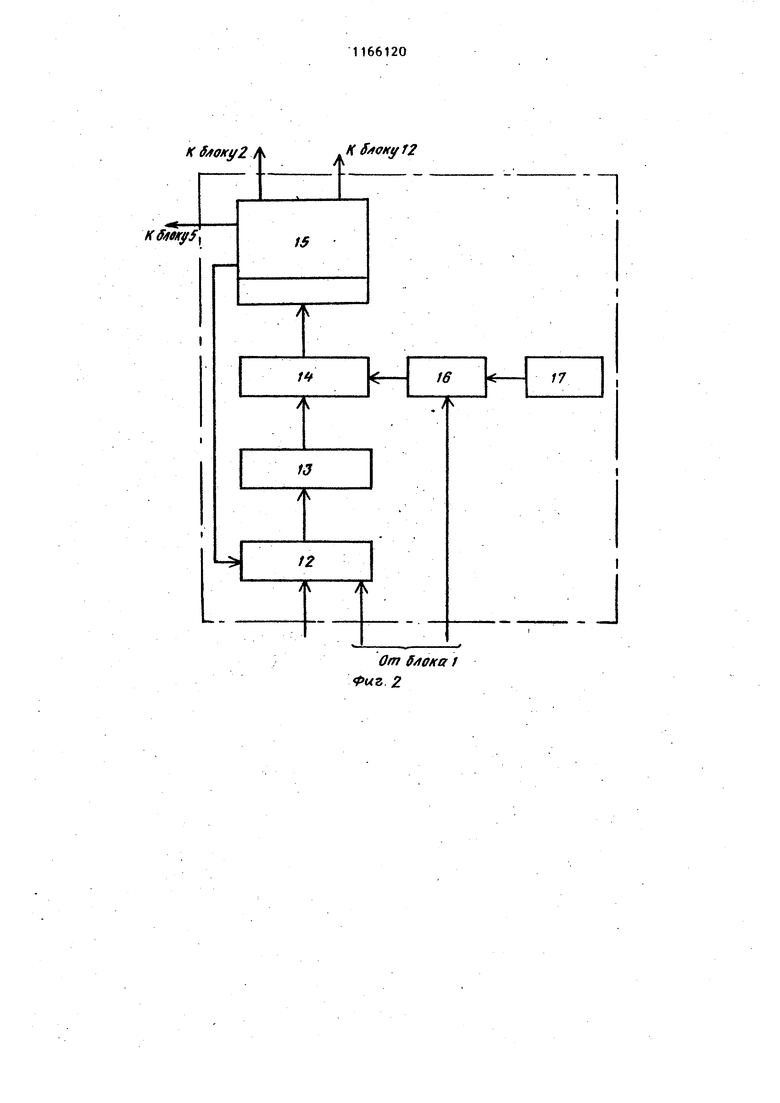

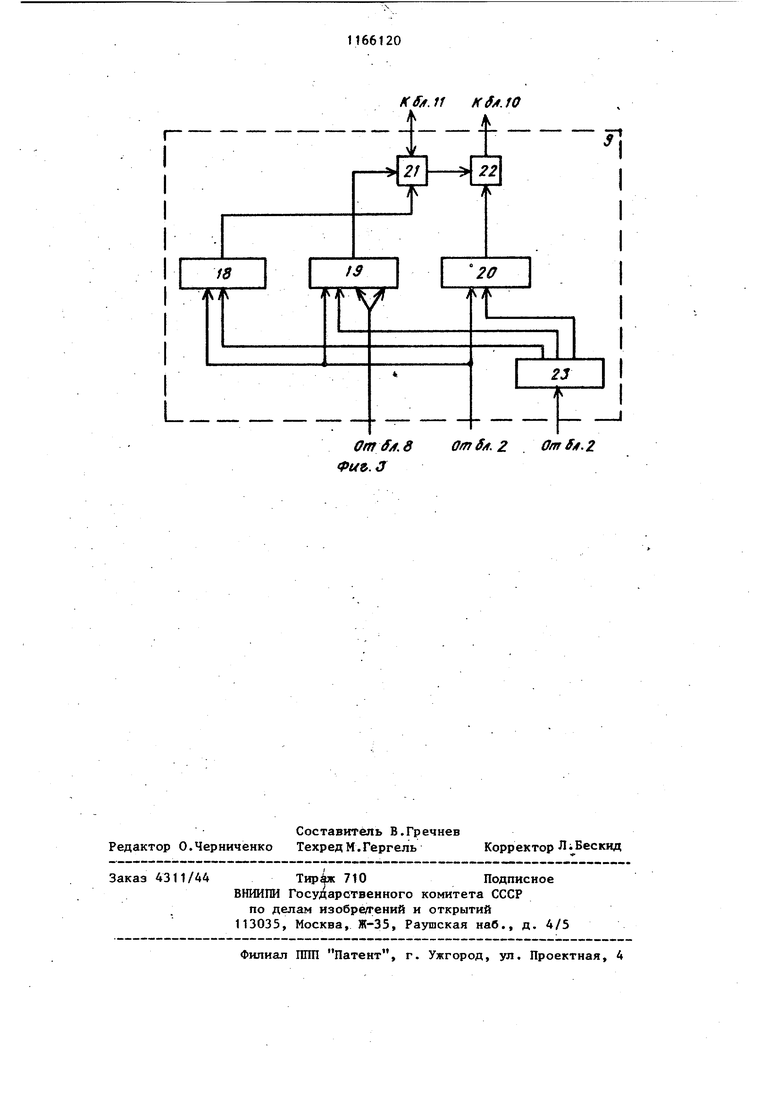

группой информационных входов коммутатора, информационные входы второго блока памяти соединены с выходами И1гформационных разрядов первого блока памяти, выход второго разряда режима работы узла памяти программ блока управления соединен с входом режима работы второго блока памяти.На фиг. 1 приведена структурная схема предлагаемого устройства для контроля цифровых узлов; на фиг.2 структурная схема блока управления; на фиг. 3 - структурная схема коммутатора.

Устройство (фиг. 1), содержит блок 1 ввода-вывода, первый блок 2 памяти, блок 3 управления, блок 4 индикации, счетчик 5, группу 6 формирователей импульсов, шифратор 7, второй блок 8 памяти, коммутатор 9, блок 10 сравнения и объект 11 контроля.

Блок 3 управления (фиг. 2) содержит регистр 12, шифратор 13, счетчик 14 адреса, узел 15 памяти программ, элемент И 16, генератор 17 тактовых импульсов.

Коммутатор 9 (фиг. 3) содержит регистр 18 типа выходного контакта, информационньй регистр 19, группу 20 регистров эталонного уровня, группу 21 двунаправленных формирователей импульсов, группу 22 компараторов и дешифратор 23.

Устройство работает следующим образом.

При помощи блока 1 ввода-вывода в блок 2 памяти вводится программа проверки и размещается в нем словами определенной дпины. (Управление записью осуществляет программа блока 3 управления).

Каждое слово содержит информацию, признаки вида информации и признаки корректировки адреса программы блока 3 управления.

По окончании зайиси программы проверки в первый блок 2 памяти блок 3 управления начинает считывать содержимое блока 2 памяти и рассылать его по блокам устройства в зависимости от признаков типа информации, содержащихся в считанном слове.

Таким образом, заполняется второй блок 8 памяти. В него записывается переменная информация, предназначенная для передачи на объект контроля (разрядность блока 8 памяти в общем случае равна количеству входов объекта 11 контроля).

Постоянная информация, передаваемая в объект контроля, записывается на регистр 19 выхода коммутатора 3 . На регистр 18 типа контакта из блока 2 памяти записываются Признаки, указывающие является данный контакт входом или выходом. Состояние разрядов регистра 18 управляет режимом работы группы 21 двунаправленных формирователей импульсов.

На группу 20 регистров эталонного уровня записывается код,уровня, которьй по соответствующему выходному контакту объекта 11 контроля соответствует единичному сигналу.

На блок 10 сравнения записываетс ожидаемое значение выходных сигналов объекта 11 контроля.

Переменные входные последовательности для объекта 11 контроля формируются с использованием того свойст кода Грея, что в каждом очередном такте изменение логического состояния происходит только в одном разряде.

Перед проверкой объекта 11 контроля с использованием последовательности по коду Грея словами, поступащими из блока 2 памяти в блок 8 памяти, записываются адреса контактов, в которые должны поступать соответствующие разряды кода Грея. Пр поступлении слова о генерации последовательности блок 8 памяти переводится в режим формирования последовательности, а блок 3 управления запускает двоичный счетчик 5. Выходные сигналы счетчика 5 поступают на формирователи импульсов группы 6 Сигнал на выходе формирователя импульсов группы 6 указывает Тот разряд, в котором происходит изменение логического состояния.

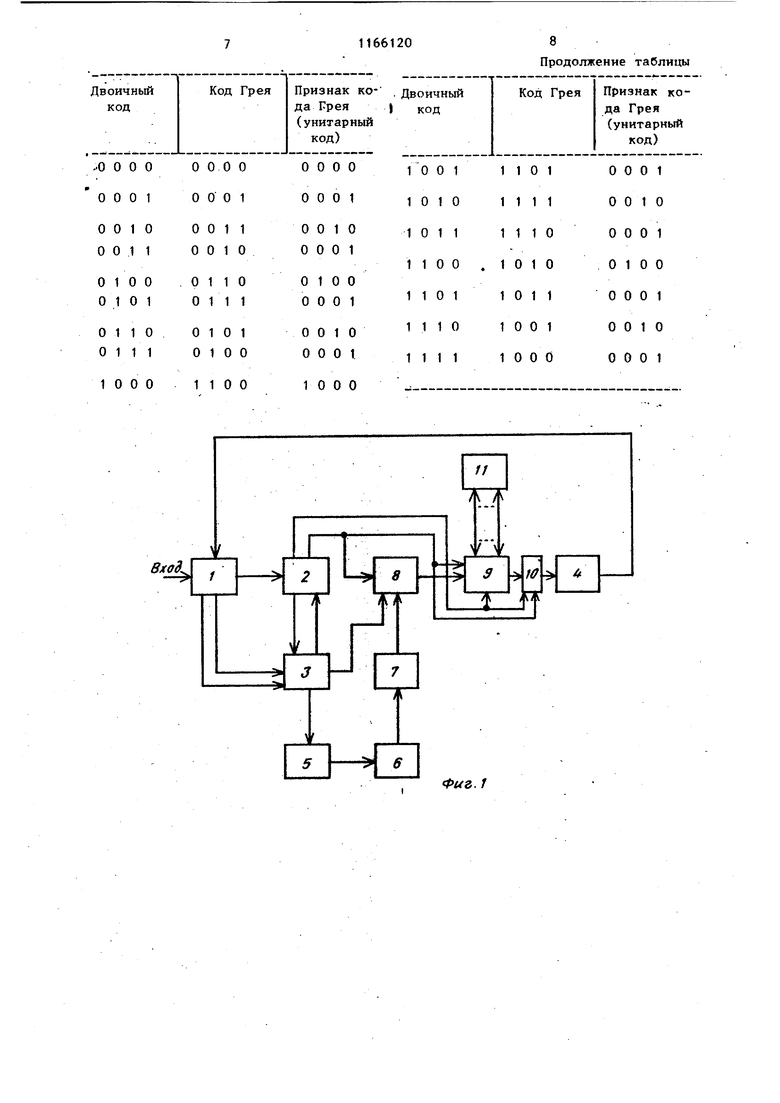

В таблице дан анализ возрастающей двоичной последовательности, в результате которого информацию о признаке кода Грея несет разряд, логическое состояние которого изменяется из О в 1.

Группа 6 формирователей импульсов формирует признак кода Грея в виде унитарного кода. Импульс формируется при переходе соответствующего разряда счетчика из нулевого

в единичное состояние. Единица в унитарном коде соответствует тому разряду кода Грея, в котором в данный такт происходит изменение состояния логического уровня. Далее унитарный код поступает на шифратор 7, преобразующий унитарный код признака кода Грея в двоичный код.

Двоичный код.признака кода Грея из шифратора 7 поступает в блок 8 памяти в качестве адреса. При этом блок 8 памяти вьщает в коммутатор 9 номера контактов (в позиционном коде) , адрес канала, в которых необходимо изменить логический уровень стимулирующего сигнала на противоположный, т.е. сформировать стимулирующий сигнал по коду Грея, разряд которого соответствует вьщеленному унитарному признаку кода Грея. На один входной контакт объекта 11 контроля можно направить несколько разрядов двоичного признака кода Грея, т.е. можно стимулировать входной контакт объекта 11 контроля по суммарной последовательности нескольких разрядов кода Грея.

Для оценки правильности функцио«ирования контролируемого цифрового узла при его проверке по последовательности кода коммутатор 9 формирует для блока 10 сравнения информацию о логическом уровне отклика каждого вькода объекта 11 контроля, в котором формируется общая многоканальная сигнатура откликов для всех выходов и после прохождения всей программы сравнивается с образцовой сигнатурой. В случае несовпадения многоканальных сигнатур определяются сигнатуры по каждому выходу объекта 1 1 контроля и сравниваются с образцовыми. Таким образом, как и в режиме проверки по таблице истинности, определяются каналы с непра вш1ьными откликами.

Блок 4 индикации информации индицирует информацию о каналах с неправильными откликами, а при необходимости вьвдачи - на внешние регистрирующие приборы. Эти информация выдается в блок 1 ввода-вьшода.

Таким образом, предлагаемое устройство .обладает более высоким быстродействием, так как подключение контролирующих сигналов к объекту контроля осуществляется автоматически Кроме того,исключение ручной коммутаци повьрает надежность контроля.

Продолжение таблицы

Фиг. 1

От ff/te/ftr 1 Фиъ. 2 Фиъ. J

Kff.ll KfA.lO

OmSjt.8 OmS/i.Z . OmS4.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для испытания логических блоков | 1975 |

|

SU551573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Установка автоматизированного контроля функционирования цифровых плат Линза-Ш | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-07—Публикация

1983-05-12—Подача