Изобретение относится к электронной технике и может быть использовано при изготовлении полупроводниковых приборов, в частности МДП-транзисторов на подложке из арсенида галлия.

Целью изобретения является повышение крутизны транзисторов.

Усилительные и частотные свойства МДП-транзисторов определяются главным образом энергетическими и кинематическими параметрами ловушек в приграничной области гетероконтакта полупроводник диэлектрик и в объеме слоя диэлектрика. Указанные параметры, в свою очередь, определяются как материалом компонентов гетеропары, так и условиями формирования слоя подзатворного диэлектрика. Экспериментально установлено, что в случае осаждения на поверхность подложки из арсенида галлия n-типа проводимости слоя сульфида цинка, полученного разложением диэтилдитиокарбамата (ДЭДТК) цинка, при определенных значениях температур подложки и испарителя с ДЭДТК формируется гетерограница, характеризуемая плотностью Nss состояний (3-5) х 1011 ЭВ-1/см-2. Достижение указанного значения Nss, приемлемого для создания МДП-приборов, обусловлено хорошим встраиванием атомов цинка и серы в решетку арсенида галлия, сопровождающимся "залечиванием" дефектов в приповерхностной области GaAs, что обеспечивается благоприятным соотношением полных радиусов атомов Zn и Ga, с одной стороны, и SuAs, с другой, и подтверждается высокой растворимостью серы и цинка в матрице арсенида галлия. Связывание As атомами цинка и серы приводит к насыщению свободных валентностей и, как следствие, к уменьшению Nss и стабилизации свойств поверхности.

Таким, образом, получение в системе ZnS-n-AsGa гетероконтакта с низкой плотностью пограничных состояний (менее 1012 см-2) позволяет создать на его основе МДП-транзисторы с повышенной крутизной и пониженной длинновременной релаксацией тока стока.

Экспериментально установлено, что положительный эффект достигается в ограниченном интервале температур подложки (Тп) и испарителя (Ти) ДЭДТК цинка при формировании пленки сульфида цинка.

При Тп < 290оС граница раздела полупроводник диэлектрик характеризуется высоким значением Nss, что не позволяет изготовить МДП-прибор с требуемыми параметрами транзисторов.

При Тп > 350оС повышение уровня вторичных реакций распада продуктов распада ДЭДТК цинка приводит к загрязнению слоя диэлектрика углеродистыми остатками. В результате наблюдается рост активной компоненты тока утечки и, как следствие, падение крутизны управляющей ВАХ транзистора.

Аналогичная ситуация имеет место при температуре испарителя более 250оС, когда наблюдается частичное разложение ДЭДТК цинка в испарителе, что приводит к изменению состава паровой фазы. Адсорбция продуктов распада на поверхность растущего слоя приводит к его загрязнению и появлению дополнительных центров, перезарядка которых снижает крутизну управляющей ВАХ транзистора и увеличивает длинновременную релаксацию тока стока прибора.

При Ти < 200оС давление пара ДЭДТК цинка в приповерхностной кристаллизации области подложки мало, что нарушает условия кристаллизации пленок и способствует переадсорбции продуктов распада, вызывая описанные последствия, затрудняющие достижение поставленной цели.

П р и м е р. Для изготовления транзистора по данному способу использованы стандартные эпитаксиальные структуры арсенида галлия марки "САГИС 6Н".

Способ изготовления МДП-транзистора включает следующие операции: формирование областей истока и стока (Au-Ge-Ni, вжигание;

формирование контактных площадок к областям истока, стока и затвора (200  Cr 0,6 мкм Au);

Cr 0,6 мкм Au);

обработка пластин в 5%-ном водном растворе соляной кислоты при комнатной температуре;

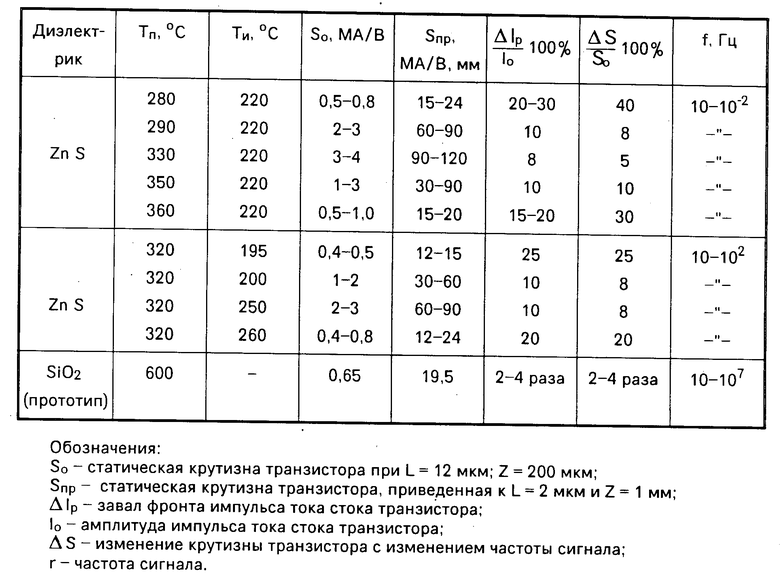

осаждение слоя сульфида цинка разложением ДЭДТК цинка (см. таблицу);

прямая фотолитография по ZnS;

формирование электрода затвора (V Au) и металла разводки;

скрайбирование и разводка в корпусе.

Результаты измерений для различных режимов формирования слоя сульфида цинка приведены в таблице.

Для транзисторов, изготовленных по данному способу, длинновременная релаксация тока стока и частотная дисперсия крутизны наблюдается в интервале частот 10-122 Гц и не превышает 10% В области частот 103-109Гц изменения основных параметров транзистора с изменением частоты не наблюдается. Полоса рабочих частот прибора не менее 109 Гц, времена переключения ≈ 5х10-10 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОКРЫТИЙ | 1980 |

|

SU940601A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВЫХ ТРАНЗИСТОРОВ С САМОСОВМЕЩЕННЫМ ЗАТВОРОМ | 1989 |

|

SU1628766A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1984 |

|

SU1153768A1 |

| ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ | 1991 |

|

RU2025831C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ ПОЛЕВОГО ТРАНЗИСТОРА | 2012 |

|

RU2523060C2 |

| ОПТОЭЛЕКТРОННЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1985 |

|

SU1284439A1 |

| ЭЛЕМЕНТ ПАМЯТИ (ЕГО ВАРИАНТЫ) | 1984 |

|

SU1153769A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВЫХ ТРАНЗИСТОРОВ С САМОСОВМЕЩЕННЫМ ЗАТВОРОМ | 1988 |

|

SU1565292A1 |

| ИНВЕРТОР | 1988 |

|

SU1649973A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО ТРАНЗИСТОРА С БАРЬЕРОМ ШОТТКИ | 2007 |

|

RU2349987C1 |

Изобретение относится к электронной технике и может быть использовано при изготовлении полупроводниковых приборов, в частности МДП - транзисторов на подложке арсенида галлия. Целью является повышение крутизны транзисторов. Цель достигается тем, что на подложку арсенида галлия, содержащую области стока и истока, осаждают диэлектрик методом пиролиза. В качестве газовой смеси используют диэтилдитиокарбамат цинка. 1 табл.

Способ изготовления МДП-транзисторов, включающий формирование на подложке арсенида галлия n-типа проводимости областей истока и стока, осаждение слоя диэлектрика методом пиролиза, формирование электрода затвора, отличающийся тем, что, с целью повышения крутизны транзисторов, слой диэлектрика осаждают пиролитическим разложением диэтилдитиокарбамата цинка при температуре подложки 290 350oС и температуре испарителя диэтилдитиокарбамата 200

250oС.

| Патент США N 4354198, кл | |||

| Клапан | 1919 |

|

SU357A1 |

| Becke H | |||

| et al | |||

| Gallium arsenide MOS-transistors | |||

| Solid State Electronics, 1965, v.8, p.813-823. | |||

Авторы

Даты

1996-05-27—Публикация

1989-02-03—Подача