Изобретение относится к импульсной технике, может быть использовано в устройствах автоматики и вычислительной техники и является дополнительным к авт. св. f 898601.

Цель изобретения - повышение поме- хозащиьченности путем фильтрации отрицательных кратковременных помех.

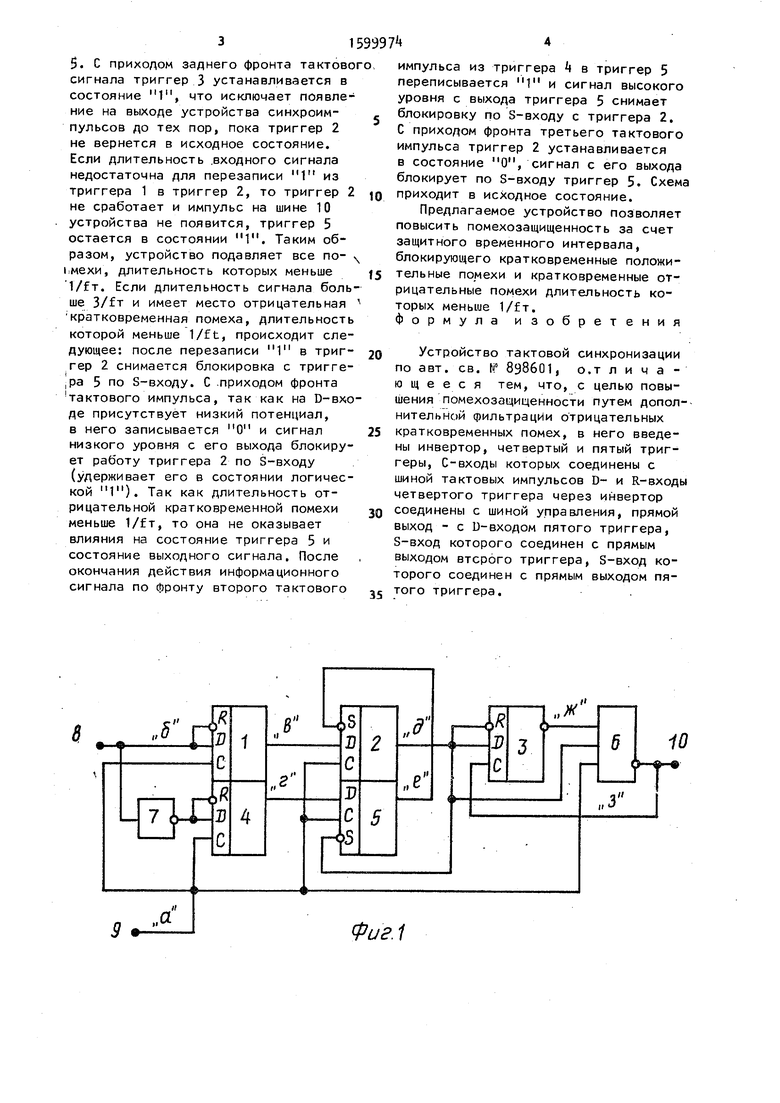

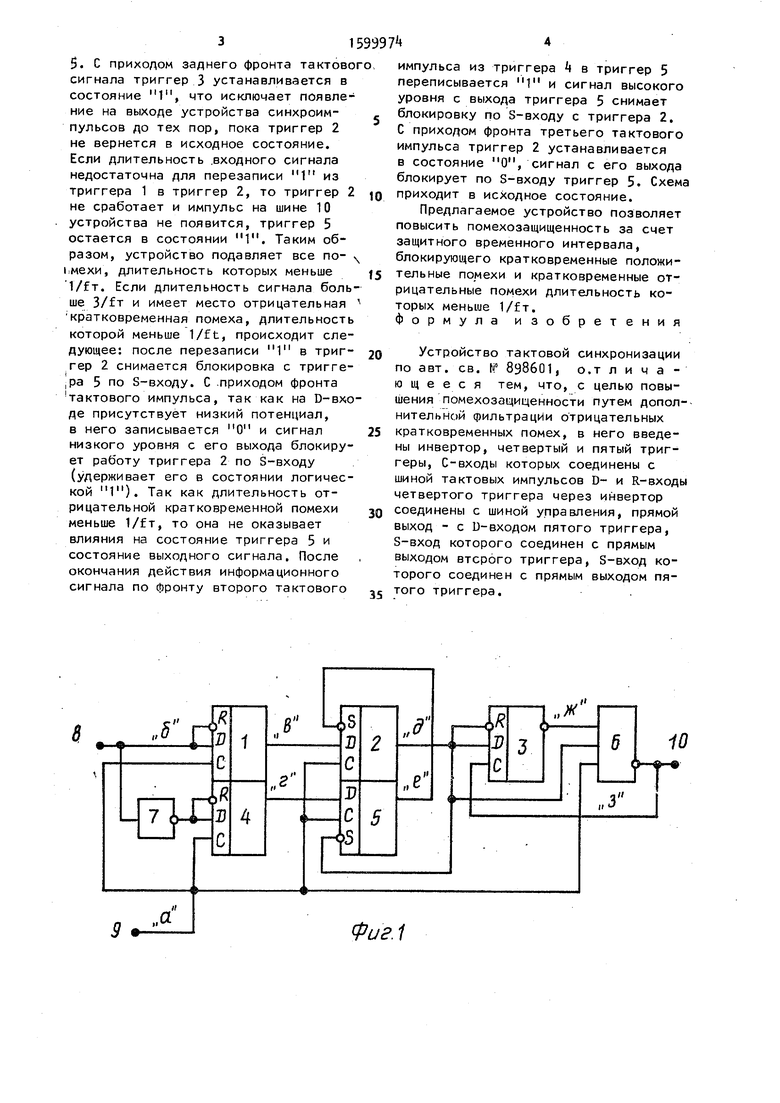

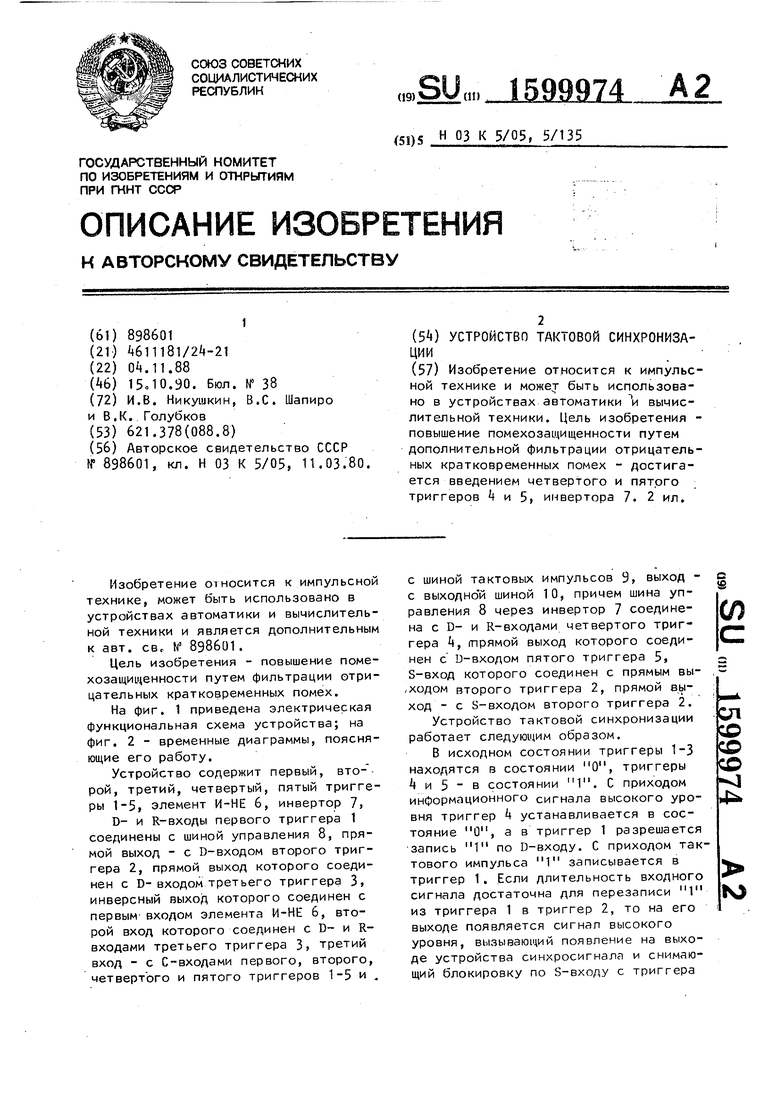

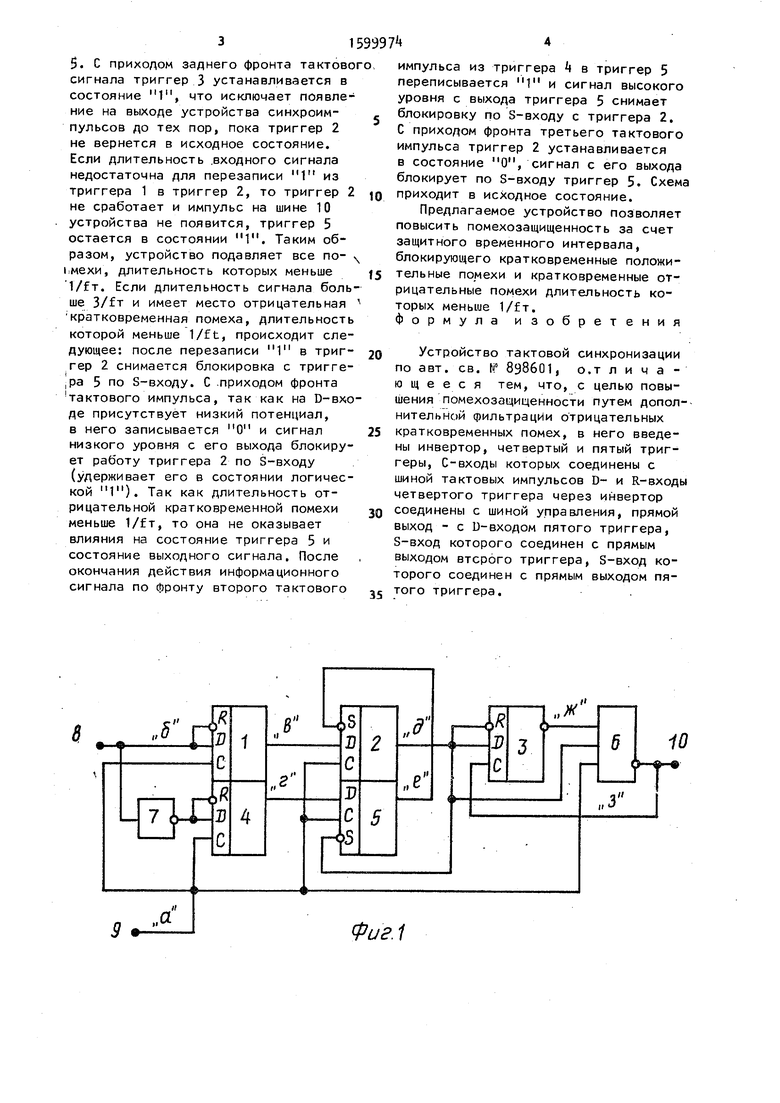

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит первый, вто-- рой, третий, четвертый, пятый триггеры 1-5, элемент И-НЕ 6, инвертор 7,

D- и R-входы первого триггера 1 соединены с шиной управления 8, прямой выход - с D-входом второго триггера 2, прямой выход которого соединен с D-входом третьего триггера 3, инверсный выход которого соединен с первым входом элемента И-НЕ 6, второй вход которого соединен с D и R- входами третьего триггера 3, третий вход - с С-входами первого, второго, четвертого и пятого триггеров 1-5 и ,

с шиной тактовых импульсов 9, выход - с выходной шиной 10, причем шина управления 8 через инвертор 7 соединена с D- и R-входами четвертого триггера , трямой выход которого соединен с D-входом пятого триггера 5, S-вход которого соединен с прямым вы- ,ходом второго триггера 2, прямой выход - с S-входом второго триггера 2.

Устройство тактовой синхронизации работает следующим образом.

В исходном состоянии триггеры 1-3 находятся в состоянии О, триггеры и 5 - в состоянии 1. С приходом информационного сигнала высокого уровня триггер t устанавливается в состояние О, а в триггер 1 разрешается запись 1 по D-входу. С приходом тактового импульса 1 записывается в триггер 1. Если длительность входного сигнала достаточна для перезаписи из триггера 1 в триггер 2, то на его выходе появляется сигнал высокого уровня, вызывающий появление на выходе устройства синхросигнала и снимающий блокировку по S-входу с триггера

о

:л

;& :о х |

4

М

5. с приходом заднего фронта тактово сигнала триггер 3 устанавливается в состояние 1, что исключает появление на выходе устройства синхроимпульсов до тех пор, пока триггер 2 не вернется в исходное состояние. Если длительность .входного сигнала недостаточна для перезаписи 1 из триггера 1 в триггер 2, то триггер 2 не сработает и импульс на шине 10 устройства не появится, триггер 5 остается в состоянии 1. Таким образом, устройство подавляет все по- , длительность которых меньше 1/fT. Если длительность сигнала больше 3/fT и имеет место отрицательная кратковременная помеха, длительность которой меньше I/ft, происходит следующее: после перезаписи 1 в триг- гер 2 снимается блокировка с тригге- |ра 5 по S-входу. С .приходом фронта тактового импульса, так как на D-BXO де присутствует низкий потенциал, в него записывается О и сигнал низкого уровня с его выхода блокирует работу триггера 2 по S-входу (удерживает его в состоянии логической 1). Так как длительность отрицательной кратковременной помехи меньше 1/fT, то она не оказывает влияния на состояние триггера 5 и состояние выходного сигнала. После окончания действия информационного сигнала по фронту второго тактового

0

j 0 ,

5

0

импульса из триггера Ц в триггер 5 переписывается 1 и сигнал высокого уровня с выхода триггера 5 снимает блокировку по S-входу с триггера 2. С приходом фронта третьего тактового импульса триггер 2 устанавливается в состояние О, сигнал с его выхода блокирует по S-входу триггер 5. Схема приходит в исходное состояние.

Предлагаемое устройство позволяет повысить помехозащищенность за счет защитного временного интервала, блокирующего кратковременные положительные помехи и кратковременные отрицательные помехи длительность которых меньше 1/fT. Формула изобретения

Устройство тактовой синхронизации по авт. св. If 898601, о.т л и ч а - ю щ е е с я тем, что, с целью повышения помехозащищенности путем допол-- нительной фильтрации отрицательных кратковременных помех, в него введены инвертор, четвертый и пятый триггеры, С-входы которых соединены с шиной тактовых импульсов D- и R-входы четвертого триггера через инвертор соединены с шиной управления, прямой выход - с и-входом пятого триггера, S-вход которого соединен с прямым выходом втсрого триггера, S-вход которого соединен с прямым выходом пятого триггера.

п п п п п

HL

П

J

П П П П

И

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1988 |

|

SU1599976A1 |

| Формирователь импульсов датчика положения | 1991 |

|

SU1836661A3 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Устройство для подавления помехпРи цифРОВОй пЕРЕдАчЕ иМпульСНОйпОСлЕдОВАТЕльНОСТи | 1977 |

|

SU840745A1 |

| Устройство для измерения временных интервалов | 1988 |

|

SU1539724A1 |

| Формирователь импульсов датчика положения | 1984 |

|

SU1238038A1 |

| Устройство для управления следящим приводом | 1985 |

|

SU1308988A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для одновременного наблюдения N-цифровых сигналов на экране осциллографа | 1990 |

|

SU1721521A1 |

| Коммутатор для управления шаговым двигателем | 1988 |

|

SU1566327A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение помехозащищенности путем дополнительной фильтрации отрицательных кратковременных помех - достигается введением четвертого и пятого триггеров 4 и 5, инвертора 7. 1 ил.

фиг. 2

| Устройство тактовой синхронизации | 1980 |

|

SU898601A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-15—Публикация

1988-11-04—Подача