v,-4

VH

(2)

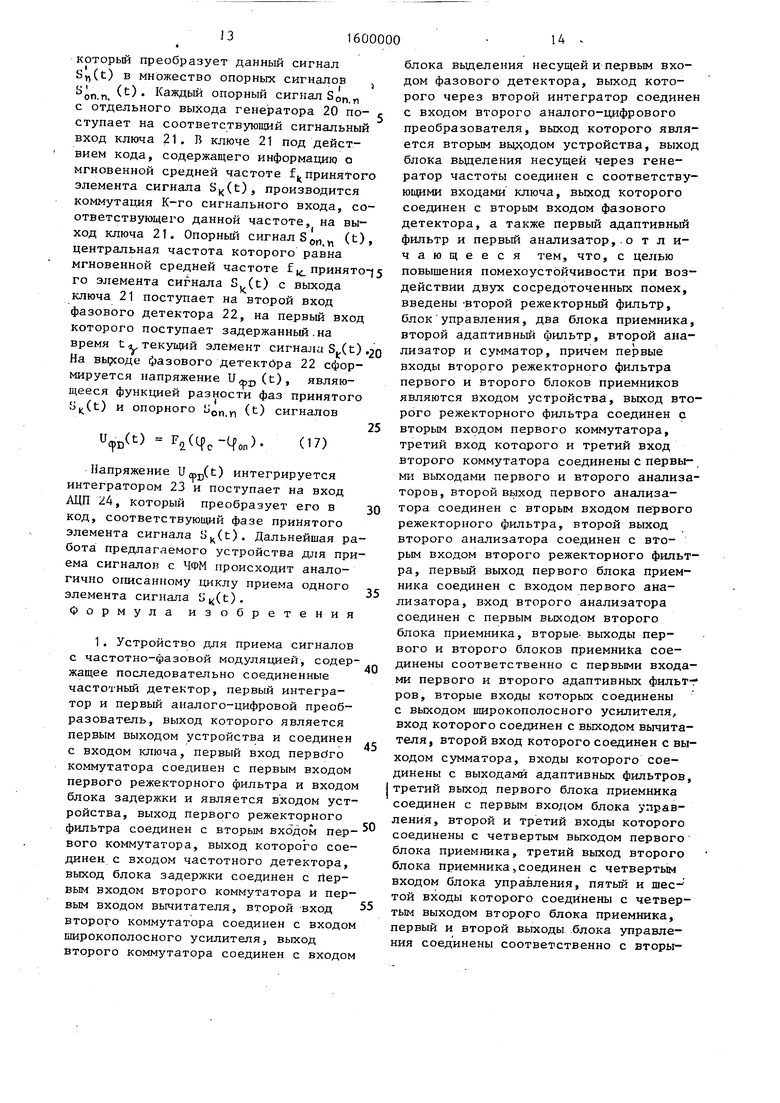

Vвц частота сигнала с выхода

входного блока 25; f VT частота сигнала гетеродиf

на 29;

Уц промежуточная частота БП1 / и БП2 10. На выходе смесителя 26 получается

набор комбинационных частот

- fy. + 2f, 6ц

(3)

Указанный набор комбинационных сигналов (3) поступает на вход усилителя 27, на выход которого проходит только сигнал частоты fv,jn.,,, удовлетворяющий условию (2). Выходной сигнал усилителя 27 (t) одновременно подается на сигнальный вход адаптивного фильтра 8 и на вход частотного детектора 30, выход которого соединен с входом управителя 32. Частотный детектор 30 и управитель 32 образуют систему автоматической подстройки частоты (АПЧ), т.е. систему подстройки частоты резонанса контура входного блока 25 и частоты гетеродина 29 fу за возможными изменениями положения центральной частоты fccni частотной оси. Система АПЧ работает следующим образом. Если

- f

V. т

(4)

30

35

40

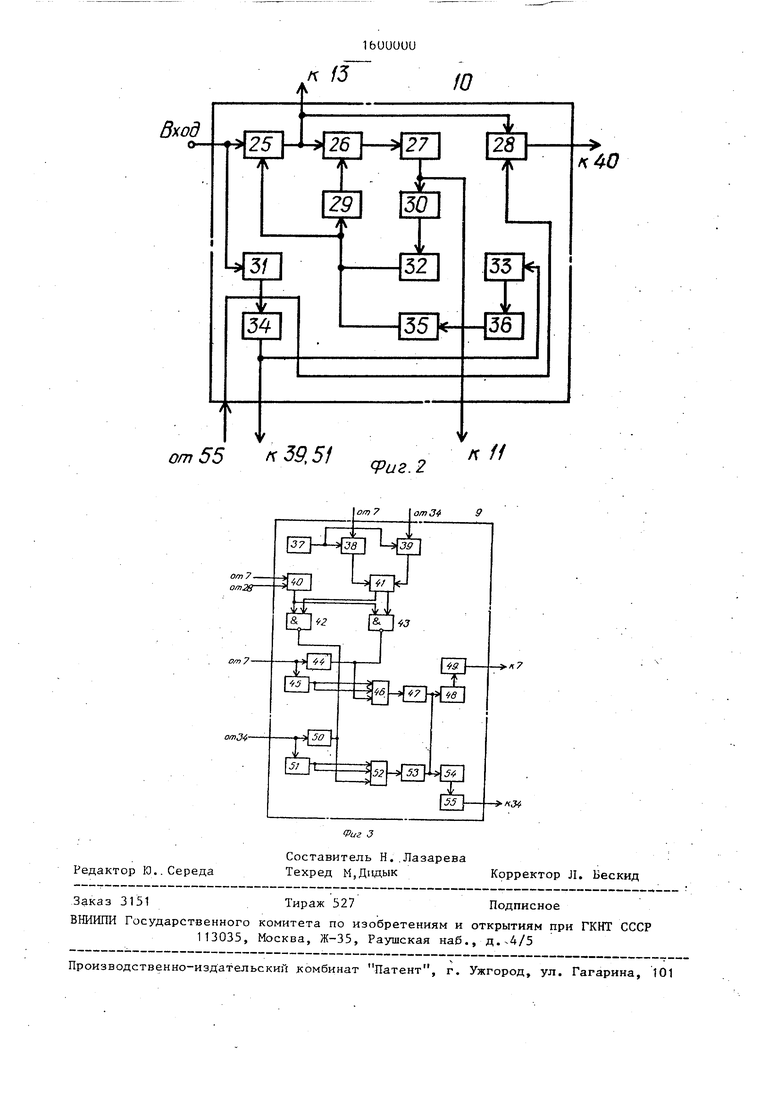

При захвате ПСП M(t) данные от .АЦП 28 в цифровой форме поступают на первьш вход блока 40. Одновременно импульс 1 с йыхода триггера 34 разрешает однократньш запуск формирователей 45, выход которого одновременно подключен к адресному (первому) входу и входу данных (второму) ОЗУ 46, так как в этот момент на вход W (третий) подается логический О (за счет прохождения 1 через инвертор 44), в ОЗУ 46 происходит запись числа 0001 соответствующего ПСП M,(t), в первую адресную ячейку. Импульс 1 с выхода триггера 34 прекращает подсчет временных импульсов с работающего непрерывно с момента включения предлагаемого устройства (t 0).. Генератор 37 в счетчике 38. Таким образом, в счет- 45 чике 38 происходит запись времени захвата ПСП M(t), поступакмцего на первый вход блока 41. Допустим, что эту же ПСП M,(t) через время t захватил блок 10. Тогда данные с АЦП 28 поступают 0 на второй вход блока 40. Одновременно импульс логической 1 с выхода триггера 34 разрешает однократный запуск формирователя 51, выход которого подключен одновременно к адресному (пер- 5 вому) входу и входу данных второму; ОЗУ 52, так как в этот момент на вход W (третий) подается О (за счет прохолщения 1 через инвертор 50) в ОЗУ 52 происходит запись числа 0010,

11600000

соответствующего не ССП Mj(t), а ПСП M(t) во вторую адресную ячейку.

Импульс 1 с выхода триггера 34 прекращает счет временных импульсов с j работающего непрерывно генератора 37 в счетчике 39. Таким образом, в счетчике 39 происходит запись времени захвата не ИСП M(t), а ПСП М(t), поступающего на второй вход блока 41. Q Поскольку числа, записанные в блок 40, равны (произошел захват блока 7 и блока 10 одной и той же ПСП M,(t), то на выходе блока 40 появится импульс 1 который поступает одвновременно на 15 первые входы элементов И-НЕ. Так как блок 7 захватил ПСП Ы ,(t) раньше, то на первом выходе блока 41 появится импульс 1. В результате на входах элемента,И-НЕ 42 будут 1, на выходе 20 также появится импульс 1, разрешающий считывание написанного числа 0010 в втором адресе ОЗУ 52. Это число че- рез инвертор 53 подаётся одновременно на вход блока 48 и блока 54. В 25 блоке 48 постоянно записано число 0001, а в блоке 54 - число 0010. Так как совпадение происходит в блоке 54, то на выходе 54 появляется им8

с выхода триггера 34 пр ращает счет временных импульсов в счетчике 38, в котором происходит запись времени захвата ПСП ), поступающего на.первый вход блока Ввиду того, что числа, записанные блок 40, равны, то на выходе блока 40 появится импульс 1, который п тупит одновременно на первые входы элементов И-НЕ 42 и 43, так как бл 10 захватил ПСП ) раньше, то н втором выходе блока 41 появится им пульс 1. В результате на входах элемента И-НЕ 43 будут 1, на вых де также появится импульс 1, раз решающий считывание записанного чи 0001 в первом адресе ОЗУ 46. Далее импульс совпадения появится на вых блока 48 и этот импульс 1 через инвертор 49 поступит на вход тригг ра 34, разрешая вновь, продолжить р боту генератора 33, осуществляя те самым дальнейший поиск ПСП блока 7 Инверторы 47 и 53 установлены всле ствие того, что выход 033 46 и вых ОЗУ 52 инвертирующие.

Сигнал с входного блока 25 пода ся на вход анализатора -12, т.е. на

пульс 1, который через инвертор 55 зо входы всех параллельных полосовых

фильтров. Выход каждого полосового фильтра соединен с сигнальным вход отдельного компаратора. При появле нии ПСП M(t) в полосе частот одно из полосовых фильтров, его выходно напряжение превысит порог срабатыв ния соответствующего ему компарато на выходе которого появится импуль 1. Этот импульс подается на один из входов т-входовой схемы сравнен и на вход отдельного усилителя пос янного тока (УПТ). Все отдельные в ходы УТП подключены в анализатор 1 к соответствующим входам т-входног суг-шатора, на выходе которого сфор руется управляющее напряжение, обе печивающее перестройку режекторног фильтра 3 по диапазону и его настр ку .строго на ПСП M(t). Указанный пульс 1, поступая на вход т-вход схемы сравнения, приведет к появле на ее выходе тоже импульса 1. Э напряжение поступает на третий вхо коммутатора 4 и третий вход коммут тора 18. В результате этого на вых данных коммутаторов поступят не си налы соответственно с входа предла мого устройства и с-входа блока 16 с выхода режекторного фильтра 5 и

поступает на вход триггера 34, разрешая вновь продолжить работу генератора 33, осуществляя тем самым даль- не11ший поиск ПСП блока 10 по диапазону частот. При дальнейших захватах : ПСП H,(t) блока 10 будет происходить то же: прием ПСП M(t) будет продолжать вести блок 7, а блок 10 продолжит поиск дальше.

При захвате ПСП M(t) блока 10 произойдет только запись числа 0010 во второй адрес ОЗУ 52 и блок 10 будет отслеживать ПСП ) . При попадании ПСП il,(t) импульс О с триггера 34 разрешит дальнейшую работу ге- гератора 33, блок 7 продолжит поиск и захватит ПСП ). При захвате этой помехи данные с АЦП 28 поступают на первый вход блока 40, импульс 1 с выхода триггера 34 разрешает однократньй запуск формирователя 45, выход которого одновременно подключен к адресному (первому) входу и входу данных (второму) ОЗУ 46. Поскольку в этот момент на вход V7 (третий) подается О (за счет прохождения 1 через инвертор 44, то в ОЗУ 46 происходит запись числа 0001 в первую адресную ячейку. Импульс логи8

с выхода триггера 34 прекращает счет временных импульсов в счетчике 38, в котором происходит запись времени захвата ПСП ), поступающего на.первый вход блока 41, Ввиду того, что числа, записанные в блок 40, равны, то на выходе блока 40 появится импульс 1, который пос тупит одновременно на первые входы элементов И-НЕ 42 и 43, так как блок 10 захватил ПСП ) раньше, то на втором выходе блока 41 появится импульс 1. В результате на входах элемента И-НЕ 43 будут 1, на выходе также появится импульс 1, разрешающий считывание записанного числа 0001 в первом адресе ОЗУ 46. Далее импульс совпадения появится на выходе блока 48 и этот импульс 1 через инвертор 49 поступит на вход триггера 34, разрешая вновь, продолжить работу генератора 33, осуществляя тем самым дальнейший поиск ПСП блока 7. Инверторы 47 и 53 установлены вследствие того, что выход 033 46 и выход ОЗУ 52 инвертирующие.

Сигнал с входного блока 25 подается на вход анализатора -12, т.е. на

входы всех параллельных полосовых

5

0

5

0

5

фильтров. Выход каждого полосового фильтра соединен с сигнальным входом отдельного компаратора. При появлении ПСП M(t) в полосе частот одного из полосовых фильтров, его выходное напряжение превысит порог срабатывания соответствующего ему компаратора, на выходе которого появится импульс 1. Этот импульс подается на один из входов т-входовой схемы сравнения и на вход отдельного усилителя постоянного тока (УПТ). Все отдельные выходы УТП подключены в анализатор 12 к соответствующим входам т-входного суг-шатора, на выходе которого сформируется управляющее напряжение, обеспечивающее перестройку режекторного фильтра 3 по диапазону и его настройку .строго на ПСП M(t). Указанный импульс 1, поступая на вход т-входовой схемы сравнения, приведет к появлению на ее выходе тоже импульса 1. Это напряжение поступает на третий вход коммутатора 4 и третий вход коммутатора 18. В результате этого на выход данных коммутаторов поступят не сигналы соответственно с входа предлагаемого устройства и с-входа блока 16, а с выхода режекторного фильтра 5 и с

выхода вычитателя 17 соответственно т.е. в этом в сигналах на выходах коммутаторов 4 и 18 будет практически отсутствовать ПСП M(t). Аналогично первому работает анализатор 13, осуществляя настройку режекторно- го фильтра 6 под ПСП M(t) и управляя работой коммутаторов 4 и 18

Сигнал на входе адаптивного фильтра 8 можно представить в виде

V,n/t)M,(t)-HS,(t)+n(t), (5)

где S ,Xt) - часть полезного сигнала S(t), попавшая в полосу пропускания усилителя 27.

Выходной сигнал адаптивного фильтра 8 имеет вид:

i:,(t) w,(t) VB, (t).

(6)

где W(t) - изменяемая во времени

импульсная характеристика 25

адаптивного фильтра. При воздействии сигнала ошибки (t) с выхода широкополосного усилителя 15 на управляющий вход адаптивного . фильтра 8, передаточная функция W,(t) последнего изменяется таким образом, что в вычитателе 17 обеспечивается оптимальное (по критерию минимума среднеквадратической ошибки) подавление ПСП М,, (t) во входном воздействии

где U2(t) - изменяемая во времени и пульсная характеристика адаптивного фильтра 11. При воздействии сигнала ошибки J5 с выхода широкополосного усили теля 15 на управляющий вход адатив- ного фильтра 11 передаточная функци W2.(t) последнего изменяется таким о разом, что в вычитателе 17 обеспечи вается оптимальное (по критерию мин мума среднеквадратической ошибки) п давление ПСП MgCt) во входном воздей ствии V,(t). Адаптивный фильтр 8 и адаптивный фильтр 11 идентичны, позт му для адаптивного фильтра 11 справедливо

li(t)U(t).V,Jt)M2(t).(10

Выходные сигналы адаптивных фильт ров 8 и 11 складываются в сумматоре 14 и с его выхода поступают на инвер тирующий вход вычитателя 17.

Таким образом, адаптивный фильтр 8 учитывает и устраняет дд вычитател

1 - .,. 1 arLri

V,(t). Действительно совокупность из35 ,7 возможные различия характеристик последовательно соединенньк перемно- при проховдении ПСП M(t) от входа :;п/я Г ° адаптивного предлагаемого устройства через Фильтра 8 образует коррелятор, выход- 16 до неинвертирующего входа вьгчитанои отклик которого Z (t) характери- теля 17 и от входа устройства чер1з

зует степень линейной стохастической - -устройства через

взаимосвязи, между воздействием ) 1,на сигнальном (т.е. с выхода усили- теля 27 и управляющем (t) (т.е. .с выхода широкополосного усилителя 15) входах адаптивного филь1;ра 8. Этим и обеспечивается формирование выходного сигнала ii(t) адаптивного фильтра 8, в максимальной степени похожего на подавляемую ПСП M,(t) (а значит и ее подавление в вычитателе 17). При зтом можно показать, что

45

блок 7, адаптивный фильтр 8 и сумматор 14 до инвертирующего входа вычитателя 17. В то же время адаптивный фильтр 11 учитывает и устраняет до вычи.тателя 17 возможные различия характеристик при прохождении ПСПМ (t) от входа предлагаемого устройства через блок 16 до неинвертирующего входа вычитателя 17 и от входа предлагаемого устройства через блок 10, 50 адаптивный фильтр 11 и сумматор 14

до инвертирующего входавычитателя 17

limZ,(t)limV7,(t). rt)M,(t). (7)

Сигнал на входе адаптивного фильтра 11 можно представить в виде

Vbn(t)M(t)+S5,(t)+n(t), (8)

где S(t)

10

- часть полезного . сигнала S(t), попавшая в полосу

пропускания uf усилителя 27.

Выходной сигнал адаптивного фильтра 11 имеет вид

Wj,(t)

бПг

,(t),

(9)

10

5

где U2(t) - изменяемая во времени импульсная характеристика адаптивного фильтра 11. . При воздействии сигнала ошибки J5 с выхода широкополосного усилителя 15 на управляющий вход адатив- ного фильтра 11 передаточная функция W2.(t) последнего изменяется таким образом, что в вычитателе 17 обеспечивается оптимальное (по критерию минимума среднеквадратической ошибки) подавление ПСП MgCt) во входном воздействии V,(t). Адаптивный фильтр 8 и адаптивный фильтр 11 идентичны, позто- му для адаптивного фильтра 11 спра0

ведливо

li(t)U(t).V,Jt)M2(t).(10)

Выходные сигналы адаптивных фильтров 8 и 11 складываются в сумматоре 14 и с его выхода поступают на инвертирующий вход вычитателя 17.

Таким образом, адаптивный фильтр 8 учитывает и устраняет дд вычитателя

5 ,7 возможные различия характеристик при проховдении ПСП M(t) от входа предлагаемого устройства через 16 до неинвертирующего входа вьгчитателя 17 и от входа устройства чер1з

- -устройства через

блок 7, адаптивный фильтр 8 и сумматор 14 до инвертирующего входа вычитателя 17. В то же время адаптивный фильтр 11 учитывает и устраняет до вычи.тателя 17 возможные различия характеристик при прохождении ПСПМ (t) от входа предлагаемого устройства через блок 16 до неинвертирующего входа вычитателя 17 и от входа предлагаемого устройства через блок 10, адаптивный фильтр 11 и сумматор 14

до инвертирующего входавычитателя 17.

Кроме того, необходимо устранить ПСП M(t), претерпевшие частотно- селективные искажения в блоке 16 с практи чески неибежной дисперсионно- стью его,характеристик. Адаптивные фильтры 8 и 11 также позволяют устранить влияние изменения характеристик

ПСП M(t) во времени (поскольку предполагается, что параметры ПСП 1. изменяются медленнее, чем параметры самого сигнала S(t), который по условию является существенно более широкополосным по сравнению с подавляемыми ПСП M(2(t).

На неинвертирующий вход .вычитателя 17 поступает через блок 16 входное . воздействие V)(t), а на инвертирующий вход - сигнал с выхода сумматора 14

v,(t)

v(t)

Z,(t) + Z(t). (11)

Из соотношений (1) и (11) следует, что выходной сигнал вычитателя 17 Vg(t) представить в вцце

160000012

тора 4 поступает на вход частотного детектора 1, а очищенный сигнал Vg,(t) (12) с выхода вычитателя 17 через второй вход коммутатора 18 поступает на вход блока 19 и на первый вход фазового детектора 22. Если же обе ПСП M,(t) отсутствуют, то входное воздействие V (t) с входа предлагаемого устройства через первый вход коммутатора 4 поступает на вход частотного детектора 1 и это же входное воздей- ствие Vi,(t) с выхода блока 16 через первый вход коммутатора 18 поступает на вход блока 19 и на первый вход фазового детектора 22.

На выходе частотного детектора 1 по результатам приема элемента сигнала S,(t) за тактовый интервал време- ни сформируется напряжение Uy.i3(t), которое является функцией отклонения значения мгновенной средней частоты принятого элемента сигнала ц от частоты настройки частотного детектора 1 ц

15

25

и

4D

(t) F,(f - „).

(13)

VBe(t)V,(t)-Z,(t)-Z2(t)-S(t)+M,(t)+ +Mj(t)+ii(t)-Z(t)-Z2(t). (12)

Адаптивные фильтры 8 и 11 настраиваются таким образом, чтобы минимизировать мощность Я следует, что минимизируется мощность разностей Р;, - Р, и Р . В этом случае, выходной сигнал сумматора 14 (t) является наилучшей оценкой (.г() в смысле минимума среднеквад- ратической ошибки.

Шумы, n(t) не коррелированные с ПСП ,(t), остаются нескомпенсированными. Сигнал S(t) проходит на вы- 35 где t - постоянная времени интегра30

Данное напряжение Uqj,(t) интегрируется за время тактового интервала интегратора 2, выходное напряжение которого равно

/V

о

UM,(t) - (t)dt, (16)

ход в.ычитателя 17 практически без искажения, так как передаточная функция для сигнала S(t) адаптивных фильтров 8 и 11 равна 1.

Для минимизации искажений сигнала S(t) необходимо повьш1ать отношение сигнал/шум

тора 2.

Напряжение U(t) с выхода интегратора 2 поступает на вход АЦП 3, который преобразует данное напряжение в

40 код, соответствующий мгновенной средней частоте f принятого теку1цего элемента сигнала S(t), который и выдается на первый выход предлагаемого устройства.

h,

S(t)

M,rt))+n(t)

(13)

на неинвертирующем входе вычитателя 17, а также уменьшить отношение сигнал/шум h на сигнальном входе адаптивного фильтра 8 и уменьшать отношение сигнал/шум hlj на сигнальном входе 11 адаптивного фильтра

и

4D

(t) F,(f - „).

(13)

где t - постоянная времени интегра

Данное напряжение Uqj,(t) интегрируется за время тактового интервала интегратора 2, выходное напряжение которого равно

/V

о

t - постоянная времени интегра

UM,(t) - (t)dt, (16)

тора 2.

Напряжение U(t) с выхода интегратора 2 поступает на вход АЦП 3, который преобразует данное напряжение в

код, соответствующий мгновенной средней частоте f принятого теку1цего элемента сигнала S(t), который и выдается на первый выход предлагаемого устройства.

Блок 16 производит задержку входного воздействия на время t., равное длительности обработки одного элемента сигнала S(t), с момента поступления его на вход предлагаемого устройства до момента вьщачи решения о

)

в виде кода с выхода АЦП 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема сигналов с частотным разделением каналов | 1988 |

|

SU1626410A1 |

| АППАРАТУРА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, УСТОЙЧИВАЯ К ВОЗДЕЙСТВИЮ МОЩНОЙ ЧМ ПОМЕХИ | 2001 |

|

RU2205506C1 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2117392C1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1987 |

|

SU1499523A2 |

| СИСТЕМА СВЯЗИ | 1985 |

|

SU1840076A1 |

| Устройство для контроля достоверности телеметрической информации | 1982 |

|

SU1035632A1 |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2115236C1 |

| РЕЖЕКТОРНЫЙ ФИЛЬТР | 2016 |

|

RU2641647C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2017 |

|

RU2660645C1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1518915A2 |

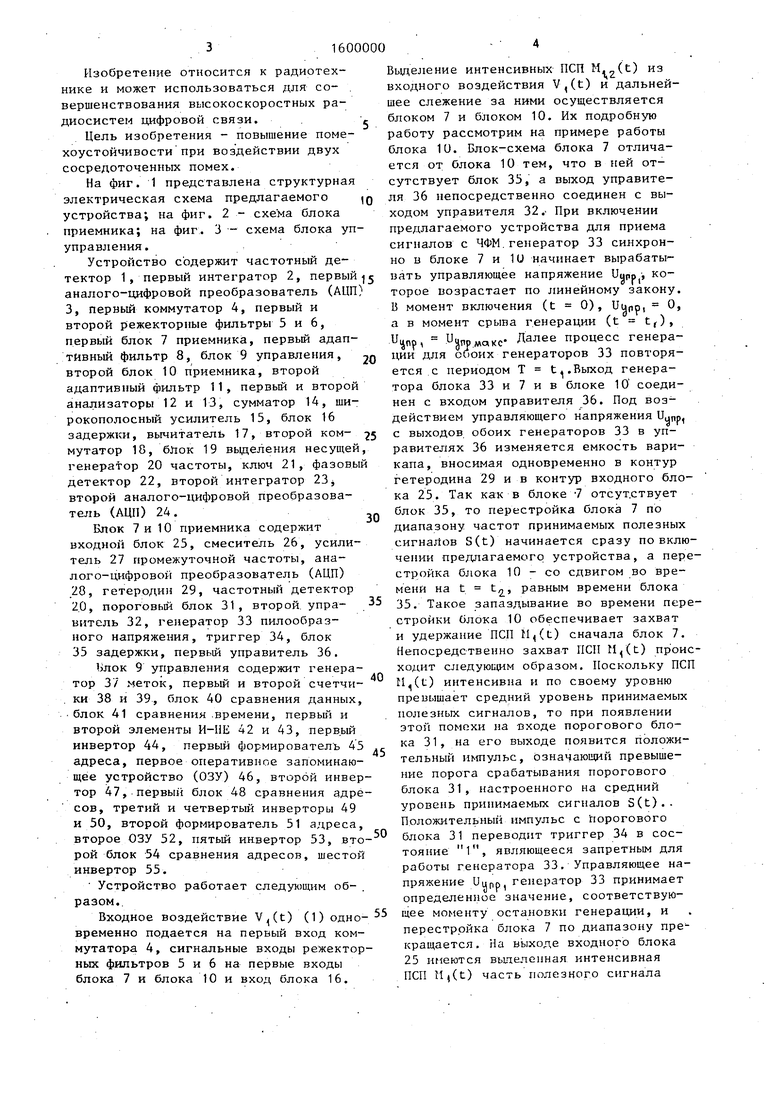

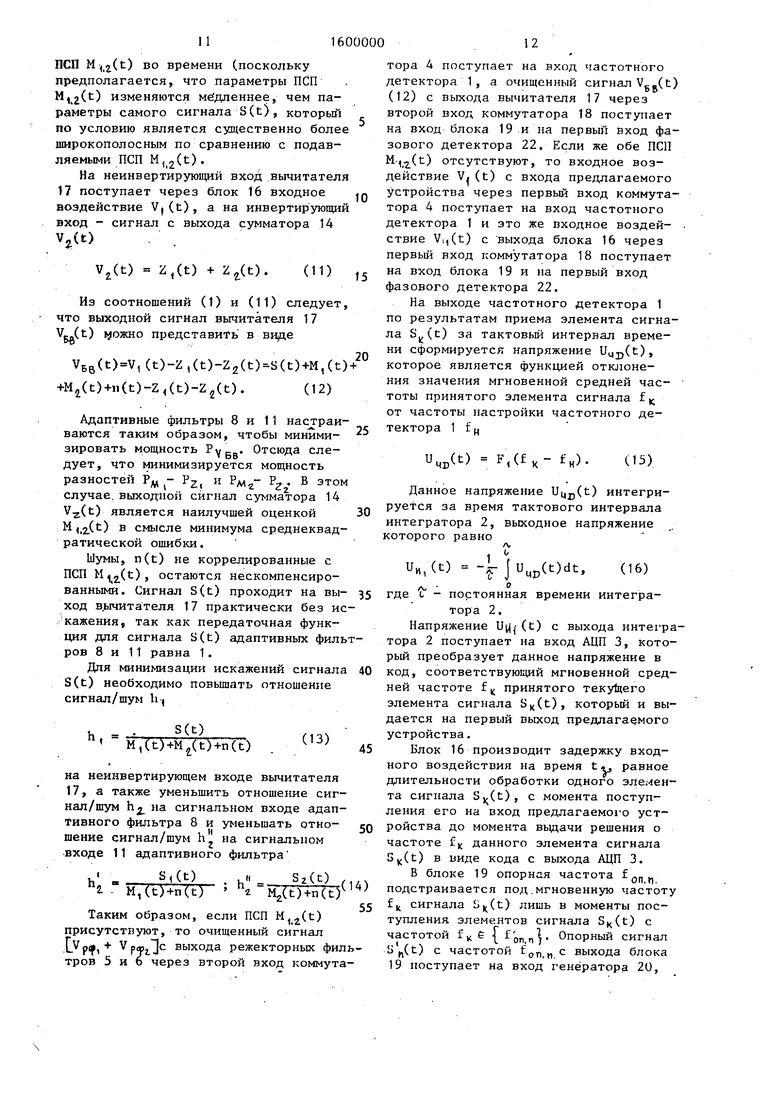

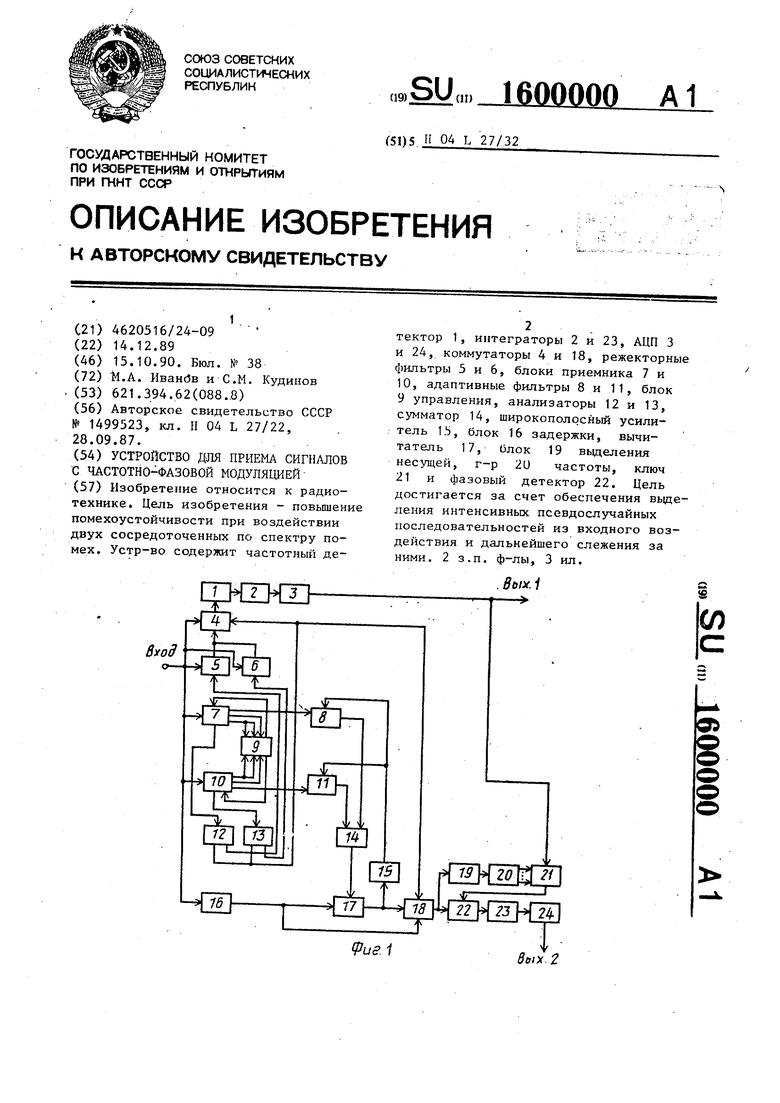

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости при воздействии двух сосредоточенных по спектру помех. Устройство содержит частотный детектор 1, интеграторы 2 и 23, АЦП 3 и 24, коммутаторы 4 и 18, режекторные фильтры 5 и 6, блоки приемника 7 и 10, адаптивные фильтры 8 и 11, блок управления 9, анализаторы 12 и 13, сумматор 14, широкополосный усилитель 15, блок задержки 16, вычитатель 17, блок выделения 19 несущей, г-р 20 частоты, ключ 21 и фазовый детектор 22. Цель достигается за счет обеспечения выделения интенсивных псевдослучайных последовательностей из входного воздействия и дальнейшего слежения за ними. 2 з.п. ф-лы, 3 ил.

Si(t)

i M,(t)+n(t)

h (14) г M(t)+n(t)

55

Таким образом, если ПСП M,(t) присутствуют, то очищенный сигнал ., + pftl выхода режекторных фильтров 5 и 6 через второй вход коммутаВ блоке 19 опорная частота f

on. п.

подстраивается под .мгновенную частоту ц сигнала |(t) лишь в моменты поступления элементов сигнала S(t) с частотой f к е {f on. Опорный сигнал Sf,(t) с ча:стотой ЕОЛ,ц выхода блока 19 поступает на вход генератора 20,

on.n. с

который преобразует данный сигнал Sy,(t) в множество опорных сигналов

(t). Каждый опорный сигнал Son отдельного выхода генератора 20 поступает на соответствующий сигнальный вход ключа 21. В ключе 21 под действием кода, содержащего информацию о мгновенной средней частоте f npHHHtoro элемента сигнала S(t), производится коммутация К-го сигнального входа, соответствующего данной частоте, на выход ключа 21. Опорный сигнал S (t), центральная частота которого равна мгновенной средней частоте f ц, принятого элемента сигнала S(t) с выхода ключа 21 поступает на второй вход фазового детектора 22, на первый вход которого поступает задержанный.на время t у текущий элемент сигнала S.(t) .j На вырсоде фазового детектйра 22 сформируется напряжение ), являющееся функцией разности фаз принятого ) и опорного tJon.n (t) сигналов

F,,(q),-Cf

on

).

(17)

Напряжение Ua,j,(t)

интегрируется

интегратором 23 и поступает на вход АЦП 24, который преобразует его в код, соответствующий фазе принятого элемента сигнала Sjt). Дальнейшая работа предлагаемого устройства для приема сигналов с ЧФМ происходит аналогично огшсанному циклу приема одного элемента сигнала .Ct). Формула изобретения

,

o , ч jn

25

0

5

0

5

0

блока выделения несущей и первым входом фазового детектора, выход которого через второй интегратор соединен с входом второго аналого-цифрового преобразователя, выход которого является вторым выводом устройства, выход блока вьщеления несущей через генератор частоты соединен с соответствующими входами ключа, выход которого соединен с вторым входом фазового детектора, а также первый адаптивный фильтр и первый анализатор,.о т л и- чающееся тем, что, с целью повышения помехоустойчивости при воздействии двух сосредоточенных помех, введены второй режекторный фильтр, блок управления, два блока приемника, второй адаптивный фильтр, второй анализатор и сумматор, причем первые входы второго режекторного фильтра первого и второго блоков приемников являются Входом устройства, выход второго режекторного фильтра соединен с вторым входом первого коммутатора, третий вход котор.ого и третий вход второго коммутатора соединены с первыми выходами первого и второго анализаторов, второй выход первого анализатора соединен с вторым входом пегрвого режекторного фильтра, второй выход второго анализатора соединен с вторым входом второго режекторного фильтра, первый выход первого блока приемника соединен с входом первого анализатора, вход второго анализатора соединен с первым выходом второго блока приемника, вторые- выходы первого и второго блоков приемника соединены соответственно с первыми входами первого и второго адаптивных фильтг ров, вторые входы которых соединены с выходом широкополосного усилителя, вход которого соединен с выходом вычитателя, второй вход которого соединен с выходом сумматора, входы которого соединены с выходами адаптивных фильтров, третий выход первого блока приемника соединен с первым входом блока управления, второй и третий входы которого соединены с четвертым выходом первого блока приемника, третий выход второго блока приемника,соединен с четвертым входом блока управления, пятый и шее- той входы которого соединены с четвертым выходом второго блока приемника, первый и второй выходы блока управления соединены соответственно с вторыми входами первого и второго блоков приемника.

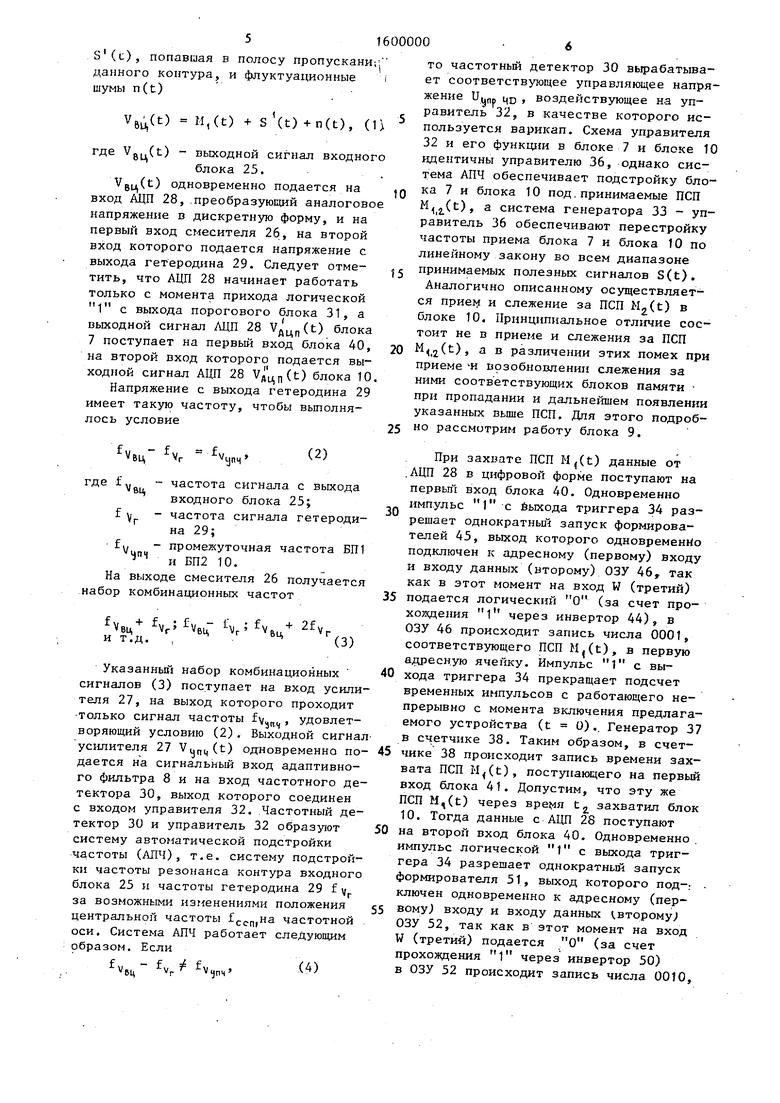

j приемника, первым выходом которого является выход входного блока, соеди ненный с первыми входами смесителя и аналого-цифрового преобразователя,выход которого является третьим выходом блока приемника, выход порогового блока соединен с вторым входом аналого- цифрового преобразователя и входом триггера, которьи является вторым входом блока приемника, четвертым выходом которого является выход триггера, соединенный через последовательно соединенные генератор пилообразного напряжения, первый управитель, блок задержки и гетеродин с вторым входом смесителя,, выход частотного детектора через второй управитель соединен с вторым входом входного блока, выход смесителя через усилитель промежуточной частоты соединен с входом частотного детектора и является вторым выходом блока приемника.

., г ° 5

0

5

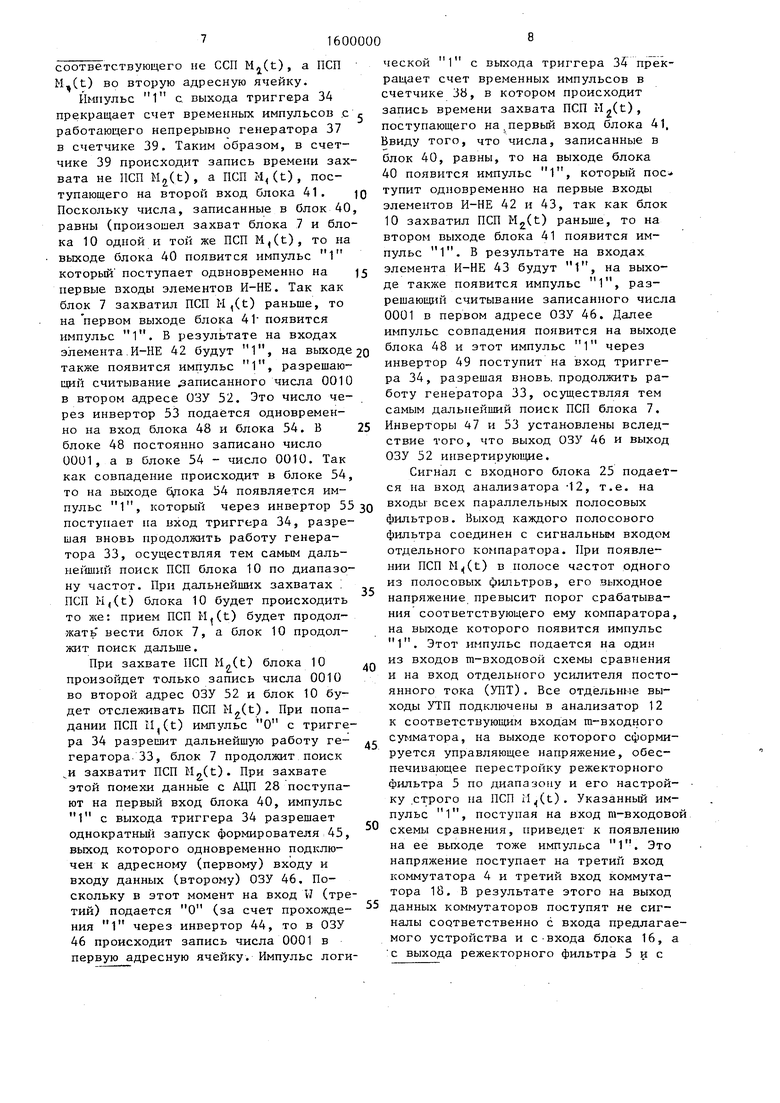

являются первым и четвертым входами блока управления, а выход соединен с первыми входами первого и второго элементов И-ПЕ, вторые входы которых соединены с соответствующими выходами блока сравнения времени, входы первого инвертора и первого формирователя адреса являются пятым входом блока управления, выход первого формирователя адреса соединен с первым и вторым входами первого оперативного запоминающего устройства, третий вход .которого соединен с выходом первого инвертора, соединенным с выходом второго элемента И-НЕ, выход первого оперативного запоминающего устройства через последовательно соединенные второй инвертор и первый блок сравнения адресов соединен с входом третьего инвертора, выход которого является первым выходом блока управления, входы четвертого инвертора и второго формирователя адреса являются вторьм входом блока управления, выход второго формирователя адреса соединен с первым и вторым входами второго оперативного запоминающего устройства, третий вход которого соединен с выходом четвертого инвертора, соединенным с выходом первого элемента И-НЕ, выход второго оперативного запоминающего устройства через питый инвертор соединен с входами первого, и второго блоков сравнения адресов, выход второго блока сравнения адресов соединен с входом шестого инвертора, выход которого является вторым выходом блока управления .

от

55 л-55 5/

отЗ

. 2

/г //

017

кз

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1987 |

|

SU1499523A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-10-15—Публикация

1989-12-14—Подача