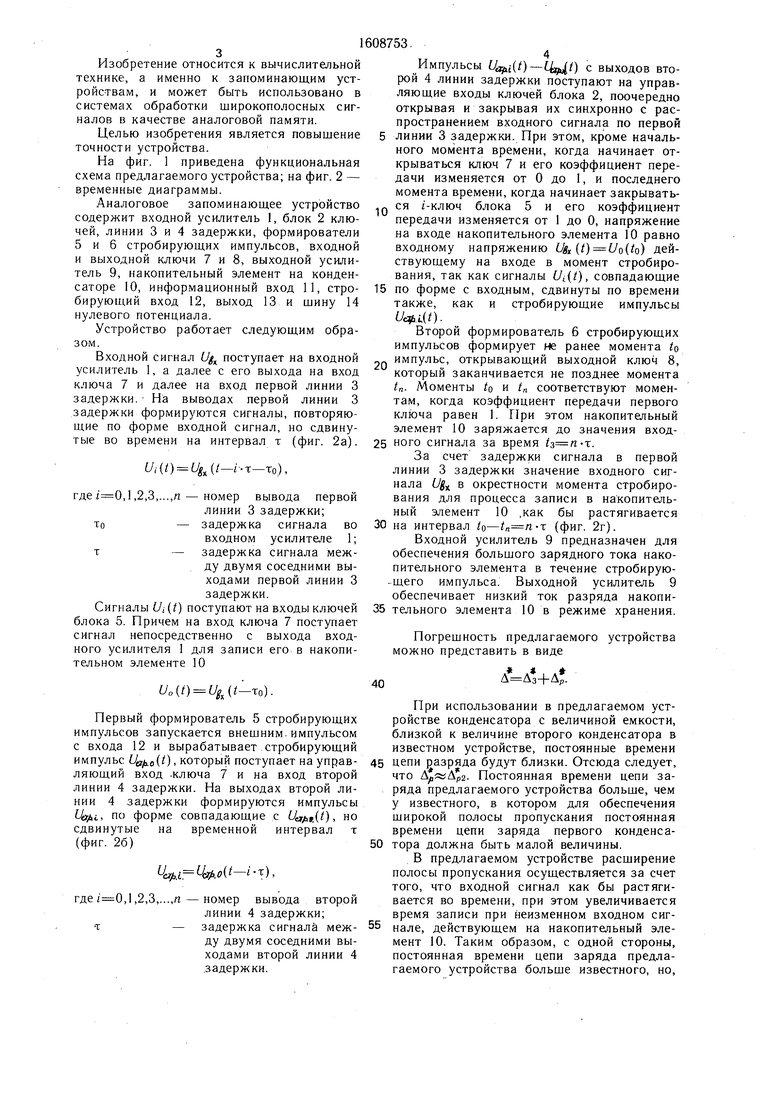

Фаг, 1

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в системах обработки широкополосных сигналов в качестве аналоговой памяти.

Целью изобретения является повышение точности устройства.

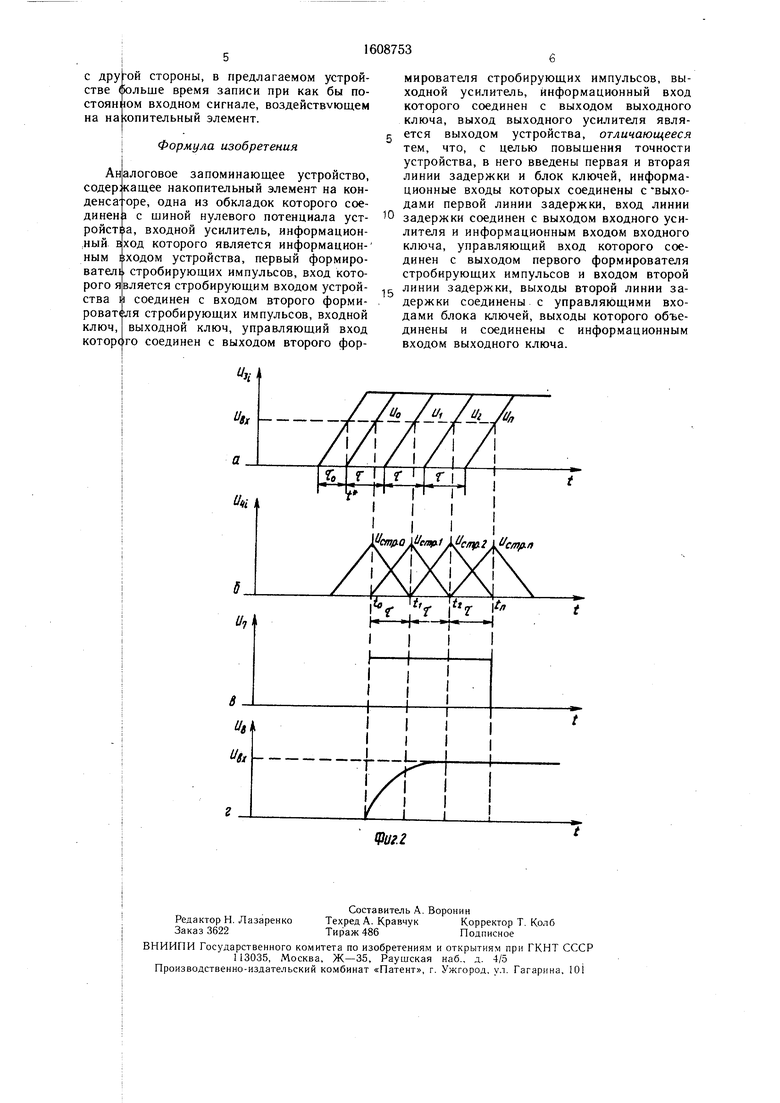

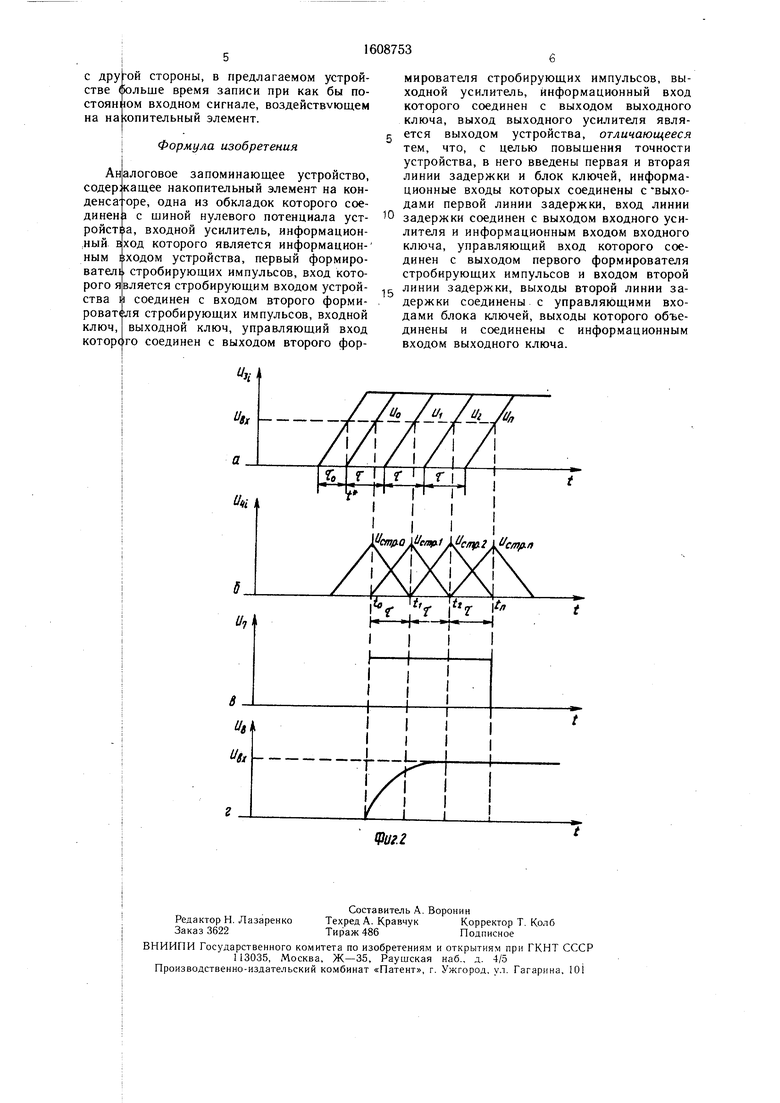

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы.

Аналоговое запоминающее устройство содержит входной усилитель 1, блок 2 ключей, линии 3 и 4 задержки, формирователи 5 и 6 стробирующих импульсов, входной и выходной ключи 7 и 8, выходной усилитель 9, накопительный элемент на конден4

„Импульсы ( с выходов второй 4 линии задержки поступают на управляющие входы ключей блока 2, поочередно открывая и закрывая их синхронно с распространением входного сигнала по первой 5 линии 3 задержки. При этом, кроме начального момента времени, когда начинает открываться клюя 7 и его коэффициент передачи изменяется от О до 1, и последнего момента времени, когда начинает закрывать- ..Q ся /-ключ блока 5 и его коэффициент передачи изменяется от 1 до О, напряжение на входе накопительного элемента 10 равно входному напряжению Ug (t) Uo{to) действующему на входе в момент стробиро- вания, так как сигналы Ui{t), совпадающие

саторе 10, информационный 11, стро- 15 по форме с входным, сдвинуты по времени также, как и стробирующие импульсы

.(0Второй формирователь 6 стробирующих импульсов формирует не ранее момента о

бирующий вход 12, выход 13 и шину 14 нулевого потенциала.

Устройство работает следующим образом.

Входной сигнал Ug поступает на входнойимпульс, открывающий выходной ключ 8,

ГТ МТР ПК 1 Q riQnoo г rn-Tvi ni но f ,,,„.,, ««-, .

усилитель 1, a далее с его выхода на вход ключа 7 и далее на вход первой линии 3 задержки. На выводах первой линии 3 задержки формируются сигналы, повторяющие по форме входной сигнал, но сдвинукоторыи заканчивается не позднее момента tn. Моменты IQ и tn соответствуют моментам, когда коэффициент передачи первого ключа равен 1. При этом накопительный элемент 10 заряжается до значения вход- тые во времени на интервал т (фиг. 2а). 25 ного сигнала за время .

За счет задержки сигнала в первой линии 3 задержки значение входного сигнала и в окрестности момента стробиро- вания для процесса записи в накопительный элемент 10 ,как бы растягивается 30 на интервал (фиг. 2г).

Входной усилитель 9 предназначен для обеспечения большого зарядного тока накопительного элемента в течение стробирую- -щего импульса. Выходной усилитель 9 обеспечивает низкий ток разряда накопиСигналы (//(/) поступают на входы ключей 35 тельного элемента 10 в режиме хранения, блока 5. Причем на вход ключа 7 поступает

Погрещность предлагаемого устройства можно представить в виде

То

Ui(t) U(t-i.-To),

,1,2,3,...,/ - номер вывода первой линии 3 задержки; задержка сигнала во входном усилителе 1; задержка сигнала между двумя соседними выходами первой линии 3 задержки.

сигнал непосредственно с выхода входного усилителя 1 для записи его в накопительном элементе 10

.

Uo(t Ug(t-T).

40

.

При использовании в предлагаемом уст- Первый формирователь 5 стробирующих ройстве конденсатора с величиной емкости, импульсов запускается внешним, импульсомблизкой к величине второго конденсатора в

с входа 12 и вырабатывает стробирующийизвестном устройстве, постоянные времени

импульс LJay(,o(0. который поступает на управ- 46 депи разряда будут близки. Отсюда следует, ляющий вход .ключа 7 и на вход второйчто . Постоянная времени цепи заряда предлагаемого устройства больше, чем у известного, в котором для обеспечения широкой полосы пропускания постоянная времени цепи заряда первого конденса- 50 тора должна быть малой величины.

В предлагаемом устройстве расширение полосы пропускания осуществляется за счет того, что входной сигнал как бы растягивается во времени, при этом увеличивается время записи при неизменном входном сигнале, действующем на накопительный элемент 10. Таким образом, с одной стороны,

линии 4 задержки. На выходах второй линии 4 задержки формируются импульсы U(rjti, по форме совпадающие с Uafet.(t), но сдвинутые на временной интервал т (фиг. 26)

,.

,1,2,3,...,rt - номер вывода второй

линии 4 задержки;

т- задержка сигнала меж- 55

ду двумя соседними выходами второй линии 4 задержки.

постоянная времени цепи заряда предлагаемого устройства больше известного, но.

608753.

4

„Импульсы ( с выходов второй 4 линии задержки поступают на управляющие входы ключей блока 2, поочередно открывая и закрывая их синхронно с распространением входного сигнала по первой 5 линии 3 задержки. При этом, кроме начального момента времени, когда начинает открываться клюя 7 и его коэффициент передачи изменяется от О до 1, и последнего момента времени, когда начинает закрывать- ..Q ся /-ключ блока 5 и его коэффициент передачи изменяется от 1 до О, напряжение на входе накопительного элемента 10 равно входному напряжению Ug (t) Uo{to) действующему на входе в момент стробиро- вания, так как сигналы Ui{t), совпадающие

15 по форме с входным, сдвинуты по времени также, как и стробирующие импульсы

40

.

постоянная времени цепи заряда предлагаемого устройства больше известного, но.

с другой стороны, в предлагаемом устройстве (юльше время записи при как бы постоянном входном сигнале, воздействующем на на {опительный элемент.

;Формула изобретения

Аналоговое

содер: денса динен

запоминающее устройство кащее накопительный элемент на кон- оре, одна из обкладок которого сое- 1 с щиной нулевого потенциала устройства, входной усилитель, информацион- вход которого является информационвходом устройства, первый формиро- стробирующих импульсов, вход кото- является стробирующим входом устрой- соединен с входом второго форми- роват я стробирующих импульсов, входной выходной ключ, управляющий вход го соединен с выходом второго фор,ный

ным

вател

рого

ства

ключ, котор(

мирователя стробирующих импульсов, выходной усилитель, информационный вход которого соединен с выходом выходного ключа, выход выходного усилителя является выходом устройства, отличающееся тем, что, с целью повыщения точности устройства, в него введены первая и вторая линии задержки и блок ключей, информационные входы которых соединены с выхо- дами первой линии задержки, вход линии задержки соединен с выходом входного усилителя и информационным входом входного ключа, управляющий вход которого соединен с выходом первого формирователя стробирующих импульсов и входом второй

линии задержки, выходы второй линии задержки соединены с управляющими входами блока ключей, выходы которого объединены и соединены с информационным входом выходного ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения нелинейности закона модуляции частоты сигналов | 1984 |

|

SU1228035A1 |

| Устройство управления пьезодвигателем | 1990 |

|

SU1737407A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1084897A1 |

| Квадратор | 1982 |

|

SU1084824A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Устройство компенсации помех при сдвоенном приеме радиосигналов | 1987 |

|

SU1406801A1 |

| Стохастический стробоскопический измеритель разности фаз | 1986 |

|

SU1413549A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Устройство для воспроизведенияцифРОВОй иНфОРМАции | 1979 |

|

SU838713A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки широкополосных сигналов в качестве аналоговой памяти. Цель изобретения - повышение точности устройства. Для этого в устройство введены две линии 3,4 задержки и блок 2 ключей. Усиленный входной сигнал с выхода усилителя 1 через ключ 7 поступает на вход первой линии 3 задержки, на которой формируются сигналы, повторяющие по форме входной сигнал, но сдвинутые во времени. На второй линии 4 формируются импульсы, по форме совпадающие со стробирующими импульсами, но сдвинутые во времени. Расширение полосы пропускания осуществляется за счет того, что входной сигнал как бы растягивается во времени. 2 ил.

| Аналоговое запоминающее устройство | 1979 |

|

SU832602A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| АвтЬрское свидетельство СССР № 756487, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-11-23—Публикация

1989-01-04—Подача