Изобретение относится к импульсной и вычислительной технике и может быть использовано, например, при построении статистических анализаторов, цифровых измерительных приборов и др.

Целью изобретения является расширение функциональных возможностей устройств за счет определения величины отношения количества импульсов в двух импульсных потоках.

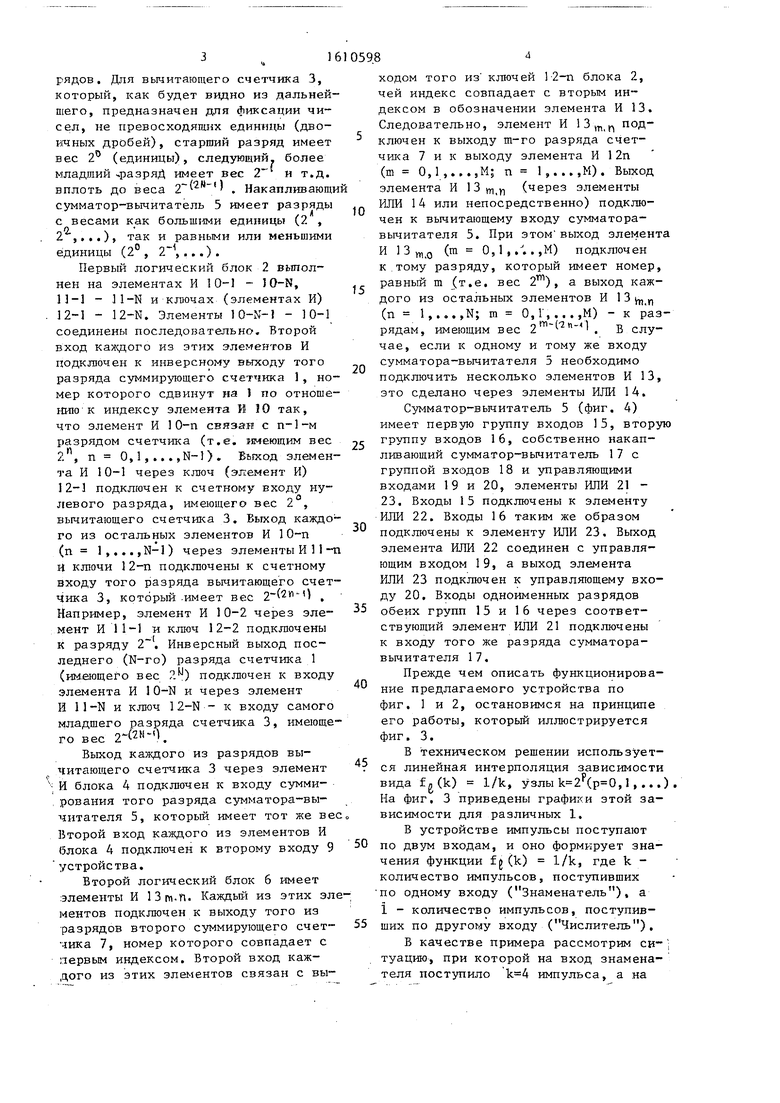

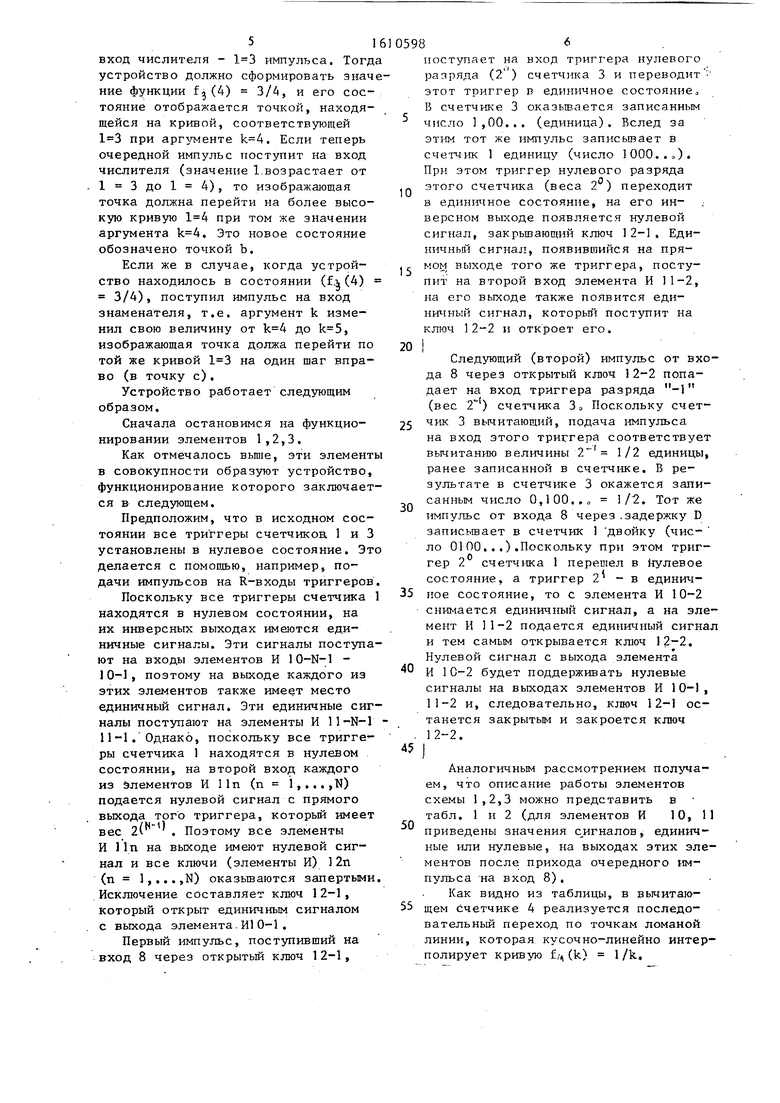

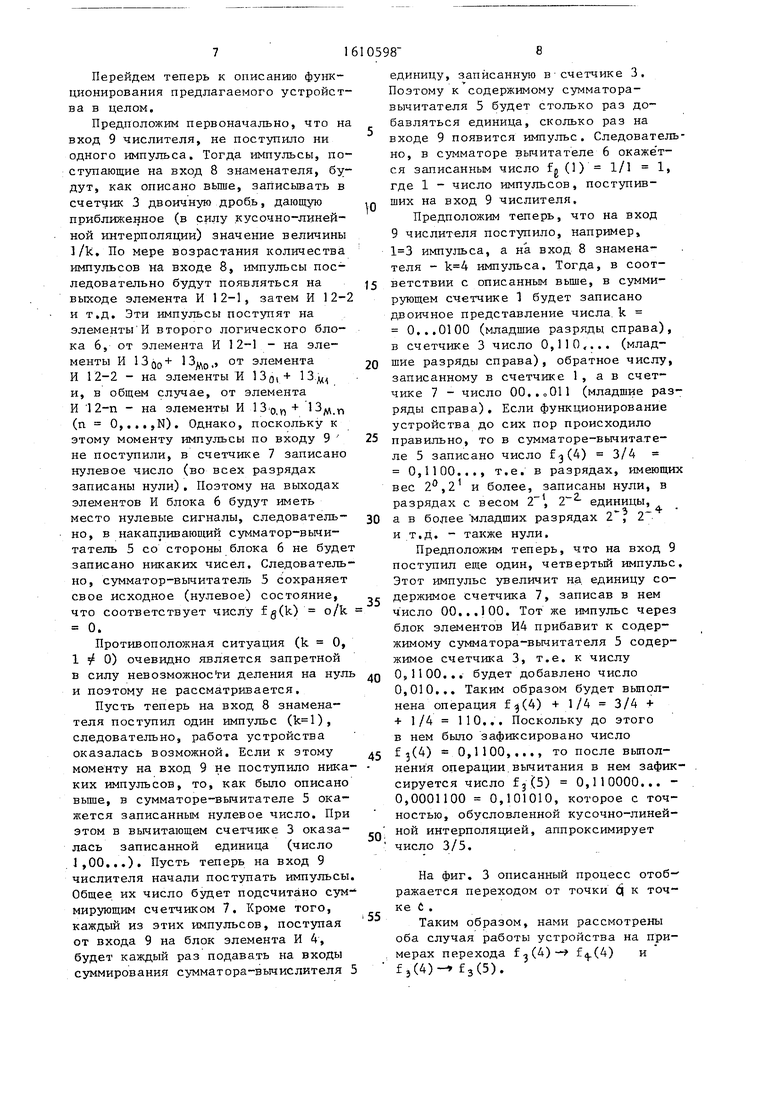

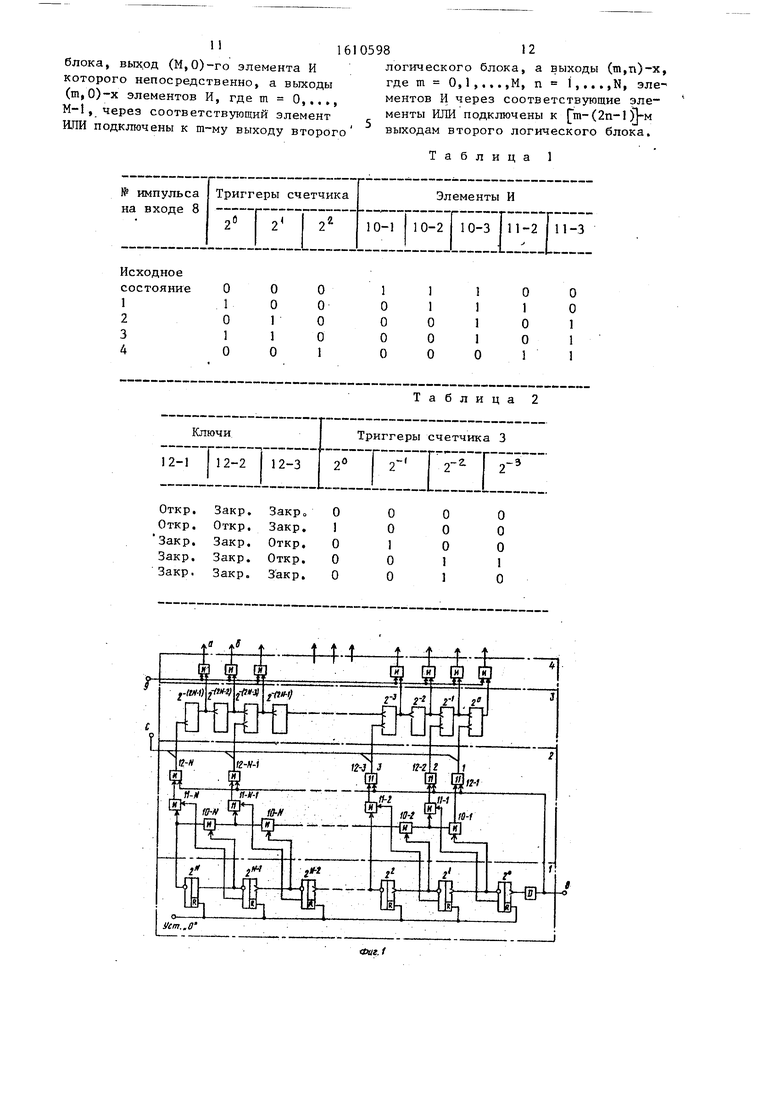

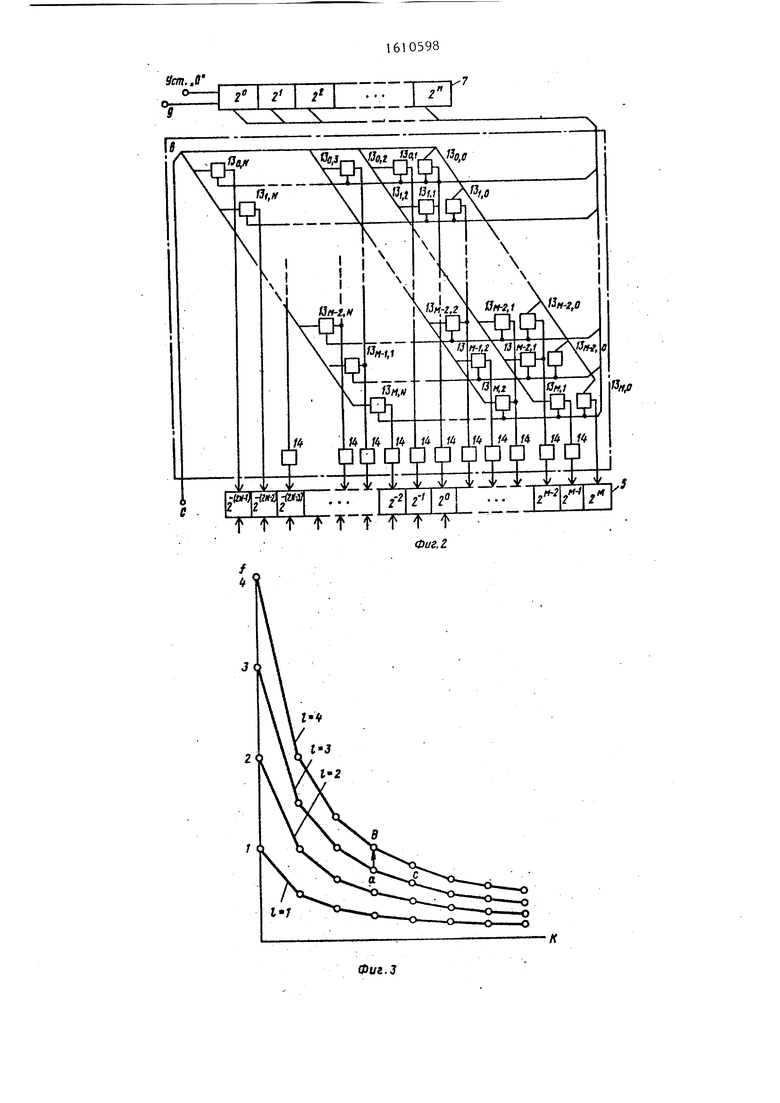

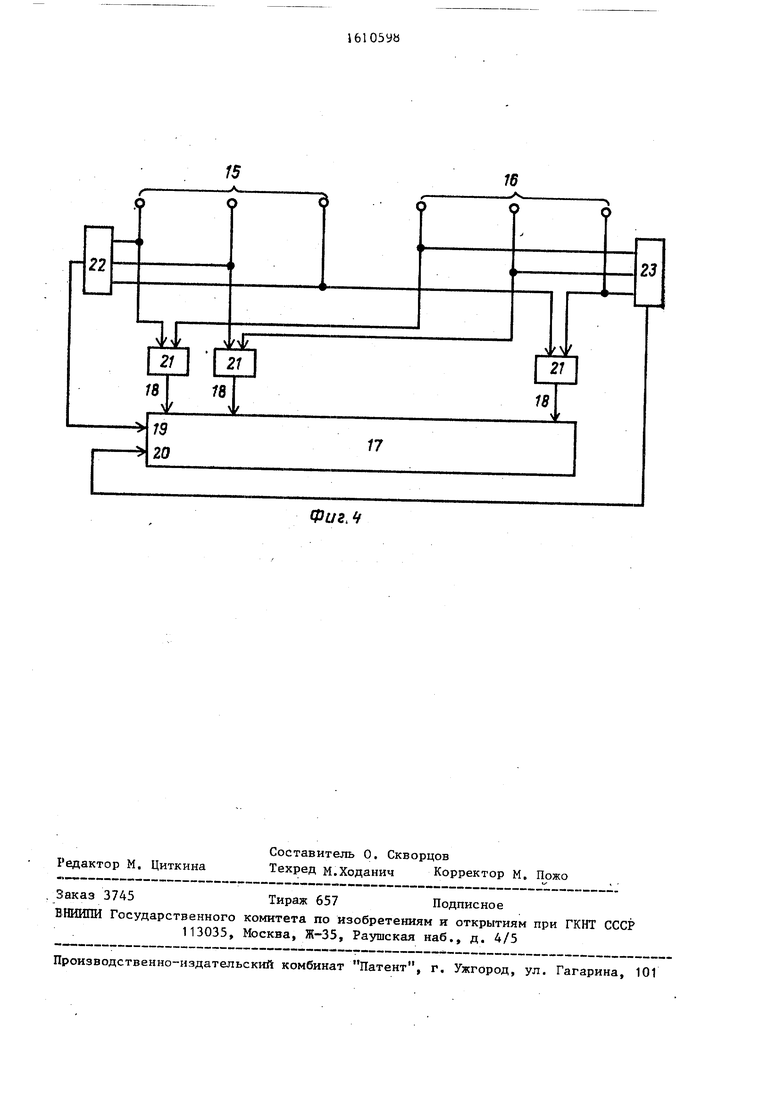

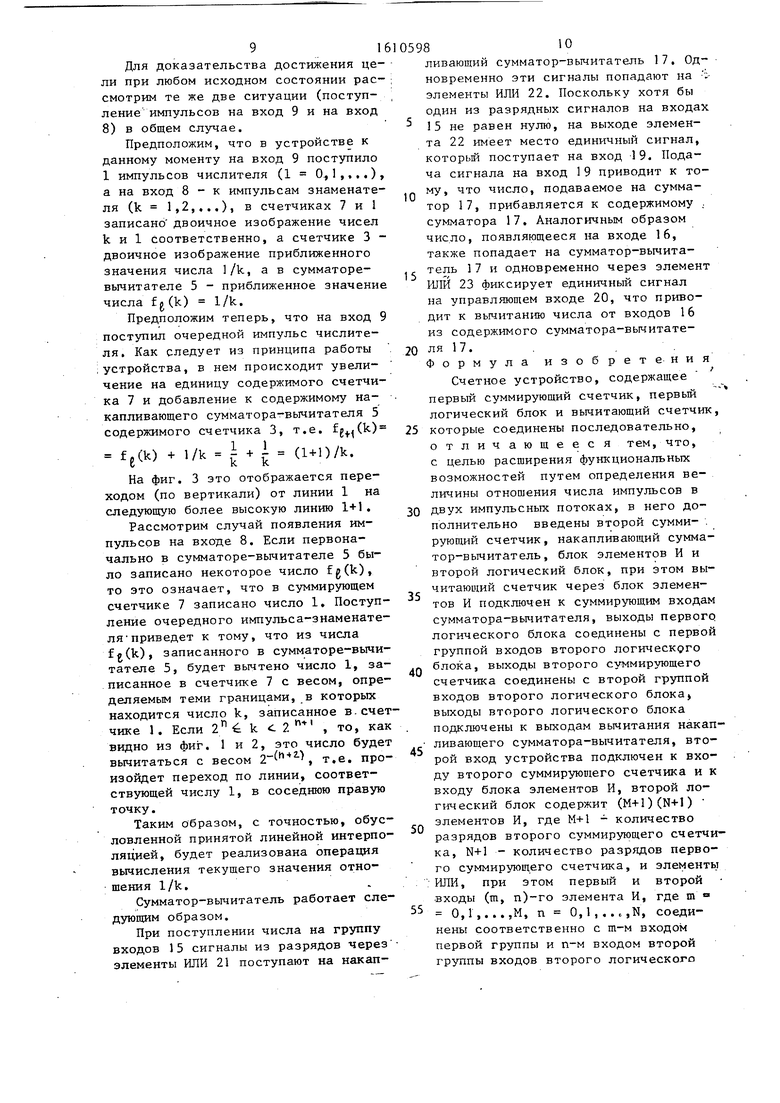

На фиг. 1 и 2 показана функциональная схема предлагаемого устройства; на фиг. 3 - диаграмма, поясняющая принцип работы устройства; на фиг, 4 - схема накапливающего сумма- тора-вычитателя.

. Устройство содержит первый суммирующий счетчик 1, первый логический

.блок 2, вычитающий счетчик 3, блок элементов И 4, накапливающий сумматор- вычитатель 5, второй логический блок 6 и второй суммирующий счетчик 7. Кроме того, устройство имеет первый вход 8 (вход знаменателя) и второй вход 9 (вход числителя).Первый суммирующий счетчик 1, первый логический блок 2 и вычитающий счетчик 3 соединены последовательно.

На фиг. 1 и 2 указаны веса разрядов накапливающих счетчиков 1 и 7, счетчика 3 и сумматора-вычитателя 5, Как известно, младший (нулевой) разряд имеет вес 2, следующий - вес 2 и т.д. вплоть до разряда 2 у счетчика 1 и до разряда 2 у счетчика 7. Таким образом, счетчик 1 имеет (N+1) разрядов, а счетчик 7 - (М+1) разО

сд

со

ОС

рядов. Для вычитающего счетчика 3, который, как будет видно из дальней- niero, предназначен для фиксации чисел, не превосходящих единицы (двоичных дробей), старший разряд имеет вес 2 (единицы), следующий, более младший фазряД имеет вес 2 и т.д. вплоть до веса . Накапливающий

сумматор-вычитатель 5 имеет разряды с весами как большими единицы (2 , 2 ,...), так и равными или меньшими единицы (2°, 2...).

Первый логический блок 2 выполнен на элементах И 10-1 - 10-N, П-1 - H-N и ключах (элементах И) 12-1 - 12-N. Элементы 10-N- - 10-1 соединены последовательно. Второй вход кахсдого из этих элементов И подключен к инверсному выходу того разряда суммирующего счетчика 1, номер которого сдвинут на 1 по отношению к индексу элемента И 10 так, что элемент И 10-п связан с п-1-м разрядом счетчика (т.е. имеющим вес 2, п 0,1N-1). Выход элемента И 10-1 через ключ (элемент И)

12-1 подключен к счетному входу нуп о левого разряда, имеющего вес Z ,

вычитающего счетчика 3. Выход каждого из остальных элементов И 10-п (п 1 ,... ,N-1) через элементы И 11 --п И ключи 12-п подключены к счетному входу того разряда вычитающего счетчика 3, который .имеет вес . Например, элемент И 10-2 через элемент И 11-1 н ключ 12-2 подключены к разряду . Инверсный выход последнего (N-ro) разряда счетчика 1 (имеющего вес 2) подключен к входу элемента И 10-N и через элемент И 11-N и ключ 12-N - к входу самого младшего разряда счетчика 3, имеющего вес 2(2М-0.

Выход каждого из разрядов вычитающего счетчика 3 через элемент И блока 4 подключен к входу суммирования того разряда сумматора-вы- читателя 5, который имеет тот же ве Второй вход каждого из элементов И (Злока 4 подключен к второму входу 9 устройства.

Второй логический блок 6 имеет элементы И Пт-П. Каждый из этих элментов подключен к выходу того из разрядов второго суммирующего счетчика 7, номер которого совпадает с первым индексом. Второй вход каждого из этих элементов связан с вы-

0

5

0

598

ходом того из ключей l-2-n блока 2, чей индекс совпадает с вторым индексом в обозначении элемента И 13. Следовательно, элемент И 13, под- ключен к выходу т-го разряда счетчика 7 и к выходу элемента И 12п (т 0,1,...,М; п 1,...,М). Выход элемента И ,п (через элементы ИЛИ 14 или непосредственно) подключен к вычитающему входу сумматора- вычитателя 5. При этом выход элемента И 1 3 (m 0,1,.. .,М) подключен к тому разряду, который имеет номер, равньш m (т.е. вес 2), а выход каждого из остальных элементов И 1 3 у, (п 1,...,N; m 0,1,...,М) - к разрядам, имеющим вес . В случае, если к одному и тому же входу сумматора-вычитателя 5 необходимо подключить несколько элементов И 13, это сделано через элементы ИЛИ 14.

Сз мматор-вычитатель 5 (фиг. 4) имеет первую группу входов 15, вторую группу входов 16, собственно накапливающий сумматор-вычитатель 1 7 с группой входов 18 и управляющими входами 19 и 20, элементы ИЛИ 21 - 23. Входы 15 подключены к элементу ИЛИ 22. Входы 16 таким же образом подключены к элементу ИЛИ 23. Выход элемента ИЛИ 22 соединен с управляющим входом 19, а выход элемента ИЛИ 23 подключен к управляющему входу 20. Входы одноименных разрядов обеих групп 15 и 16 через соответствующий элемент ИЛИ 21 подключены к входу того же разряда сумматора- вычитателя 17.

Прежде чем описать функционирование предлагаемого устройства по фиг. 1 и 2, остановимся на принципе его работы, который иллюстрируется фиг. 3.

В техническом рещении используется линейная интерполяция зависимости вида fg(k) 1/k, узлы (,1,...). На фиг. 3 приведены графики этой зависимости для различных 1.

В устройстве импульсы поступают

5

0

5

0

5

0

по двум входам, и оно формирует значения функции fJ(k) 1/k, где k - количество импульсов, поступивших ПО одному входу (Знаменатель) а 1 - количество импульсов, поступив- 5 ших по другому входу (Числитель).

В качестве примера рассмотрим си- туацию, при которой на вход знаменателя поступило импульса, а на

51

вход числителя - импульса. Тогда устройство должно сформировать значение функции f (4) 3/4, и его состояние отображается точкой, находящейся на кривой, соответствующей при аргументе . Если теперь очередной импульс поступит на вход числителя (значение 1.возрастает от 1 3 до 1 4), то изображающая точка должна перейти на более высокую кривую при том же значении аргумента , Это новое состояние обозначено точкой Ь.

Если же в случае, когда устройство находилось в состоянии (л(4) 3/4), поступил импульс на вход знаменателя, т.е. аргумент k изменил свою величину от до изображающая точка дрлжа перейти по той же кривой на один шаг вправо (в точку с).

Устройство работает следующим образом.

Сначала остановимся на функционировании элементов 1,2,3.

Как отмечалось вьш1е, эти элементы в совокупности образуют устройство, функционирование которого заключается в следующем.

Предположим, что в исходном состоянии все триггеры счетчиков. 1 и 3 установлены в нулевое состояние. Это делается с помощью, например, подачи импульсов на R-входы триггеров.

Поскольку все триггеры счетчика 1 находятся в нулевом состоянии, на их инверсных выходах имеются единичные сигналы. Эти сигналы поступают на входы элементов И 10-N-1 - 10-1, поэтому на выходе каждого из этих элементов также имеет место единичный сигнал. Эти единичные сигналы поступают на элементы И 11-N-1 11-1. Однако, поскольку все триггеры счетчика 1 находятся в нулевом состоянии, на второй вход каждого иэ Элементов И 11п (п 1,...,N) подается нулевой сигнал с прямого выхода того триггера, которьй имеет вес 21 . Поэтому все элементы И lln на выходе имеют нулевой сигнал и все ключи (элементы И) 12п (п ,,..,N) оказьшаются запертыми Исключение составляет ключ I2-1, который открыт единичным сигналом с вьпсода элемента И1 0-1 .

Первый импульс, поступивщий на ;вход 8 через открытьш ключ 12-1,

598fпоступает на вход триггера нулевого разряда (2) счетчика 3 и переводит этот триггер в единичное состояние, В счетчике 3 оказьшается записанным число ,00... (единица). Вслед за этим тот же импульс записывает в счетчик 1 единицу (число 1000.. о). При этом триггер нулевого разряда этого счетчика (веса 2 ) переходит в единичное состояние, на его инверсном выходе появляется нулевой сигнал, закрьшающий ключ 12-1. Еди- иичньм сигнал, появившийся на прямом выходе того же триггера, поступит на второй вход элемента И 11-2, на его выходе также появится единичный сигнал, которьш поступит на ключ 12-2 и откроет его.

0

Следующий (второй) импульс от входа 8 через открытый кл}оч 1 2-2 попадает на вход триггера разряда -1 (вес 2) счетчика За Поскольку счетчик 3 вычитающий, подача импульса на вход этого триггера соответствует вычитанию величины 1/2 единицы, ранее записанной в счетчике. В результате в счетчике 3 окажется записанным число 0,100.,(, 1/2. Тот же импульс от входа 8 через .задержку D записьшает в счетчик 1 двойку (число 0100...).Поскольку при этом триггер 2 счетчика 1 перешел в Нулевое состояние, а триггер 2 - в единичное состояние, то с элемента И 10-2 снимается единичный сигнал, а на элемент И 11-2 подается единичный сигнал и тем самым открывается ключ 12-2, Нулевой сигнал с выхода элемента И 10-2 будет поддерживать нулевые сигналы на выходах элементов И 10-1, 11-2 и, следовательно, ключ 12-1 останется закрытым и закроется ключ 12-2.

)

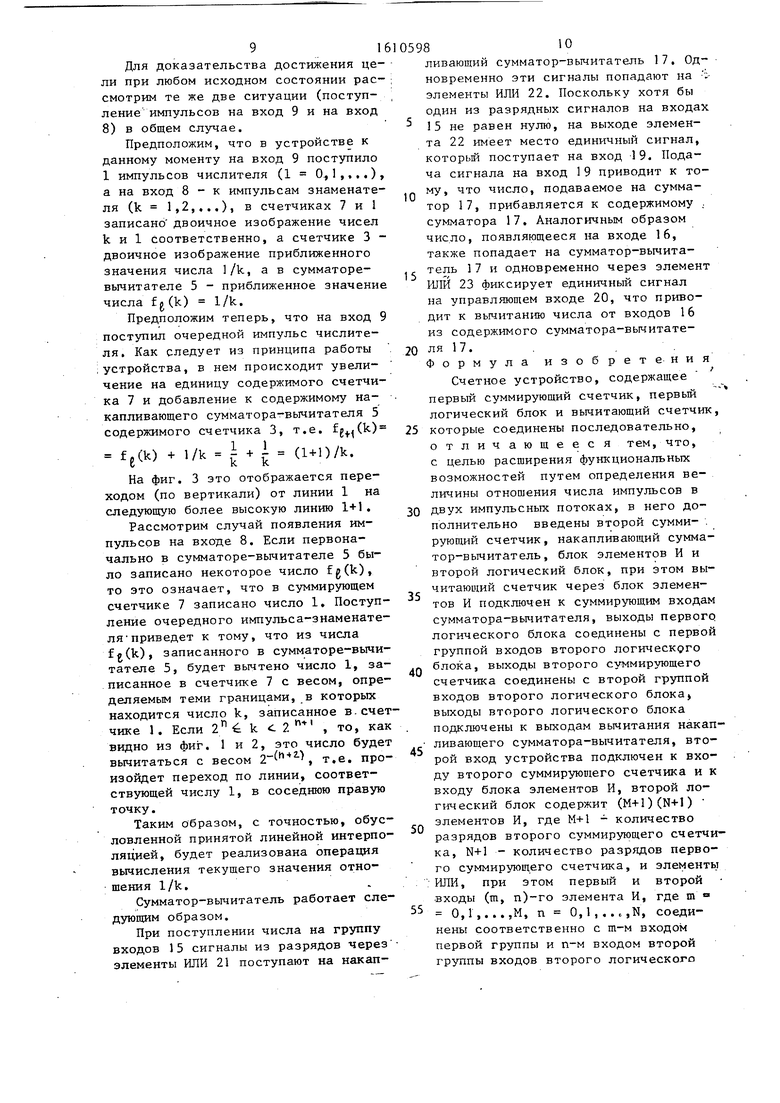

Аналогичным рассмотрением получаем, что описание работы элементов схемы 1,2,3 можно представить в табл. 1 и 2 (для элементов И 10, 11 приведены значения с игналов, единичные или нулевые, на выходах этих элементов после прихода очередного импульса на вход 8),

Как видно из таблицы, в вычитающем счетчике 4 реализуется последовательный переход по точкам ломаной линии, которая кусочно-линейно интерполирует кривую f/n (k) 1 /k.

Перейдем теперь к описанию функционирования предлагаемого устройства в целом.

Предположим первоначально, что на вход 9 числителя, не поступило ни одного импульса. Тогда импульсы, поступающие на вход 8 знаменателя, будут, как описано выше, записьюать в счетчик 3 двоичную дробь, дающую приближенное (в силу кусочно-линейной интерполяции) значение величины 1/k, По мере возрастания количества импульсов на входе 8, импульсы последовательно будут появляться на выходе элемента И 12-1, затем И 12и т.д. Эти импульсы поступят на элементы И второго логического блока 6, от элемента И 12-1 - на элементы И 13(55+ .

от элемента

И Г2-2 - на элементы И 13о,+ 13ji и, в общем случае, от элемента И 2-п - на элементы И , + 13дд у (п 0,..,,N). Однако, поскольку к этому моменту импульсы по входу 9 не поступили, в счетчике 7 записано нулевое число (во всех разрядах записаны нули). Поэтому на выходах элементов И блока 6 будут иметь место нулевые сигналы, следовательно, в накапливающий сумматор-вычи- татель 5 со стороны блока 6 не буде записано никаких чисел. Следовательно, сумматор-вычитател1: 5 сохраняет свое исходное (нулевое) состояние, что соответствует числу fg(k) o/k 0.

Противоположная ситуация (k О, ) очевидно является запретной в силу невозможнос ги деления на нул и поэтому не рассматривается.

Пусть теперь на вход 8 знаменателя поступил один импульс (), следовательно, работа устройства оказалась возможной. Если к этому моменту на вход 9 не поступило никаких импульсов, то, как было описано выше, в сумматоре-вычитателе 5 окажется записанным нулевое число. При этом в вычитающем счетчике 3 оказалась записанной единица (число .1,00.,.). Пусть теперь на вход 9 числителя начали поступать импульсы Общее их число будет подсчитано суммирующим счетчиком 7, Кроме того, каждый из этих импульсов, поступая от входа 9 на блок элемента И 4, будет каждый раз подавать на входы суммирования сумматора-вычислителя

единицу, записанную в-счетчике 3, Поэтому к содержимому сумматора- вычитателя 5 будет столько раз добавляться единица, сколько раз на входе 9 появится импульс. Следовательно, в сумматоре вычитателе 6 окаже т- ся записанным число fg (1) 1/1 1, где 1 - число импульсов, поступив- щих на вход 9 числителя.

Предположим теперь, что на вход 9 числителя поступило, например, импульса, а на вход 8 знаменателя - импульса. Тогда, в соответствии с описанным выше, в суммирующем счетчике 1 будет записано двоичное представление числа, k 0...0100 (младщив разряды справа), в счетчике 3 число 0,110,.., (младшие разряды справа), обратное числу, записанному в счетчике 1, а в счетчике 7 - число 00..о011 (младщие разряды справа), Если функционирование устройства до сих пор происходило

правильно, то в сумматоре-вычита.те- ле 5 записано число fj() - 3/4 0,1100,.., т.е. в разрядах, имеющих вес 2,2 и более, записаны нули, в

45

разрядах с весом 2, 2 единицы,

а в более младщих разрядах 2, 2 и т.д. - также нули.

Предположим теперь, что на вход 9 поступил еще один, четвертый импульс. Этот импульс увеличит на. единицу содержимое счетчика 7, записав в нем число 00...100. Тот же импульс через блок элементов И4 прибавит к содержимому сумматора-вычитателя 5 содержимое счетчика 3, т.е. к числу

0,1100.., будет добавлено число

0,010... Таким образом будет выполнена операция (4) +1/4 3/4 + + 1/4 110,,, Поскольку до этого в нем было зафиксировано число

з() 0,1100,,.,, то после выполнения операции.вычитания в нем зафиксируется число f3 (5) 0,110000... - 0,0001100 0,101010, которое с точностью, обусловленной кусочно-линей50

ной интерполяцией, аппроксимирует число 3/5.

На фиг. 3 описанный процесс отоб- ражается переходом от точки dj к точ

Таким образом, нами рассмотрены

оба случая работы устройства на при- мерах перехода f(4)- f(4) и

fjC)

3(5).

916

Для доказательства достижения цели при любом исходном состоянии рас- смотрим те же две ситуации (поступ- ление импульсов на вход 9 и на вход 8) в общем случае.

Предположим, что в устройстве к данному моменту на вход 9 поступило 1 импульсов числителя (1 ,.,.), а на вход 8 - к импульсам знаменателя (k 1,2,...) в счетчиках 7 и 1 записано двоичное изображение чисел k и 1 соответственно, а счетчике 3 - двоичное изображение приближенного значения числа 1/k, а в сумматоре- вычитателе 5 - приближенное значение числа fg(k) 1/k.

Предположим теперь, что на вход 9 поступил очередной импульс числителя. Как следует из принципа работы iустройства, в нем происходит увеличение на единицу содержимого счетчика 7 и добавление к содержимому на- капливающего сумматора-вычитателя 5 содержимого счетчика 3, т.е. fj(k)

fg(k) f 1/k i (l+l)/k.

Ha фиг. 3 это отображается переходом (по вертикали) от линии 1 на следующую более высокую линию 1+1.

Рассмотрим случай появления импульсов на входе 8. Если первоначально в сумматоре-вычитателе 5 было записано некоторое число fg(k), то это означает, что в суммирующем счетчике 7 записано число 1. Поступление очередного импульса-знаменателя -приведет к тому, что из числа ffl(k), записанного в сумматоре-вычитателе 5, будет вычтено число 1, записанное в счетчике 7 с весом, определяемым теми границами, в которых находится число k, записанное в.счетчике 1. Если 2 k с , то, как видно из фиг. 1 и 2, это число будет вычитаться с весом т.е. произойдет переход по линии, соответствующей числу 1, в соседнюю правую

точку.

Таким образом, с точностью, обусловленной принятой линейной интерполяцией, будет реализована операция вычисления текущего значения отношения 1/k.

Сумматор-вьшитатель работает следующим образом.

При поступлении числа на группу входов 15 сигналы из разрядов через элементы ИЛИ 21 поступают на накап0

59810

ливающий сумматор-вычитатель 17. Од- новременно эти сигналы попадают на ;- элементы ИЛИ 22. Поскольку хотя бы один из разрядных сигналов на входах 5 15 не равен нулю, на выходе элемента 22 имеет место единичный сигнал, которьй поступает на вход 19. Подача сигнала на вход 19 приводит к тому, что число, подаваемое на сумматор 17, прибавляется к содержимому ; сумматора 17. Aнaлoг гчным образом число, появляющееся на входе 16, также попадает на сумматор-вычитатель 17 и одновременно через элемент ИЛИ 23 фиксирует единичный сигнал на управляющем входе 20, что приводит к вычитанию числа от входов 16 из содержимого сумматора-вьиитате0 ля 17.

Формула изобретения

Счетное устройство, содержащее первый суммирующий счетчик, первый логический блок и вычитающий счетчик,

5 которые соединены последовательно, отличающееся тем, что, с целью расширения функциональных возможностей путем определения величины отношения числа импульсов в

30 двух импульсных потоках, в него дополнительно введены второй сумми- . рующий счетчик, накапливающий сумматор-вычитатель, блок элементов И и второй логический блок, при этом вычитающий счетчик через блок элементов И подключен к суммирующим входам сумматора-вьмитателя, выходы первого логического блока соединены с первой группой входов второго логического блока, выходы второго суммирующего счетчика соединены с второй группой входов второго логического блока выходы второго логического блока подключены к выходам вычитания накапливающего сумматора-вычитателя, второй вход устройства подключен к входу второго суммирующего счетчика и к входу блока элементов И, второй логический блок содержит (M+1)(N+1) элементов И, где М+1 - количество разрядов второго суммирующего счетчика, N+1 - количество разрядов первого суммирующего счетчика, и элементы ИЛИ, при этом первый и второй входы (т, п)-го элемента И, где m

55 0,1,...,М, п 0,1,...,N, соединены соответственно с т-м входом первой группы и п-м входом второй группы входов второго логического

35

45

50

161059812

блока, выход (М,0)-го элемента И логического блока, а выходы (т,тО-х,

которого непосредственно, а вькоды где m 0,1М, п i,...,N, эле(т,0)-х элементов И, где m О,..., ментов И через соответствующие эле- М-1, через соответствующий элемент менты ИЛИ подключены к т-(2п-1)}-м ИЛИ подключены к т-му выходу второго выходам второго логического блока.

Т а б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1984 |

|

SU1170461A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2449350C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2451328C1 |

Изобретение относится к вычислительной технике и технике передачи дискретных сообщений. Цель изобретения - расширение функциональных возможностей устройства путем определения текущего значения отношения количества импульсов в двух импульсных потоках. Для этого в устройство, содержащее первый суммирующий счетчик, первый логический блок и вычитающий счетчик, введены второй суммирующий счетчик, второй логический блок, накапливающий сумматор-вычитатель и блок элементов И. Предлагаемое устройство может быть использовано для оперативного эксплуатационного контроля частости ошибок в системах передачи дискретных сообщений. 4 ил., 1 табл.

№ импульса на входе 8

Триггеры счетчика

О

. 1 О 1 О

о о 1 1 о

о о о о

1

k А

Элементы И

10-1

10-2 Г10-3 |ll-2 Г11-:

1 1

о о о

1 1 1 1 о

о 1

о о

1

о о I

1

Таблица 2

Уш.Ж

t t т т Т Т t t t

.г

PI

г

О

/5

«.

22

vL

2/

27

/8

Г8

7S 20

Фг/г.

/б

о

2J

27

/в

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник, М.: Радио и связь, 198.6 | |||

| Мельников А.А, и др | |||

| Обработка частотных и временных импульсных сигналов | |||

| М„: Энергия, 1976 | |||

| 0 |

|

SU403070A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-11-30—Публикация

1989-01-02—Подача