Изобретение относится к измерительной технике и может быть использовано в устройствах совмещения механических и электрических нулей датчиков фэзовраща- тельного типа.

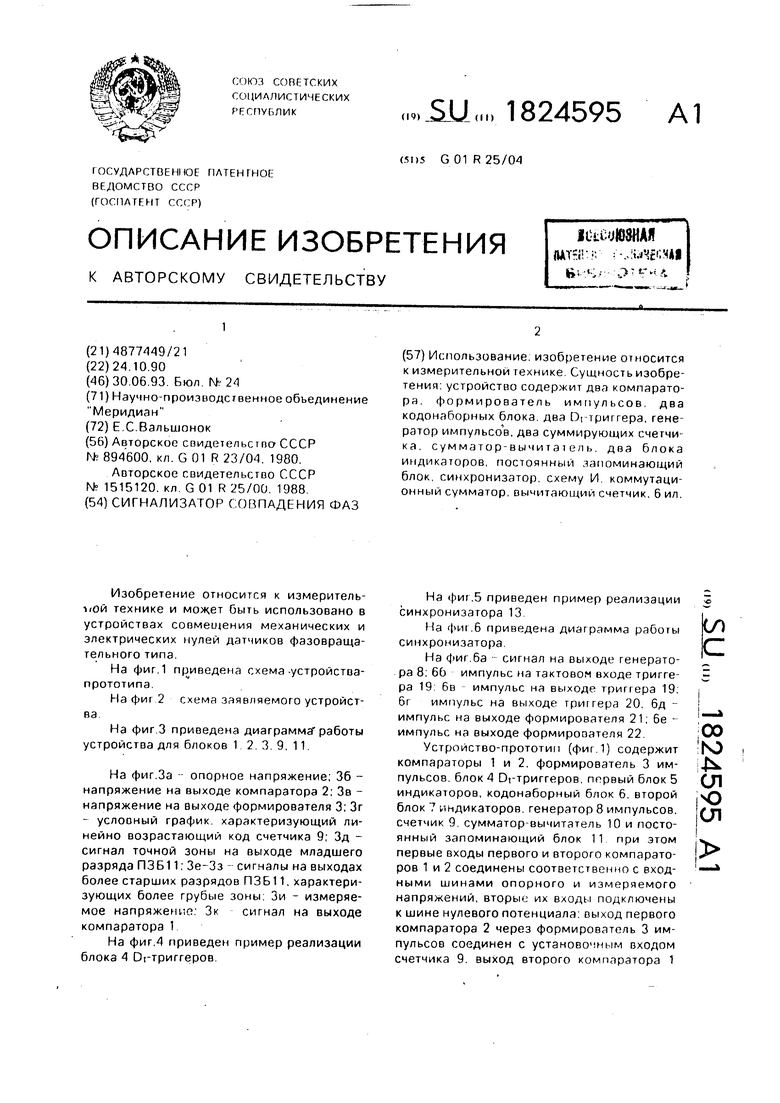

На фиг.1 приведена схема-устройства- прототипа.

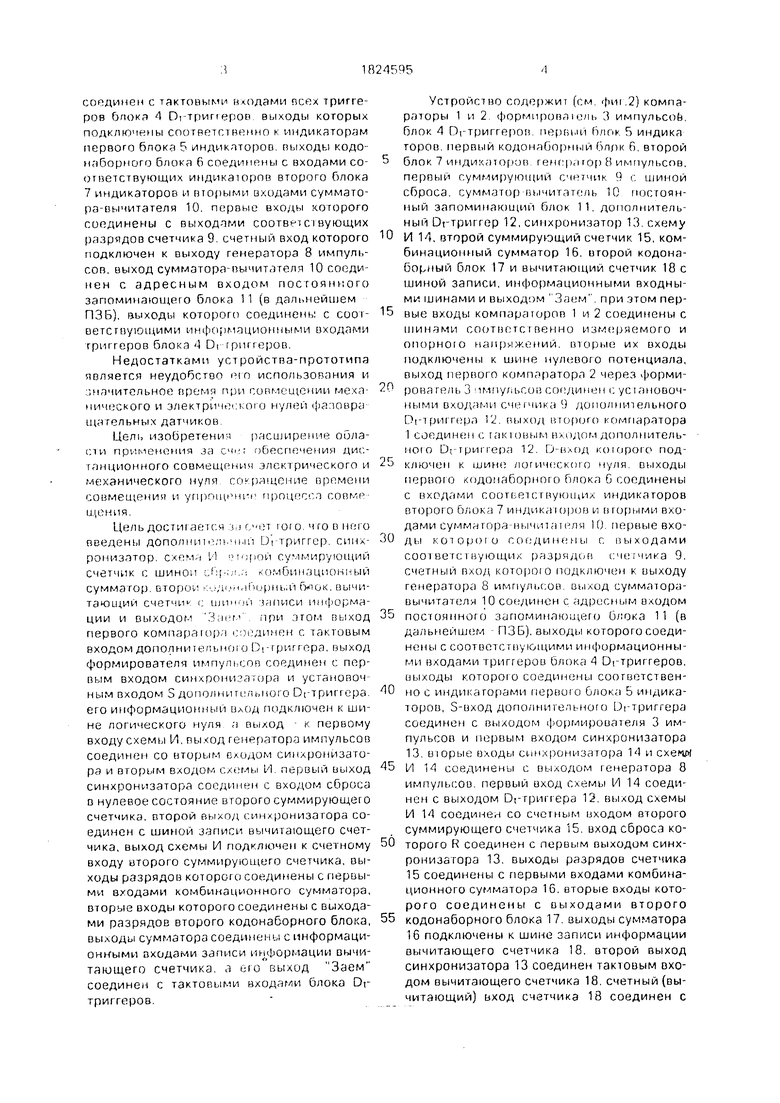

На фиг 2 схема заявляемого устройства

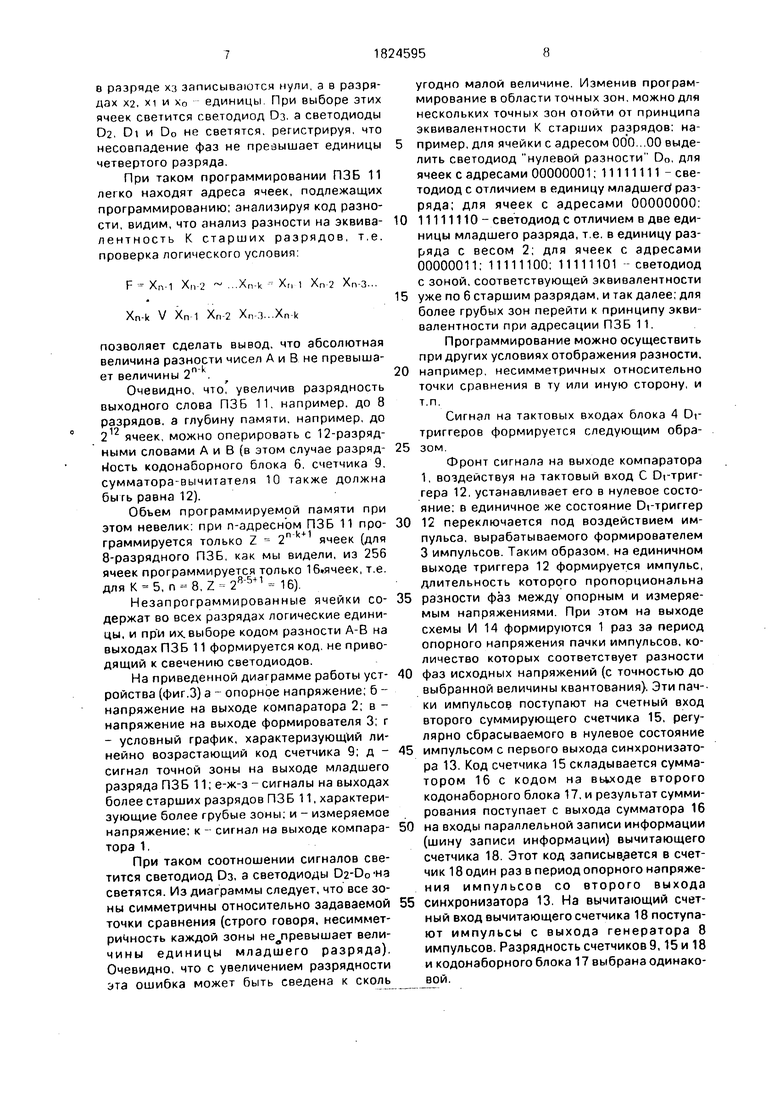

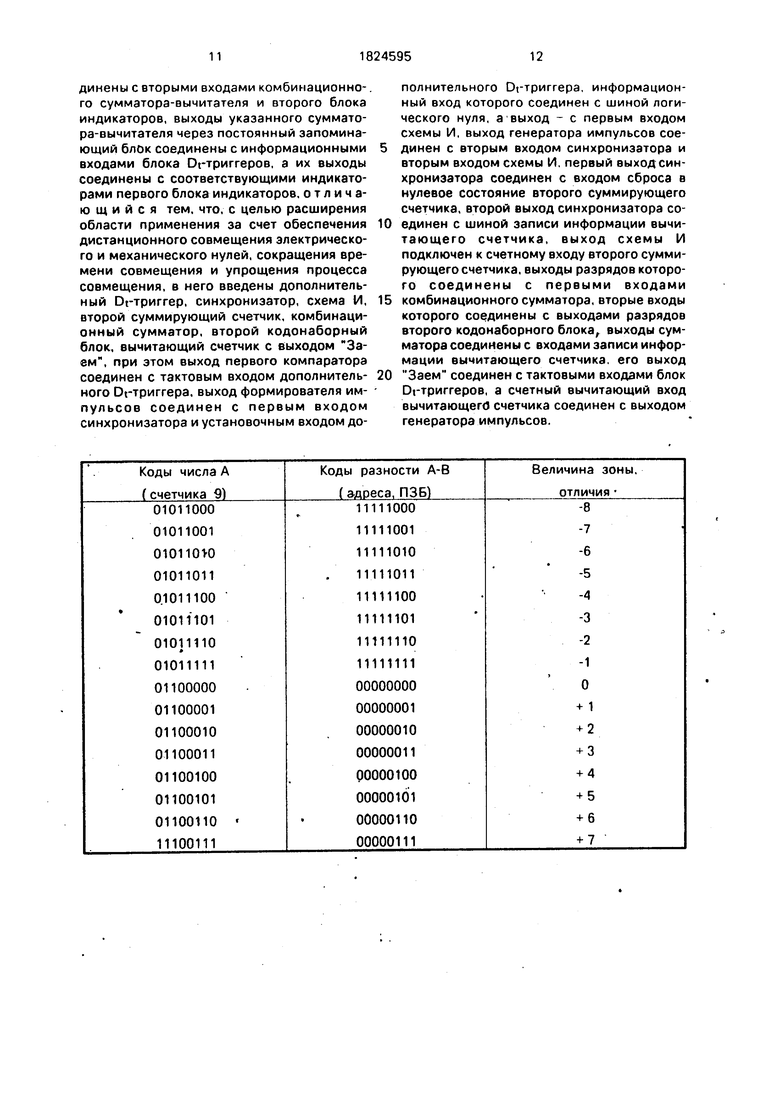

На фиг 3 приведена диаграмма работы устройства для блоков 1 2, 3, 9, 11.

На фиг.За - опорное напряжение; 36 - напряжение на выходе компаратора 2; Зв - напряжение на выходе формирователя 3; Зг - условный график, характеризующий линейно возрастающий код счетчика 9; Зд - сигнал точной зоны на выходе младшего разряда ПЗБ11; Зе-Зз - сигналы на выходах более старших разрядов ПЗБ11, характеризующих более грубые зоны. Зи - измеряемое напряженно: Зк сигнал на выходе компаратора 1

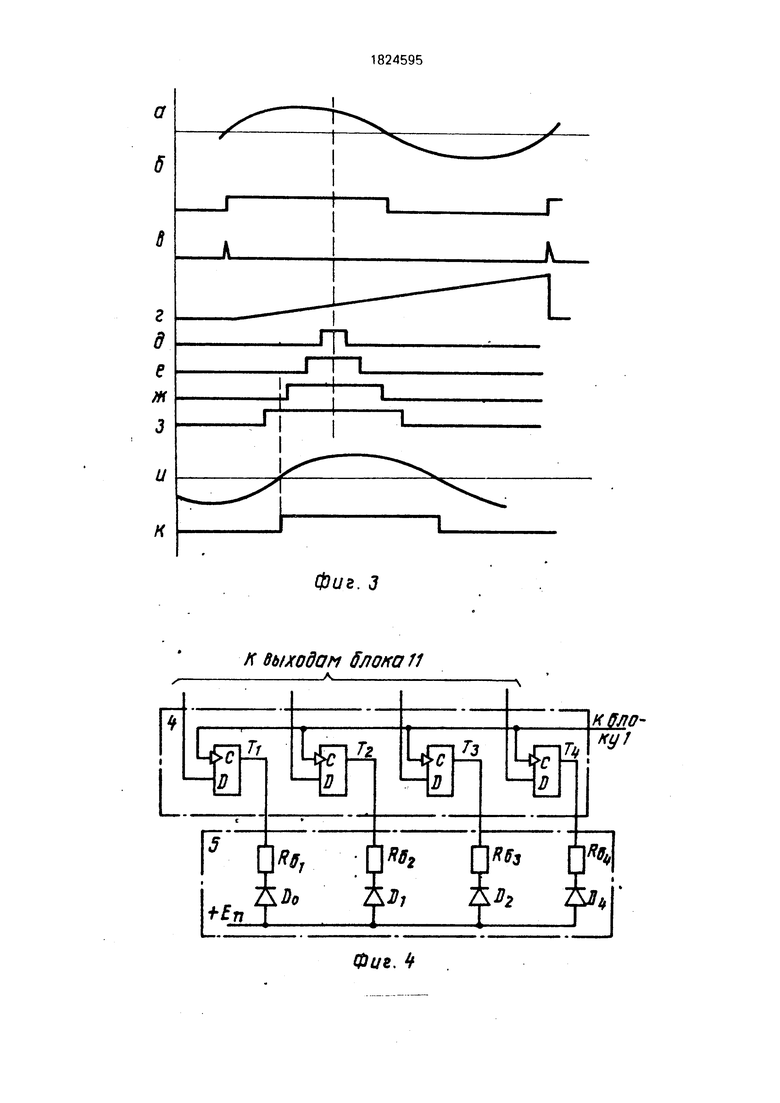

На фиг.4 приведен пример реализации блока 4 Dt-триггеров.

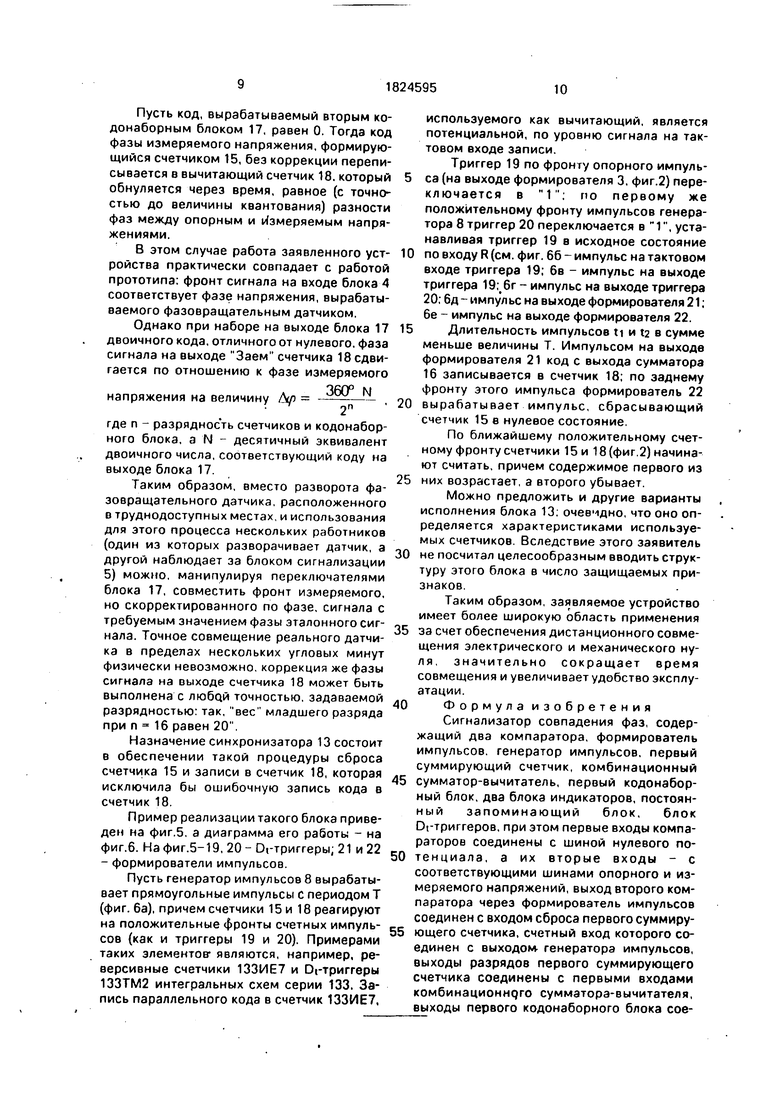

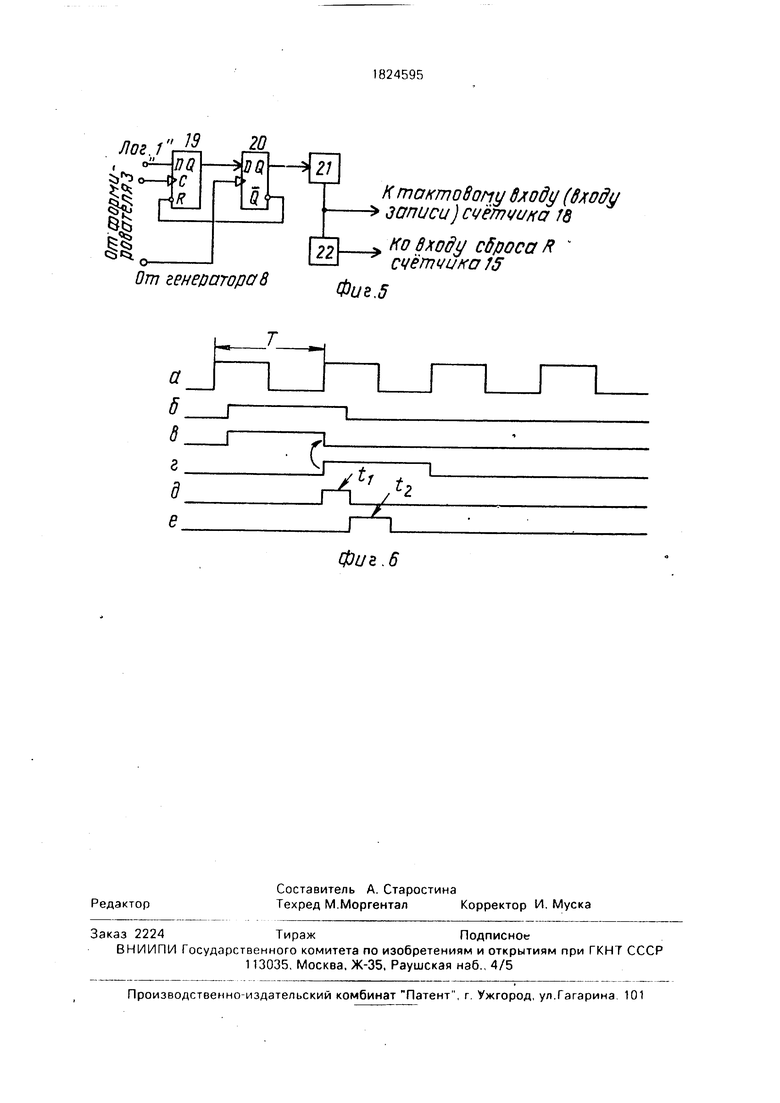

На фиг.5 приведен пример реализации синхронизатора 13

На фиг.6 приведена диаграмма работы синхронизатора.

На фиг.ба - сигнал на выходе генератора 8; 66 импульс на тактовом входе триггера 19 6в - импульс на выходе триггера 19. 6г импульс на выходе триггера 20, 6д - импульс на выходе формирователя 21; бе - импульс на выходе формирователя 22.

Устройство-прототип (фиг.1) содержит компараторы 1 и 2. формирователь 3 импульсов, блок 4 Dt-триггеров, первый блок 5 индикаторов, кодонаборный блок 6. второй блок 7 индикаторов, генератор 8 импульсов, счетчик 9, сумматор-вычитатель 10 и постоянный запоминающий блок 11 при этом первые входы первого и второго компараторов 1 и 2 соединены соответственно с входными шинами опорного и измеряемого напряжений, вторые их входы подключены к шине нулевого потенциала: выход первого компаратора 2 через формирователь 3 импульсов соединен с установочным входом счетчика 9, выход второго компаратора 1

(Л

С

00

ю

ел ю ел

соединен с тактовыми вводами всех триггеров блока 4 Dt трип еров выходы которых подключены соответственно и индикаторам первого блока 5 индикаторов выходы кодонаборного блока 6 соединены с входами со ответствующих индикаторов второго блока 7 индикаторов и вторыми входами суммато- ра-вычитателя 10 первые входы которого соединены с выходами соответствующих разрядов счетчика 9 счетный вход которого подключен к выходу генератора 8 импульсов выход сумматора вычитагеля 10 соединен с адресным входом постоянного запоминающего блока 11 (в дальнейшем ПЗБ), выходы которого соединена с cooi- ветсгвующими информационными входами триггеров блока A D триггеров

Недостатками устройства-прототипа является неудобство em использования и значительное время при совмещении мека иичоского и злектриче т ою нулей фа ювра щагельных датчиков

Цел, изоЬретенш расширение облает и применения за обеспечения дистанционного совмещения электрического и механического нуля сокращение времени совмещения и упрощенп процес1 i совме щения

Цель достигаете ч мгчетюго чговнею введены дополнитен чг ш DI триггер СИПА ронизатор схем i LI м JOH суммирующий счетчик с шиной иомбинационныи

сумматор второе , Ншрныи вычи- тающии счетчи г шин ш ыписи информации и вы-одом - кт1 при )том выход первого компаратор) единен с тактовым входом дополнительною DI григгера выход формирователя пмпушсов соединен с первым входом синхоони а юра и установоч ным входом S дополнитемг.по о Dt триггера его информационный ВАОД подключен к шине логического нуля ,i выход к первому входу схемы И вы од генепатора импульсов соединен со вторым сходом синхронизатора и вторым входом (.хемы И первый выход синхронизатора соединен с входом сброса в нулевое состояние второго суммирующего счетчика второй выход t инхронизагора соединен с шиной записи вычитающего счетчика, выход схемы И подключен к входу второго суммирующего счетчика, выходы разрядов которого соединены с первыми входами комбинационного сумматора, вторые входы которого соединены с выходами разрядов второго кодонаборного блока, выходы сумматора соединены с информационными входами записи информации вычитающего счетчика а «го выход Заем соединен с тактовыми входами блока Dr триггеров

Устройство содержит (см фиг 2) компараторы 1 и 2 формировании, 3 импульсов блок 4 П| триггеров перыш блок 5 индика торов первый кодонаборныи бллк 6 второй

блок 7 индикаторов генг р,иор В импульсов первый суммирующий счетчик Q шиной сброса сумматор иычитатель 10 постоянный запоминающий блок 11 дополнитель ный Dt-триггер 12, синхронизатор 13 схему

0 И 14, второй суммирующий счетчик 15, комбинационный сумматор 16 второй кодонаборныи блок 17 и вычитающий счетчик 18 с шиной записи информационными входными шинами и выходом Заем при этом пер5 вые входы компараторов 1 и 2 соединены с шинами соответственно измеряемого и опорного напряжении вторые их входы подключены к шине нулевого потенциала, выход первого компаратора 2 через формировагельЗ umy/ibroii соединен i установочными входами 9 дополнительного PI трипера 12 выход второго компаратора 1 соединен с такт овым влодом дополнительною U; гримера 12 D i отрою под

J ключам к шине логическою нуля выходы первою кодонаборного блока G соединены с входами соогг етегвующил индикаторов второго блока 7 индпкаiоров и вгорыми входами сумматора вычиытеля 10 первые вхо0 дп коте/рот о соединены г выходами соот ве гст вующил разряде) (чегчика 9 счетный ВАОД которою подключен к выходу генератора 8 импульс ов аьиод сумматора- вычитателя 10 соединен с адресным входом

5 постоянного запоминающею блока 11 (в дальнейшем ПЗБ) выходы которого соединены с соответстпу ющими информационными входами триггеров блока 4 DI триггеров выходы которою соединены соогветствен0 но с инди агорами первою Слон а Ь индикаторов, S-вход дополни) ель ното )| триггера соединен с выходом формирователя 3 импульсов и первым входом синхронизатора 13 вюрые В-.ОДЫ синхронизатора 14 и cxenpf

5 и 14 соединены с вылодом генератора 8 импульсов первый вход схемы И 14 соединен с выходом Оргрипера 12 выход схемы И 14 соединен со счетным входом второго суммирующего счетчика 15 вход сброса ко0 торого R соединен с первым выходом синхронизатора 13 выходы разрядов счетчика

15соединены с первыми входами комбинационного сумматора 16 вторые входы которого соединены с выходами второго

5 кодонаборного блока 17 выходы сумматора

16подключены к шине записи информации вычитающего счетчика 18 второй выход синхронизатора 13 соединен тактовым DXO- дом вычитающего счегчика 18 счетный (вычитающий) вход счегчика 18 соединен с

выходом генератора 8 импульсов, а выход Заем вычитающего счетчика 18 соединен с тактовыми входами С блока 4 Dt-тригге- ров.

Устройство работает следующим образом.

Компаратор 2 в момент положительного перехода входного (опорного) напряжения через нулевой уровень вырабатывает импульс, передний фронт которого совпадает с нулевой фазой опорного напряжения. Формирователь 3 импульсов вырабатывает по этому фронту короткий импульс, сбрасывающий счетчик 9 в нулевое состояние. Частота генерации генератора 8 импульсов и разрядность счетчика 9 выбраны такими, чтобы переполнение счетчика происходило за интервал времени, равный периоду опорного напряжения (например, если частота опорного и измеряемого сигналов равны F0, а разрядность счетчика 9 - п, то частота генерации генератора 8 должна быть F0 2П).

При выполнении этого условия состояние счетчика 9 с точностью до выбранного уровня квантования, определяемого разрядностью счетчика 9. соответствует фазе опорного напряжения.

Кодонаборный блок 6 предназначен для задания значения фазы опорного напряжения, о совпадении с которой нулевой фазы измеряемого напряжения должно сигнализировать устройство. Кодонаборный блок 6 может быть выполнен, например, на тумблерах. Совокупность выходных сигналов ко- донаборного блока 6 характеризует двоичный код этой фазы, отображаемый вторымблоком 7 индикации. Одновременно этот код поступает в качестве вычитаемого на второй вход сумматора-вычитателя 10. На первый вход сумматора-вычитателя 10 поступает линейно-ступенчато изменяющийся код фазы опорного напряжения с выходом разрядов счетчика 9.

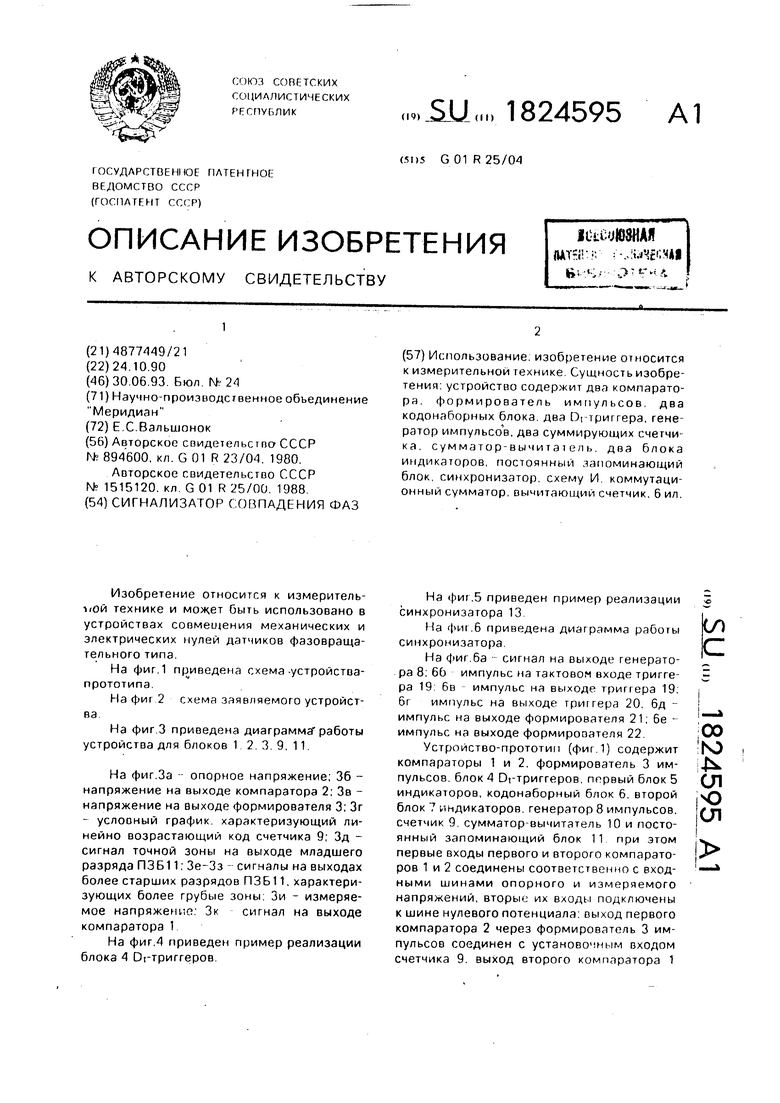

Рассмотрим, как меняется в течение периода напряжения n-разрядный результат вычитания из кода счетчика 9 (А) кода кодо- наборного блока 6 (В), для чего рассмотрим коды разности чисел А и В при изменении одного из них (А) от меньших значений до больших, например, в диапазоне трех младших разрядов. Для вычитания кода В из кода А необходимо код В преобразовать в дополнительный код, для чего его надо ин- версировать и прибавить единицу младшего разряда, после чего сложить код числа А и дополнительней код числа В. Все операции при этом осуществляем в п-разрядной сетке. Возникающий при этом перенос в (п+1)-й разряд теряется.

Именно по такому алгоритму работает n-разрядный сумматор-вычитатель 10 сигнализатора.

Допустим, что разрядность счетчика 9, 5 сумматора 10 и кодонаборного блока б равна 8. Тогда коду нулевой фазы соответствует код 00000000, коду 180° код 10000000, коду 90° - код 01000000, коду 45° - код 00100000 и так далее.

0 Допустим, что в кодонаборном блоке 6 установлен код 01100000. что соответствует фазе 135° (код числа В).

Дополнительный код числа В имеет вид 10011111

5 ±1

10100000

Рассмотрим текущие разности А-В (см. таблицу).

Таблица помогает понять принцип про0 граммирования ПЗБ 11 (ПЗБ 11-может быть выполнен, например, на основе микросхем серии 541РТ1. no 6KO 347236ТУЗ. 1 корпус микросхемы позволяет построить ПЗБ 11 на 256 4-разрядных слов). Допустим, что в

5 ячейки с адресами 11111111 и 00000000 записываются нули во все разряды выходного слова Используются, например, упомянутые микросхемы 541РТ4

Допустим, что нулевое значение разря0 да в выходном слове ПЗБ 11 в момент прихода нулевой фазы измеряемого напряжения приводит к свечению соответствующего светодиода блока 5. Пусть свето- диод Do соответствует младшему разряду

5 выходного слова, а Оз - старшему. Все све- тодиоды Do Da в таком случае светятся, когда несовпадение фаз опорного и измеряемого напряжений не превышает единицы младшего разряда n-разрядного (в

0 нашем примере - 8-разрядного) кода.

В ячейки с адресами 00000001 и 11111110 записываются нули в разрядах выходного слова хз, Х2, ж, а в разрядах х0 - единицы. Следовательно, при выборе этих

5 ячеек светятся светодиоды Оз-Di, а О0 не светится, при этом регистрируется ситуация, когда несовпадение фаз опорного и измеряемого напряжений не превышает единицы второго разряда. В ячейках с адре0 сами 00000010 и 11111100, 00000011 и 11111101 в разрядах хз и Х2 записываются нули, а в разрядах xi и х0 - единицы. При выборе этих ячеек светятся светодиоды Оз и Ог. a DI и Do не светятся, регистрируя, что

5 несовпадение фаз не превышает единицы третьего разряда. В ячейки с адресами

0000010011111000

0000010111111001 00000110 11111010 000001-11 11111011

в разряде хз записываются нули, а в разрядах Х2, xi и х0 единицы При выборе этих ячеек светится светодиод Оз. а светодиоды D2, Di и Do не светятся, регистрируя, что несовпадение фаз не превышает единицы четвертого разряда.

При таком программировании ПЗБ 11 легко находят адреса ячеек, подлежащих программированию; анализируя код разности, видим, что анализ разности на эквивалентность К старших разрядов, т.е. проверка логического условия:

F-Xn-1 Хп

Xn-k Хг, 1 Хп 2 Хп-3...

Xn-k V Хп1 Хп-2 ХпЗ.. Xnk

позволяет сделать вывод, что абсолютная величина разности чисел А и В не превышает величины 2П .

Очевидно, что, увеличив разрядность выходного слова ПЗБ 11, например, до 8 разрядов, а глубину памяти, например, до 212 ячеек, можно оперировать с 12-разрядными словами А и В (в этом случае разряд- йость кодонаборного блока 6, счетчика 9, сумматора-вычитателя 10 также должна быть равна 12).

Объем программируемой памяти при этом невелик: при п-адресном ПЗБ 11 программируется только Z 2nk+1 ячеек (для 8-разрядного ПЗБ, как мы видели, из 256 ячеек программируется только 16 ячеек, т.е.

для К 5, п 8, Z - 2

8-5+1

16).

Незапрограммированные ячейки содержат во всех разрядах логические единицы, и при их. выборе кодом разности А-В на выходах ПЗБ 11 формируется код. не приводящий к свечению светодиодов.

На приведенной диаграмме работы устройства (фиг.З) а - опорное напряжение; б - напряжение на выходе компаратора 2; в - напряжение на выходе формирователя 3; г - условный график, характеризующий линейно возрастающий код счетчика 9; д - сигнал точной зоны на выходе младшего разряда ПЗБ 11; е-ж-з - сигналы на выходах более старших разрядов ПЗБ 11, характеризующие более грубые зоны; и - измеряемое напряжение; к - сигнал на выходе компаратора 1,

При таком соотношении сигналов светится светодиод Оз, а светодиоды Оа-Оо-на светятся. Из диаграммы следует, что все зоны симметричны относительно задаваемой точки сравнения (строго говоря, несимметричность каждой зоны невпревышает величины единицы младшего разряда). Очевидно, что с увеличением разрядности эта ошибка может быть сведена к сколь

угодно малой величине. Изменив программирование в области точных зон. можно для нескольких точных зон отойти от принципа эквивалентности К старших разрядов: на- пример, для ячейки с адресом 000...00 выделить светодиод нулевой разности D0, для ячеек с адресами 00000001; 11111111 - светодиод с отличием в единицу младшего1 разряда; для ячеек с адресами 00000000:

0 11111110 - светодиод с отличием в две единицы младшего разряда, т.е. в единицу разряда с весом 2; для ячеек с адресами 00000011; 11111100; 11111101 --светодиод с зоной, соответствующей эквивалентности

5 уже по 6 старшим разрядам, и так далее; для более грубых зон перейти к принципу эквивалентности при адресации ПЗБ 11.

Программирование можно осуществить при других условиях отображения разности,

0 например, несимметричных относительно точки сравнения в ту или иную сторону, и т.п.

Сигнал на тактовых входах блока 4 триггеров формируется следующим обра5 зом.

Фронт сигнала на выходе компаратора 1, воздействуя на тактовый вход С Dt-триг- гера 12, устанавливает его в нулевое состояние: в единичное же состояние Dt-триггер

0 12 переключается под воздействием импульса, вырабатываемого формирователем 3 импульсов. Таким образом, на единичном выходе триггера 12 формируется импульс, длительность которого пропорциональна

5 разности фаз между опорным и измеряемым напряжениями. При этом на выходе схемы И 14 формируются 1 раз за период опорного напряжения пачки импульсов, количество которых соответствует разности

0 фаз исходных напряжений (с точностью до выбранной величины квантования). Эти пач- ки импульсов поступают на счетный вход второго суммирующего счетчика 15, регулярно сбрасываемого в нулевое состояние

5 импульсом с первого выхода синхронизатора 13. Код счетчика 15 складывается сумматором 16 с кодом на выводе второго кодонаборлого блока 17, и результат суммирования поступает с выхода сумматора 16

0 на входы параллельной записи информации (шину записи информации) вычитающего счетчика 18. Этот код записывается в счетчик 18 один раз в период опорного напряже- ния импульсов со второго выхода

5 синхронизатора 13. На вычитающий счетный вход вычитающего счетчика 18 поступают импульсы с выхода генератора 8 импульсов. Разрядность счетчиков 9,15 и 18 и кодонаборного блока 17 выбрана одинаковой.

Пусть код, вырабатываемый вторым ко- донаборным блоком 17, равен 0. Тогда код фазы измеряемого напряжения, формирующийся счетчиком 15, без коррекции переписывается в вычитающий счетчик 18. который обнуляется через время, равное (с точностью до величины квантования) разности фаз между опорным и Измеряемым напряжениями.

В этом случае работа заявленного устройства практически совпадает с работой прототипа: фронт сигнала на входе блока 4 соответствует фазе напряжения, вырабатываемого фазовращательным датчиком.

Однако при наборе на выходе блока 17 двоичного кода, отличного от нулевого, фаза сигнала на выходе Заем счетчика 18 сдвигается по отношению к фазе измеряемого

напряжения на величину А/э ,

где п - разрядность счетчиков и кодонабор- ного блока, а N - десятичный эквивалент двоичного числа, соответствующий коду на выходе блока 17.

Таким образом, вместо разворота фа- зовращательного датчика, расположенного в труднодоступных местах, и использования для этого процесса нескольких работников (один из которых разворачивает датчик, а другой наблюдает за блоком сигнализации 5) можно, манипулируя переключателями блока 17, совместить фронт измеряемого, но скорректированного по фазе, сигнала с требуемым значением фазы эталонного сигнала. Точное совмещение реального датчика в пределах нескольких угловых минут физически невозможно, коррекция же фазы сигнала на выходе счетчика 18 может быть выполнена с любо.й точностью, задаваемой разрядностью: так, вес младшего разряда при п 16 равен 20.

Назначение синхронизатора 13 состоит в обеспечении такой процедуры сброса счетчика 15 и записи в счетчик 18, которая исключила бы ошибочную запись кода в счетчик 18.

Пример реализации такого блока приведен на фиг.5, а диаграмма его работы - на фиг.6. Нафиг.5-19, 20-Dt-триггеры; 21 и 22 - формирователи импульсов.

Пусть генератор импульсов 8 вырабатывает прямоугольные импульсы с периодом Т (фиг, 6а), причем счетчики 15 и 18 реагируют на положительные фронты счетных импульсов (как и триггеры 19 и 20). Примерами таких элементов- являются, например, реверсивные счетчики 133ИЕ7 и Dt-триггеры 133ТМ2 интегральных схем серии 133. Запись параллельного кода в счетчик 133ИЕ7,

используемого как вычитающий, является потенциальной, по уровню сигнала на тактовом входе записи.

Триггер 19 по фронту опорного импуль- 5 са (на выходе формирователя 3, фиг.2) пере- ключается в по первому же положительному фронту импульсов генератора 8 триггер 20 переключается в 1, устанавливая триггер 19 в исходное состояние

0 по входу R (см. фиг. 66 - импульс на тактовом входе триггера 19; 6в - импульс на выходе триггера - импульс на выходе триггера 20; 6д - импульс на выходе формирователя 21; бе - импульс на выходе формирователя 22.

5 Длительность импульсов ti и t2 в сумме меньше величины Т. Импульсом на выходе формирователя 21 код с выхода сумматора 16 записывается в счетчик 18; по заднему Фронту этого импульса формирователь 22

0 вырабатывает импульс, сбрасывающий счетчик 15 в нулевое состояние.

По ближайшему положительному счетному фронту счетчики 15и 18(фиг.2) начинают считать, причем содержимое первого из

5 них возрастает, а второго убывает.

Можно предложить и другие варианты исполнения блока 13; очевидно, что оно определяется характеристиками используемых счетчиков. Вследствие этого заявитель

0 не посчитал целесообразным вводить структуру этого блока в число защищаемых признаков.

Таким образом, заявляемое устройство имеет более широкую область применения

5 за счет обеспечения дистанционного совмещения электрического и механического нуля, значительно сокращает время совмещения и увеличивает удобство эксплуатации.

0Формула изобретения

Сигнализатор совпадения фаз, содержащий два компаратора, формирователь импульсов, генератор импульсов, первый суммирующий счетчик, комбинационный

5 сумматор-вычитатель, первый кодонабор- ный блок, два блока индикаторов, постоянный запоминающий блок, блок Dt-триггеров, при этом первые входы компараторов соединены с шиной нулевого по0 тенциала, а их вторые входы - с соответствующими шинами опорного и измеряемого напряжений,выход второго компаратора через формирователь импульсов соединен с входом сброса первого суммиру5 ющего счетчика, счетный вход которого соединен с выходом- генератора импульсов, выходы разрядов первого суммирующего счетчика соединены с первыми входами комбинационндго сумматора-вычитателя, выходы первого кодонаборного блока соединены с вторыми входами комбинационно-. го сумматора-вычитателя и второго блока индикаторов, выходы указанного сумматора-вычитателя через постоянный запоминающий блок соединены с информационными входами блока Dt-триггеров, а их выходы соединены с соответствующими индикаторами первого блока индикаторов, отличающийся тем, что, с целью расширения области применения за счет обеспечения дистанционного совмещения электрического и механического нулей, сокращения времени совмещения и упрощения процесса совмещения, в него введены дополнительный Dt-триггер, синхронизатор, схема И, второй суммирующий счетчик, комбинационный сумматор, второй кодонаборный блок, вычитающий счетчик с выходом Заем, при этом выход первого компаратора соединен с тактовым входом дополнительного Dt-триггера, выход формирователя им- пульсов соединен с первым входом синхронизатора и установочным входом дополнительного Dt-триггера, информационный вход которого соединен с шиной логического нуля, а выход - с первым входом схемы И, выход генератора импульсов соединен с вторым входом синхронизатора и вторым входом схемы И, первый выход синхронизатора соединен с входом сброса в нулевое состояние второго суммирующего счетчика, второй выход синхронизатора соединен с шиной записи информации вычитающего счетчика, выход схемы И подключен к счетному входу второго суммирующего счетчика, выходы разрядов которого соединены с первыми входами

комбинационного сумматора, вторые входы которого соединены с выходами разрядов второго кодонаборного блока, выходы сумматора соединены с входами записи информации вычитающего счетчика, его выход

Заем соединен с тактовыми входами блок Dt-триггеров, а счетный вычитающий вход вычитающего счетчика соединен с выходом генератора импульсов.

Uujfi. 0 1 f I

1824595

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнализатор совпадения фаз | 1987 |

|

SU1515120A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1534435A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

Использование, изобретение относится к измерительной технике. Сущность изобретения: устройство содержит два компаратора, формирователь импульсов, два кодонаборных блока, два Ортриггера, генератор импульсо в, два суммирующих счегчи- ка. сумматор-вычитатель, два блока индикаторов, постоянный запоминающий блок, синхронизатор, схему И. коммутационный сумматор, вычитающий счетчик. 6 ил.

Фиг. 2

К

Фиг. 3

/г выходам б л ока 11

л

L.

UFI

Р u

ммммвнянниннни

Ј

Л

Gn7

с

D

5

КОЛОку

л

Ц It

От ген ер агора в

Фие.5

с

Г

Фиг.6

Ктактовопу 6л оду (бходу - вопи си) счётчика /в

но входу сброса к счётчика fff

г-Ч

| Устройство для сравнения фаз | 1980 |

|

SU894600A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Сигнализатор совпадения фаз | 1987 |

|

SU1515120A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-06-30—Публикация

1990-10-24—Подача