Изобретение относится к автоматике, вычислительной технике и средствам обработки экспериментальной информации.

Целью изобретения является расширение области применения путем значений функции в произвольной последовательности точек.

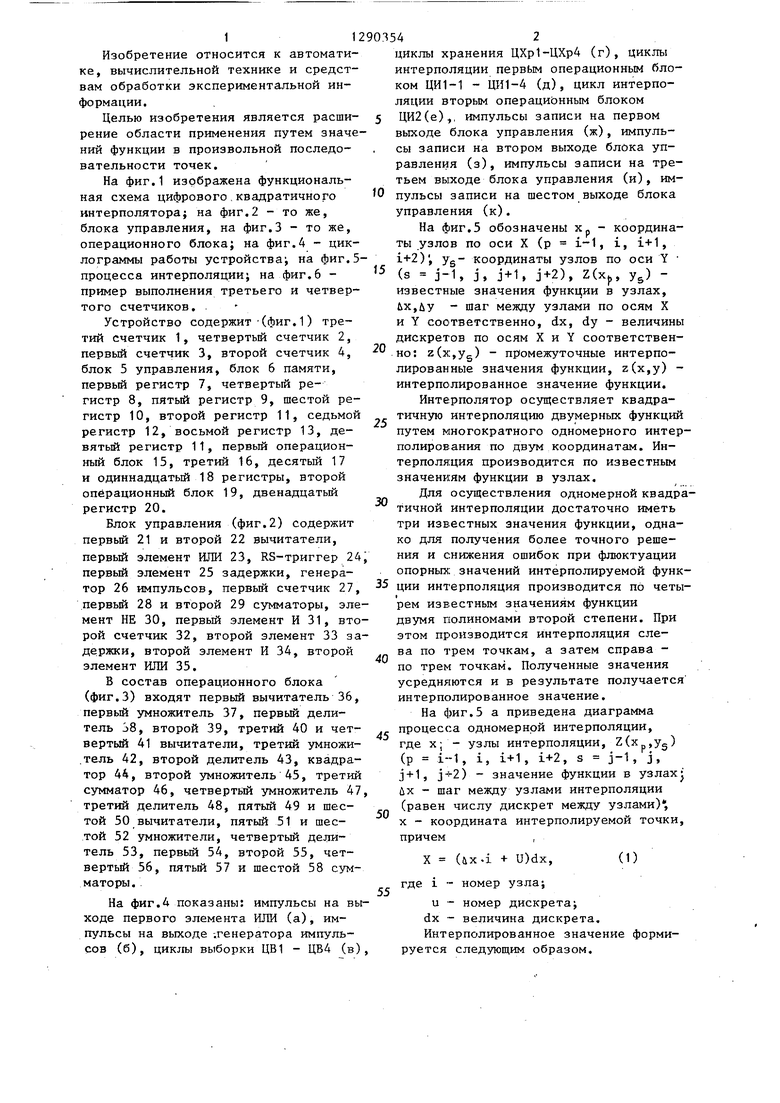

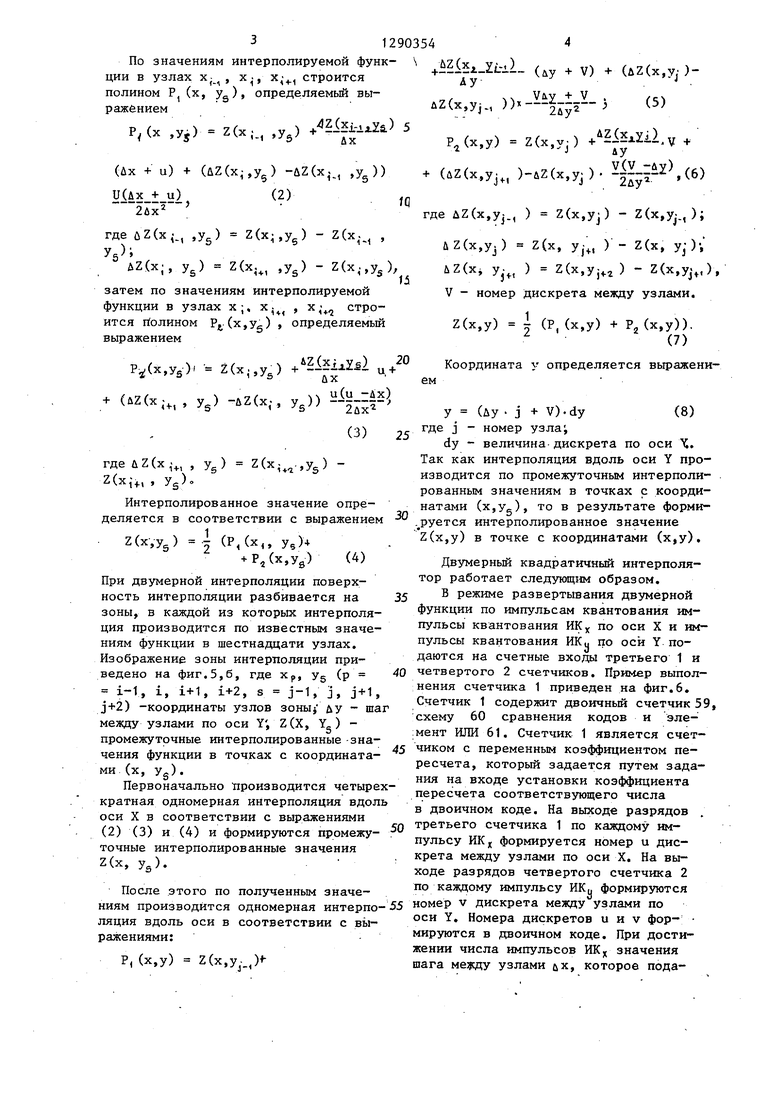

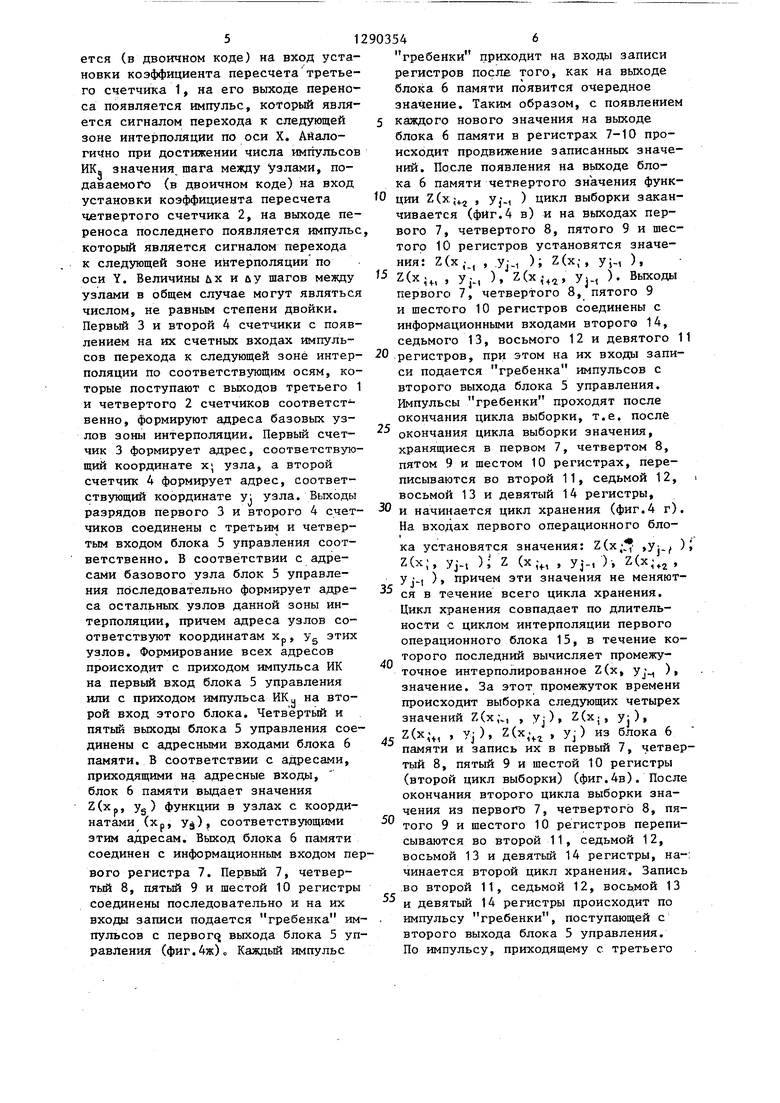

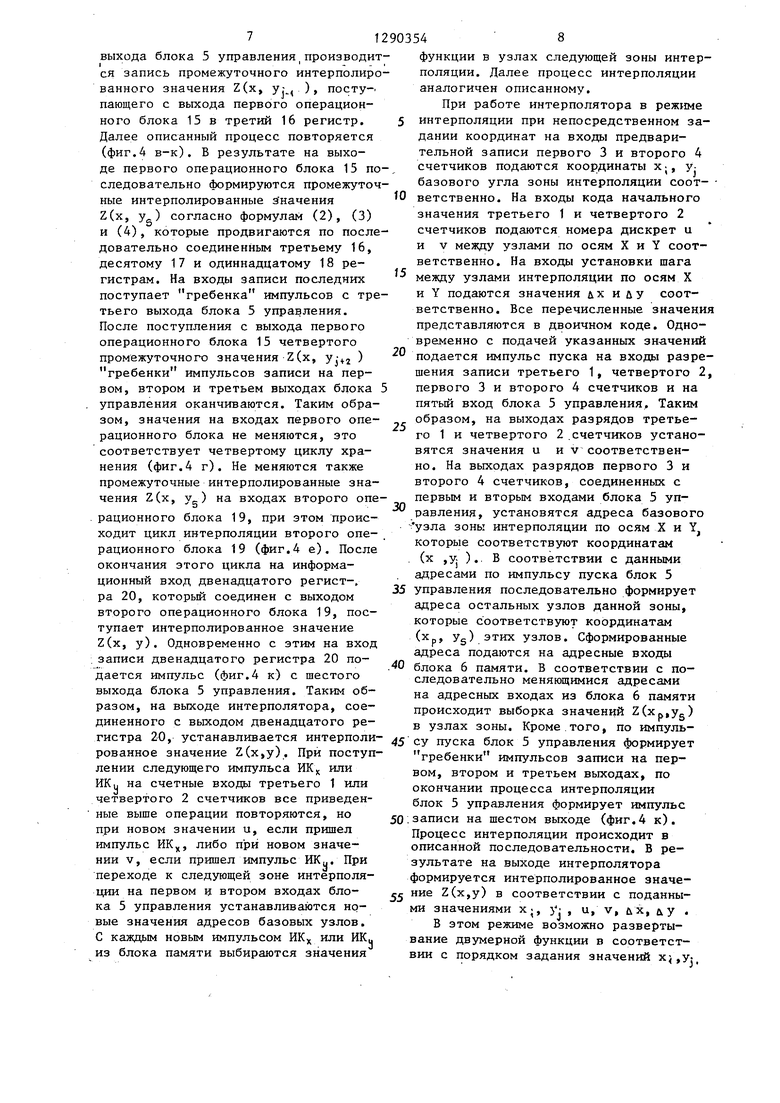

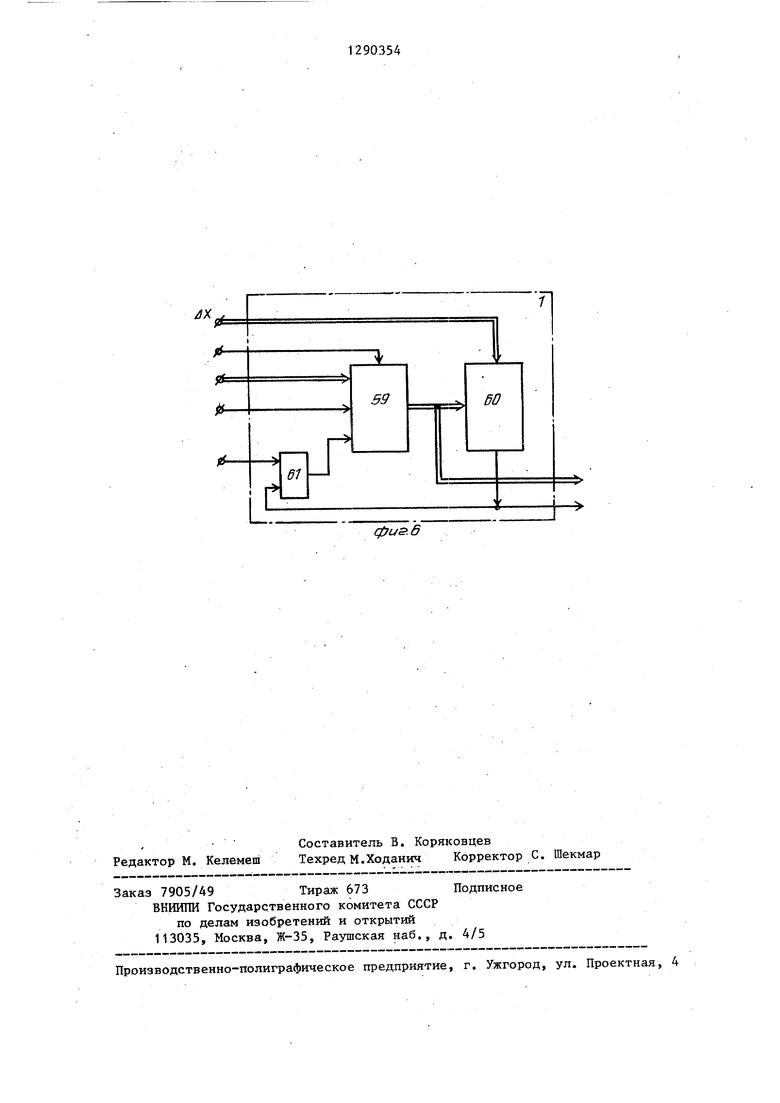

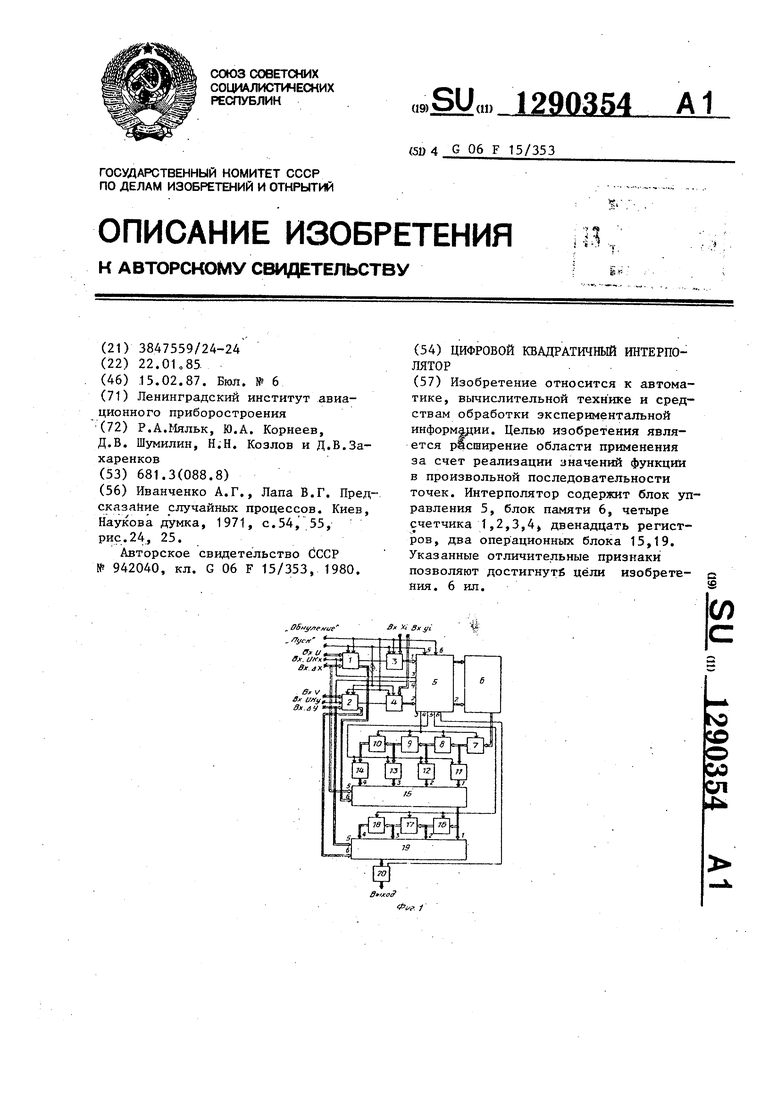

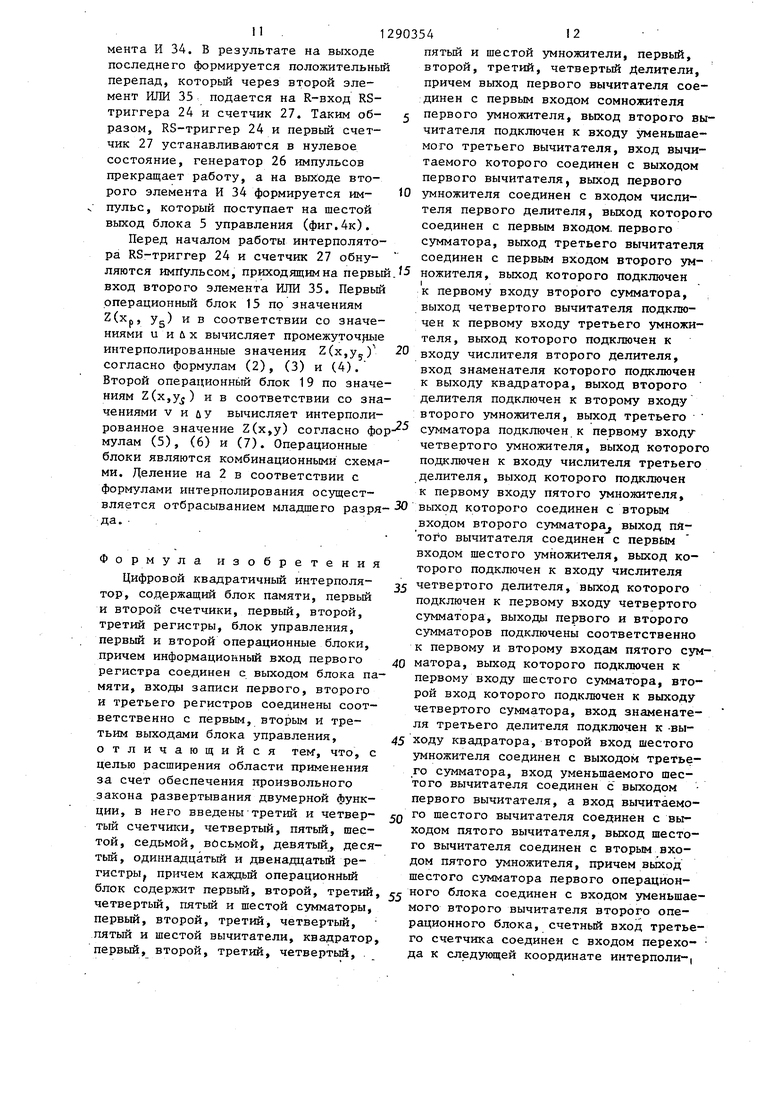

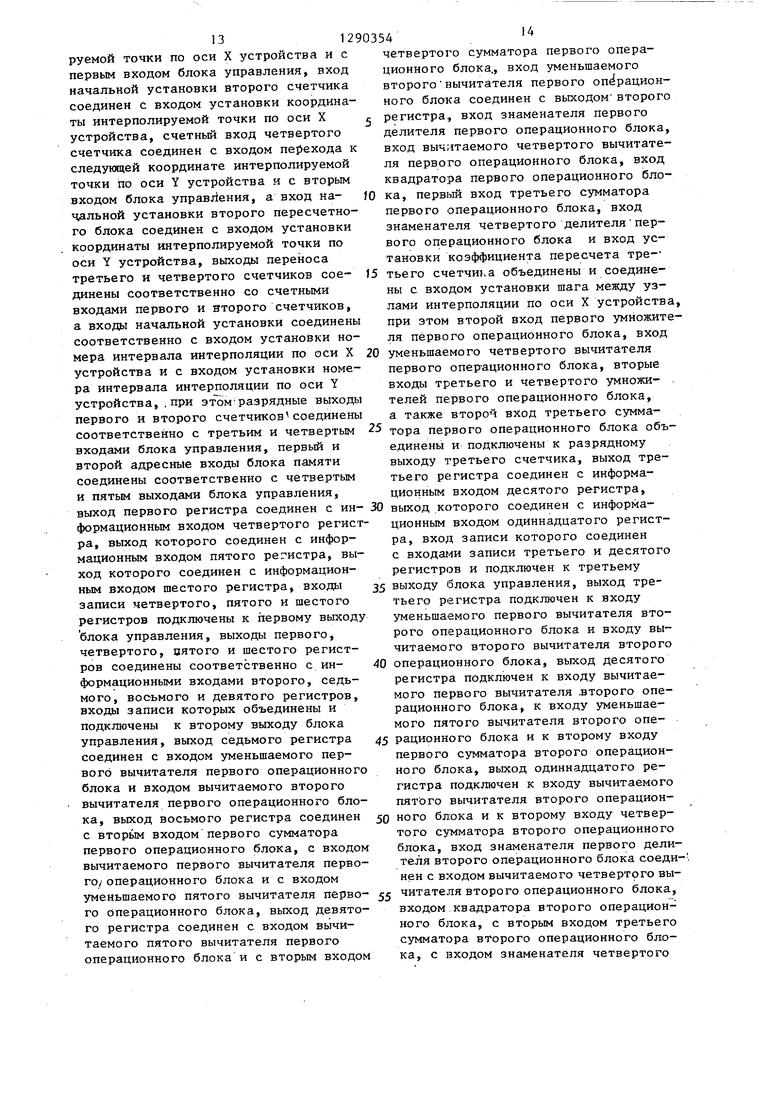

На фиг.1 изображена функциональная схема цифрового,квадратичного интерполятора; на фиг.2 - то же, блока управления, на фиг.З - то же, операционного блока; на фиг.4 - циклограммы работы устройства; на фиг.5- процесса интерполяции; на фиг.6 - пример выполнения третьего и четвертого счетчиков. .

Устройство содержит (фиг.1) третий счетчик 1, четвертый счетчик 2, первый счетчик 3, второй счетчик 4, блок 5 управления, блок 6 памяти, первый регистр 7, четвертый регистр 8, пятьй регистр 9, шестой регистр 10, второй регистр 11, седьмой регистр 12, восьмой регистр 13, девятый регистр 11, первый операционный блок 15, третий 16, десятый 17 и одиннадцатый 18 регистры, второй опёрационньй блок 19, двенадцатый регистр 20.

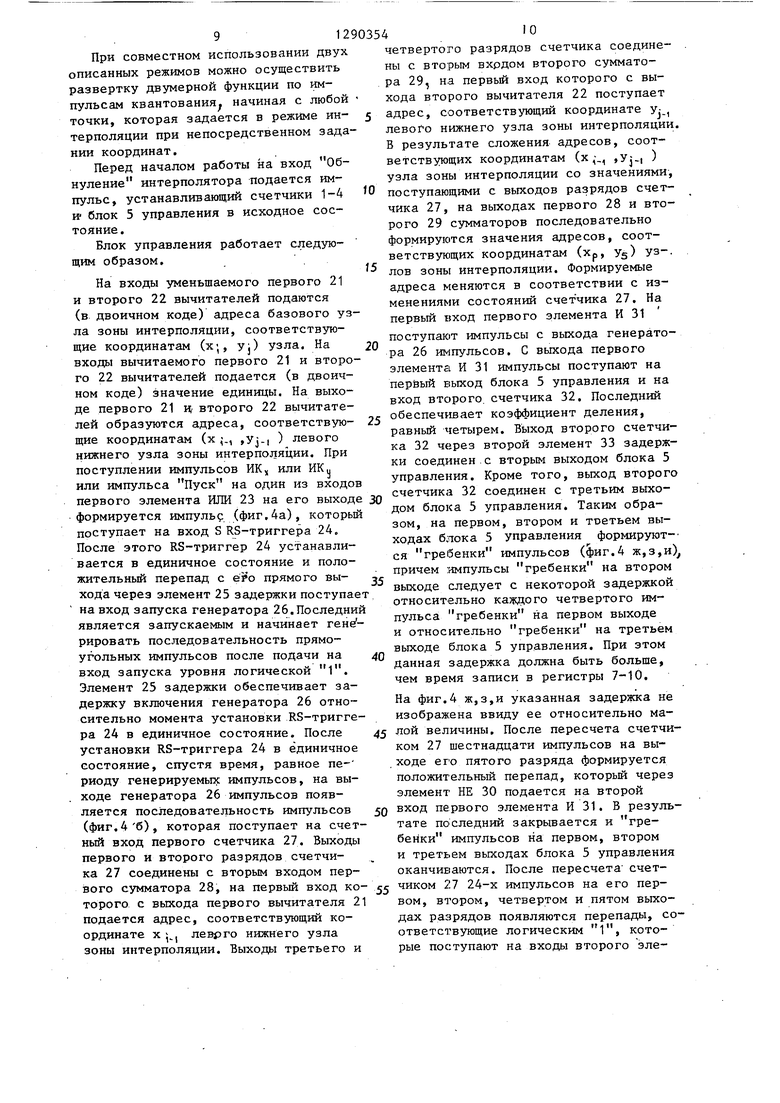

Блок управления (фиг.2) содержит первьм 21 и второй 22 вычитатели, первый элемент ИЛИ 23, RS-триггер 24 первый элемент 25 задержки, генератор 26 импульсов, первый счетчик 27, первьй 28 и второй 29 сумматоры, элемент НЕ 30, первый элемент И 31, второй счетчик 32, второй элемент 33 задержки, второй элемент И 34, второй элемент ИЛИ 35.

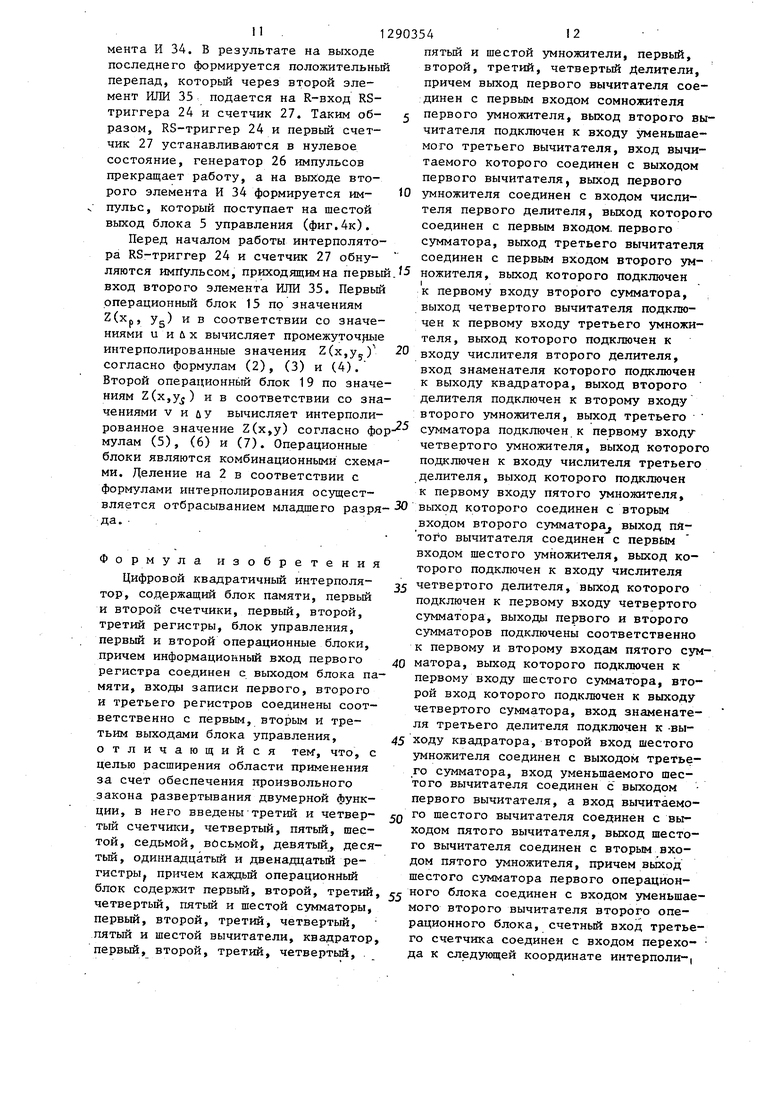

В состав операционного блока (фиг.З) входят первый вычитатель 36, первый умножитель 37, первый делитель Ь8, второй 39, третий 40 и четвертый 41 вычитатели, третий умножи- .тель 42, второй делитель 43, квадратор 44, второй умножитель 45, третий сумматор 46, четвертый умножитель 47 третий делитель 48, пятьй 49 и шестой 50 вычитатели, пятый 51 и шестой 52 умножители, четвертьй делитель 53, первьй 54, второй 55, четвертьй 56, пятьй 57 и шестой 58 сумматоры. .

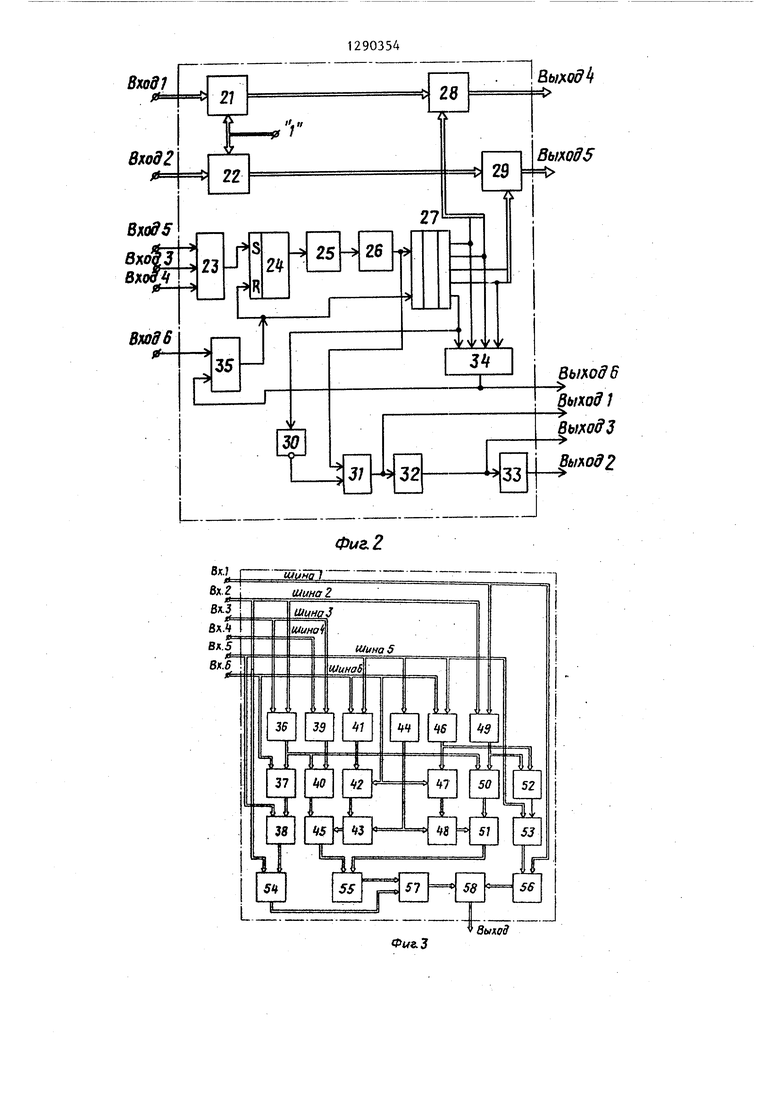

На фиг.4 показаны: импульсы на выходе первого элемента ИЛИ (а), импульсы на выходе -.генератора импульсов (б), циклы выборки ЦВ1 - ЦВ4 (в)

5

циклы хранения ЦХр1-ЦХр4 (г), циклы интерполяции первЬм операционным блоком ЦИ1-1 - ЦИ1-4 (д), цикл интерполяции вторым операционным блоком ЦИ2(е),, импульсы записи на первом выходе блока управления (ж), импульсы записи на втором выходе блока управления (з), импульсы записи на третьем выходе блока управления (и), импульсы записи на шестом выходе блока управления (к).

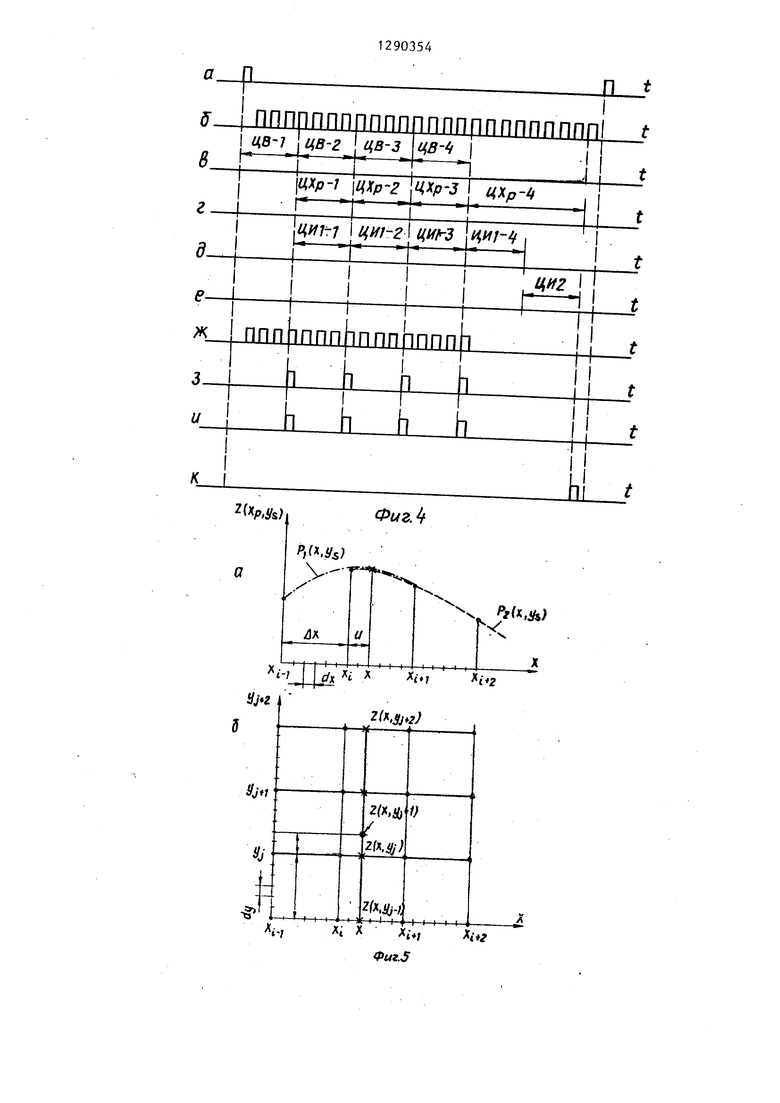

На фиг.5 обозначены х. - координаты узлов по оси X (р i-1, i, i+1, i+2). Уд- координаты узлов по оси Y (s J-1, j, J+1, J+2), Z(xp, Yg) 0

5

0

известные значения функции в узлах, Ьх,йу - шаг между узлами по осям X и Y соответственно, dx, dy - величины дискретов по осям X и Y соответственно: z(x,yg) - промежуточные интерполированные значения функции, г(х,у) - интерполированное значение функции.

Интерполятор осуществляет квадратичную интерполяцию двумерных функций путем многократного одномерного интер- полиров;ания по двум координатам. Интерполяция производится по известным значениям функции в узлах.

Для осуществления одномерной квадратичной интерполяции достаточно иметь три изв естных значения функции, однако для получения более точного решения и снижения ошибок при флюктуации опорных; значений интерполируемой функ- 5 ции интерполяция производится по четырем известным значениям функции двумя полиномами второй степени. При этом производится интерполяция слева по трем точкам, а затем справа - по трем точкам. Полученные значения усредняются и в результате получается интерполированное значение.

На фиг.5 а приведена диаграмма процесса одномерной интерполяции, где X; - узлы интерполяции, Z(x ,73) (р 1-1, i, i+1, i+2, S J-1, J, j+1, j+2) - значение функции в узлах- их - шаг между узлами интерполяции (равен числу дискрет между узлами), X - координата интерполируемой точки, причем,

(1)

0

5

0

5

X (ux-i + U)dx,

где i - номер узла;

U - номер дискрета; dx - величина дискрета. Интерполированное значение формируется следующим образом.

31290354

По значениям интерполируемой функ- ции в узлах Х;, , х,-, строится полином Р, (х. Уа), определяемьш вы). Э

ражёнием

+Ml5z ZL-L (ду + V) + (uZ(x,y; )дуJ .

uZ(x,yj., )))

PC v) + -- 2i-J.i2s. 5AZfx vO

,yg) ZU,., ,У) + P,(x,y) Z(x,yj) + 51XxXi2.v +

- UZ(x,yj,, )-uZ(x,yj). (6)

(Дх + u) + (uZ(x-,yg) -uZ(x., ,уд)) U(AX + u)(2)

JQ

2ux

где uZ(x., ,у) Z(x-,yg) - Z(x., ,

Yg);

Д2(х;, y) Z(x,, ,yg) - Z(x.,y5),

затем no значениям интерполируемой функции в узлах х;, х, , х,- строится йолином Р|5,(х,Уд) , определяемый выражением

i + (uZ(x

V (., л, - 7(v лгЛ 4.l5ij.2) „4. Координата у определяется выражени- ,УзЛ - Uj.ys + Ц+

, у ) -&Z(x,., у ))

UX

u(u -Дх)

У (ду j + V).dy(8)

(3)

гдeдZ(x-., , Уд) Z(x..,yg) - Z(x,-4., , Уд) о

Интерполированное значение определяется в соответствии с выражением

Z(x,yg) I (Р,(х,, у)

+ P,(x,yg) (4)

При двумерной интерполяции поверхность интерполяции разбивается на зоны, в каждой из которых интерполяция производится по известньм значениям функции в шестнадцати узлах. Изображение зоны интерполяции приведено на фиг.5,б, где Хр, Уд (р i-1, i, i+1, i+2, s j-1, j, j+1, j+2) -координаты узлов зоны} лу - шаг между узлами по оси Y; Z(X, Yg) 30

35

dy - величина дискрета по оси X. Так как интерполяция вдоль оси Y производится по промежуточным интерполированным значениям в точках с координатами (х,у), то в результате форми- .руется интерполированное значение Z(x,y) в точке с координатами (х,у).

Двумерный квадратичный интерполятор работает следующим образом.

В режиме развертывания двумерной функции по импульсам квантования импульсы квантования ИК по оси X и импульсы квантования ИКи по оси Y подаются на счетные входы третьего 1 и 40 четвертого 2 счетчиков. Пример выполнения счетчика 1 приведен на фиг.б. Счетчик 1 содержит двоичньм счетчик 59, схему 60 сравнения кодов и эле:мент ШШ 61. Счетчик 1 является счет- промежуточные интерполированные-зна,45 чиком с переменным коэффициентом печения функции в точках с координата-„

,. чресчета, которьи задается путем зада„ S ния на входе установки коэффициента

Первоначально производится четырех- . чл ч

кратная одномерная интерполяция вдоль

о , соответствии с выражениямитретьего счетчика 1 по каждому им(2) (3) и (4) и формируются промежу- формируется номер u дисточные интерполированные значения

s ходе разрядов четвертого счетчика 2

После этого по полученным значе- по кавдому импульсу ИК, формируются ниям производится одномерная интерпо-55 номер v дискрета между узлами по ляция вдоль оси в соответствии с вы- ° дискретов u и v фор- ражениями:мируются в двоичном коде. При достижении числа импульсов ИК значения Р) (у) 2(х,)шага меуду узлами х, которое подапересчета соответствующего числа в двоичном коде. На выходе разрядов

+Ml5z ZL-L (ду + V) + (uZ(x,y; )дуJ .

uZ(x,yj., )))

где uZ(x,yj., ) Z(x,yj) - Z(x,yj., );

uZ(x,yj) Z(x, yj, ) - Z(x, yj); iZ(xi y-, ) ZCx.yj) - Z(x,yj,,), V - номер Дискрета меявду узлами.

1

2

Z(x,y) (Р, (х,у) + .у)).

У (ду j + V).dy(8)

где j - номер узла;

dy - величина дискрета по оси X. Так как интерполяция вдоль оси Y производится по промежуточным интерполированным значениям в точках с координатами (х,у), то в результате форми- .руется интерполированное значение Z(x,y) в точке с координатами (х,у).

Двумерный квадратичный интерполятор работает следующим образом.

В режиме развертывания двумерной функции по импульсам квантования импульсы квантования ИК по оси X и импульсы квантования ИКи по оси Y подаются на счетные входы третьего 1 и четвертого 2 счетчиков. Пример выполнения счетчика 1 приведен на фиг.б. Счетчик 1 содержит двоичньм счетчик 59, схему 60 сравнения кодов и эле . чл ч

третьего счетчика 1 по каждому импересчета соответствующего числа в двоичном коде. На выходе разрядов

ется (в двоичном коде) на вход установки коэффициента пересчета третьего счетчика 1, на его выходе переноса появляется импульс, который является сигналом перехода к следующей зоне интерполяции по оси X, Айало- гично при достижении числа импульсов ИК„ значения шага между узлами, подаваемого (в двоичном коде) на вход установки коэффициента пересчета четвертого счетчика 2, на выходе переноса последнего появляется импульс который является сигналом перехода к следующей зоне интерполяции по оси Y. Величины лх и ьу шагов между узлами в общем случае могут являться числом, не равным степени двойки. Первый 3 и второй 4 счетчики с появлением на их счетных входах импульсов перехода к следующей зоне интерполяции По соответствующим осям, которые поступают с вькодов третьего 1 и четвертого 2 счетчиков соответст венно, формируют адреса базовых узлов зоны интерполяции. Первый счетчик 3 формирует адрес, соответствующий координате х; узла, а второй счетчик 4 формирует адрес, соответствующий координате у; узла. Выходы разрядов первого 3 и второго 4 счетчиков соединены с третьим и четвертым входом блока 5 управления соответственно. В соответствии с адресами базового узла блок 5 управления последовательно формирует адреса остальных узлов данной зоны интерполяции, причем адреса узлов соответствуют координатам х-, Vg этих узлов. Формирование всех адресов происходит с приходом импульса ИК на первый вход блока 5 управления или с приходом импульса ИКц на второй вход этого блока. Четвертьпй и пятый выходы блока 5 управления соединены с адресными входами блока 6 памяти. В соответствии с адресами, приходящими на адресные входы, блок 6 памяти вьщает значения Z(xp, Уд) функции в узлах с координатами (хр, у), соответствующими этим адресам. Выход блока 6 памяти соединен с информационным входом первого регистра 7. Первый 7, четвертый 8, пятый 9 и шестой 10 регистры соединены последовательно и на их входы записи подается гребенка импульсов с первого выхода блока 5 управления (фиг.4ж)„ Каждый импульс

гребенки приходит на входы записи регистров после того, как на выходе блока 6 памяти появится очередное значение. Таким образом, с появлением

каждого нового значения на выходе блока 6 памяти в регистрах 7-10 происходит продвижение записанных значений. После появления на выходе блока 6 памяти четвертого значения функции Z(x;.2 , Yj ., ) цикл выборки заканчивается (фиг.4 в) и на выходах первого 7, четвертого 8, пятого 9 и шестого 10 регистров установятся значения: Z(x,., , .Yj-,, ); Z(x;, Yi-1 ).

Z(x., , YjM ), ZCx,, , ). Выходы первого 7, четвертого 8, пятого 9 и шестого 10 регистров соединены с информационными входами второго 14, седьмого 13, восьмого 12 и девятого 11

регистров, при этом на их входы записи подается гребенка импульсов с второго выхода блока 5 управления. Импульсы гребенки проходят после окончания цикла выборки, т.е. после

окончания цикла выборки значения, хранящиеся в первом 7, четвертом 8, пятом 9 и шестом 10 регистрах, переписываются во второй 11, седьмой 12, i восьмой 13 и девятый 14 регистры,

и начинается цикл хранения (фиг.4 г). На входах первого операционного блока установятся значения: Z(x, У;- ) Z(x;, Yj-t ) Z (х,-, , YJ-I ). Z( Yj-i ), причем эти значения не меняются в течение всего цикла хранения. Цикл хранения совпадает по длительности с циклом интерполяции первого операционного блока 15, в течение которого последний вычисляет промежуточное интерполированное Z(x, yj ), значение. За этот промежуток времени происходит выборка следующих четырех значений Z(x,-., , YJ ) , Z(xj, Yj ) Z(X , , yj), Z(x,. , YJ) из блока 6 памяти и запись их в первый 7, четвер- ть1й 8, пятый 9 и шестой 10 регистры (второй цикл выборки) (фиг.4в). После окончания второго цикла выборки значения из первого 7, четвертого 8, пятого 9 и шестого 10 регистров переписываются во второй 11, седьмой 12, восьмой 13 и девятый 14 регистры, на-: чинается второй цикл хранения. Запись во второй 11, седьмой 12, восьмой 13 и девятый 14 регистры происходит по импульсу гребенки, поступающей с второго выхода блока 5 управления. По импульсу, приходящему с третьего

выхода блока 5 управления,производится запись промежуточного интерполированного значения Z(x, у., ), посту-, пающего с выхода первого операционного блока 15 в третий 16 регистр. Далее описанный процесс повторяется (фиг.4 в-к). В результате на выходе первого операционного блока 15 последовательно формируются промежуточные интерполированные з начения Z(x, у ) согласно формулам (2), (3) и (4), которые продвигаются по последовательно соединенным третьему 16, десятому 17 и одиннадцатому 18 регистрам. На входы записи последних поступает гребенка импульсов с третьего выхода блока 5 управления. После поступления с выхода первого операционного блока 15 четвертого промежуточного значения Z(x, гребенки импульсов записи на первом, втором и третьем выходах блока 5 управления оканчиваются. Таким образом, значения на входах первого операционного блока не меняются, это соответствует четвертому циклу хранения (фиг.4 г). Не меняются также промежуточные интерполированные значения Z(x, у ) на входах второго операционного блока 19, при этом происходит цикл интерполяции второго one- . рационного блока 19 (фиг.4 е). После окончания этого цикла на информационный вход двенадцатого регист-, ра 20, который соединен с выходом второго операционного блока 19, поступает интерполированное значение Z(x, у). Одновременно с этим на вход записи двенадцатого регистра 20 поается импульс (фиг.4 к) с шестого ыхода блока 5 управления. Таким обазом, на выходе интерполятора, соеиненного с выходом двенадцатого блока 6 памяти. В соответствии с последовательно меняющимися адресами на адресных входах из блока 6 памяти происходит выборка значений Z(xp,y-) в узлах зоны. Кроме.того, по импульгистра 20, устанавливается интерполи- 45 су пуска блок 5 управления формирует рованное значение Z(x,y).. При поступ- гребенки импульсов записи на первом, втором и третьем выходах, по окончании процесса интерполяции

лении следующего импульса ИК или

ИКп на счетные входы третьего 1 или четвертого 2 счетчиков все приведенблок 5 управления формирует импульс

ные выше операции повторяются, но при новом значении и, если пришел импульс ИК, либо при новом значении V, если пришел импульс ИКц. При переходе к следующей зоне интерполяции на первом и втором входах блока 5 управления устанавливаются новые значения адресов базовых узлов. С каждым новым импульсом ИК или ИКц из блока памяти выбираются значения

0

5

функции в узлах следующей зоны интерполяции. Далее процесс интерполяции аналогичен описанному.

При работе интерполятора в режиме интерполяции при непосредственном задании координат на входы предварительной записи первого 3 и второго 4 счетчиков подаются координаты х;, у- базового угла зоны интерполяции соот- - ветственно. На входы кода начального значения третьего 1 и четвертого 2 счетчиков подаются номера дискрет и и V между узлами по осям X и Y соответственно. На входы установки шага между узлами интерполяции по осям X и Y подаются значения лх и ау соответственно. Все перечисленные значения представляются в двоичном коде. Одновременно с подачей указанных зн-ачений подается импульс пуска на входы разрешения записи третьего 1, четвертого 2, первого 3 и второго 4 счетчиков и на пятый вход блока 5 управления. Таким образом, на выходах разрядов третьего 1 и четвертого 2 .счетчиков установятся значения и и v соответственно. На выходах разрядов первого 3 и второго 4 счетчиков, соединенных с первым и вторым входами блока 5 управления, установятся адреса базового узла зоны интерполяции по осям X и Y которые соответствуют координатам . (х ,У| ). В соответствии с данными адресами по импульсу пуска блок 5

5 управления последовательно формирует адреса остальных узлов данной зоны, которые соответствуют координатам (Хр, Уд) этих узлов. Сформированные адреса подаются на адресные входы

0 блока 6 памяти. В соответствии с последовательно меняющимися адресами на адресных входах из блока 6 памяти происходит выборка значений Z(xp,y-) в узлах зоны. Кроме.того, по импуль0

5

0

5 су пуска блок 5 управления формирует гребенки импульсов записи на первом, втором и третьем выходах, по окончании процесса интерполяции

блок 5 управления формирует импульс

50

записи на шестом выходе (фиг.4 к). Процесс интерполяции происходит в описанной последовательности. В результате на выходе интерполятора формируется интерполированное значе- ние Z(x,y) в соответствии с поданными значениями х

yj , U, V, ьх, ьу . В этом режиме возможно развертывание двумерной функции в соответствии с порядком задания значений х,у.,

При совместном использовании двух описанных режимов можно осуществить развертку двумерной функции по импульсам квантования начиная с любой точки, которая задается в режиме интерполяции при непосредственном задании координат.

Перед началом работы на вход Обнуление интерполятора подается импульс, устанавливающий счетчики 1-4 и- блок 5 управления в исходное состояние.

Блок управления работает следующим образом.

На входы уменьшаемого первого 21 и второго 22 вычитателей подаются (в двоичном коде) адреса базового узла зоны интерполяции, соответствующие координатам (х;, у;) узла. На входы вычитаемого первого 21 и второго 22 вычитателей подается (в двоичном коде) значение единицы. На выходе первого 21 и, второго 22 вычитателей образуются адреса, соответствую- щие координатам (х ., ,yj.| ) левого нижнего узла зоны интерполяции. При поступлении импульсов ИК, или ИКи или импульса Пуск на один из входов первого элемента ИЛИ 23 на его выходе формируется импульр (фиг,4а), который поступает на вход S RS-триггера 24. После этого RS-триггер 24 устанавливается в единичное состояние и положительный перепад с прямого вы- хода через элемент 25 задержки поступае на вход запуска генератора 26.Последний является запускаемым и начинает рировать последовательность прямоугольных импульсов после подачи на вход запуска уровня логической 1. Элемент 25 задержки обеспечивает задержку включения генератора 26 относительно момента установки RS-триггера 24 в единичное состояние. После установки RS-триггера 24 в единичное состояние, спустя время, равное пе- риоду генерируемых импульсов, на выходе генератора 26 импульсов появляется последовательность импульсов (фиг.4 б), которая поступает на счетный вход первого счетчика 27. Выходы первого и второго разрядов счетчика 27 соединены с вторым входом пер- iBoro сумматора 28, на первый вход ко- торого с выхода первого вычитателя 21 подается адрес, соответствующий координате X | ленрго нижнего узла зоны интерполяции. Выходы третьего и

5

четвертого разрядов счетчика соединены с. BTopbw вхрдом второго сумматора 29, на первьй вход которого с выхода второго вычитателя 22 поступает адрес, соответствующий координате yj, левого нижнего узла зоны интерполяции. В результате сложения адресов, соответствующих координатам (х,-., , ) узла зоны интерполяции со значениями, поступающими с выходов разрядов счетчика 27, на выходах первого 28 и второго 29 сумматоров последовательно формируются значения адресов, соот- ветствук1щих координатам (хр, у) уз-.

0 5 О 5

0

0

ки

управления. счетчика 32 дом блока 5

лов зоны интерполяции. Формируемые адреса меняются в соответствии с изменениями состояний счетчика 27. На первый вход первого элемента И 31 поступак1т импульсы с выхода генератора 26 импульсов. С выхода первого элемента И 31 импульсы поступают на первый выход блока 5 управления и на вход второго, счетчика 32. Последний обеспеч шает коэффициент деления, равньй четырем. Выход второго счетчика 32 через второй элемент 33 задерж- соединен.с вторым выходом блока 5 Кроме того, выход второго соединен с третьим выхо- управления. Таким образом, на первом, втором и тоетьем выходах блока 5 управления формируют- ся гребенки импульсов (фиг.4 ж,з,и) причем ;№1пульсы гребенки на втором выходе следует с некоторой задержкой относительно каждого четвертого импульса гребенки на первом выходе и относительно гребенки на третьем выходе блока 5 управления. При этом данная задержка должна быть больше, чем время записи в регистры 7-10.

На фиг.4 ж,з,и указанная задержка не изображена ввиду ее относительно ма- 5 лой величины. После пересчета счетчиком 27 шестнадцати импульсов на вы- . ходе его пятого разряда формируется положительный перепад, который через элемент НЕ 30 подается на второй вход первого элемента И 31. В результате по следний закрывается и гребенки импульсов на первом, втором и третьем выходах блока 5 управления оканчиваются. После пересчета счетчиком 27 24-х импульсов на его первом, втором, четвертом и пятом выходах разрядов появляются перепады, соответствующие логическим 1, которые поступают на входы второго элемента И 34. В результате на выходе последнего формируется положительный перепад, который через второй элемент ИЛИ 35 подается на R-вход RS- триггера 24 и счетчик 27. Таким образом, RS-триггер 24 и первьм счетчик 27 устанавливаются в нулевое состояние, генератор 26 импульсов прекращает работу, а на выходе второго элемента И 34 формируется импульс, который поступает на шестой выход блока 5 управления (фиг.4к).

Перед началом работы интерполятора RS-триггер 24 и счетчик 27 обну10

пятый и шестой умножители, первый, второй, третий, четвертый Делители, причем выход первого вычитателя соединен с первым входом сомножителя первого умножителя, выход второго вы читателя подключен к входу уменьшаемого третьего вычитателя, вход вычитаемого которого соединен с выходом первого вычитателя, выход первого умножителя соединен с входом числителя первого делителя, выход которог соединен с первым входом, первого сумматора, выход третьего вычитателя соединен с первым входом второго умляются имЯульсом, приходящим на первый. 5 ножителя, выход которого подключен вход второго элемента ИЛИ 35. Первьй операционный блок 15 по значениям Z(xp, Yg) и в соответствии со значениями U и U X вычисляет промежуточною интерполированные значения Z(x,yy) согласно формулам (2), (3) и (4). Второй операционньш блок 19 по значениям Z(x,y) и в соответствии со значениями V и йу вычисляет интерполированное значение Z(x,y) согласно сумматора подключен к первому входу

20

к первому входу второго сумматора, выход четвертого вычитателя подключен к первому входу третьего умножителя, выход которого подключен к входу числителя второго делителя, вход знаменателя которого подключен к выходу квадратора, выход второго делителя подключен к второму входу второго умножителя, выход третьего

мулам (5), (6) и (7). Операционные блоки являются комбинационными схемя- ми. Деление на 2 в соответствии с формулами интерполирования осуществляется отбрасыванием младшего разря- - да. .

четвертого умножителя, выход которог подключен к входу числителя третьего делителя, выход которого подключен к первому входу пятого умножителя, выход которого соединен с вторым входом второго сумматора выход пятого вычитателя соединен с первым входом шестого умножителя, выход которого подключен к входу числителя четвертого делителя, выход которого подключен к первому входу четвертого сумматора, выходы первого и второго сумматоров подключены соответственно к первому и второму входам пятого сум матора, выход которого подключен к первому входу шестого сумматора, второй вход которого подключен к выходу четвертого сумматора, вход знаменателя третьего делителя подключен к -вы- 45 ходу квадратора, второй вход шестого умножителя соединен с выходом третьего сумматора, вход уменьшаемого шестого вычитателя соединен с выходом первого вычитателя, а вход вычитаемого шестого вычитателя соединен с выходом пятого вычитателя, выход шестого вычитателя соединен с вторым входом пятого умножителя, причем выход шестого сумматора первого операционФормула изобретения

Цифровой квадратичный интерполятор, содержащий блок памяти, первьй и второй счетчики, первый, второй, третий регистры, блок управления, первый и второй операционные блоки, причем информационный вход первого регистра соединен с выходом блока памяти, входы записи первого, второго и третьего регистров соединены соответственно с первым, вторым и третьим выходами блока управления, отличающийся тем , что, с целью расширения области применения за счет обеспечения произвольного закона развертывания двумерной функции, в него введены-третий и четвертый счетчики, четвертый, пятый, шесчетвертого умножителя, выход которого подключен к входу числителя третьего делителя, выход которого подключен к первому входу пятого умножителя, выход которого соединен с вторым входом второго сумматора выход пятого вычитателя соединен с первым входом шестого умножителя, выход которого подключен к входу числителя четвертого делителя, выход которого подключен к первому входу четвертого сумматора, выходы первого и второго сумматоров подключены соответственно к первому и второму входам пятого сумматора, выход которого подключен к первому входу шестого сумматора, второй вход которого подключен к выходу четвертого сумматора, вход знаменателя третьего делителя подключен к -вы- 45 ходу квадратора, второй вход шестого умножителя соединен с выходом третьего сумматора, вход уменьшаемого шестого вычитателя соединен с выходом первого вычитателя, а вход вычитаемого шестого вычитателя соединен с выходом пятого вычитателя, выход шестого вычитателя соединен с вторым входом пятого умножителя, причем выход шестого сумматора первого операционтой, седьмой, восьмой, девятьй десятьш, одиннадцатый и двенадцатый регистры причем каждый операционный

блок содержит первый, второй, третий, j но го блока соединен с входом уменьшаечетвертьй, пятый и шестой сумматоры, мого второго вычитателя второго опе рационного блока, счетный вход третьего счетчика соединен с входом перехода к следующей координате интерполипервый, второй, третий, четвертый, пятый и шестой вычитатали, квадратор, первый, второй, третий, четвертый, .

пятый и шестой умножители, первый, второй, третий, четвертый Делители, причем выход первого вычитателя соединен с первым входом сомножителя первого умножителя, выход второго вычитателя подключен к входу уменьшаемого третьего вычитателя, вход вычитаемого которого соединен с выходом первого вычитателя, выход первого умножителя соединен с входом числителя первого делителя, выход которого соединен с первым входом, первого сумматора, выход третьего вычитателя соединен с первым входом второго умножителя, выход которого подключен сумматора подключен к первому входу

к первому входу второго сумматора, выход четвертого вычитателя подключен к первому входу третьего умножителя, выход которого подключен к входу числителя второго делителя, вход знаменателя которого подключен к выходу квадратора, выход второго делителя подключен к второму входу второго умножителя, выход третьего

5

четвертого умножителя, выход которого подключен к входу числителя третьего делителя, выход которого подключен к первому входу пятого умножителя, выход которого соединен с вторым входом второго сумматора выход пятого вычитателя соединен с первым входом шестого умножителя, выход которого подключен к входу числителя четвертого делителя, выход которого подключен к первому входу четвертого сумматора, выходы первого и второго сумматоров подключены соответственно к первому и второму входам пятого сумматора, выход которого подключен к первому входу шестого сумматора, второй вход которого подключен к выходу четвертого сумматора, вход знаменателя третьего делителя подключен к -вы- 5 ходу квадратора, второй вход шестого умножителя соединен с выходом третьего сумматора, вход уменьшаемого шестого вычитателя соединен с выходом первого вычитателя, а вход вычитаемого шестого вычитателя соединен с выходом пятого вычитателя, выход шестого вычитателя соединен с вторым входом пятого умножителя, причем выход шестого сумматора первого операцион0

0

131290354

руемой точки по оси X устройства и с четвертого сумматора первого опера- первым входом блока управления, вход ционного блока., вход уменьшаемого начальной установки второго счетчика второго вычитателя первого оп рацион- соединен с входом установки координа- него блока соединен с выходом второго ты интерполируемой точки по оси X г регистра., вход знаменателя первого устройства, счетный вход четвертого делителя первого операционного блока, счетчика соединен с входом перехода к вход вычитаемого четвертого вычитате- следующей координате интерполируемой ля первого операционного блока, вход точки по оси Y устройства и с вторым квадратора первого операционного бло- входом блока управления, а вход на- JO ка, первый вход третьего сумматора чальной установки второго пересчетно- первого операционного блока, вход го блока соединен с входом установки знаменателя четвертого делителя пер- координаты интерполируемой точки по вого операционного блока и вход ус- оси Y устройства, выходы переноса тановки коэффициента пересчета тре- третьего и четвертого счетчиков сое- 15 тьего счетчика объединены и соедине- динены соответственно со счетными ны с входом установки шага между уз- входами первого и второго счетчиков, лами интерполяции по оси X устройства, а входы начальной установки соединены при этом второй вход первого умножите- соответственно с входом установки но- ля первого операционного блока, вход мера интервала интерполяции по оси X 20 уменьшаемого четвертого вычитателя устройства и с входом установки номе- первого операционного блока, вторые ра интервала интерполяции по оси Y входы третьего и четвертого умножи- устройства, .при этом разрядные выходы телей первого операционного блока, первого и второго счетчиков соединены а также втором вход третьего сумма- соответственно с третьим и четвертым 25 тора первого операционного блока объ- входами блока управления, первый и единены и подключены к разрядному второй адресные входы блока памяти выходу третьего счетчика, выход тре- соединены соответственно с четвертым тьего регистра соединен с информа- и пятым выходами блока управления, ционным входом десятого регистра, выход первого регистра соединен с ин- 30 выход которого соединен с информа- формационным входом четвертого регист- ционным входом одиннадцатого регистра, выход которого соединен с инфор- ра, вход записи которого соединен мационным входом пятого регистра, вы- с входами записи третьего и десятого ход которого соединен с информацион- регистров и подключен к третьему ным входом шестого регистра, входы j выходу блока управления, выход тре- записи четвертого, пятого и шестого тьего регистра подключен к входу регистров подключены к первому выходу уменьшаемого первого вычитателя вто- блока управления, выходы первого, рого операционного блока и входу вы- четвертого, пятого и шестого регист- читаемого второго вычитателя второго ров соединены соответственно с ин- 40 операционного блока, выход десятого формационными входами второго, седь- регистра подключен к входу вычитаемого, восьмого и девятого регистров, мого первого вычитателя .второго one- входы записи которых объединены и рационного блока, к входу уменьшае- подключены к второму выходу блока мого пятого вычитателя второго one- управления, выход седьмого регистра 45 рационного блока и к второму входу соединен с входом уменьшаемого пер- первого сумматора второго операцион- вого вычитателя первого операционного ного блока, выход одиннадцатого ре- блока и входом вычитаемого второго гистра подключен к входу вычитаемого вычитателя первого операционного бло- пят ого вычитателя второго операцион- ка, выход восьмого регистра соединен 50 ного блока и к второму входу четвер- с BTOpbw входом первого сумматора того сумматора второго операционного первого операционного блока, с входом блока, вход знаменателя первого дели- вычитаемого первого вычитателя перво- теля второго операционного блока соеди- го/операционного блока и с входом нен с входом вычитаемого четвертого вы- уменьшаемого пятого вычитателя перво- 55 читателя второго операционного блока, го операционного блока, выход девято- входом квадратора второго операцион- го регистра соединен с входом вычи- ного блока, с вторым входом третьего таемого пятого вычитателя первого сумматора второго операционного бло- операционного блока и с вторым входом ка, с входом знаменателя четвертого

делителя второго операционного блока входом установки коэффициента пересчета четвертого счетчика и подключен к входу установки шага между узлами интерполяции по оси Y устройства, второй вход первого умножителя второго операционного блока соединен с входом уменьшаемого четвертого вы- читателя второго операционного блока с вторыми входами третьего и четвертого умножителя второго операционир- го блока, с вторым входом третьего сумматора второго операционного блок и подключен к разрядному выходу четвертого счбтчика, выход шестого сумматора второго операционного блока соединен с информационным входом двенадцатого регистра, вход записи которого соединен с шестым выходом блока управления, входы установки первого, второго, третьего и четвертого счетчиков, а также пятый вход блока управления соединены с входом пуска устройства, входы сброса первого, второго, третьего и четвертого счетчиков и шестой вход блока управления соединены с входом сброса устройства выход двенадцатого регистра является выходом значения функции в интерполируемой точке устройства, причем блок управления содержит первый и второй вычитатели, первый и второй сумматоры первый и второй элементы ИЛИ, RS-триг гер, генератор импульсов, первый и второй счетчики, первый и второй элементы И, первый и второй элементы задержки, элемент НЕ, выходы первого и второго вычитателей блока управления соединены соответственно с входами первого слагаемого первого и второго сумматоров, входы уменьшаемого первого и второго вычитателей блока управления являются соответственно третьим и четвертым входами блока

управления, входы вычитаемого первого 45 ляется шестым входом блока - npasne- и второго вычитателей блока управле- ния, выход второго элемента ИЛИ сое- ния соединены с входом единичного динен с R-входом RS-триггера и вхо- кода устройства, выход первого эле- дом сброса первого счетчика блока мента ИПИ соединен с S-входом RS- управления.

10

15

0

триггера, первый, второй и третий входы первого элемента ИЛИ соединены соответственно с первым, вторым и пятым входами блока управления, прямой выход RS-триггера через первый элемент задержки соединен с входом запуска генератора импульсов, выход которого соединен со счетным входом первого счетчика блока управления и с первым входом первого элемента И, выходы первого и второго разрядов первого счетчика блока управления соединены с входом второго слагаемого первого сумматора блока управления, а выходы третьего и четвертого разрядов первого счетчика блока уп- равления соединены с входом второго слагаемого второго сумматора блока управления, при этом выходы разрядов первого и второго сумматоров блока управления являются соответственно четвертым и пятым выходами блока управления, выход пятого разряда первого счетчика блока управления соединен с первым входом .второго элемента И и с входом элемента НЕ, выход которого подключен к второму входу первого элемента И, выход которого подключен к первому выходу блока управления и к. счетному входу второго счетчика блока управления, выход которого соединен с третьим выходом блока управления и с входом второго элемента задержки, выход которого 5 является вторым выходом блока управления,, второй, третий и четвертый входы второго элемента И соединены соответственно с выходами первого, второго и четвертого разрядов первого счетчика блока управления-, а выход второго элемента И соединен с первым входом второго элемента ИЛИ и шестым выходом блока управления, второй вход второго элемента ШШ яв-

5

0

0

Вюд1

8мд2

28

Выход

Вы)(од5

ии

| название | год | авторы | номер документа |

|---|---|---|---|

| Двумерный линейный интерполятор | 1985 |

|

SU1269152A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1317452A1 |

| Устройство для интерполяции | 1985 |

|

SU1264202A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| МОДИФИЦИРОВАННЫЙ ФИЛЬТР КАЛМАНА | 1992 |

|

RU2160496C2 |

Изобретение относится к автоматике, вычислительной техн ике и средствам обработки экспериментальной информадии. Целью изобретения является расширение области применения за счет реализации значений функции в произвольной последовательности точек. Интерполятор содержит блок управления 5, блок памяти 6, четыре счетчика 1,2,3,4, двенадцать регистров, два операционных блока 15,19. Указанные отличительные признаки позволяют достигнутй цели изобретения. 6 ил. i (Л Л« к вх yi

Фиг. 2

8x.J

32

33

Вы}(од6 Выход 1 Вы}(0&3

Bbiwd2

Фи&З

вылог

Редактор М. Келемеш

Составитель В. Коряковцев

Техред М.Ходанич Корректор С. Шекмар

Заказ 7905/49 Тираж 673 Подписное ВКИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

фи.6

| Иванченко А.Г., Лапа В.Г | |||

| Пред- сказайие случайных процессов | |||

| Киев, Наукова думка, 1971, с.54, 55, рис.24, 25 | |||

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-01-22—Подача