Изобретение относится к вычисли- тельной технике и может быть использовано для связи ЭВМ типа ЕС с различными устройствами цифровой вьгаисли- тельной техники.

Цель изобретения - здаеньшение объема аппаратуры.

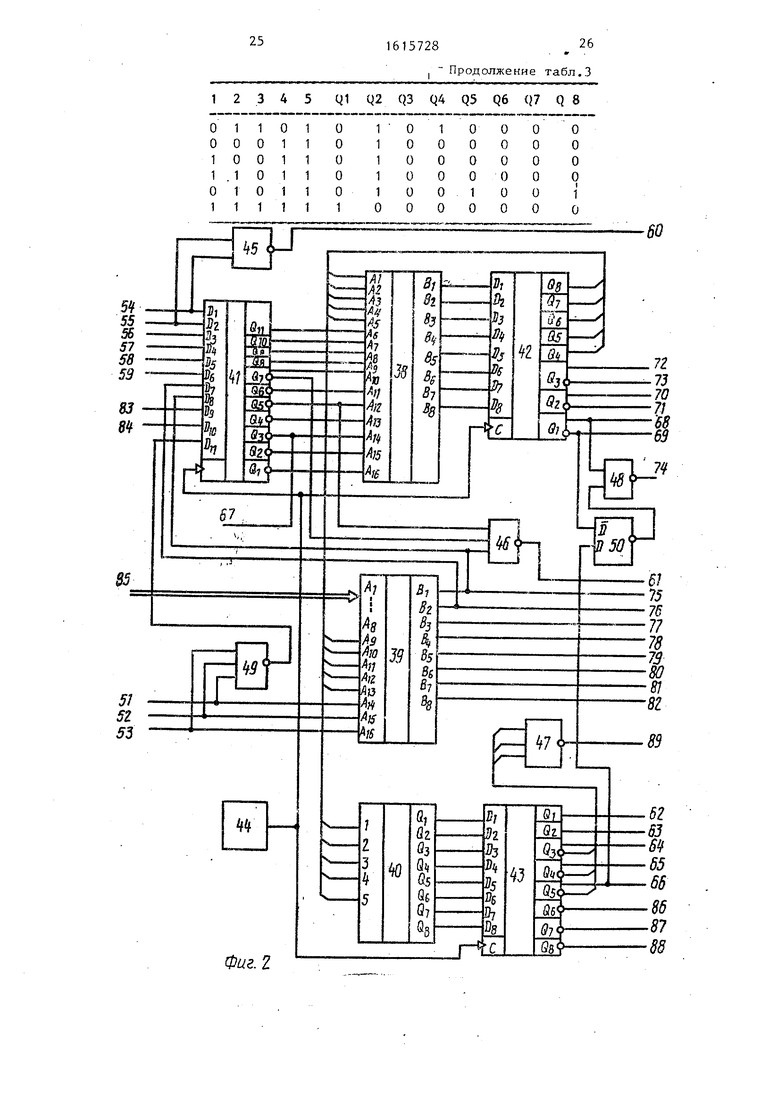

На фиг. 1 представлена структурная схема устройства; на фиг, 2 - схема блока управления обменом с ЭВМ; на фиг. 3 и 4 - схемы блока управлени;. обменом с абонентом.

Устройство (фиг. 1) содержит входы и выходы 1-14 устройства, блок 15 усилителей-приемников, блок 16 усили телей-передатчиков, блок 17 управления обменом с ЭВМ, -второй буферньш |регистр 18 данных, мультиплексор 19

1615728 .. 4

Последовательность сигналов выборки, вводимая устройством, инициирую- щая при установке высокого зФовня хо- тя бы на одном из входов 51-53 блока 17 (высокий уровень сигнала 51 означает освобождение буферной памяти передачи, высокий уровень сигнала 52 - заполнение буферной памяти приема,

Q а высокий уровень на входе 53 устанавливается при включении устройства) при этом на выходе элемента ИЛИ- НЕ 49 устанавливается низкий уровень, которьй через регистр 41 постзшает

|5 на вход А6 схемы 38.

Программирование ПЛМ 38 осуществляется по табл. 1, в соответствии с которой ПЛМ 38 при наличии низкого уровня на входе А6 и при свободном

буферную память 20 приема регистр 21 20 интерфейсе ввода-вывода ЭВМ что опсостояния, буферную память 22 переда чи, первьм буферный регистр 23 данных блок 24 управления обменом с абонентом,, входы и выходы устройства 25 - 36 и коммутатор 37 линии выборки.

Блок 17 управления обменом с ЭВМ |(фиг. 2) содержит первьй 38 и второй, 39 шие1)раторы5 в качестве которых, могут использоваться программируемые ло

ределяется уровнями сигналов на выхо - дах А11 - А16 ПЛМ 38, устанавливает на выходах В4 - В9 код режима (поз. 46 и 47, табл. 1), по которому память 40 25 в соответствии с программой, представленной в табл. 3, выставляет сигнал высокого уровня, которьй через регистр 43 проходит на выход 62 и поступает на вход блока 16 усилителей7ические матрицы (П.ПМ), постоянную передатчиков, что приводит к вьщаче шть 40, первый 41, второй 42 и третий 43 регистры, генератор 44 такто- i Bbix и myльcoв, первьй 45j второй .46, третий 47 и четвертьш 48 элементы И-НЕ, рлемент ИЛИ-НЕ 49, одновибратор 50, входы и выходы 51-89 блоков 39-43

35

ртветственно, I Блок 24 управлешля обменом с а бо- .Центом (фиг. 3 и 4) содержит триггер: 00, элемент И 91, триггеры 92 - 94, элементы ИЛИ - НЕ 95-97, элемент И 98, рдновибраторы 99-101, триггер 102, Ьлемент И 103, триггеры 104 и 105, элемент ИЛИ-НЕ 106, триггер 107, элемент ИЛИ-НЕ 108, одновибраторы 109 - 112, элемент ИЛИ-НЕ 113, элемент И 114 и входы-выходы 115-130 устрой- стёа.

Устройство работает следующим образом,,

При взаимодействии с ЭВМ могут вы- йолняться такие последовательности i Сигналов; последовательность сигналов }ыборки, вводимая устройством; последовательность сигналов начальной вьг- | (5орки устройства; последовательность (Сигналов передачи данных; последова- , дельность сигналов окончания операции,

в интерфейс ввода-вывода сигнала ТРБ-А на выходе 9.

При связи с ЭВМ ПЛМ 38 устанавливает сигнал высокого уровня на выходе В2, что поиводит к блокировке сигналом на выхоле 71 усилителя-передатчика сигнала распространения выборки и разблокированию сигналом на выходе 70 усилителей-передатчиков сигналов ройства. Получив сигнал ТРБ-А, канал ЭВМ может ответить сигналом БЛК-К по входу 3;, поступающему по входу 54 на вход Д1 регистра 41 и далее на вход А16 ПЛМ 38, что приводит к сбросу сигД5 нала ТРБ-А, либо может ответить сигналом ВБР-К по входу 5, которьй после усиления поступает на вход ДЗ регистра 41- и далее на вход А14 ПЛМ 38, что приводит к установке на выходах В4 - ВВ 11ЛМ 38 кода режима (поз. 48, 4 и 5, табя„ 1), по которому ШШ 38 в соответствии с табл. 2 устанавливает на вьпкодах Б1 - В8 собственный адрес а память 40 устанавливает сигналы вь1 сокого уровня на выходах 63 и 64 которые после усиления поступают на выходы РАБ-А 10 и АДР-А 11. собствен- ньй адрес устройства по выходам 75 - 82 поступает на входы мультиплексора

50

55

ределяется уровнями сигналов на выхо - дах А11 - А16 ПЛМ 38, устанавливает на выходах В4 - В9 код режима (поз. 46 и 47, табл. 1), по которому память 40 в соответствии с программой, представленной в табл. 3, выставляет сигнал высокого уровня, которьй через регистр 43 проходит на выход 62 и поступает на вход блока 16 усилителейпередатчиков, что приводит к вьщаче

в интерфейс ввода-вывода сигнала ТРБ-А на выходе 9.

При связи с ЭВМ ПЛМ 38 устанавливает сигнал высокого уровня на выходе В2, что поиводит к блокировке сигналом на выхоле 71 усилителя-передатчика сигнала распространения выборки и разблокированию сигналом на выходе 70 усилителей-передатчиков сигналов устройства. Получив сигнал ТРБ-А, канал ЭВМ может ответить сигналом БЛК-К по входу 3;, поступающему по входу 54 на вход Д1 регистра 41 и далее на вход А16 ПЛМ 38, что приводит к сбросу сигнала ТРБ-А, либо может ответить сигналом ВБР-К по входу 5, которьй после усиления поступает на вход ДЗ регистра 41- и далее на вход А14 ПЛМ 38, что приводит к установке на выходах В4 - ВВ 11ЛМ 38 кода режима (поз. 48, 4 и 5, табя„ 1), по которому ШШ 38 в соответствии с табл. 2 устанавливает на вьпкодах Б1 - В8 собственный адрес а память 40 устанавливает сигналы вь1 сокого уровня на выходах 63 и 64 которые после усиления поступают на выходы РАБ-А 10 и АДР-А 11. собствен- ньй адрес устройства по выходам 75 - 82 поступает на входы мультиплексора

5. 16

19 и далее на входы регистра 18, ин- формация в которой стробируется сигналом на выходе 89 элемента И-НЕ 47 при появлении высокого уровня на одном из выходов 64 - 66 (выходы 64 - 66 соответствуют сигналам АДР-А, УПР-А, ИНФ-А).

Получив сигналы РАБ-А и АДР-А, канал выдает сигнал Л1Р-К по входу 7, которьй после усиления поступает по входу 58 на вход Д5 регистра 41 и - с выхода этого регистра на вход А12 1ШМ38, которая затем устанавливает на своих выходах код регкима, приводя1ций к сбросу сигнала АДР-А на выходе 11. После сброса сигнала АДР-А канал сбра сьюает сигнал УПР-К, что приводит к установке устройством сигнала УПР-А (поз. 15, табл. 1, и поз. 9, табл. 3) сопровождающего байт состояния, причем указатели байта состояния, выставляемого на выходах 2, задаются выходами ПЛМ 39 в зависимости от кода режима, установленного на входах А9 - А13.ПЛМ 39, и в зависимости от уровней сигналов на входах 51-53 (на входах А14, А14, А16 ПЛМ 39). Так, например, при крде режима, равном 01101 и при наличии высокого уровня только на входе А16 ШШ 39-, выходы ШШ 39 определяют байт состояния с указателями Канал кончил, Устройство кончило (поз. 7, табл. 2).

При выполнении последовательности сигналов выборки, вводимой абонентом, канал при получении байта состояния после сброса сигнала ВБР-К на входе 5 может либо выдать сигнал УПР-К, означающий указание заполнить состояние, в результате чего устройство отключается от интерфейса (при этом состоя- :ние регистра 21 не изменяется), либо выдать сигнал ИНФ-К по входу 8, означающий прием каналом байта состояния, что приводит к отключению устройства от интерфейса ЭВМ с одновременной вьщачей сигнала высокого уровня на выходе 72 и сигнала низкого уровня на выходе 73, которыми обеспечивается сбррс соответствующих триггеров регистра 21 в зависимости от выставленных на выходах регистра 18 указателей байта состояния.

Рассмотрим выполнение устройством различных команд канала ЭВМ, задаваемых во время последовательности сигналов начальной выборки, которая начинается установкой каналом на инфор-

7286

мационные входы 1 адреса устройства, которьй после усиления поступает на входы А1 - А8 Ш1М 39, и сигнала иден тификации АДР-К на входе 6, который после усиления и регистра 41 поступает на вход А13 ШМ 38. ПЛМ 39 производит обозначение адреса, и если адрес, выставленньй на входах 1, привад0 лежит другому устройству, на выходе В1 Ш1М 39 и соответственно на входе - А9 ПЛИ 38 остается низкий уровень, и подключения устройства к интерфейсу ввода-вывода ЭВМ не происходит, В

5 случае опознания адреса на выходе В1 ПЛМ 39 и соответственно на входе А9 ПЛМ 38 устанавливается высокий уровень, после чего на выходе В2 ПЛМ 38 устанавливается высокий уровень и тем

0 самым блокируется распространение сигнала ВБР-К, поступающего с определенной задержкой после сигнала АДР-К на входе 5.

После прихода сигнала ВБР-К, по5 ступающего после усиления и регистра 41 на вход А14 ШЖ 38, устанавливается код режима, по которому память 40 формирует высокий уровень сигнала на : выходе 63, которьй после усиления про

0 ходит на выход РАБ-А 10. Получив сигнал РАБ-А, канал сбрасывает сигнал АЛР-К, после чего ПЛМ 38 устанавливает код режим, по которому ПЛМ 39 выставляет собственньй адрес устройства, а память 40 обеспечивает вьщачу

сигнала АДР-А на выходе 11 и занесе.ние собственного адреса в регистр 18.

Получив сигнал АДР-А, канал-вьщает на

входы 1 байт команды, сопровождая его

0 сигналом УПР-К по входу 7. ПЛМ 39 де- ;кодирует байт команды, поступающий на ее группу входов, после чего ПЛМ 38 устанавливает код режима, по которому память 40 обеспечивает сброс сигнала

с АДР-А. Результат декодирования байта команды выставляется на выходах В1, В2, ПЛМ 39 и через регистр 41 до сброса сигнала АДР-А поступает на входы А9, А10 Ш1М 38, при этом по результа0 У декодирования все команды канала разделяются на три группы, в первую из которых входит команда Записать, во вторую - команды Считать, Считать в обратном направлении, а в тре-г е тью - команды Проверить ввод-вывод, Уточнить состояние, управление.

После сброса сигнала АДР-1 канал сбрасывает сигнал ШР-К, после чего ПЛМ 38 устанавливает один из кодов

режима в зависимости от результата i декодирования команды, по которому ПЩ 39 обеспечивает вьщачу начального ; байта состояния в зависимости от

уровней сигналов на входах 51 - 53 и i в соответствии с табл. 2, а память 40 ; обеспечивает выдачу сигнала УПР-А на выход 12 и занесение байта состояния в регистр 18. После получения сигнала УПР-А канал либо завершает операцию, сбрасьюая сигнал ВБР-К и устанавливая сигнал по входу 8 (либо по входу 7), после чего устройство отключается от интерфейса либо про- должает операцию, вьщавая сигнал j , которьй после усиления и регистра 41 поступает на вход All ILTO l 38, и ПЛМ 38 устанавливает код режима, по которому память 40 обеспечивает сброс сигнала УПР-А, после чего канал сбрасывает сигнал ИНФ-К.:

Если устройством бьша декодирована команда, относящаяся к тре1тьей группе, и канал продолжает операцию, то I после сброса сигнала ИНФ-К устанавли- : вается код режима (поз. 18, табл. 1),

по которому память 40 обеспечивает вьщачу сигнала ИНФ-А на выход 13, при- I чем на информационных выходах 2 у ст- I ройства сигналы имеют низкий уровень.; I Получив сигнал ИНФ-А канал; либо про-; должает операцию, выполняя последова- тельность сигналов передачи данных и I вьщавая сигнал ИНФ-К, после чего уст-: I ройство сбрасывает ИНФ-А канал сбра- : сьшает сигнал ИНФ-К, а устройство : снова выставляет сигнал ИНФ-А, либо : переходит к последовательности сиг- 1 налов окончания операции, выдавая в ; ответ на очередной сигнал ИНФ-А сигнал УПР-К, ползгчив которьй устройст- во сбрасьгоает сигнал ИНФ-А, после че- го канал сбрасьшает сигнал УПР-К, после сброса которого ШЖ 38 устанавливает код режима (поз. 21, табл. 1).j по которому ПЛМ 39 .обеспечивает вьща-i чу .конечного байта состояния с указателями Канал кончил, Устройство кончило, а память 40 - выдачу сигнала 5TIP-А и занесение конечного байта , состояния в регистре 18. Канал прини-i мает конечньй байт состояния, сбрасы- вая сигнал ВБР-К и выставляя сигнал ИНФ-К, после чего устройство-,ртключа- ется от интерфейса.

Если устройством в течение посл едо.1. вательности сигналов начальной выборки декодирована команда ЗАПИСАТЬ и канал

Q г п .

5

O

0

0

продолжает операцию, то выполнение команды зависит от уровня сигнала по : входу 84, который через регистр 41 поступает на вход А7 ПЛМ 38 и свидетельствует о готовности буферной памяти передачи 22 принять от ЭВМ сообщение. Если сигнал по входу 84 имеет низкий уровень, т.е. буферная память 22 передачи не готова к приему сообщенияs то после приема каналом начал.ьного байта состояния и сброса сигнала ИНФ-К устройство переходит к последовательности сигналов окончания операции, при которой ПЛМ 38 устанавливает код режима (поз. 26, табл, 1), по ко.- торому в канал вьщается сигнал УПР-А, сопровождающий конечный байт состоя-6 НИН с указателями Канал кончил, Устройство кончило (т.е. операция заканчивается по инициативе устройст ва). Если сигнал по входу 84 имеет высокий уровень, то после каналом начального байта состояния и сброса сигнала ИНФ-К ПЛМ 38 устанавливает код режима (поз. 30, табл . 1)р по которому в канал выдается сигнал ИНФ-А, свидетельствуюгций о хютовно-г сти принять байт данных, и вьщается сигнал низкого уровня на выходе 86 которьш поступает на схемы блока 22.. Получив сигнал ИНФ-А, канал вьщает на вход 1 в сопроводжении сигнала ИНФ-К байт данных, которьй после уси.ления .поступает на группу информационных входов блока 22 и запись которого в блок 22 обеспечивается сигналом низкого уровня на выходе 86. Получив сир- нал ИНФ-К, устройство сбрасывает сиг нал ИНФ-А и снимает сигнал низкого ЗФовня на выходе.86.

После сброса сигнала ИНФ-А канал.: сбрасывает сигнал ИНФ-К, после чего устройство снова устанавливает сиг- нап и низкий уровень на выходе 86, ожидая очередной байт данных. Последовательность сигналов передачи данных при вьтолнении команды ЗА1ШСАТЬ; продолжается аналогично до тех пор, пока либо количество передаваемых байт данных не превысит емкость буфер- ной памяти 22, о чем засвидетельствует появление низкого уровня сигнала , по входу 84, что приведет к завершению операции записи по инихдаативе устройства (такое завершение считается неуспешным, и принятое сообщение отбрасьгоается), либо пока канал не инициирует последовате тьность сигналов окончания операции, вьщавая в от- вет на очередной сигнал ИНФ-А сигнал i yilP-K, получив которьй, устанавливается код режима (поз. 33, табл. 1).

по которому сбрасьшается сигнал низкого 5ФОВНЯ на выходе 86, а затем устанавливается код режима (поз. 34, табл. 1), по которому сбрасывается сигнал ИНФ-А и устанавливается сигнал низкого уровня на выходе 87, которьй . свидетельствует об успешном завершении команды Записать.

После сброса сигнала ИНФ-А канал сбрасьшает сигнал УПР-К и устройство вьщает сигнал УПР-А, сопровождающий конечный.байт состояния с последующим отключением от интерфейса, при этом снимается сигнал низкого уровня на выходе 87, после чего устройство ус танавливает сигнал готовности на выхо,де 32 и осуществляется передача принятого сообщения абоненту. Каждьй раз перед выполнением непосредственной записи данных в буферную память 22 сигналам на выходе 61 схемы адресации буЙ1ерной памяти 22 приводятся в началь ное состояние..

Если устройством во время последовательности сигналов начальной выборки декодируется комднда Считать (считать в обратном направлении) и канал продолжает операцию, то выполнение команды зависит от уровня по входу 83, который через регистр 41 поступает на вход 48 ПЛМ 38, и свидетельствует о готовности буферной памяти 20 приема передать сообщение в канал ЭВМ. Если сигнал на входе 83 имеет низкий уровень, т.е в буферной памяти 20 отсутствует .сообщение для передачи в ка- нал ЭВМ, то после приема .каналом начального байта состояния и сброса сир- нала ИНФ-К устройство переходит к последовательности сигналов окончания операции, при которой ГО1М 38 устанавливает код режима (поз. 26, табл. 1), по которому в канал вьщается сигнал У11Р-4, сопровождаюпщй конечный байт состояния, т.е. операция заканчивается по инициативе устройства.

Если сигнал.на входу 83 имеет высокий уровень, то после приема каналом ; начального байта состояния и сброса сигнала ИНФ-К на выходе 68 установит- ;СЯ высокий уровень, а на выходе 69 - низкий, в результате чего по сигналу на выходе 68 мультиплексор 19 открывается для данных, поступающих из

5

0

5

0

5

0

5

0

5

блока 20, и на выходе элемента 48 (сигнал на выходе 74) устанавливается низкий уровень, которым обеспечивается считывание байта данных из блока 20, которьй через мультиплексор 19 поступает на информационные входы регистра 18. Затем Ш1М 38 устанавливает код режима (поз. 41, табл. 1), по которому память 40 обеспечивает занесение считанного из блока 20 байта данных в регистр 18, установку сигнала ИНФ-А на выходе 13 и установку низкого уровня ка выходе 88, при этом по сигналу на выходе 66, которьй опреде- сигнал ИНФ-А, срабатывает одно - вибратор.50 и на выходе 61 йоявляется импульс, которьй поступает на схемы адресации блока 20 и после которого производится считьшание очередного байта данных из блока 20. Получив сигнал ИНФ-А, канал выдает сигнал ИНФ-К, принимая байт данных, в результате чего устройство сбрасывает сигнал ИНФ-А, а на выходе 88 устанавливается высокий уровень, которым стробируется ин- форма1щя о наличии данных в буферной памяти 20. После сброса сигнала ИНФ-А канал сбрасывает сигнал ИНФ-К, после. чего устройство снова устанавливает сигнал ИНФ-А, сопровождаквдий очередной байт данных и на выходе 88 устанавливается низкий уровень.

Операция чтения данных может заканчиваться либо по инициативе канала, когда канал в ответ на очередной сигнал ИНФ-А вьщает сигнал УПР-К, после сброса которого устройство выдает ко- нечньш байт состояния в сопровождении сигнала УПР-А с последующим отклонением от интерфейса либо по инициативе устройства при установке низкого зфов- ня на входе 83, свидетельствующего о конце данных в блоке 20. Если на входе А8 ПЛМ 38 устанавливается низкий уровень, то после приема каналом очередного байта данных и после сброса сигнала ИНФ-К ШИ- 38 устанавливает код режима, по которому вырабатывается, конечный байт состояния в сопровождении сигнала УПР-1, после приема которого каналом устройство отключается от интерфейса, цри этом на выходе 69 устанавливается высокий уровень, которым, .устройство переводится в состояние, готовности приема от абонента следующего сообщения.;

Низкие уровни сигнала БЛК-К на вхо-- де 3 и сигнала РАБ-К на входе 4 свидетельствуют о проведении каналом сброса системы. В этом случае ШМ §8 : возвращается в начальное состояние, а

на выходе 60 устанавливается ниЗкий ; уров€шь, которым сбрасывается регистр I состояния 21.

При работе устройства блок 24 работает следуюпц м образом,

Йри окончании записи информации з ю |5лок 22 блок 17 вьщает сигнал 87s которым в -блоке 22 устанавливается ; 11ризнак Конец пакета и по заднему: фронту которого устанавливается в единицу триггер 94, что приводит к is появлению низкого уровня на-выходе I элемента ИЛИ-НЕ 95, и к .последующей I установке в единицу, сигнала готовно-- Iсти по выходу 27 на прямом выходе триггера 90, при этом сигналом низко-. 20 го уровня,с инверсного выхода триггера 90 через элемент И 98 обеспечивает ся сброс триггера 94 в исходном со- , стоянии.

Передача пакета абоненту происхог 25 дит следующим образом. .

Низкий уровень на инверсном выходе: триггера 90 поступая на вход элемента ИЛИ-НЕ 95, обеспечивает высокий

115 на информационный вход триггера 90 и тем самым сигнал готовности на выходе ,27 будет установлен до тех пор, пока в момент стробирования на входе 115 не будет установлен низкий уровень, что свидетельствует о.конц данных в блоке 22, Сигнал готовности на выходе 27 сбрасывается также при поступлении на входы элемента И 91 сигнала ошибки по входу 30 либо сигнала конца передачи по входу 31. Пе редача данных считается неуспешной, если до с:игнала конца передачи по входу 31 от абонента поступает сигн ошибки 30, которьй устанавливает в е,п;иницу триггер ошибки 92, В этом сл чае по заднему фронту сигнала конца передачи на входе 31 -установится в единицу триггер, 93,, что приводит к установке сигнала готовности на вых де 27 с последующим сбросом триггер 92 и 93 н таким образом осзтцествля ется следующая попытка передает теку щего пакета. Передача данных считае ся успешной, если до сигнала конца п редачи по входу 31 не поступает сиг- напа ошибки по входу 30. В этом слу чае на выходе 124 с выхода элемента

уровень сигнала на выходе 121, псэ ко-| зо ИЛИ-НЕ 96 формируется импульс „ кото

: торому осуществляется счит:ьшание сло- ;ва данных из блока 22„ Передача паке- та инициируется абонентом, который вьщает импульсньй сигнал запроса по входу 29 отрицательной полярности„ который поступает на входы запуска одновибраторов 99 и 100. Одновибратор 100 формирует импульс длит.ельност:ью ,; ; не более 600 не, причем передним фронтом импульса на -выходе 120 прочи-: танное из блока 22 слово данных стро- .бируется в регистр 23, а импульс с инверсного выхода одновибратора 100 является сигналом ответа на выходе 28 на запрос по входу 29 и поступает к ; абоненту, Одновибратор 99 формирует , короткий импульс, который через элемент ИЛИ-НЕ 97 вызывает и после дующую установку сигнала на выходе ,: 121, причем сброс сигнала на выходе 121 вызьшает увеличение на единицу адреса памяти в блоке 22, а его уста новка приводит к срабатыванию одно- ; вибратора 101, которьй фор1 шрует импульс; меньшей длительности, чем тельность импульса на выходе 28. Зад° НИИ фронт импульса, вырабатываемого одновибратором 101 стробирует призна Конец пакета, поступающий по входу ,

115 на информационный вход триггера 90 и тем самым сигнал готовности на выходе ,27 будет установлен до тех пор, пока в момент стробирования на входе 115 не будет установлен низкий уровень, что свидетельствует о.конце данных в блоке 22, Сигнал готовности на выходе 27 сбрасывается также при поступлении на входы элемента И 91 сигнала ошибки по входу 30 либо сиг нала конца передачи по входу 31. Передача данных считается неуспешной, если до с:игнала конца передачи по входу 31 от абонента поступает сигнал ошибки 30, которьй устанавливает в е,п;иницу триггер ошибки 92, В этом слу чае по заднему фронту сигнала конца передачи на входе 31 -установится в единицу триггер, 93,, что приводит к установке сигнала готовности на выхо- де 27 с последующим сбросом триггеров 92 и 93 н таким образом осзтцествля- ется следующая попытка передает текущего пакета. Передача данных считает- ся успешной, если до сигнала конца пе редачи по входу 31 не поступает сиг- напа ошибки по входу 30. В этом слу чае на выходе 124 с выхода элемента

ИЛИ-НЕ 96 формируется импульс „ кото

.5

0

pbtM блок 22 освобождается для приема- следующего пакета из ЭВМ.

Прием данных от абонента происхо дит следующим образом.

Устройство сигнализирует о готовности принимать информацию сигналом готовности на выходе 32 высокого уро- вня. От абонента на вход одновибрато ра 109 пост-упает импульс по входу 34 запроса на прием слова данных, по переднему фронту которого на инверсном выходе одновибратора 109 вьфабатьта- ется сигнал по выходу 33 ответа, а на прямом выходе сиг:нал по выходу

g 127 одновременно с которым вырабатывается сигнал на выходе 128. Сигналы 127 и 128 обеспечивают запись слова данных5 поступающех о от абонента по входу 26 в блок 20, причем по задне-

0 фронту сигнала на выходе 127 происходит увеличение на единицу адреса памяти в блоке 20, Запись следующего слова данных в блоке 20 производится- :ири постутшении очередного сигнала запроса на вход 34,.

, Прием данных завершается либо при установке в единицу сигнала на входе ri9s что свидетельствует о переполнен :нии буферной памяти блока 20 и при5

1316

водит к сбросу сигнала готовности на выходе 32, либо при поступлении на входы элемента И 103 сигнала ошибки на вхбде 35 или сигнала конца приема на входе 36. Прием данных считается неуспешным,.если до прихода сигнала конца приема на входе 36 от абонента поступает сигнал ошибки по входу 35 Которьй устанавливает в единицу триггер ошибки 107, либо при установке сигнала переполнения на входе 119, которьй закрывает элемент ИЛИ-НЕ 108. В этом случае на входе 118 остается высокий уровень и по заднему фронту сигнала конца приема на входе 36 триггер 1.04 устанавливается в единицу, что приводит к установке низкого уровня на выходе элемента ИЛИ-НЕ 106 и к установке сигнала готовности на выхо- де 32 с последующим сбросом триггеров 104 и 107, и, таким образом, принятое сообщение отбрасывается, и устройство находится в состоянии готовности к приему следующего пакета,

Прием данных считается успешным, если не устанавливается сигнал переполнения на входе 119, и до сигнала конца приема на входе 36 не постутшл сигнал ошибки по входу 35. В этом случае установка триггера ошибки 107 не происходит, по сигналу конца приема на входе 36 сбрасывается сигнал готовности на выходе 32, и на выходе элемента ИЛИ-НЕ 108 устанавливается высокий уровень, по которому сбрасывает одновибратор 110 и сигналами на выходах 128 и 129 устанавливается признак Конец пакета в блоке 20, а по заднему фронту импульса с инверсного выхода одновибратора 110 сраба- тьгоает одновибратор 112, сигналом с прямого выхода которого по выходу 130 приводятся в начальное состоя1ше схемы адресации памяти блока 20, после чего блок 20 готов к передаче принятого от абонента пакета в ЭВМ. При чтении пакета из блока 20 блок 17 вырабатывает сигнал по выходу 69, по заднему фронту которого (после чтения пакета) устанавливается в единицу триггер 105, что приводит к последующей установке сигнала готовности на выходе 32 для приема следующего пакета.

Формула изобретения

Устройство для согфяжения ЭВМ с абонентом, содержащее блок усилителей572814

,приемников, блок усилителей-передат- .иков, блок управления обменом с ЭВЙ первый и второй буферные регистры данс ных, мультиплексор, буферную память приема, регистр состояния, буферную память передачи, блок управления обменом с абонентом, коммутатор линии выборки, причем группа информационных

0 выходов блока усилителей-передатчиков и группа информационных входов блока усилителей-приемников образуют группы выходов и входов устройства для подключения соответственно к группе ин5 формационных входов и группе информа- . цнонных выходов ЭВМ первьш, второй, третий, четвертьй, пятьот и шестой ин- ;формаи юнные выходы блока усилителей- передатчиков являются выходами устрой

20 ства для подключения соответственно к / первому, второму, третьему, четвертому, пятому и шестому командным входам ЭВК, первьй, второй, третий, четвертьй и пятьй информационные входы бло25 ка усилителей-приемников являются входами устройства для подюшчения соответственно к первому, втором у, третьему, четвертому и пятому командным выходам ЭВМ, первьй информационный вход

30 коммутатора линии выборки является входом устройства .для подключения к выходу выборки ЭВМ, группа информационных входов буферной памяти приема образует группу входов устройства для.

,, подключения к группе информационных выходов абонента, группа информационных выходов первого буферного регистра даннь х образует группу выходов устройства для подключения к группе ин0 формационных входов абонента, первьй, второй, третий, четвертьй, пятьй и шестой входы логического условия блока управления обменом с абонентом являются входами устройства для подклю5 чения соответственно к первому, второму выходам запроса, первому, второму выходам ошибки, первому, второму выходам конца передачи абонента, первьвЧ, второй, третий к0 четвертьй выходы блока управления об-- меном с абонентом являются выходами устройства для подключения соответст-, венно к первому, второму выходам готовности, первому, второму входам от5 вета абонента, шестой информационньй выход блока усилителей-передатчиков -соединен с вторым информационным вхо- дом коммутатора линии выборки, первьй информационньй выход которого соеди-

15

нен с шестым информационным входом блока усилителей-приемников, группа информационных выходов которого сое- динена с группой информационныхвходов блока управления обменом с ЭВМ, :группа информационных выходов буфер- i ной памяти передачи соединена с группой информационных входов первого буферного регистра данных, синхровход которого соединен с пятым выходом блока управления обменом с абонентом, шестой, седьмой выходы и седьмой вход I логического условия которого соединены соответственно с первым разрешаю- щим входом, с первым синхровходом и с первым информационным выходом буфер- дой памяти передачи, первьй установоч- Iньй вход которой соединен с установочным входом регистра состояний, с восьмым входом логического условия блока управления обменом с абонентом, с первым разрешаюидим входом блока усилителей-передатчиков и с вторым информа- ционным выходом коммутатора линии вы- борки, первый, второй, третий входы логического условия и первый выход блока управления обменом с ЭВМ соеди Iнены соответственно с первым, вторым i и третьим информационными выходами и с первым разрешающим входом регистра состояний, первый, второй, третий, четвертый, пятый и шестой информационные выходы блока усилителей приемников, второй информационньй выход буферной памяти передачи соединены соответственно с четвертым, пятым, шес- |тым, седьмым, восьмым, девятым и десяН |тым входами логического условия блока Iуправления обменом с ЭВМ, второй, тре- ;Тий, четвертьй, пятьй, шестой, седь- мой и восьмой выходы которого соединены соответственно с вторым установочным входом буферной памяти переда- чи, с первым, вторым, третьим, четвертым, пятым и шестым информационными входами блока усилителей-передатчиков, группа информационных входов которого соединена с группой информационных вы-; ходов второго буферного регистра дан- ных, группа информационньк входов ко-: торого соединена с группой информаци | онных выходов мультиплексора, управ- ляюпщй вход которого соединен с девя-; тым выходом блока управления обменом с ЭВМ, группа информационных выходов которого соединена с первой группой информационных входов мультиплексора J. вторая группа информационных входов

161572816

которого соединена с группой информа-, ционных выходов буферной памяти приема, первый установочный вход которой соединен с четвертым информационным выходом регистра состояний, первьй синхровход и пятьй информационньй выход которого соединены соответственно с восьмым выходом и девятым входом

10 логического условия блока управления обменом с абонентом, девятьй выхоХ которого соединен с вторыми синхро- входами регистра состояний и буферной памяти приема, десятьй, одиннадцатьй

5 и двенадцатьй входы логического условия десятьй, одиннадцатьй, двенадцатьй, тринадцатьй, четырнадцатью и пятнадцатьй выходы блока управления обменом с абонентом соединены соответ-

20 ственно с десятым выходом блока управления обменом с ЭВМ, с первым и вторым информационными выходами, с вторым установочным входом, с первым синхровходом, с первым разрешающим

25 входомJ с входом записи-чтения, с вторым разрешаюндам входом, с третьим; установочным входом буферной памяти приема, третий информационньй выход которой соединен с одиннадцатым вхс

30 дом логического условия блока управления обменом с ЭВМ, одиннадцатьй р двенаддатьй тринадцатьй и четырнад- цатьй выходы которого соединены соответственно с вторым и третьим разре- шающими входами блока усилителёй-пе35

45

50

55

редатчиков, с вторым и третьим разрешающими входами регистра состояний первьй, второй и третий информационные входы которого соединены соответственно с первым, пятым и шестым раз-: рядами группы информаилонных выходов второго буферного регистра данных, пятнаддатьй и шестнадцатьй выходы блока управления обменом с ЭВМ -соединены соответственно с вторым синхровходом буферной памяти приема и с входом записи-чтения буферной памяти передачи, второй разрешающий вход торой соединен с тринадцатым входом логического условия блока управлеьшя обменом с абонентом и с семнадцатым выходом блока управления обменом с ЭВМ, восемнадцатьй и девятнадцатьй выходы которого соединены соответственно с третьим синхровходом буферной памяти приема и с синхровходом второ го буферного регистра данных, при этом блок управления обменом с ЭВМ содержит два шифратора, постоянную

0 дом логического условия блока управления обменом с ЭВМ, одиннадцатьй р двенаддатьй тринадцатьй и четырнад- цатьй выходы которого соединены соответственно с вторым и третьим разре- шающими входами блока усилителёй-пе5

5

0

5

редатчиков, с вторым и третьим разрешающими входами регистра состояний первьй, второй и третий информационные входы которого соединены соответственно с первым, пятым и шестым раз-: рядами группы информаилонных выходов второго буферного регистра данных, пятнаддатьй и шестнадцатьй выходы блока управления обменом с ЭВМ -соединены соответственно с вторым синхровходом буферной памяти приема и с входом записи-чтения буферной памяти передачи, второй разрешающий вход торой соединен с тринадцатым входом логического условия блока управлеьшя обменом с абонентом и с семнадцатым выходом блока управления обменом с ЭВМ, восемнадцатьй и девятнадцатьй выходы которого соединены соответственно с третьим синхровходом буферной памяти приема и с синхровходом второ го буферного регистра данных, при этом блок управления обменом с ЭВМ содержит два шифратора, постоянную

память, три регистра, генератор так- tojpbix импульсов, четыре элемента И - НЕ, элемент ШШуНЕ, одновибратор, причем первый вход элемента ИЛИ-НЁ соединен с первым входом второго шифратора и является nepsbiH входом логического условия блока, второй вход элемента ИЛИ-НЕ соединен с вторым вхо дом второго шифратора и является вто- рым входом логического условия блока, третий вход элемента ИЛК-НЕ соединен с третьим входом второго шифратора и является третьим входом логического условия блока, первьм информационный вход первого регистра соединен с первым входом первого элемента И-НЕ и является четвертым входом логического условия блока, второй информационньм вход первого регистра соединен с пер- вым входом первого элемента И-НЕ и является пятым входом логического условия блока, третий, четвертьй, пя- тьй и шестой информационные входы первого регистра являются соответственно шестым, седьмым, восьмым и девятым входами логического Vcлoвия блока, выходы первого, второго элементов И-НЕ, первьй, второй, третий и четвертый прямые выходы третьего регистра являют- |ся соответственно первым, вторым, тре- тьим, четвертым, пятыми шестым выходами блока, пятый прямой выход третьего регистра соединен с первым входом запуска одновибратора и является седь- мь1м выходом блока, первый инверсный выход первого регистра соединен с первым входом первого шифратора и является восьмым выходом блока, первьй прямой выход второго регистра соединен с первым входом четвертого элемента И-НЕ и является девятым выходом блока, первьй инверсньй выход второго регистра соединен с вторым входом запуска одновибратора и является десятым выходом блока, второй прямой, второй инверсньй, третий прямой, третий ин - версньй выходы второго регистра, выход четвертого элемента И-НЕ являются соответственно одиннадцатым, двенадцатым, тринадцатым, четырнадцатым и пят надцатым выходами блока, первьй, второй, третий, четвертьй, пятьй, шестой седьмой и восьмой выходы второго шифратора образуют группу информационных выходов блока, причем в блоке управления обменом с ЭВМ синхровыход генератора тактовых импульсов соединен с синхровходами первого, .вт-орого и тре

JQ J5 2025зо

35

40

45

0

тьего регистров, четвертьй, пятьй, шестой, седьмой и восьмой прямые выходы второго регистра соединены соответственно с вторым, третьим, четвертым, пятым и шестым входами первого шифратора, с четвертым, пятым, шестым, седьмым и восьмым входами второго шифратора, с первым, вторым, третьим, четвертым и пятым адресными- входами постоянной памяти, первьй , второй, третий, четвертьй, пятьй и шестой информационные выходы которой соединены соответственно с первым, , третьим, четвертым, пятым и шестым информационными входами т-ре- тьего регистра, второй, третий и четвертьй -инверсные выходы первого регистра соединены соответственно с седьмым, восьмым и девятым входами перво-. го шифратора, первьй, второй, третий четвертьй, пятьй, шестой, седьмой и восьмой выходы которого соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым информационными входами второго регистра, пятьй инверсньй выход первого регистра соединен с десятым входом первого шифратора и с первым входом второго элемента И-КЕ, второй вход которого соединен с первым выходом второго шифратора, шестой инверсньй выход первого регистра соединен с одиннадцатым входом первого шифратора, второй вход четвертого элемента И-НЕ соединен с инверсным выходом одновибратора, отличающееся тем, что, с целью уменьшения объема аппарат фы, группа информационных входов буфернрй памяти передачи соединена с группой информационных выходов блока усилителей-приемников при этом в блоке управления обменом с ЭВМ седьмой и восьмой информационные входы первого регистра являются соответственно десятым и одиннадцатым входами логического условия блока, девятьй, десятьй, один- надцатьй, двенадцатьй, тринадцатьй, четырнадцатьй, пятнадцатьй и шестнад-- цатьй входы второго шифратора образуют группу .информационных входов блока, шестой, седьмой и восьмой инверсные выходы третьего регистра являются соответственно шестнадцатым, семнадцатым и восемнадцатым выходами блока, выход третьего элемента И-НЕ является девятнадцатым выходом блока, девятьй и десятьй информационные входы первого регистра соединены соот- ) ветственно с вторым и с первьм выходами второго шифратора, одиннадцатьй информационньй вход первого регистра; соединен с выходом элемента ИПИ-НЕ, седьмые инверсньй и прямой выходы первого регистра соединены соответст венно с третьим входом йтброго элемента И-НЕ и с двенадцатым входом первого шифратора, тринадцатьй, че- тырнадцатьй, пятнадцатьй и шестнадцатьй входы которого соединены соот- ветственно с восьмым, девятым, десятым и одиннадцатым прямыми выходами первого регистра, первьй, второй и третий входы третьего элемента И-НЕ соединены соответственно с третьим, четвертым и пятьр инверсными выходами третьего регистра, седьмой и вдсьмой информационные входы которого ..соединены соответственно с седьмым и восьмым информационными выходами постоянной .памяти,

Таблица 1

Входная переменная

16 15 14 13 12 11 10 0908 07 06 05 04 03 02-01

1 1 О

НН1НННННТО f lHHHHHI-IOOn

о о о н н н н нS о п

о о о Н Н Н Н Н 1

о н н 1 н н 1 1 о 1 н о н н н н н 1

о о о о

оо 1

0.1

О 1

о1

н ц j д j JJ

ОООННОНН1 1

н г н н н и нио J i

° ° ° « и и и оо о о о о

о н н н н н н о1 1 1 I

о о о н н н о1

Продолжение табл.1

01

О

n

п

11 1 111 11

, I .1.,

Выходная функция 8. 7- 6 54 32 1

-14 III .11 т,ш

--АААА -

n

п

н

1

i

о

I

-А

-А - А

А А

-А А г А А

-А А

-А -А -А. -А - А

25

1615728 26

I Продолжение табл.3

фие.З

ФигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1985 |

|

SU1310828A1 |

| Устройство для сопряжения ЭВМ с селекторным каналом | 1986 |

|

SU1401472A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для обмена информацией | 1985 |

|

SU1339572A1 |

Изобретение относится к вычислительной технике и может быть использовано для связи ЭВМ типа ЕС с различными устройствами цифровой вычислительной техники. Целью изобретения является уменьшение объема аппаратуры. Устройство содержит блок 15 усилителей-приемников, блок 16 усилителей-передатчиков, блок 17 управления обменом с ЭВМ, второй буферный регистр 18 данных, мультиплексор 19, буферную память 20 приема, регистр 21 состояния, буферную память 22 передачи, первый буферный регистр 23 данных, блок 24 управления обменом с абонентом, коммутатор 37 линии выборки. Устройство обеспечивает обмен данными канала ЕС ЭВМ с абонентом, реализуя протокол обмена посредством программы, размещенной в постоянной памяти. 4 ил., 3 табл.

| Устройство сопряжения для вычислительных комплексов | 1983 |

|

SU1104499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторско - свидетельст-во | |||

| СССР /по заявке № 4234309/24, / кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-23—Публикация

1988-04-28—Подача