00

со о:

со

t14

Изобретение относится к вь числи- тельной технике, в частности к устройствам для сопряжения ЭВМ с периферийными ycтpoйcтвa ffl.

Целью изобретения явля.ется повышение быстродействия и расширение номенклатуры периферийных, устройств.

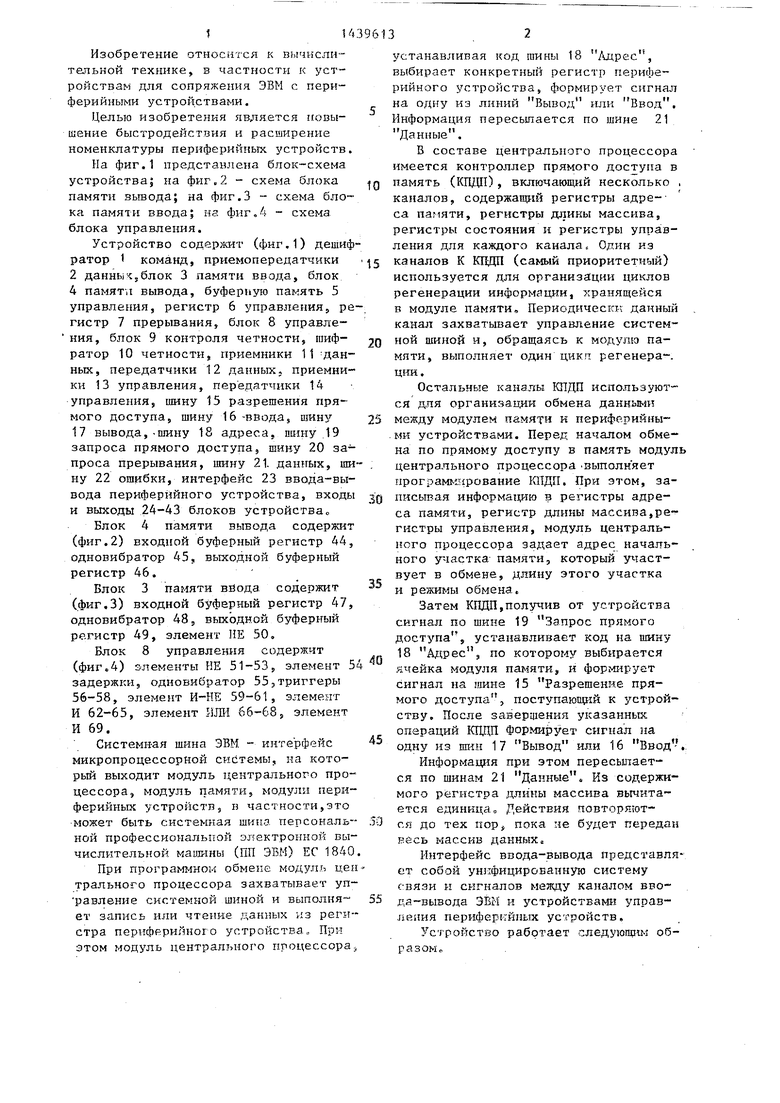

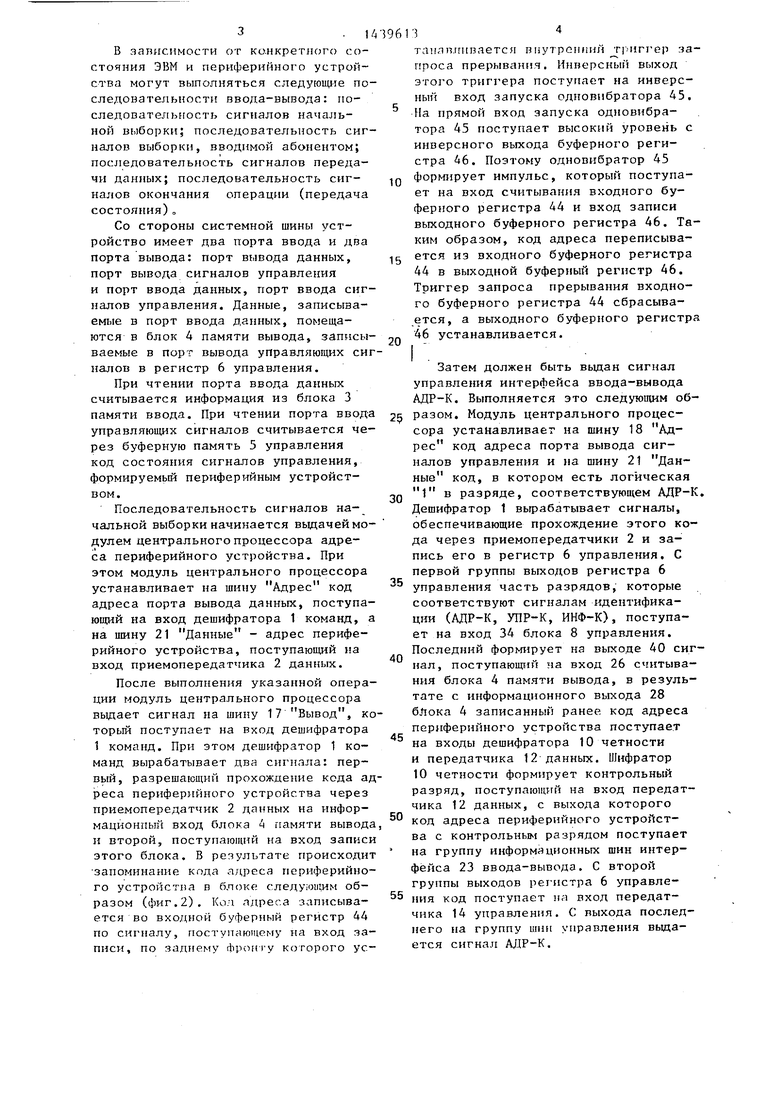

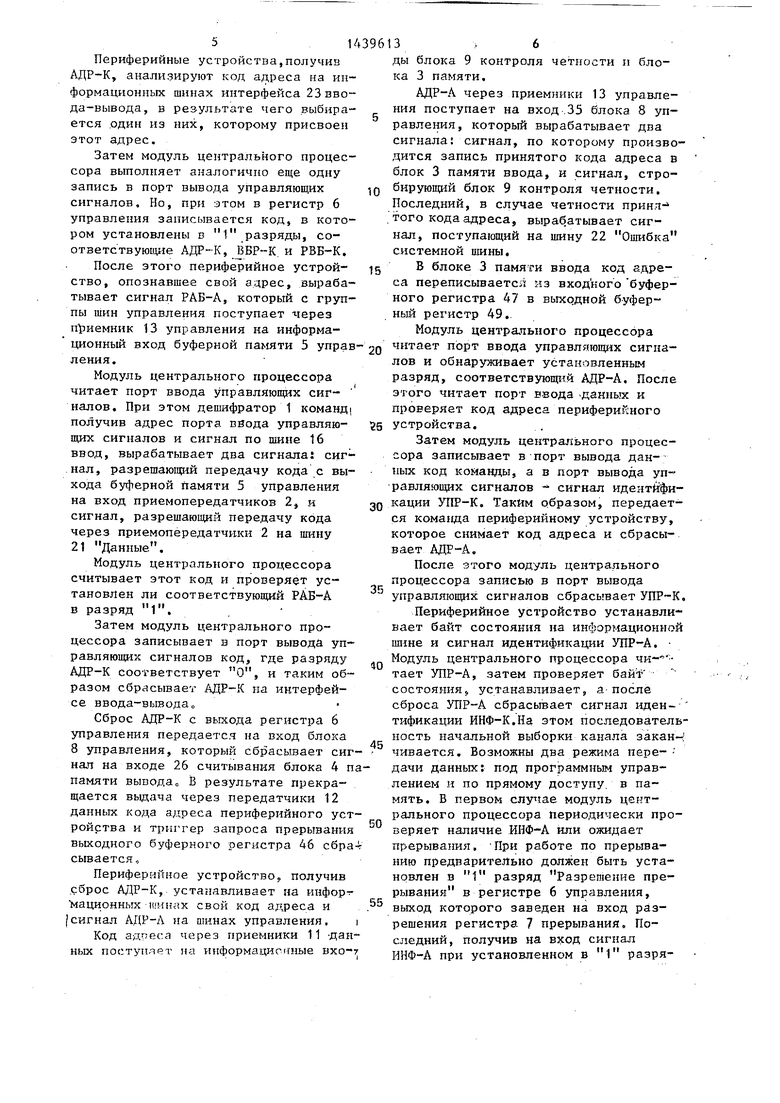

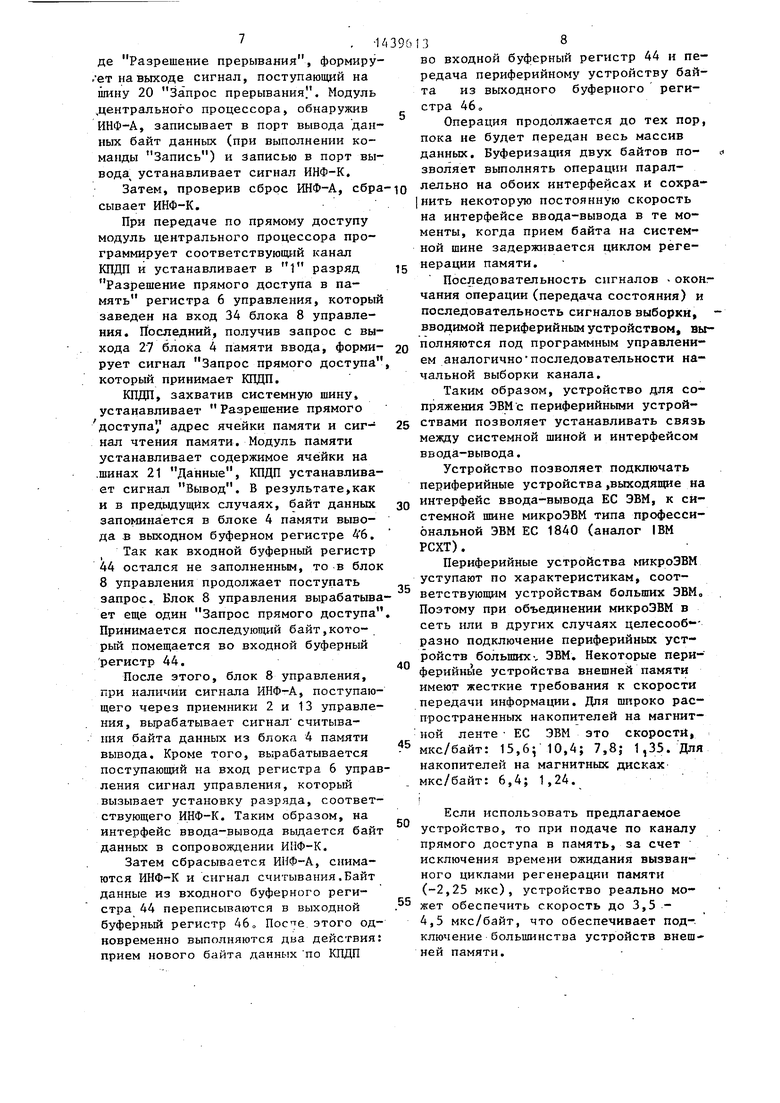

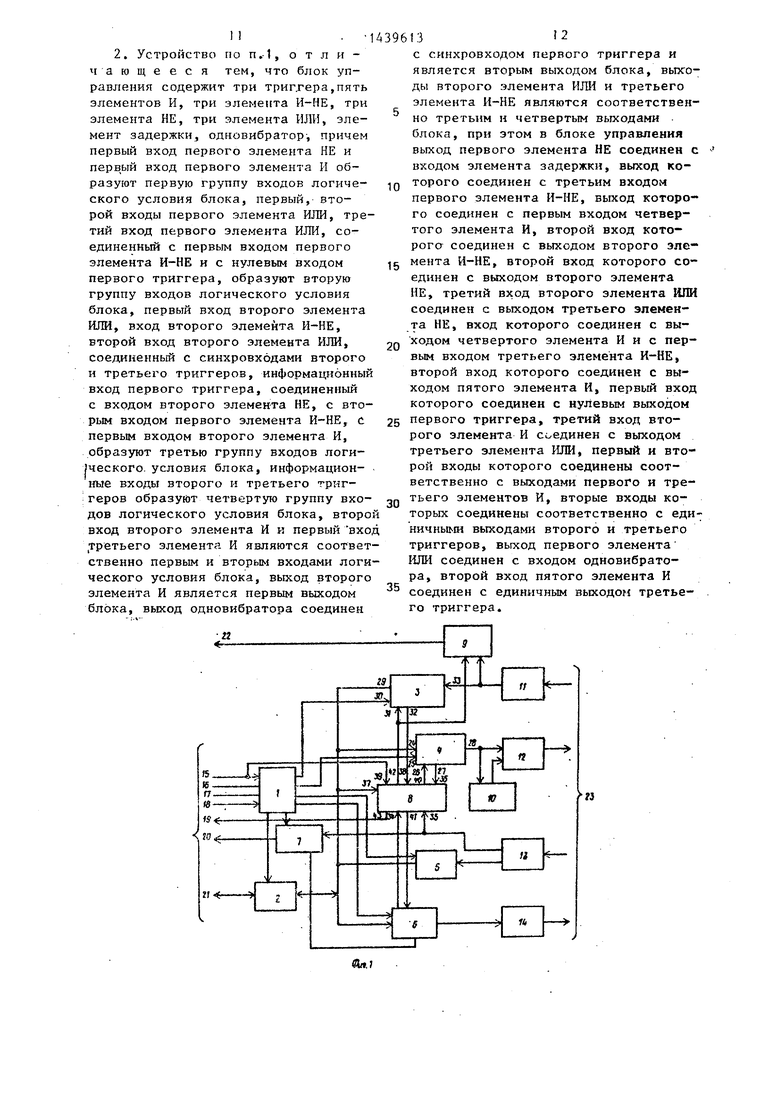

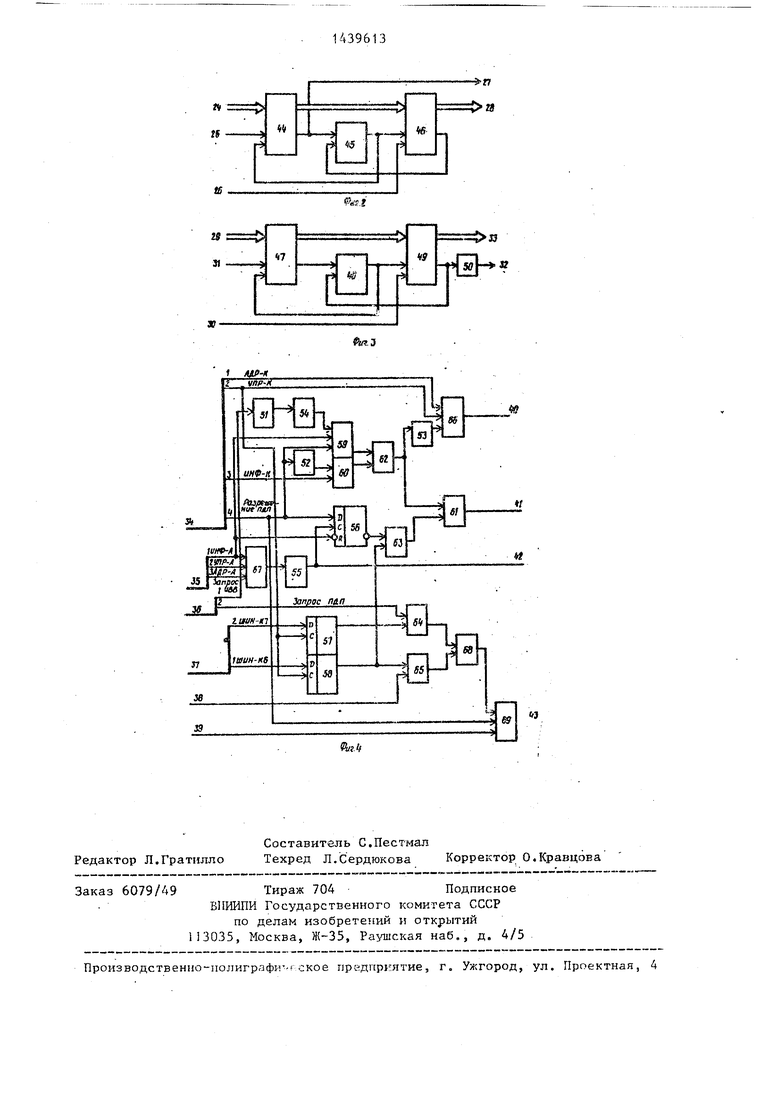

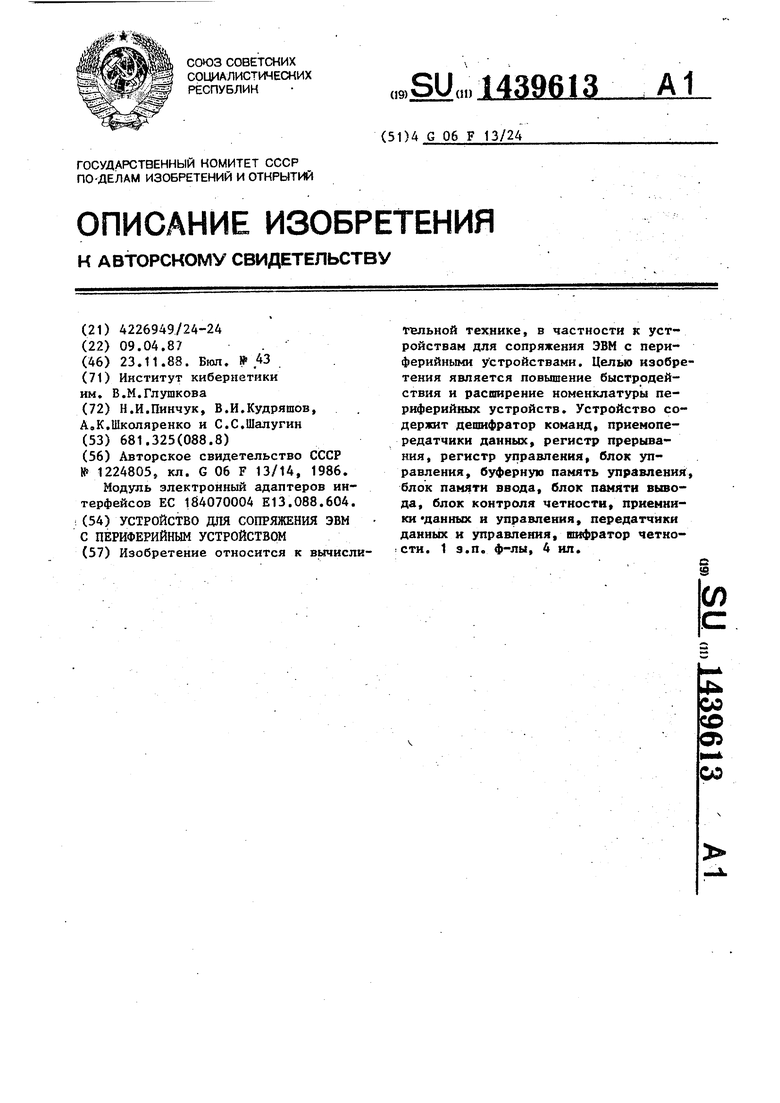

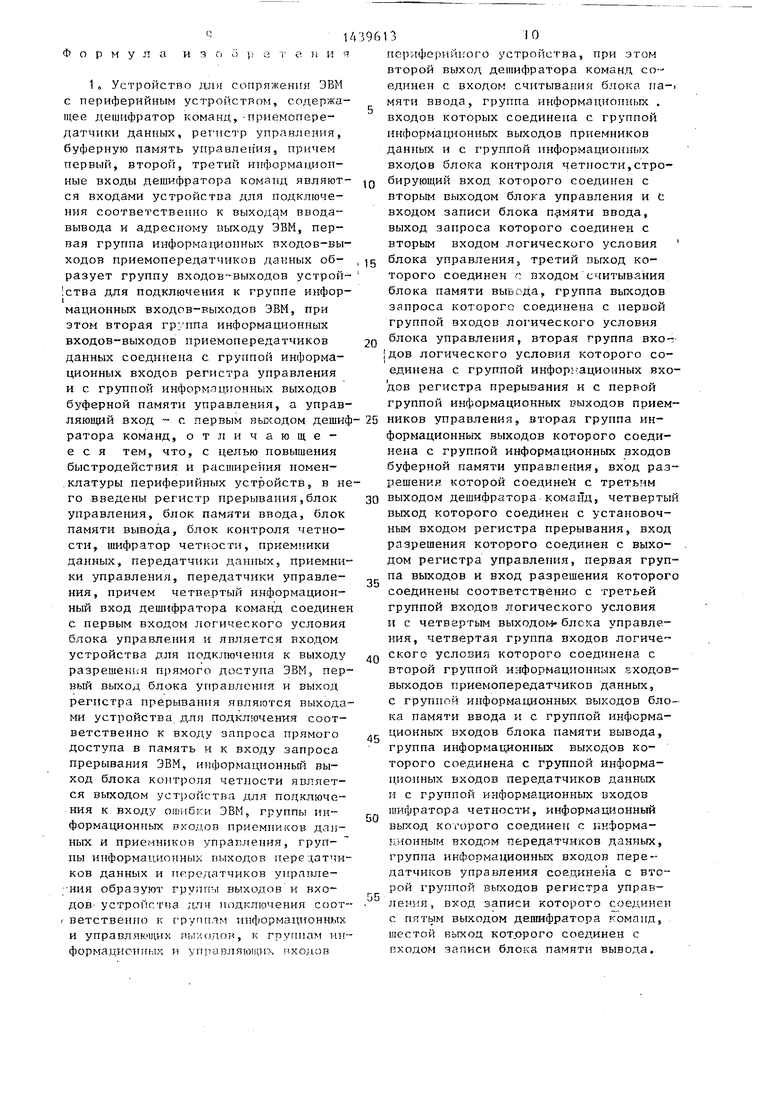

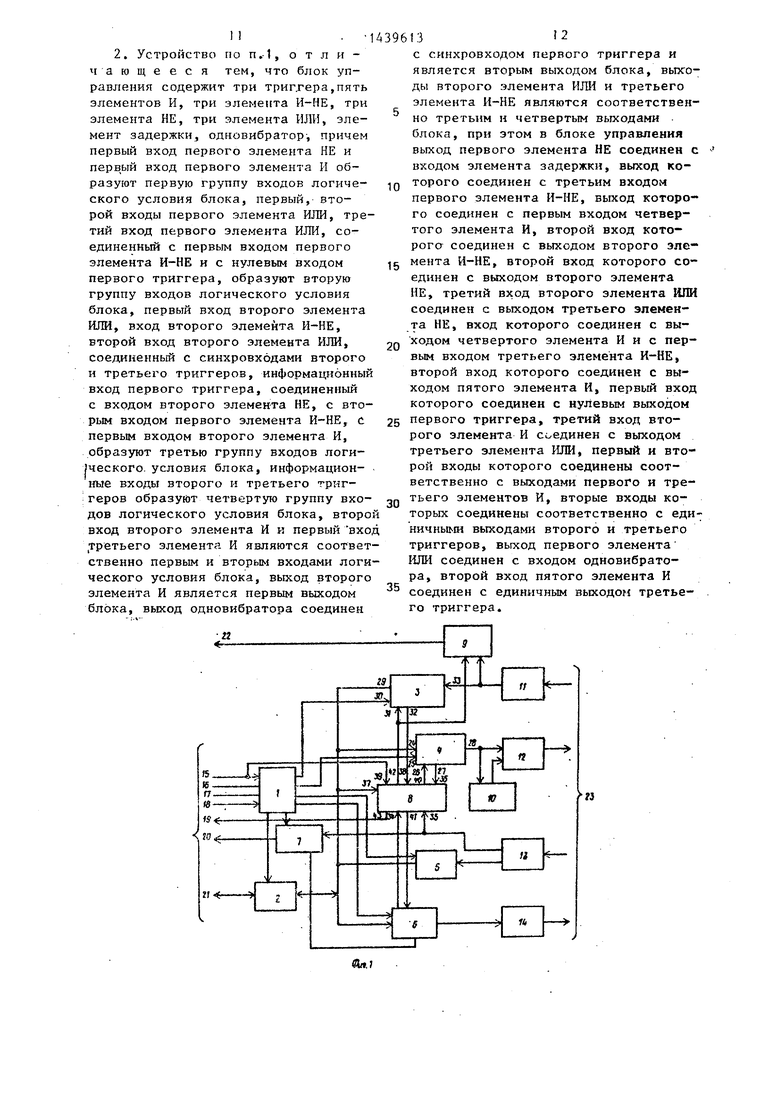

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема блока памяти вывода; на фиг.З - схема бло ка памяти ввода; на фиг,4 - схема блока управления.

Устройство содержит (фиг,1) дешифратор 1 команд, приемопередатчики 2 даннык.блок 3 памяти ввода, блок 4 памяту вывода, буферную память 5 управления, регистр 6 управления, регистр 7 прерывания, блок 8 управления, блок 9 контроля четности, шифратор 10 четности, приемники 11-данных, передатчики 12 данных, приемники 13 управления, передатчики 14 управления, шину 15 разрешения прямого доступа, шину 16 -ввода, шину 17 вывода,-шину 18 адреса, пину ,19 запроса прямого доступа, шину 20 запроса прерывания, шину 21. данных, ши ну 22 ошибки, интерфейс 23 ввода-вывода периферийного устройства, входы и выходы 24-43 блоков устройствао

Блок 4 памяти вывода содержит (фиг.2) входной буферный регистр 44, одновибратор 45, выходной буферный регистр 46.

Блок 3 памяти вйода содержит (фиг.З) входной буферный регистр 47, одновибратор 48, выходной буферный регистр 49, элемент НЕ 50,

Блок 8 управления содержит (фиг.4) элементы НЕ 51-53,, элемент 5 задержки, одновибратор 55,триггеры 56-58, элемент И-НЕ 59-61, элемент И 62-65, элемент ИЛИ 66-68, элемент И 69.

Системная шина ЭВМ - интерфейс микропроцессорной системы, на который выходит модуль центрального процессора, модуль памяти, модули периферийных устройств, ь частности,это -может быть системная шипа персональной профессиональной эхгектронной вычислительной маишны (ПП ЭВМ) ЕС 1840 При программном обмене модуль цен трального процессора захватывает уп- равление системной шиной и выполняет запись или чтение данных из регистра периферийного устройства. При этом модуль центрального процессора

0

0

5

61

5

0

5

0

5

0

5

32

устанавливая код шины 18 Адрес, выбирает конкретный регистр периферийного устройства, формирует сигнал на одну из линий Вывод или Ввод. Информация пересылается по шине 21 Данные.

В составе центрального процессора имеется контроллер прямого доступа в память (КПД11), включаюш 1й несколько , каналов, содержащий регистры адреса памяти, регистры длины массива, регистры состояния и регистры управления для каждого канала. Один из каналов К КЩЩ (самый приоритетный) используется для организации циклов регенерации информации, хранящейся в модуле памяти. Периодически данный канал захватывает управление системной шиной и, обращаясь к модулю памяти, выполняет один цикп регенера-. ции.

Остальные каналы 1ШДП используются для организации обмена данными между модулем памяти к периферийны- .ми устройствами. Перед началом обмена по прямому доступу в память модуль центрального процессора выполняет программтфование КПДП. При этом, записывая информацию в регистры адреса памяти, регистр длины массива,регистры управления, модуль центрального процессора задает адрес начального участка памяти, который участвует в обмене, длину этого участка и режимы обмена.

Затем КПДП,получив от устройства сигнал по шине 19 Запрос прямого доступа, устанавливает код на шину 18 , по которому выбирается ячейка модуля , и формирует сигнал на шина 15 Разрешение прямого доступа, поступающий к устройству. После завершения указанных операций КПДП формирует сигнал па одну из шин 17 Вывод или 16 Ввод..

Информация при этом пересьтает- ся по шинам 21 Данные, Кз содержимого регистра длины массива вычитается единица Действия повторяются до тех nopj пока не будет передан весь массив данных.

Интерфейс ввода-вывода представляет собой унифицированную систему связи и сигналов между каналом ввода-вывода ЭВМ и устройствам управления периферийных устройств.

Устройство работает следующим образом.

3. 1

В зависимости от ко.нкретного состояния ЭВМ и периферийного устройства могут выполняться следующие последовательности ввода-вывода: последовательность сигналов начальной выборки; последовательность сигналов выборки, вводимой абонентом; последовательность сигналов передачи данных; последовательность сигналов окончания операции (передача состояния)о

Со стороны системной шины устройство имеет два порта ввода и два порта вывода: порт вывода данных, порт вывода сигналов управления и порт ввода данных, порт ввода сигналов управления. Данные, записываемые в порт ввода данных, помещаются в блок 4 памяти вывода, записываемые в порт вывода управляющих сигналов в регистр 6 управления.

При чтении порта ввода данных считывается информация из блока 3 памяти ввода. При чтении порта ввода управляюиц1х сигналов считывается через буферную память 5 управления код состояния сигналов управления, формируемый периферийным устройством.

Последовательность сигналов начальной выборки начинается вьщачей модулем центрального процессора адреса периферийного устройства. При этом модуль центрального процессора устанавливает на шину Адрес код адреса порта вывода данных, поступающий на вход дешифратора 1 команд, а на шину 21 Данные - адрес периферийного устройства, поступающий на вход приемопередатчика 2 данных.

После выполнения указанной операции модуль центрального процессора выдает сигнал на шину 17 Вывод, который поступает на вход дешифратора 1 команд. При этом дешифратор 1 команд вырабатывает два сигнала: первый, разрешающий прохождение кода адреса периферийного устройства через приемопередатчик 2 данных на информационный вход блока ч памяти вывода и второй, поступающий на вход записи этого блока. В результате происходит запоминание кода адреса периферийного устройства в блоке следу;оишм образом (фиг.2). Кол адреса записывается во входной буферный регистр 44 по сигналу, поступающему на вход записи, по заднему фронту которого ус196

0

5

0

5

0

5

0

5

0

5

.ггиваетси внутренний триггер запроса прерывания. Инверсный выход этого триггера поступает на инверсный вход запуска одновибратора 45. На прямой вход запуска одновибратора 45 поступает высокий уровень с инверсного выхода буферного регистра 46. Поэтому одноБибратор 45 формирует импульс, который поступает на вход считывания входного буферного регистра 44 и вход записи выходного буферного регистра 46. Таким образом, код адреса переписывается из входного буферного регистра 44 в выходной буферный регистр 46. Триггер запроса прерывания входного буферного регистра 44 сбрасывается, а выходного буферного регистра 46 устанавливается.

Г.

Затем должен быть выдан сигнал управления интерфейса ввода-вывода АДР-К. Выполняется это следующим образом. Модуль центрального процессора устанавливает на шину 18 Адрес код адреса порта вывода сигналов управления и на шину 21 Данные код, в котором есть логическая 1 в разряде, соответствующем АДР-К. Дешифратор 1 вырабатывает сигналы, обеспечивающие прохождение этого кода через приемопередатчики 2 и запись его в регистр 6 управления. С первой группы выходов регистра 6 управления часть разрядов, которые соответствуют сигналам идентификации (АДР-К, УПР-К, ИНФ-К), поступает на вход 34 блока 8 управления. Последний формирует на выходе 40 си1- нал, поступающий на вход 26 с гитыва- ния блока 4 памяти вывода, в результате с информационного выхода 28 блока 4 записанный ранее код адреса периферийного устройства поступает на входы дешифратора 10 четности и передатчика 12 данных. Шифратор 10 четности формирует контрольный разряд, поступающ1тй на вход передатчика 12 данных, с выхода которого код адреса периферийного устройства с контрольным разрядом поступает на группу информационных шин интерфейса 23 ввода-вывода. С второй группы выходов рег истра 6 управления код поступает на вход передатчика 14 управления. С выхода последнего на группу шин управления выдается сигнал АДР-К.

514

Периферийные устройства,получив АДР-К, анализируют код адреса на информационных шинах интерфейса 23 ввода-вывода, в результате чего выбира- ется .один из них, которому присвоен этот адрес.

Затем модуль центрального процессора выполняет аналогично еще одну запись в порт вывода управляющих сигналов. Но, при этом в регистр 6 управления записывается код, в котором установлены в разряды, соответствующие АДР-К, . и РВБ-К.

После этого периферийное устрой- ство, опознавшее свой адрес, вырабатывает сигнал РАБ-А, который с группы шин управления поступает через п зиемник 13 управления на информационный вход буферной памяти 5 управ ления,

Модуль центрального процессора читает порт ввода управляющих сигналов. При этом дешифратор 1 команд| получив адрес порта ввода управляю- щих сигналов и сигнал по шине 16 ввод, вырабатывает два сигнала сигнал, разрешающий передачу кода с выхода буферной памяти 5 управления на вход приемопередатчиков 2, и сигнал, разрешающий передачу кода через приемопередатчики 2 на шину 21 Данные.

Модуль центрального процессора считывает этот код и проверяет ус тановлен ли соответствующий РАБ-А в разряд 1,

Затем модуль центрального процессора записывает и порт вывода управляющих сигналов код, где разряду АДР-К соответствует О, и таким образом сбрасывает АДР-К на интерфейсе ввода-вьгоодао

Сброс АДР-К с выхода регистра 6 управления передается на вход блока 8 управления, который сбрасывает сигнал на входе 26 считывания блока 4 п памяти выводао В результате прекращается выдача через передатчики 12 данных кода адреса периферийного устройства и триггер запроса прерывания выходного буферного регистра 46 сбра сывается,

Периферийное устройство, получив сброс АДР-К, устанавливает на инфор-г- мационньгх шинах свой код адреса и сигнал АДР-А на шинах управления,

Код адг;еса через приемники 11 -дан ньпс поступяет на информацнсггные вхо

g 0

;5 о

5

5

0

55

3 . 6

ды блока 9 контроля четности и блока 3 памяти.

АДР-А через приемники 13 управления поступает на вход .35 блока 8 управления , который вырабатывает два сигнала: сигнал, по которому производится запись принятого кода адреса в блок 3 памяти ввода, и сигнал, стро- бирующий блок 9 контроля четности. Последний, в случае четности принл- того кода адреса, вырабатывает сигнал, поступающий на шину 22 Ошибка системной ишны,

В блоке 3 памяти ввода код адреса переписывается из входного буферного регистра 47 в выходной буферный регистр 49..

Модуль центрального процессора читает порт ввода управляющих сигналов и обнаруживает установленным разряд, соответствующий АДР-А. После этого читает порт в-вода «данных и проверяет код адреса периферийного устройства.

Затем модуль центрального процессора записьтает в порт вывода данных код команды, а в порт вывода уп равляющих сигналов сигнал идентификации УПР-К. Таким образом, передается команда периферийному устройству, которое снимает код адреса и сбрасывает АДР-А.

После этого модуль центрального процессора записью в порт вывода управляющих сигналов сбрасывает УПР-К.

Периферийное устройство устанавливает байт состояния на информационной шине и сигнал идентификации УПР-А. Модуль центрального процессора тает УПР-А, затем проверяет байУ состояния, устанавливает, а-после сброса УПР-А сбрасывает сигнал иден- тификации ИНФ-К.На этом последовательность начальной выборки канала заканН чивается. Возможны два режима пере- дачи данных: под программным управлением и по прямому доступу, в память. В первом случае модуль центрального процессора периодически проверяет наличие ИНФ-А или ожидает прерывания. -При работе по прерыванию предварительно должен быть установлен в 1 разряд Разрешение прерывания в регистре 6 управления, выход которого заведен на вход разрешения регистра 7 прерывания. Последний, получив на сигнал ИНФ-А при установленном в 1 разря . -1

де Разрешение прерывания, формиру- г ет на выходе сигнал, поступающий на шину 20 Запрос прерывания. Модуль .центрального процессора, обнаружив ИНФ-А, записывает в порт вывода данных байт данных (при выполнении команды Запись) и записью в порт вывода устанавливает сигнал ИНФ-К.

Затем, проверив сброс ИНФ-А, сбра сывает ИНФ-К.

При передаче по прямому доступу модуль центрального процессора программирует соответствующий канал КПДП и устанавливает в 1 разряд Разрешение прямого доступа в память регистра 6 управления, который заведен на вход 34 блока 8 управления. Последний, получив запрос с выхода 27 блока 4 памяти ввода, форми- рует сигнал Запрос прямого доступа который принимает КПДП.

КПДП, захватив системную шину, устанавливает Разрешение прямого доступа / адрес ячейки памяти и сиг- нал чтения памяти. Модуль памяти устанавливает содержимое ячейки на .шинах 21 Данные, КПДП устанавливает сигнал Вывод. В результате,как и в предыдущих случаях, байт данных запоминается в блоке 4 памяти вывода в выходном буферном регистре 46.

Так как входной буферный регистр 44 остался не заполненным, то в блок 8 управления продолжает поступать запрос. Блок 8 управления вырабатывает еще один Запрос прямого доступа Принимается последующий байт,который помещается во входной буферный регистр 44.

После этого, блок 8 управления, при наличии сигнала ИНФ-А, поступающего через приемники 2 и 13 управления, вырабатывает сигнал считывания байта данных из блока 4 памяти вывода. Кроме того, вырабатывается поступаюшяй на вход регистра 6 управления сигнал управления, который вызывает установку разряда, соответствующего ИНФ-К. Таким образом, на интерфейс ввода-вывода вьщается байт данных в сопровождении ИИФ-К.

Затем сбрасывается ИНФ-А, снимаются ИНФ-К и сигнал считывания,Байт данные из входного буферного регистра 44 переписываются в выходной буферный регистр 46„ этого одновременно выполняются два действия: прием нового байта данных по КГЦЩ

5 0

5 О

0

5

5

0

138

во входной буферный регистр 44 и передача периферийному устройству байта из выходного буферного регистра 46 о

Операция продолжается до тех пор, пока не будет передан весь массив данных. Буферизация двух байтов по- ч зволяет выполнять операции параллельно на обоих интерфейсах и сохра- I нить некоторую постоянную скорость на интерфейсе ввода-вывода в те моменты, когда прием байта на системной шине задерживается циклом регенерации памяти.

Последовательность сигналов - оконг- чания операции (передача состояния) и последовательность сигналов выборки, - вводимой периферийным устройством, выполняются под программным управлением аналогично последовательности начальной выборки канала.

Таким образом, устройство для сопряжения ЭВМ с периферийными устройствами позволяет устанавливать связь между системной шиной и интерфейсом ввода-вывода.

Устройство позволяет подключать периферийные устройства ,выходящие на интерфейс ввода-вывода ЕС ЭВМ, к системной шине микроэвм типа профессиональной ЭВМ ЕС 1840 (аналог IBM РСХТ).

Периферийные устройства микроЭВМ уступают по характеристикам, соответствующим устройствам больших ЭВМ, Поэтому при объединении микроЭВМ в сеть или в других случаях целесооб -- разно подключение периферийных устройств больших-, ЭВМ. Некоторые периферийные устройства внешней памяти имеют жесткие требования к скорости передачи информации. Для широко распространенных накопителей на магнитной ленте ЕС ЭВМ это скорости, МКС/байт: 15,6 10,4; 7,8| 1,35. Для накопителей на магнитных дисках МКС/байт: 6,4; 1,24.

Если использовать предлагаемое устройство, то при подаче по каналу прямого доступа в память, за счет исключения времени ожидания вызванного циклами регенерации памяти (-2,25 мкс), устройство реально может обеспечить скорость до 3,5 - 4,5 МКС/байт, что обеспечивает под-, ключение большинства устройств внешней памяти.

Формула

и 3

14

и и я

1 о Устройство для сопряжения ЭВМ с периферийным устройством, содержащее дешифратор команд,-приемопередатчики данных, регистр управления, буферную память уиравле11ия, причем первый, второй, третий информационные входы дешифратора комащ; являются входами устройства для подключения соответственно к выходам ввода- вывода и адресному выходу ЭВМ, первая группа информационных входов-выходов приемопередатчиков данных образует группу входов-выходов устрой ;ства для подключения к группе инфорI

мационных входов-выходов ЭВМ, при

этом вторая группа информационных входов-выходов приемопередатчиков данных соединена с группой информационных входов регистра управления и с группой информационных выходов буферной памяти управления, а управляющий вход с первым вькодом дешиф ратора команд, отличающееся тем, что, с целью повышения быстродействия и расширения номенклатуры периферийных устройств, в него введены регистр прерывания,блок управления, блок памяти ввода, блок памяти вывода, блок контроля четности, шифратор четности, приемники данных, передатчики данных, приемники управления, передатчики управления, причем четвертый информационный вход дешифратора команд соединен с первым входом логического условия блока управления и является входом устройства для подключения к выходу разрешен -:я прямого доступа ЭВМ, первый выход блока управления и выход регистра прерывания являются выходами устройства для подключения соответственно к входу запроса прямого доступа в память и к входу запроса прерывания ЭВМ, информационньй выход блока ко}1тропя четности является выходом устройства для подключения к входу ошибки ЭВМ, группы информационных входов приемников данных и приемников управления, группы информатдионных выходов дере датчиков данных и передатчиков уиравле- -ния образуют группы выходов и входов- устройства дли подключения соотI ветственти:) к ругитлм информационных. и управляющих яьглодов, к гругпшм i-u формац1 с-ниых и у111 а}эля10 1;их яходов

15

0

1310

перифернЙ1юг о устройства, при этом второй выход дешифратора команд соединен с входом считывания блока ira-i мяти ввода, группа информационных . входов которых соединена с группой информационных выходов приемников данных и с группой информационных входов блока контрох Я четности,стро- бирующий вход которого соединен с вторым выходом блока управления и t входом записи блока памяти ввода, выход запроса которого соединен с вторым входом логического условия блока управления, третий выход которого соединен -с входом считывания блока памяти вывода группа выходов запроса которого соединена с первой группой входов логического условия блока управления, вторая группа вхо- доз логического условия которого со25

30

35

40

45

единена с группой инфорьгационных входов регистра прерывания и с первой группой информационных выходов приемников управления, вторая группа ин- формационнытс выходов которого соединена с группой информационных входов буферной памяти управления, вход разрешения которой соедине Н с третьим выходом дешифратора - команд, четвертый выход которого соединен с установочным входом регистра прерывания, вход разрешения которого соединен с выходом регистра управления, первая группа выходов и вход разрешения которого соединены соответственно с третьей группой входов логического условия и с четвертым выходом- блока управления, четвертая группа входов логиче™ ского условия которого соединена с второй группой информационных ЕХОДОВ- выходов приемопередатчиков данных, с группой информационных выходов блока памяти ввода и с группой информационных входов блока памяти вывода, группа информационных выходов которого соединена с группой информа- н,ионных входов передатчиков данных и с группой информационных входов шифратора четности, информационный выход которого соединен с информа- згионныг- входом передатчиков данных, группа информа1щонных входов передатчиков управления соединена с второй группой 55ЫХОДОВ рвгистрн управ- лення, вход записи которого соединен с пятым выходом дешифратора команд, 1 1естой выход которого соединен с входом записи блока памяти вывода.

И

/гз

f

Раг-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для мультиплексного канала | 1984 |

|

SU1265787A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1986 |

|

SU1363226A1 |

| Устройство для сопряжения ЭВМ с селекторным каналом | 1986 |

|

SU1401472A1 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

Изобретение относится к вычислиттгльной технике, в частности к устройствам для сопряжения ЭВМ с периферийными устройствами. Целью изобретения является повышение быстродействия и расширение номенклатуры периферийных устройств. Устройство содержит дешифратор команд, приемопередатчики данных, регистр прерывания, регистр управления, блок управления, буферную память управления, блок памяти ввода, блок памяти вывода, блок контроля четности, приемники «данных и управления, передатчики данных и управления, шифратор четно- :сти. 1 э.п. ф-лы, 4 ил.

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1224805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Модуль электронный адаптеров интерфейсов ЕС 184070004 Е13.088.604. | |||

Авторы

Даты

1988-11-23—Публикация

1987-04-09—Подача