Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах в качестве спецпроцессора для ре- шения систем линейных алгебраических уравнений.

Цель изобретения - повышение быстродействия устройства.

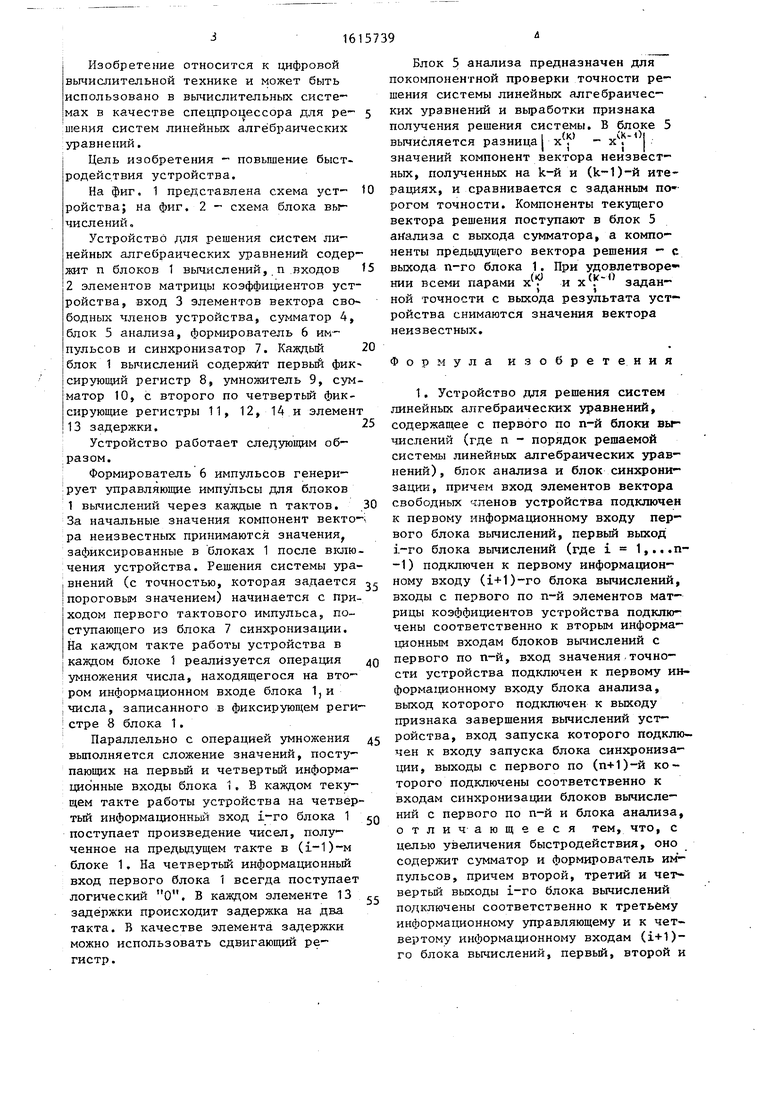

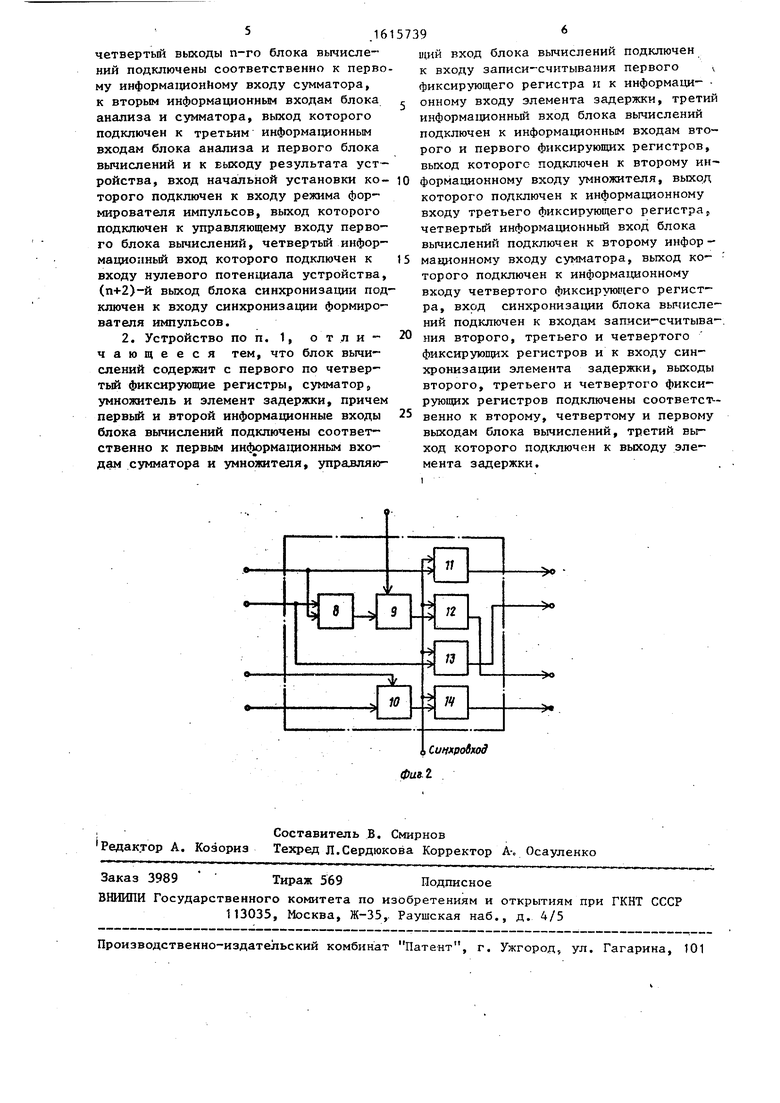

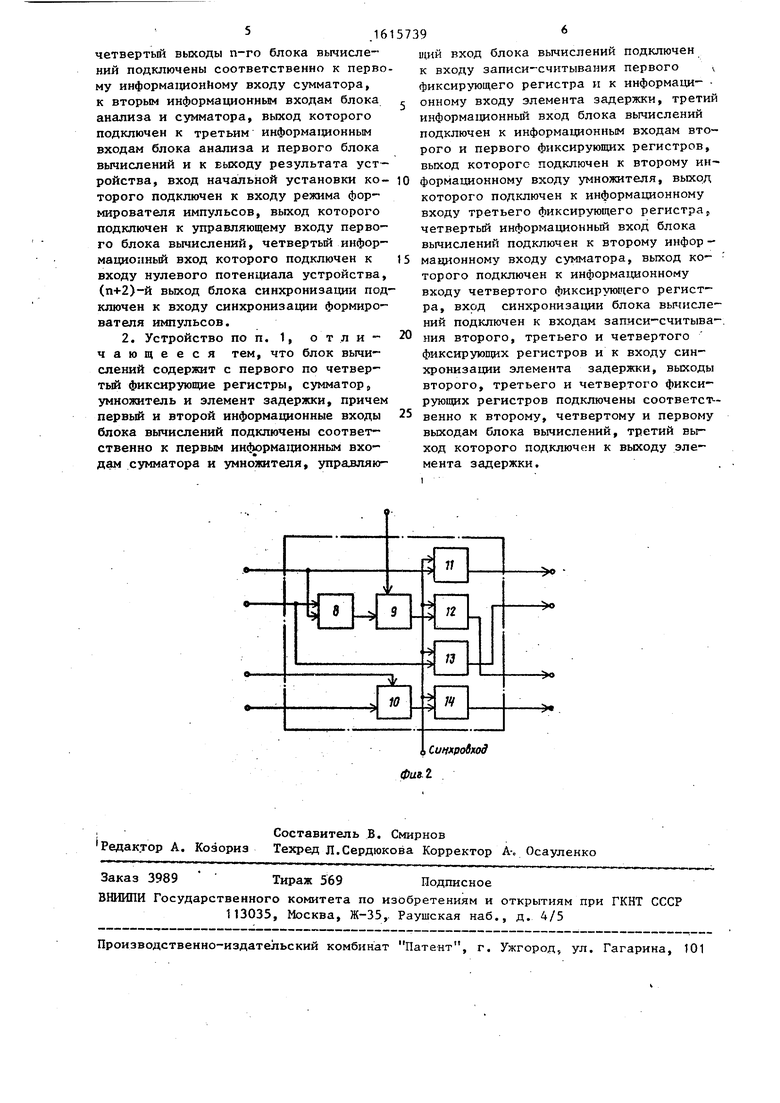

На фиг, 1 представлена схема уст- ройства; на фиг. 2 - схема блока вычислений.

Устройство для решения систем ли- |нейньгх алгебраических уравнений содержит п блоков 1 вычислений, п входов 2 элементов матрицы коэффициентов устройства, вход 3 элементов вектора сво бодных членов устройства, сумматор 4, блок 5 анализа, формирователь 6 им- пульсов и синхронизатор 7. Каждый блок 1 вычислений содержит первый фик |сирующий регистр 8, умножитель 9, сум матор 10, с второго по четвертьй фиксирующие регистры 11, 12, 14 и элемен 13 задержки.

Устройство работает следующим образом.

Формирователь 6 импульсов генери- рует управляющие импульсы для блоков 1 вычислений через каждые п тактов. За начальные значения компонент векто ра неизвестных принимаются значения, зафиксированные в блоках 1 после вютю чения устройства. Решения системы зфа ,внений (с точностью, которая задается Пороговым значением) начинается с приходом первого тактового импульса, поступающего из блока 7 синхронизаи1ии. На каждом такте работы устройства в каядом блоке 1 реализуется операция i умножения числа, находящегося на втором информационном входе блока 1,и ; числа, записанного в фиксируюп1;ем реги стре 8 блока 1.

Параллельно с операцией умножения выполняется сложение значений, поступающих на первьй и четвертьй информа- цибнные входы блока 1. В каждом текущем такте работы устройства на четвертьй информационньй вход i-ro блока 1 поступает произведение чисел, полученное на предыдущем такте в (1-1)-м блоке 1. На четвертьй информационньй вход первого блока 1 всегда поступает логический О. В каждом элементе 13 задержки происходит задержка на два такта. В качестве элемента задержки можно использовать сдвигающий регистр .

5

5

5 0

30 - Q

дз JQ

Блок 5 анализа предназначен для покомпонентной проверки точности решения системы линейных алгебраических уравнений и выработки признака получения решения системы. В блоке 5 вычисляется разница Г x -

значений компонент вектора неизвестных, полученных на k-й и (k-1)-й итерациях, и сравнивается с заданным порогом точности. Компоненты текущего вектора решения постзтают в блок 5 анализа с выхода сумматора, а компоненты предьщуи(его вектора решения - с

вьпсода п-го блока 1. При удовлетворв (j/i ()

НИИ всеми парами х . и х г заданной точности с выхода результата устройства снимаются значения вектора неизвестных.

Формула изобретения

1. Устройство для решения систем линейных алгебраических уравнений, содержащее с первого по п-й блоки вычислений (где п - порядок решаемой системы линейных алгебраических уравнений) , блок анализа и блок синхронизации, причем вход элементов вектора свободных членов устройства подключен к первому информационному входу первого блока вычислений, первый выход i-ro блока вычислений (где i 1,...п- -1) подключен к первому информационному входу (i+1)-ro блока вычислений, входы с первого по п-й элементов матрицы коэффициентов устройства подключены соответственно к вторьи информационным входам блоков вьтислений с первого по п-й, вход значения.точности устройства подключен к первому ин- форма1щонному входу блока анализа, выход которого подключен к выходу признака завершения вычислений устройства, вход запуска которого подклю чен к входу запуска блока синхронизации, выходы с первого по (п+1)-й которого подключены соответственно к входам синхронизации блоков вычислений с первого по п-й и блока анализа, отличающееся тем, что, с целью увеличения быстродействия, оно содержит сумматор и формирователь им пульсов, причем второй, третий и чет вертьй выходы i-ro блока вычислений подключены соответственно к третьему информационному управляющему и к четвертому информационному входам (i+1)- го блока вычислений, первьй, второй и

516

четвертьй выходы п-го блока вычислений подключены соответственно к первому информа1010нИому входу сумматора, к вторым информационным входам блока анализа и сумматора, выход которого подключен к третьим информатщонным входам блока анализа и первого блока вычислений и к выходу результата устройства, вход начальной установки которого подключен к входу режима формирователя импульсов, выход которого подключен к управляющему входу первого блока вычислений, четвертый информационный вход которого подключен к входу нулевого потенциала устройства, (п+2)-й выход блока синхронизации подключен к входу синхронизации формирователя импульсов.

2. Устройство по п. 1, отличающееся тем, что блок вычислений содержит с первого по четвертый фиксирующие регистры, сумматор, умножитель и элемент задержки, причем первый и второй информационные входы блока вычислений подключены соответственно к первым информа1щонным входам сумматора и умножителя, управляю

9

щнй вход блока вычислений подключен к входу записи-считывания первого v фиксирующего регистра и к информаци-

онному входу элемента задержки, третий информанлонньй вход блока вычислений подключен к информационным входам второго и первого фиксирующих регистров, выход которого подключен к второму информационному входу умножителя, выход которого подключен к информационному входу третьего фиксирующего регистра,, четвертый информационный вход блока вычислений подключен к второму инфор - мационному входу сумматора, вьгеод ко- торого подключен к информационному входу четвертого фиксирующего регистра, вход синхронизации блока вычислений подключен к входам записи-считыва-. ния второго, третьего и четвертого фиксирующих регистров и к входу синхронизации элемента задержки, выходы второго, третьего и четвертого фиксирующих регистров подключены соответственно к второму, четвертому и первому выходам блока вычислений, третий выход которого подключен к выходу элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1566367A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1566366A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1989 |

|

SU1688257A1 |

| Устройство для решения систем линейныых алгебраических уравнений | 1986 |

|

SU1394218A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1721612A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1569846A1 |

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах в качестве спецпроцессора для решения систем линейных алгебраических уравнений. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для решения систем линейных алгебраических уравнений содержит N блоков 1 вычислений, где N - порядок решаемой системы линейных алгебраических уравнений, сумматор 4, блок 5 анализа, формирователь 6 импульсов и блок 7 синхронизации. Данное устройство предназначено для нахождения решения системы линейных алгебраически: уравнений итерационным методом типа Гаусса-Зейделя. 1 з.п.ф, 2 ил.

CuffxpoSxod

| Устройство для решения системАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU813445A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1987 |

|

SU1462353A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-23—Публикация

1989-02-13—Подача