4) О) Кд

Рд сд

Од

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1566367A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1566366A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1989 |

|

SU1688257A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1989 |

|

SU1615739A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1721612A1 |

| Модуль для логических преобразований булевых функций | 1989 |

|

SU1667050A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

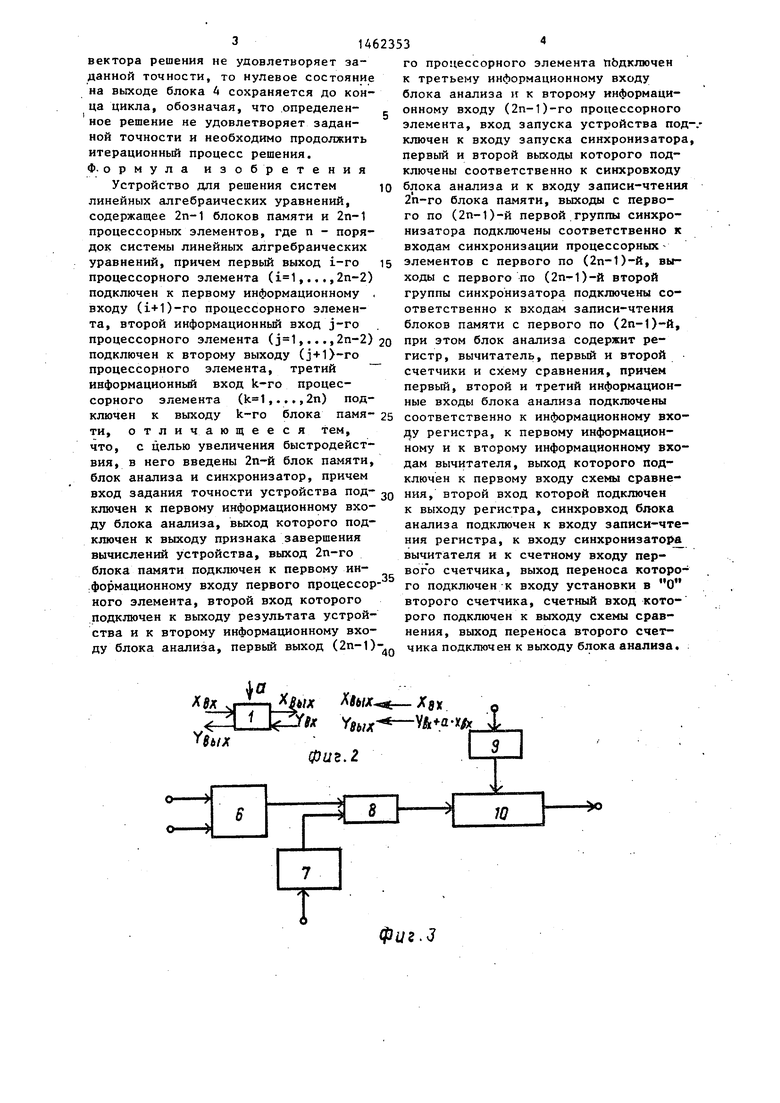

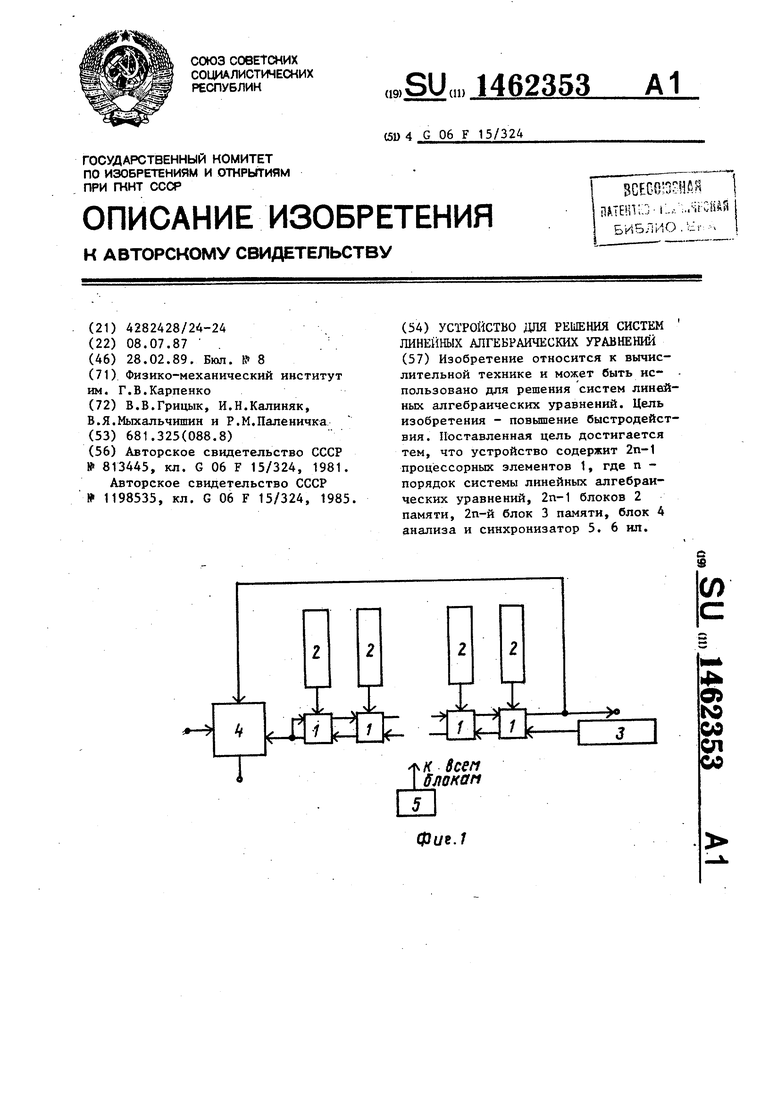

Изобретение относится к вычислительной технике и может быть ис- - пользовано для решения систем линейных алгебраических уравнений. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит 2п-1 процессорных элементов 1, где п - порядок системы линейных алгебраических уравнений, 2п-1 блоков 2 памяти, 2п-й блок 3 памяти, блок 4 анализа и синхронизатор 5. 6 ил.

фие.1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах в качестве спецпроцессора для ре- с шения систем линейных алгебраических уравнений.

Цель изобретения - увеличение быстродействия.

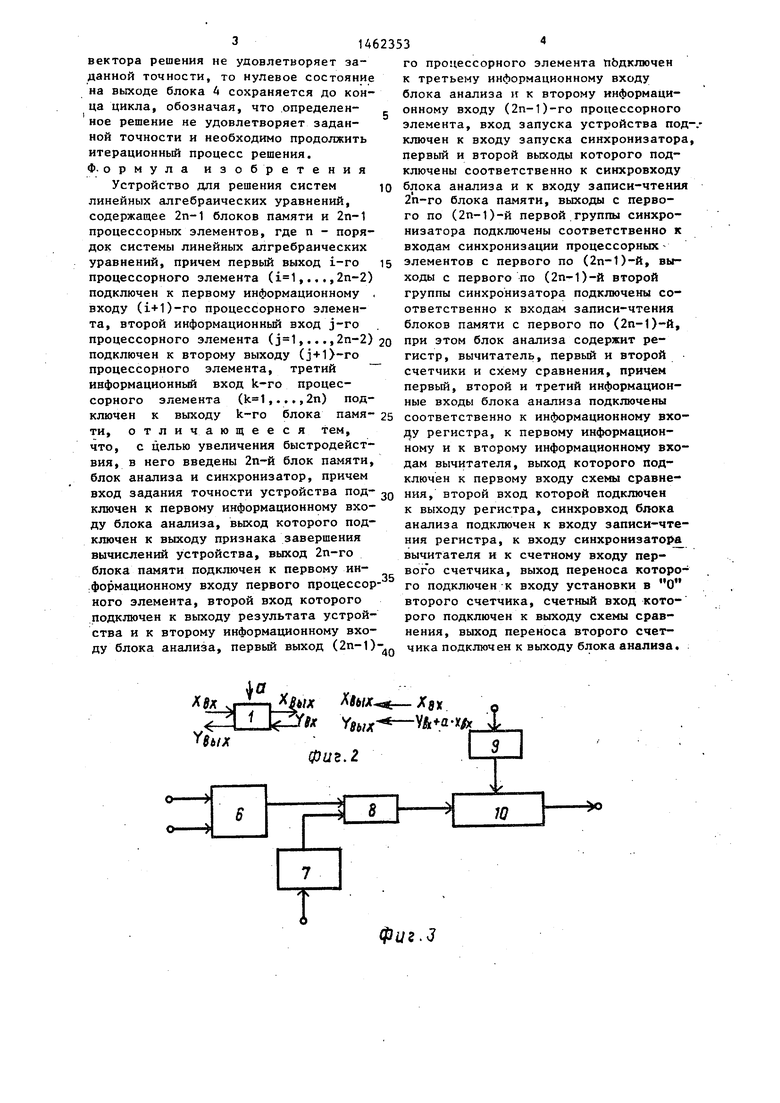

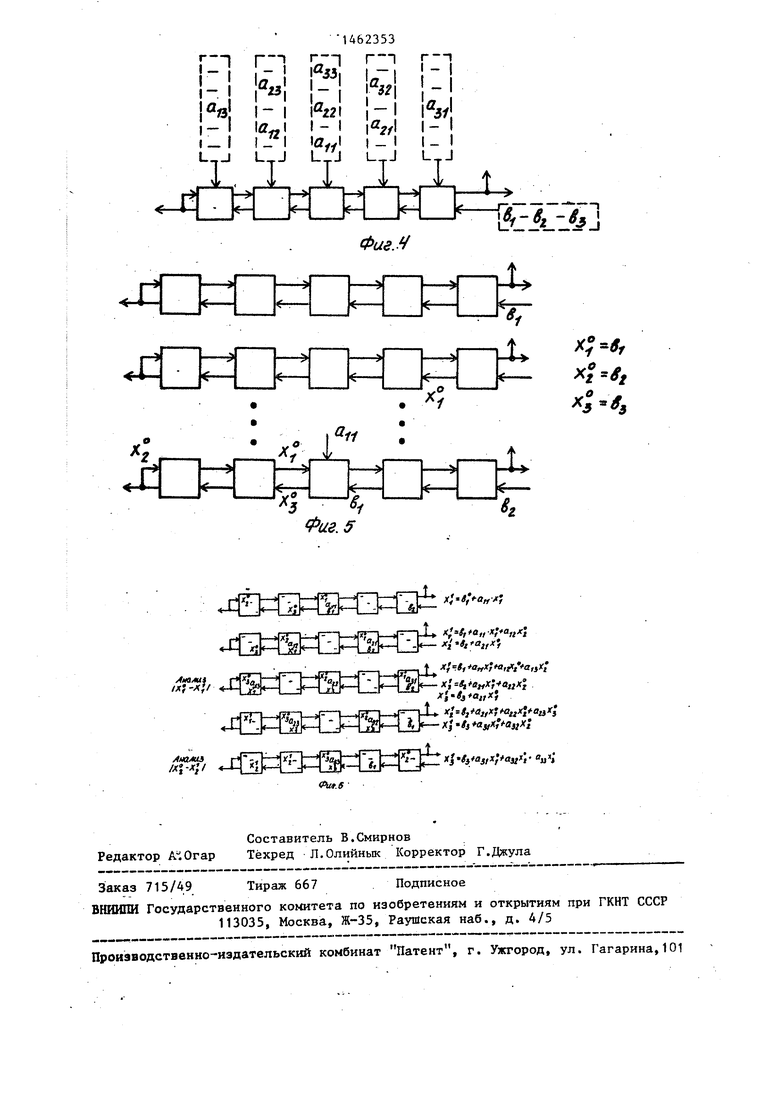

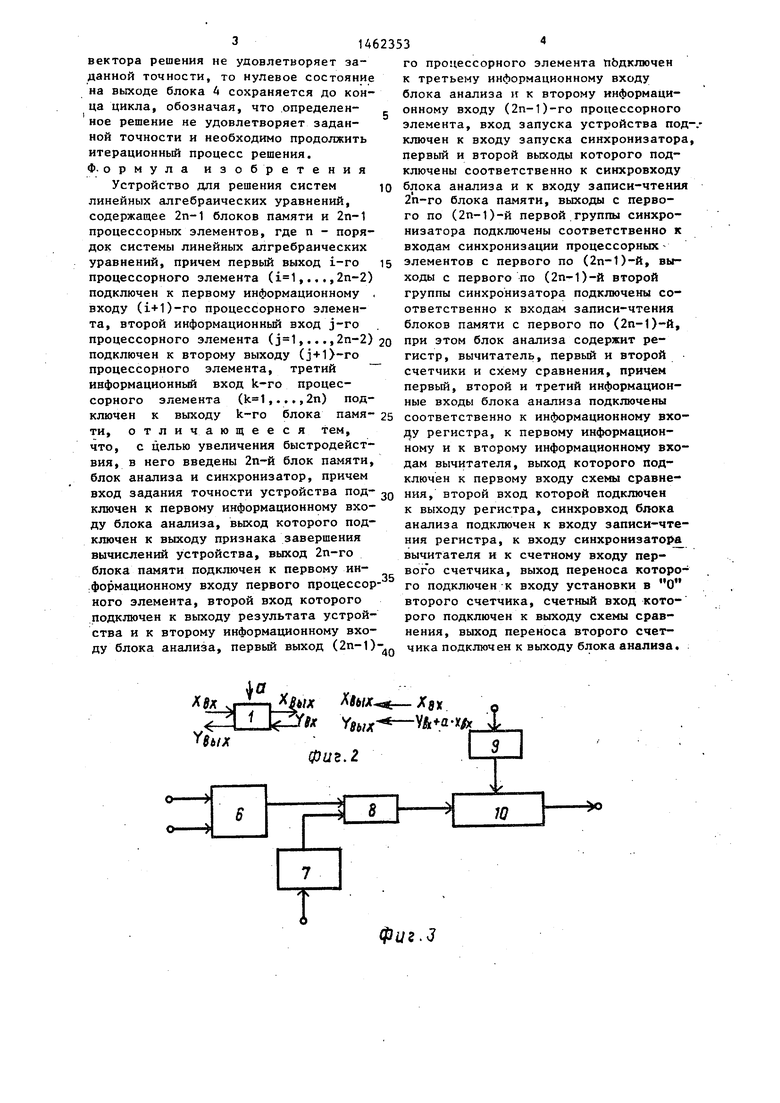

На фиг. 1 представлена схема уст- Ю ройства для решения систем алгебраи- ческих уравнений; на фиг. 2 - функ- циональная схема процессорного эле- мента; на фиг. 3 - схема блока анализа; на фиг. 4 - схема размещения 15 в блоках памяти элементов матрицы коэффициентов и вектора свободных членов размерности 3; на фиг. 5 - схема процесса начальной дагрузки процессорных элементов; на фиг, 6 - .20 схема пяти первых тактов работы уст- ройства при .

Устройство для решения систем алгебраических уравнений содержит 2п-1 процессорных элементов 1, 2п-1 блоков 25 2 памяти,- 2п-й блок 3 памяти, блок 4 анализа и синхронизатор 5. При этом блок 4 анализа состоит из вычитателя 6, регистра 7, схемы 8 сравнения, а также первого 9 и второго 10 счет- 30 чиков.

Устройство реализует итерационный процесс , где А - матри- ца перехода размерности п х п; В - вектор правой части системы урав- нений; к - номер итерации.

Перед процессом решения системы алгребраических уравнений в блоки 2 памяти устройства вводятся коэффициенты матрицы перехода А, а в блок 3 40 памяти записывается заданньй вектор В размерности п. Блоки 2 и 3 памяти :состоят из 2п-1 ячеек памяти каждьм и снабжены схемой циклической пере- записи Информации. При этом коэффч 45 циенты заданного вектора В записываются в соответствующие ячейки с не- четньми номерами блока 3 памяти, а во все ячейки с четными номерами записывается О. Аналогично происхо- 50 дит запись коэффициентов матрицы перехода А в блок 2 памяти. В регистр 7 с информационного входа устройства записывается код числа, задающего точность рещения системы алгебраи- 55 ческих уравнений. Затем происходит начальная загрузка процессорных элементов 1. При пост гплении тактовых импульсов от синхронизатора 5 на

вход считьгоания блока 3 памяти выполняется считьгаание информа-- 1ЩИ, записанной в 2п-1 ячейках памяти, и ее запись в регистры-фиксаторы соответствующих процессорных элементов 1. За начальные значения компонент вектора неизвестных прини мают значения компонент вектора В. В cocfaB блоков 2 памяти входят также схемы блокирования считывания, т.е. схемы установки в О считываемых ; анных при поступлении первых 2п-1 тактовых импульсов начальной загрузки процессорных элементов 1. После 2п-1 тактов начальной загрузки устройство начинает собственно вычисления, решения системы уравнения с точностью, которая задается значением, предварительно записанным в регистре 7.

При поступлении тактовых импульсов от синхронизатора 5 происходит считывание данных из блоков 2 памяти и блока 3 памяти. При этом числа на выходе первой ячейки памяти i-ro блока 2 памяти, где , 2п-1, поступают на информационный вход i-ro процессорного элемента 1, а число на выходе первой ячейки блока 3 памяти поступает на вход (2п-1)-го процессорного элемента 1. В каждом такте работы устройства в процессорном элементе 1 реализуются операции умноже.- ния и сложения согласно схеме на фиг. 2. Каждый процессорный элемент Г состоит из умножителя и сумматора, кроме того, он содержит соответст-i вующие регистры-фиксаторы на выходах процессорного элемента.

Блок 4 анализа предназначен, для покомпонентной проверки точности решения системы алгебраических уравне- ний, и в нем осуществляется покомпо.нентное сравнение текущего вектора решения с предыдущим вектором. В каждом такте работы устройства на выходе вычитателя 6 появляется абсолютное значение разности i-й компоненты вектора решения на k-й итерации X I и i-й компоненты вектора решения на (К+1)-й итерации X , т.е., вычисляется значение ./. Далее осуществляется сравнение этого значения с порогом, задающим точность решения системы уравнения.

Когда в данном цикле решения системы уравнений, который имеет 2п-1 тактов, хотя бы одна из компонент

И У. 8х чг- 1

Z -Lti

q&ye.J

1462353

П ГП Г«-1 г-1 г--}

Фиг.

| Устройство для решения системАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU813445A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-08—Подача