О5

4: 4

05

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1983 |

|

SU1124323A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров цифровой обработки сигналов, в том числе в составе типовых персональных управляющих и бортовых ЭВМ. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что устройство содержит блоки памяти 1, 2, блок 3 постоянной памяти, регистры 4 - 9, коммутаторы 10, 11, сумматор-вычитатель 12, счетчик 13, триггер 14, генератор 15 тактовых импульсов, коммутатор 16, регистр 17. 2 ил.

Фиг.1

Изобретение относится к вычисли- тельной технике и может быть использовано при построении процессоров цифровой обработки сигналов в том числе в составе типовых персональных управляющих и бортовых ЭВМ.

Цель изобретения - повьшение быстродействия.

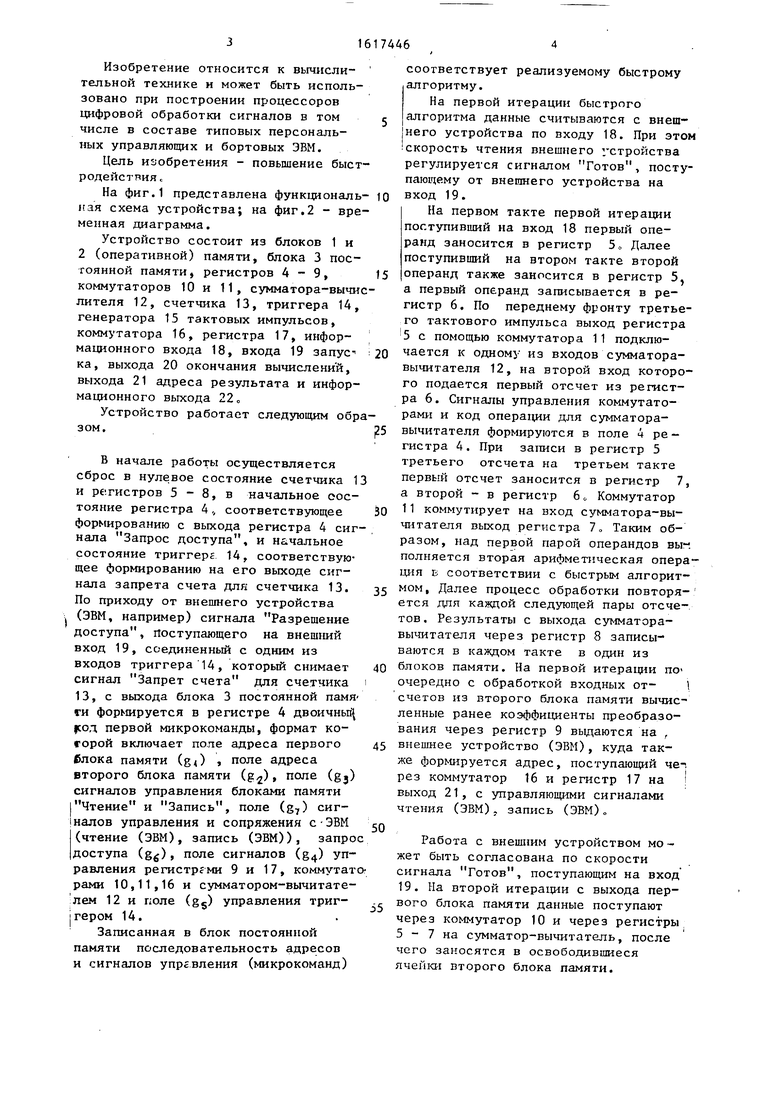

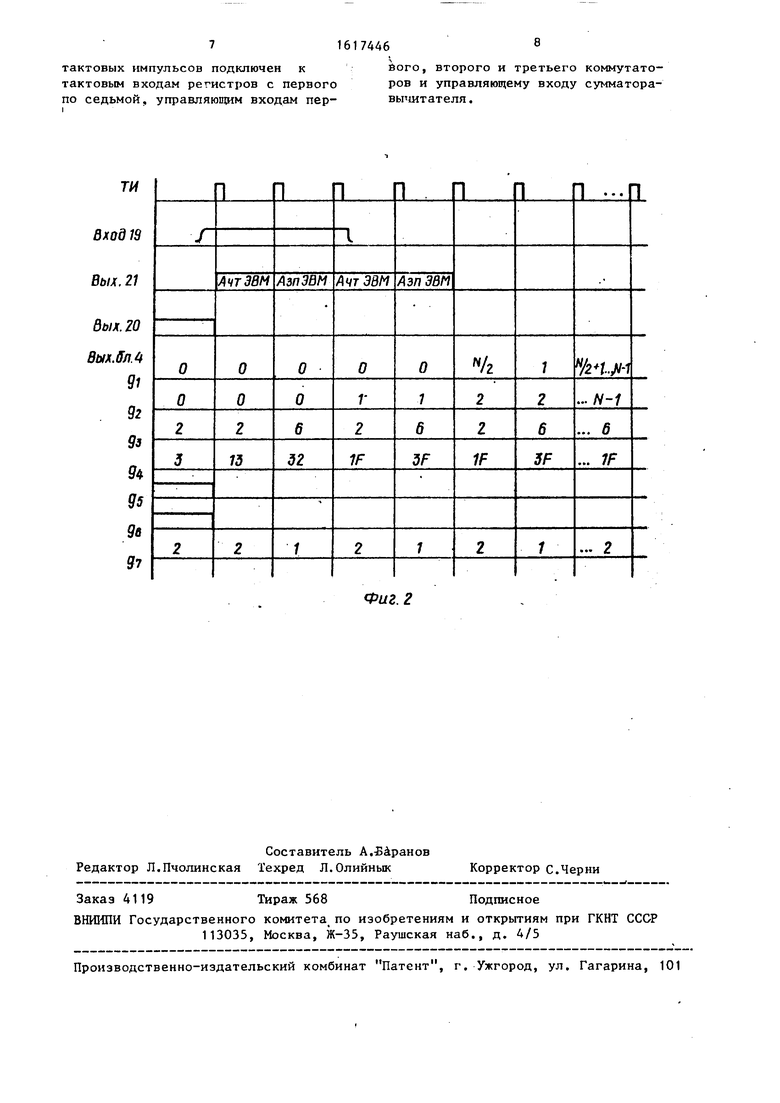

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма.

Устройство состоит из блоков 1 и 2 (оперативной) памяти, блока 3 постоянной памяти регистров 4-9, коммутаторов 10 и 11, сумматора-вычислителя 12, счетчика 13, триггера 14, генератора 15 тактовых импульсов, коммутатора 16, регистра 17, информационного входа 18, входа 19 запус ка, выхода 20 окончания вычислений, выхода 21 адреса результата и информационного выхода 22 о

Устройство работает следующим обра зом.

В начале работы осуществляется сброс в нулевое состояние счетчика 13 и ре.гистров 5 - 8, в начальное состояние регистра 4 ,, соответствующее формированию с выхода регистра 4 сигнала Запрос доступа, и начальное состояние триггере 14, соответствующее формированию на его выходе сигнала запрета счета для счетчика 13. По приходу от внешнего устройства (ЭВМ, например) сигнала Разрешение доступа, поступающего на внешний вход 19, соединенный с одним из входов триггера 14, который снимает сигнал Запрет счета для счетчика 13, с выхода блока 3 постоянной памя- ги формируется в регистре 4 двоичньп |сод первой микрокоманды, формат ко- горой включает поле адреса первого блока памяти (g) , поле адреса второго блока памяти (g) папе (gj) сигналов управления блоками памяти I Чтение и Запись, поле (Q-,) сиг- риалов управления и сопряжения с-ЭВМ (чтение (ЭВМ), запись (ЭВМ)), запрос доступа (gg), поле сигналов (§4) управления регистрами 9 и 17, коммутаторами 10,11,16 и сумматором-вычитате- лем 12 и поле (gg) управления триг- jгерои 14.

Записанная в блок постоянной памяти последовательность адресов и сигналов управления (микрокоманд)

соответствует реализуемому быстрому алгоритму.

На первой итерации быстрого алгоритма данные считываются с внешнего устройства по входу 18. При этом скорость чтения внешнего устройства регулируется сигналом Готов, поступающему от внешнего устройства на to вход 19.

На первом такте первой итерации поступивший на вход 18 первый операнд заносится в регистр 5 о Далее поступивший на втором такте второй t5 операнд также заносится в регистр 5 а первый операнд записывается в регистр 6. По переднему фронту третьего тактового импульса выход регистра 5 с помощью коммутатора 11 подклю- 20 чается к одному из входов сумматора- вычитателя 12, на второй вход которого подается первый отсчет из регистра 6 . Сигналы управления коммутаторами и код операции для сумматора- 25 вычитателя формируются в поле 4 ре - гистра 4. При записи в регистр 5 третьего отсчета на третьем такте первый отсчет заносится в регистр 7, а второй - в регистр 6 Коммутатор 0 11 коммутирует на вход сумматора-вы- читателя выход регистра 7„ Таким образом, над первой парой операндов вы-, полняется вторая арифметическая операция Е соответствии с быстрым алгорит- 5 мом, Далее процесс обработки повторя- ется для каждой следующей пары отсчетов. Результаты с выхода сумматора- вычитателя через регистр 8 записываются в каждом такте в один из 0 блоков памяти. На первой итерации по- очередно с обработкой входных от- 1 счетов из второго блока памяти вычисленные ранее коэффициенты преобразования через регистр 9 выдаются на , 5 внешнее устройство (ЭВМ), куда также форьшруется адрес, поступающий че-. рез коммутатор 16 и регистр 17 на j выход 21, с управляющими сигналами чтения (ЭВМ), запись (ЭВМ)„ 0

Работа с внешним устройством может быть согласована по скорости сигнала Готов, поступающим на вход 19. На второй итерации с выхода пер- вого блока памяти данные поступают через коммутатор 10 и через регистры 5 - 7 на сумматор-вычитатель, после чего заносятся в освободившиеся ячеЙ1ш второго блока памяти.

516

Разрядом gg микрокоманды осуществляется управление триггером 14 так, что с его выхода подается сигнал запрета счета на управляющий вход счетчика 13.

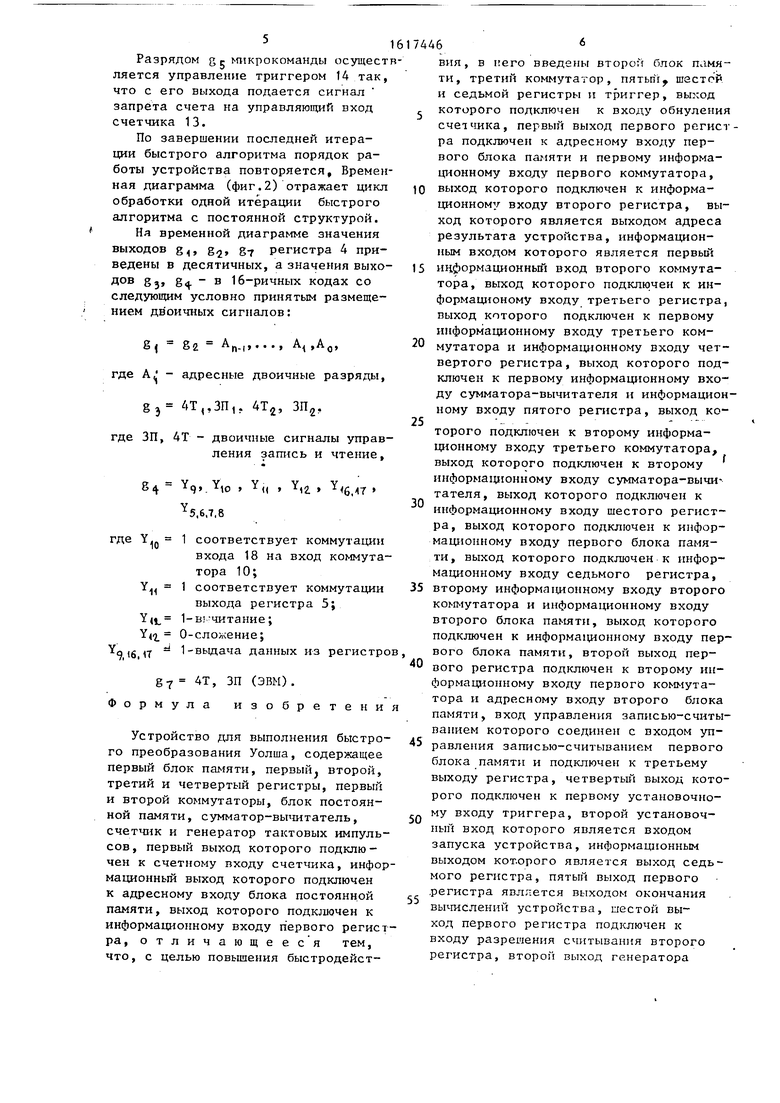

По завершении последней итерации быстрого алгоритма порядок работы устройства повторяется. Временная диаграмма (фиг.2) отражает цикл обработки одной итерации быстрого алгоритма с постоянной структурой. На временной диаграмме значения выходов g, g, g7 регистра 4 приведены в десятичных, а значения выходов gj, 8ц. - в 16-ричных кодах со следующим условно принятым размещением дв оичных сигналов:

ё 82

П-1

. ., А,А

о

где - адресные двоичные разряды, ВЗ 4Т,,ЗП,, 4Т2, ЗП2,

где ЗП, 4Т - двоичные сигналы управления запись и чтение,

64 Y,, , ,2 , , 5,6,7,8

где 1 соответствует коммутации входа 18 на вход коммутатора 10; Y 1 соответствует коммутации

выхода регистра 5; Y4i 1-в -читание; Y.2. 0-сложение; 9, б, IT 1-выдача данных из регистро

g7 4Т, ЗП (ЭВМ). Формула изобретени

Устройство для выполнения быстрого преобразования Уолша, содержащее первый блок памяти, первый, второй, третий и четвертый регистры, первый и второй коммутаторы, блок постоянной памяти, сумматор-вычитатель, счетчик и генератор тактовых импульсов, первый выход которого подключен к счетному входу счетчика, информационный выход которого подключен к адресному входу блока постоянной памяти, выход которого подключен к информационному входу п ервого регистра, отличающееся тем, что, с целью повышения быстродейст0

0

5

74466

ВИЯ, в введены второй блок памяти, третий коммутатор, пятьш щгстой и седьмой регистры и триггер, выход с которого подключен к входу обнуления счетчика, первый выход первого регистра подключен к адресному входу первого блока памяти и первому информационному входу первого коммутатора, 10 выход которого подключен к информационному входу второго регистра, выход которого является выходом адреса результата устройства, информационным входом которого является первьвТ: 5 И11формационньп1 вход второго коммутатора, выход которого подключен к ин- формационому входу третьего регистра, выход которого подключен к первому информационному входу третьего коммутатора и информационному входу четвертого регистра, выход которого подключен к первому информационному входу сумматора-вычитателя и информационному входу пятого регистра, выход которого подключен к второму информационному входу третьего коммутатора, выход которого подключен к второму информащюнному входу сумматора-вычитателя, выход которого подключен к информационному входу шестого регистра, выход которого подключен к информационному входу первого блока памяти, выход которого подключен к информационному входу седьмого регистра, 5 второму информсшщонному входу второго коммутатора и информационному входу второго блока памяти, выход которого подключен к информа1щонному входу первого блока памяти, второй выход первого регистра подключен к второму информационному входу первого коммутатора и адресному входу второго блока памяти, вход управления записью-считыванием которого соединен с входом управления записью-считыванием первого блока памяти и подключен к третьему выходу регистра, четвертый выход которого подключен к первому установочно- Q му входу триггера, второй установочный вход которого является входом запуска устройства, информационным выходом кот.орого является выход седьмого регистра, пятый выход первого .регистра является выходом окончания вы racлeний устройства, шестой выход первого регистра подключен к входу разрешения считывания второго регистра, второй выход генератора

0

5

тактовых импульсов подключен к тактовым входам регистров с первого по седьмой,, управляющим входам перти

Вход 19 0ш. 21

Вых. 20

Вых. Ул. 91

92 9з 9 9S

в

97

його, второго и третьего коммутаторов и управляющему входу сумматора- вычитателя.

Фиг. 2

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1129619A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1983 |

|

SU1141420A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-02—Подача