4 ND СЛ vj

11

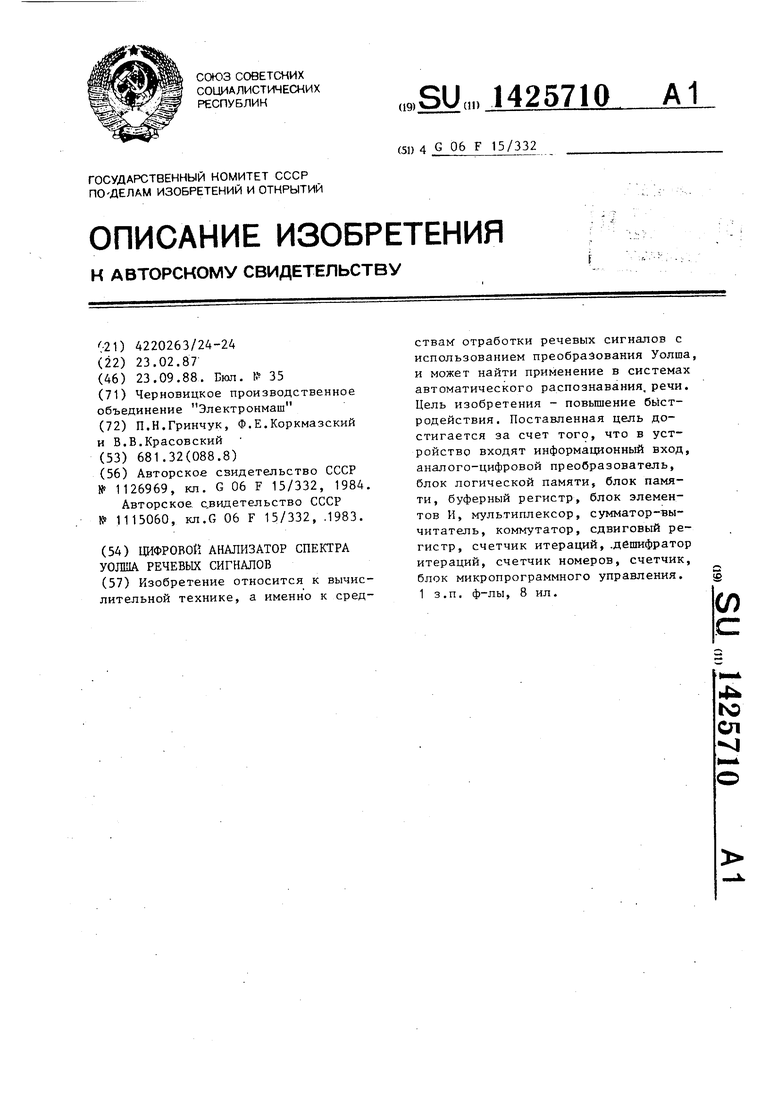

Изобретение относится к вычислительной технике, к средствам обработки речевых сигналов с использованием преобразования Уолша, и может найти применение в системах автоматического распознавания речи.

Целью изобретения является повышение быстродействия.

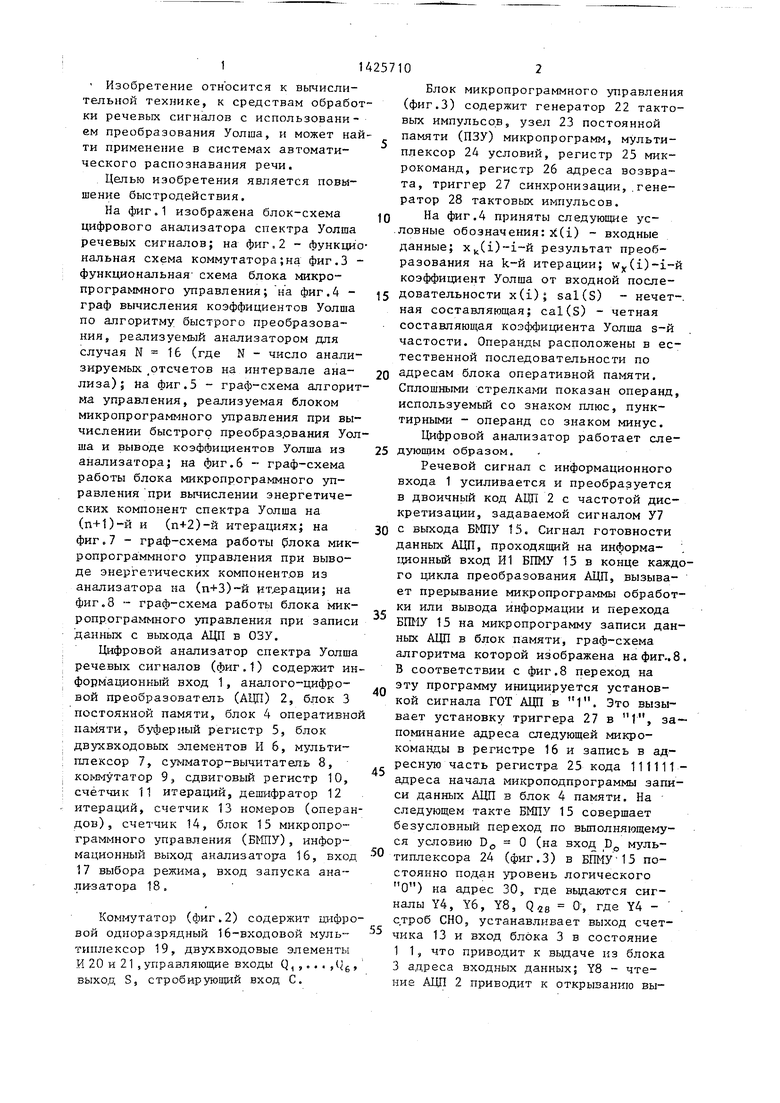

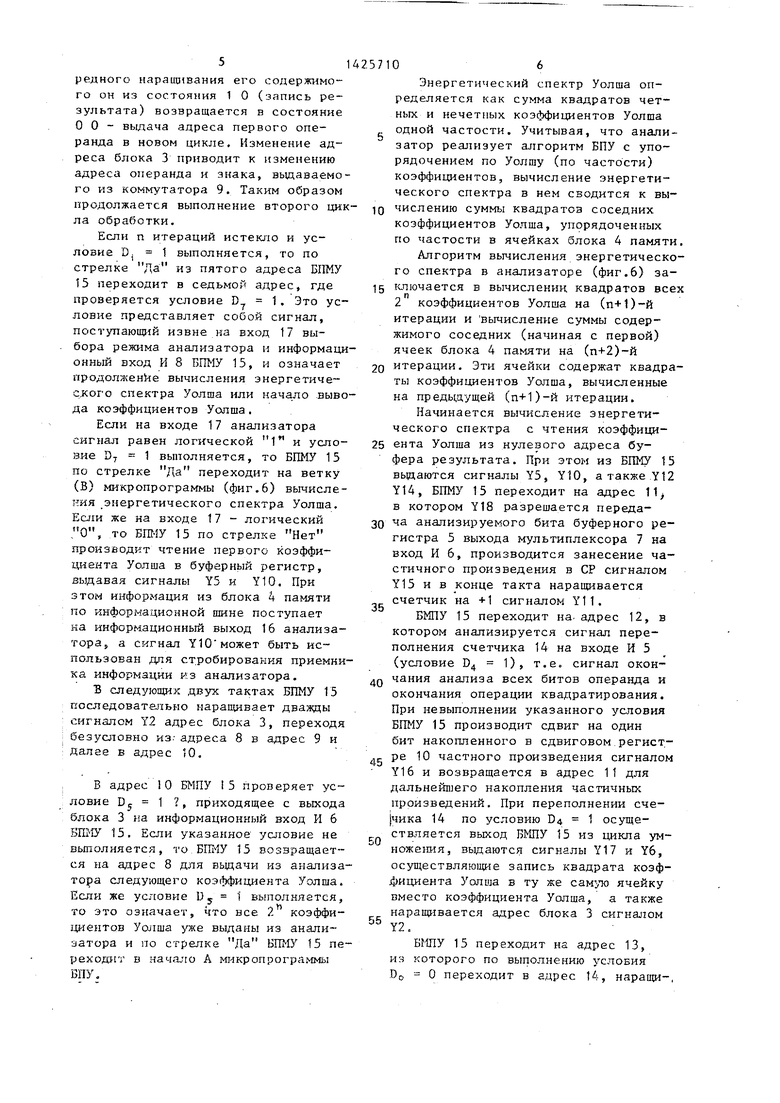

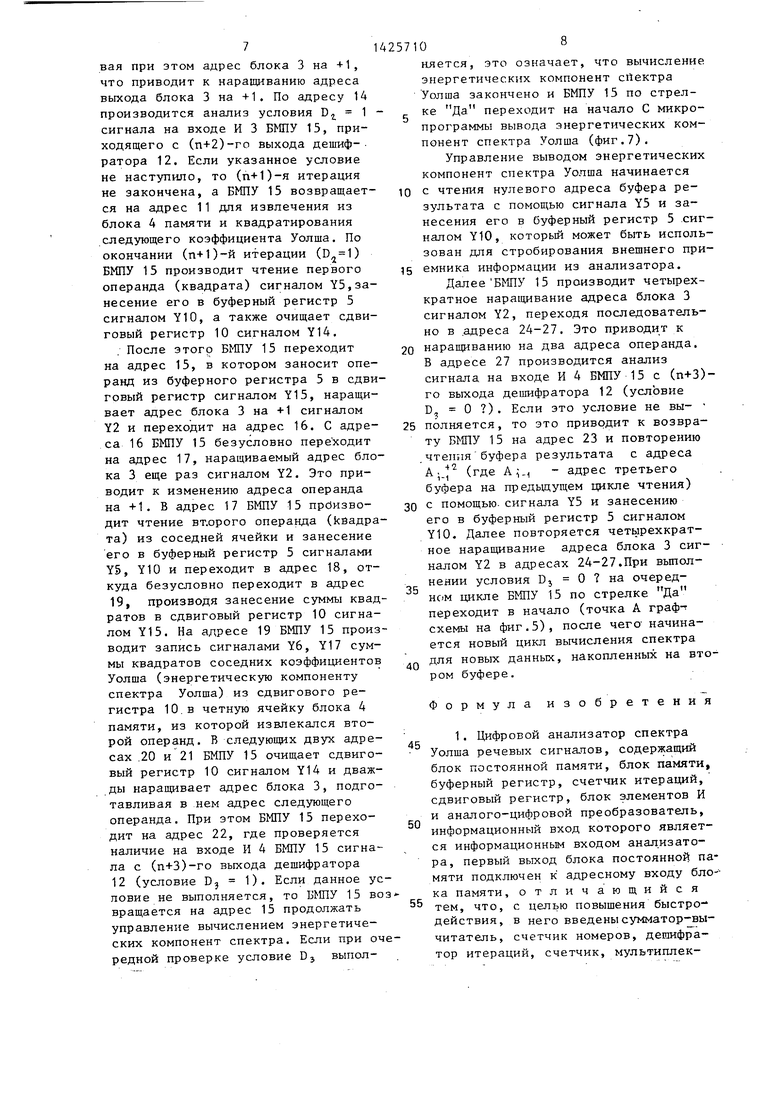

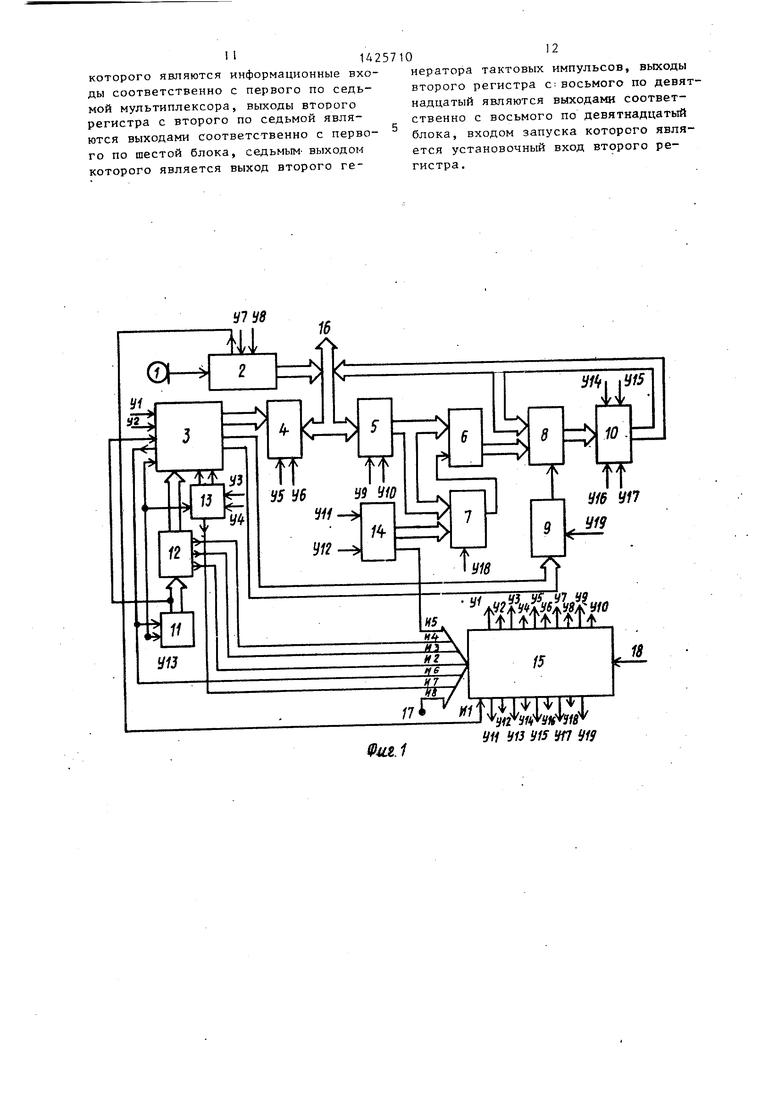

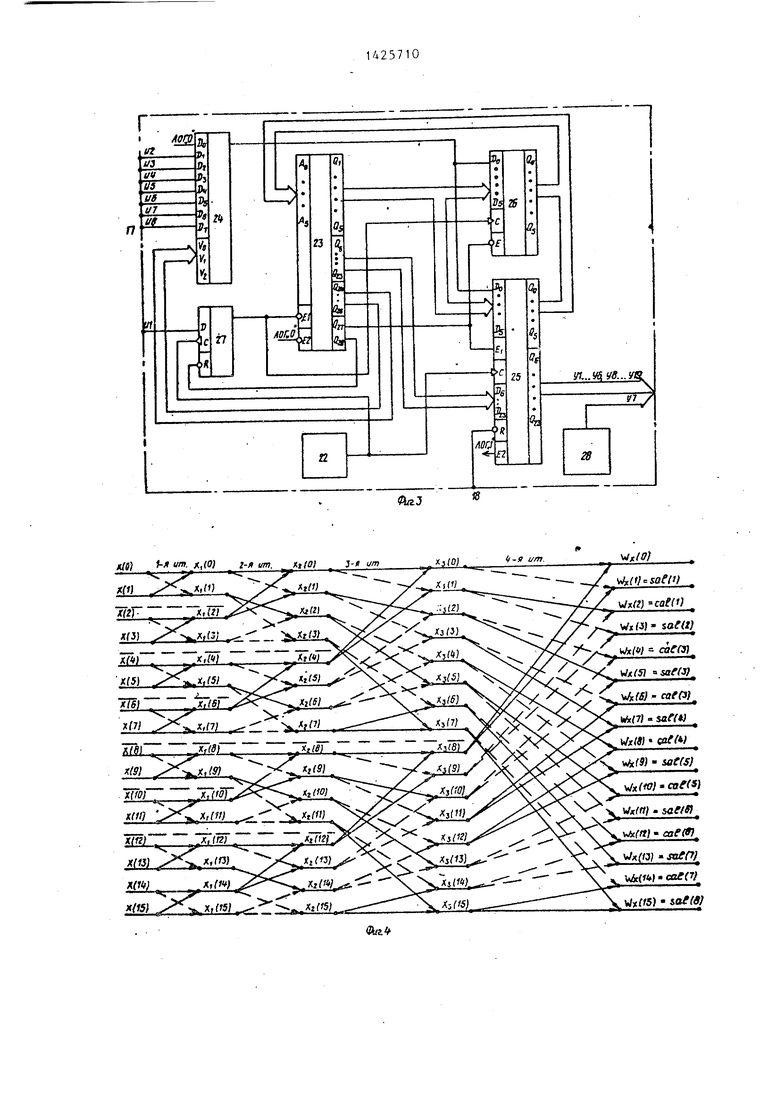

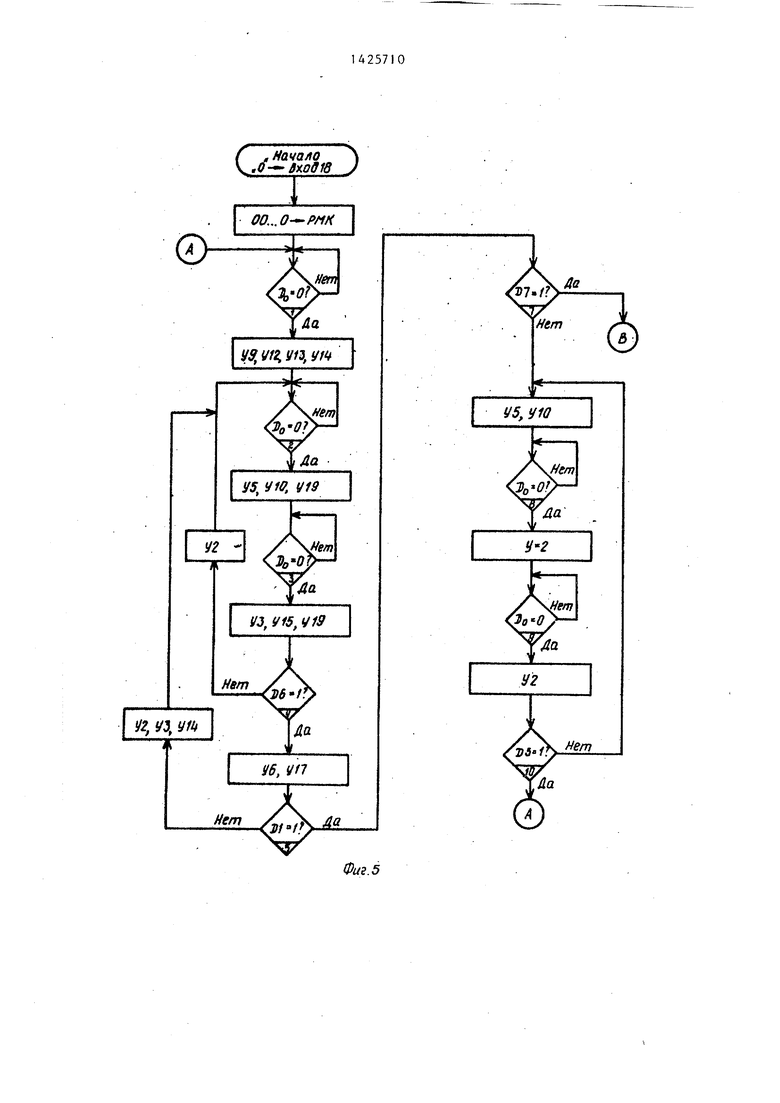

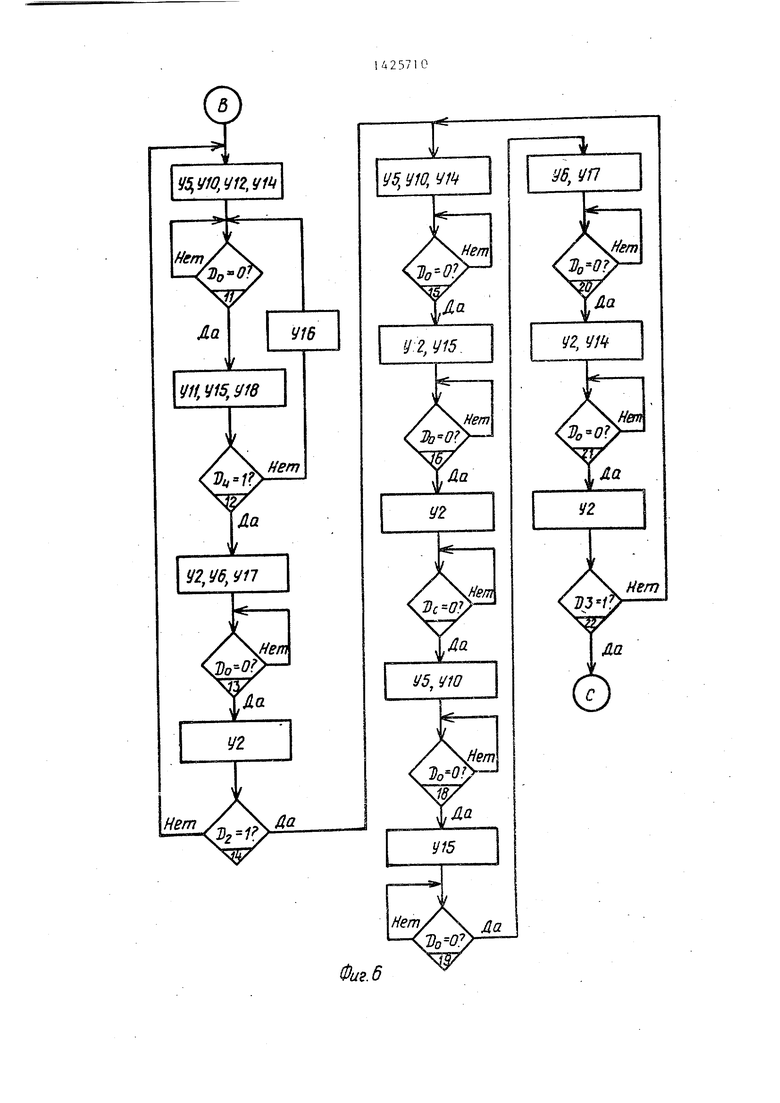

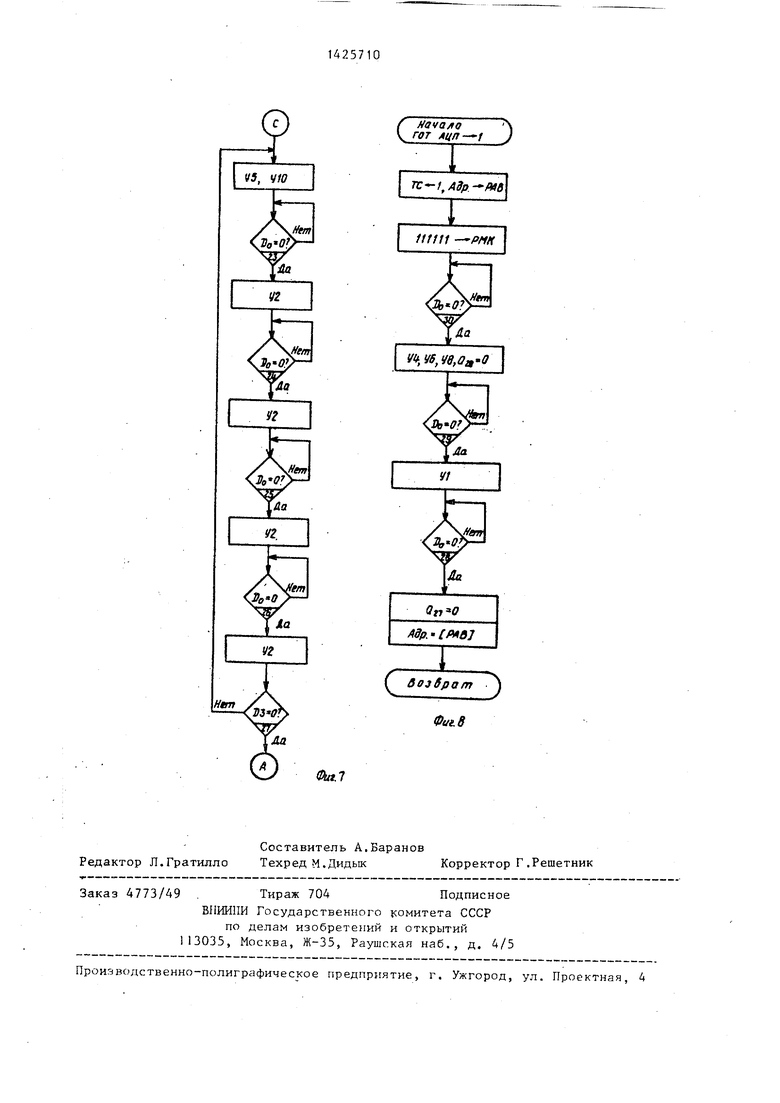

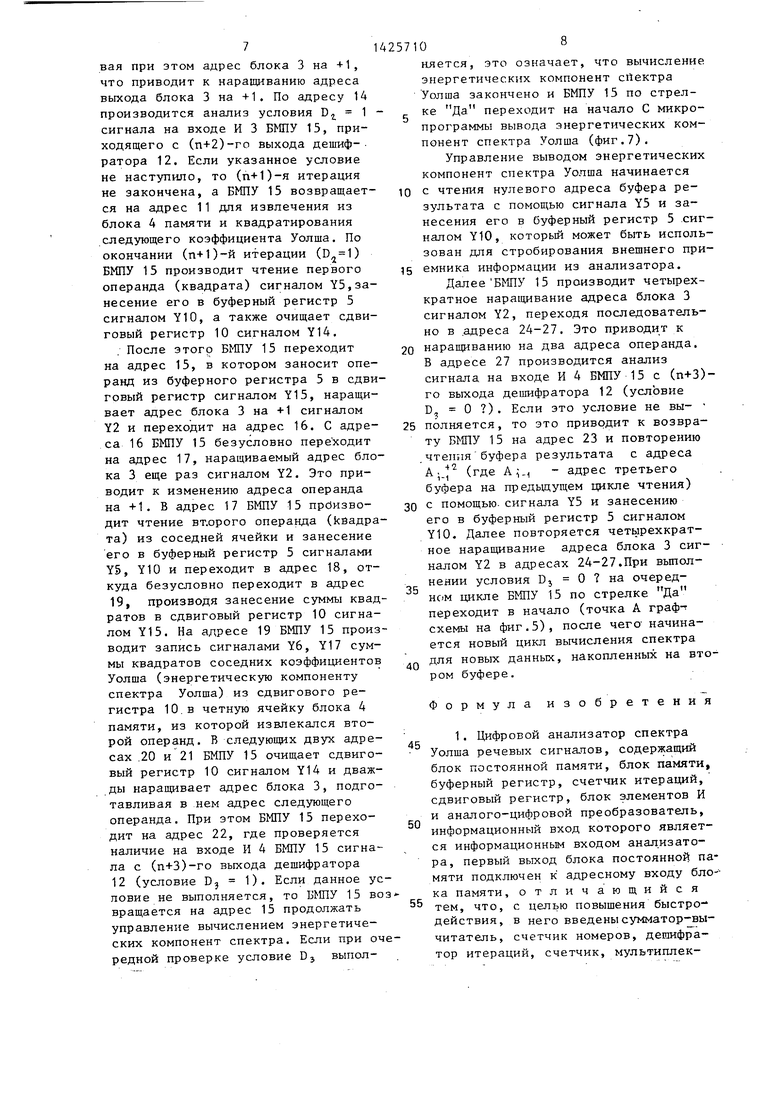

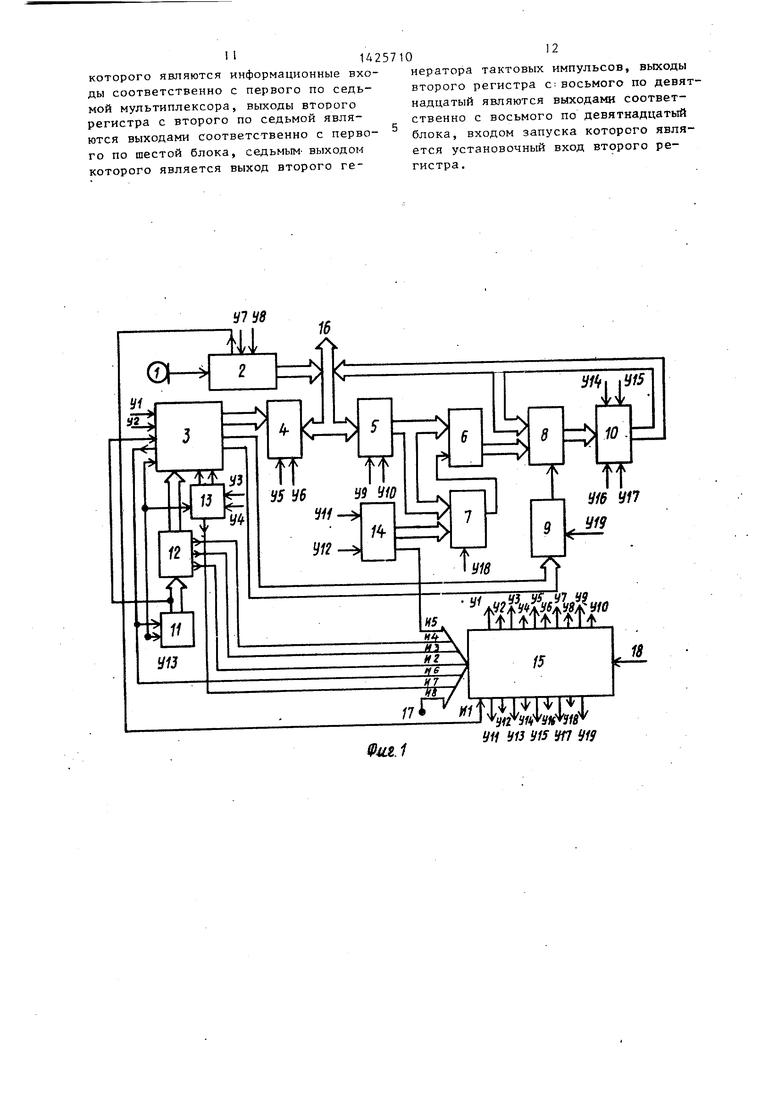

На фиг.1 изображена блок-схема цифрового анализатора спектра Уолша речевых сигналов; на фиг.2 - функциональная схема коммутатора;на фиг.З - функциональная схема блока микропрограммного управления; на фиг.4 - граф вычисления коэффициентов Уолша по алгоритму быстрого преобразования, реализуемый анализатором для случая N 16 (где N - число анализируемых отсчетов на интервале ана- лиза); На фиг.З граф-схема алгоритма управления, реализуемая блоком микропрограмг4ного управления при вычислении быстрого преобразрвания Уолша и выводе коэффициентов Уолша из анализатора; на фиг.6 - граф-схема работы блока микропрограммного управления при вычислении энергетических компонент спектра Уолша на ()-й и (п+2)-й итерациях; на фиг.7 - граф-схема работы 0лока микропрограммного управления при выводе энергетических компонентов из анализатора на (п+3)-й итерации; на фиг.З - граф-схема работы блока микропрограммного управления при записи данных с выхода АЦП в ОЗУ.

Цифровой анализатор спектра Уолша речевых сигналов (фиг.1) содержит информационный вход 1, аналого-цифровой преобразователь (АЦП) 2, блок 3 постоянной памяти, блок 4 оперативно памяти, буферный регистр 5, блок двухвкодовых элементов И 6, мультиплексор 7, сумматор-вычитатель 8, коммутатор 9, сдвиговый регистр 10, счётчик 11 итераций, дешифратор 12 итераций, счетчик 13 номеров (операндов), счетчик 14, блок 15 микропрограммного управления (), информационный выход анализатор а 16, вход 17 выбора режима, вход запуска анализатора 18.

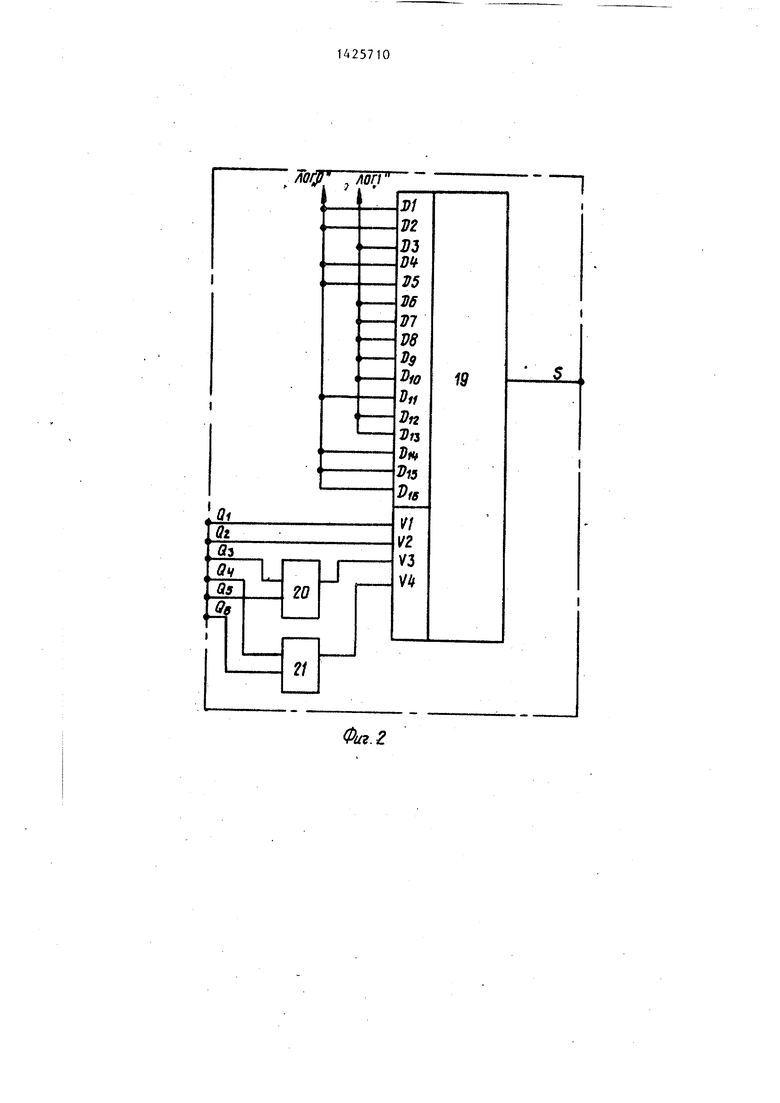

Ком1-1утатор (фиг. 2) содержит цифровой одноразрядный 16-входовой мультиплексор 19, двухвходовые элементы И 20 и 21,управляющие входы Q,,..,46 выход S, стробируюнщй вход С.

7

Q 5 0 5 о

5

0

102

Блок микропрограммного управления (фиг.З) содержит генератор 22 тактовых импульсов, узел 23 постоянной памяти (ПЗУ) микропрограмм, мультиплексор 24 условий, регистр 25 микрокоманд, регистр 26 адреса возврата, триггер 27 синхронизации,.генератор 28 тактовых импульсов.

На фиг.4 приняты следующие условные обозначения: X(i) - входные данные; (1) результат преобразования на k-й итерации; WJf(i)-i-й коэффициент Уолша от входной последовательности x(i); sal(S) - нечет-. ная составляющая; cal(S) - четная составляющая коэффициента Уолша s-й частости. Операнды расположены в естественной последовательности по адресам блока оперативной памяти. Сплошными стрелками показан операнд, используемьш со знаком плюс, пунктирными - операнд со знаком минус.

Цифровой анализатор работает сле- дуюЕЦим образом.

Речевой сигнал с информационного входа 1 усиливается и преобразуется в двоичный код АЦП 2 с частотой дискретизации, задаваемой сигналом У7 с выхода БШУ 15. Сигнал готовности данных АЦП, проходящий на информа- 1ЩОННЫЙ вход И1 БПМУ 15 в конце каждого цикла преобразования АЦП, вызывает прерывание микропрограммы обработки или вывода информации и перехода БПМУ 15 на микропрограмму записи данных АЦП в блок памяти, граф-схема алгоритма которой изображена на фиг.. 8. В соответствии с фиг.8 переход на эту программу инициируется установкой сигнала ГОТ АЦП в 1. Это вызывает установку триггера 27 в 1, запоминание адреса следующей микрокоманды в регистре 16 и запись в адресную часть регистра 25 кода 111111 - адреса начала микроподпрограммы записи данных АЦП в блок 4 памяти. На следующем такте БМПУ 15 совершает безусловный переход по выполняющемуся условию DO О (на вход D мультиплексора 24 (фиг.З) в БПМУ 15 постоянно подан уровень логического О) на адрес 30, где выдалотся сигналы Y4, Y6, Y8, О , где Y4 - . с.троб CHOj устанавливает выход счетчика 13 и вход блока 3 в состояние 1 1, что приводит к вьздаче из блока 3 адреса входных данных; Y8 - чтение АЦП 2 приводит к открыванию

ходного буфера АЦП,передаче цифрового кода речевого отсчета на информационный вход блока 4 памяти и сбросу сигнала ГОТ АЦП в Y6 - запись ОЗУ приводит к запоминанию отсчета АЦП в блоке 4 аамяти по адресу, вьщанному из блока 3; 0 приводит к сбросу триггера 27 в О.

На следующем такте БПМУ 15 север- шает безусловньш переход на адрес 29 (число в нижней части ромба условия) по условию DO 0, где из БПМУ 15 выдается сигнал Y1 , подготавливая новый адрес данных к следую щему циклу записи. По следующему такту БПМУ 15 осуществлят безусловный переход на адрес 28, где выдается сигнал 0 приводящий к выбору регистра 26 в качестве ис- точника адреса следующей микрокоманды. Так как в регистре 26 запомнен адрес в момент прерьшания микропрограммы обработки, то в следующем такте произойдут возврат к прерванной микропрограмме и продолжение ее выполнения .

Работа анализатора при выполнении быстрого преобразования Уолша происходит в соответствии с алгоритмом, изображенным на фиг.5. Переход на начало микропрограммы происходит при подаче извне на вход 18 блока 15 анализатора сигнала О. При этом в адресную часть регистра 25 записывается адрес 000000. В следующем такте рсуществляется безусловный переход на адрес 1, в котором из БПМУ 15 выдаются сигналы Y9, Y12, Y13, Y 14,

т.е. осуществляется начальная уста

новка узлов анализатора.

В следующем такте при условии БПМУ 15 переходит на адрес 2, в котором из БПМУ 15.вьщаются сигналы Y5, Y10, Y19-. При этом осуществляется чтение первого операнда из блока 4 памяти в буферный регистр 5 с адреса, задаваемого блоком 3. Сигнал Y19 разрешает выдачу знака из коммутатора 9 на вход сумматора-вычитателя.

В следующем такте БПМУ 15 осущест- вляется переход на адрес 3, где сигналом Y15 производится занесение первого операнда из буферного регистра .5 чгерез блок элементов И 6 и сумматор-вычитат ель В в сдвиговый регистр 10 со знаком, выдаваемым по Y19 из коммутатора 9 на вход сумматора-вычитателя 8. Кроме того, по окончании

д 5 0 5

Q

0

5

10

такта, по сигналу Y3 происходит наращивание счетчика 13 номеров на -«-1 с целью вьдачи на адресный выход блока 3 адреса второго операнда, В данном такте работы БПМУ 15 проверяется выполнение условия D 1. Этот сигнал выхода счетчика 13 номеров равен коду 10, что вызывает вьщачу из блока

3адреса результата. Если это условие не выполняется (выход Нет ромба условия Dg, 1), то БПМУ 15 вы- дает сигнал Y2 и возвращается на ад;- рес 2.

Так как в счетчике 13 номеров - 01 после выдачи сигнала Y3, то из блока 3 на адресный вход блока 4 поступает адрес второго операнда. В адресе 2 снова производится чтение операнда (уже второго) из блока 4 памяти в буферный регистр 5 сигнала- .ми Y5-и Y10. Второй операнд из буферного регистра 5 через блок элементов И 6 подается на вход сумматора-вычитателя 8, на другой вход которого из сдвигового регистра 10 передается первый операнд. Знак операции при этом определяется знаком из коммутатора 9, вьщаваемым по Y19.

В следующем такте результат операции фиксируется в сдиговом регистре 10 сигналом Y15 и наращивается сигналом Y3 счетчик 13 номеров до состояния 1 0. Поэтому при проверке условия Dp 1 на этот раз БПМУ 15 переходит по стрелке Да на адрес

4и производит запись в блок 4 памя- ти результата операции, выдавая сигналы Y17 - вьщача информации из сдвигового регистра 10, и Y6 - запись в блок А памяти. При этом из блока 3 выдается адрес результата.

В следующем такте БПМУ 15 переходит на адрес 5, в котором проверяется выполнение условия D 1, оз- начаюшего окончание итераций БПМУ 15 и переход на (п+1)-ю итерацию. Сигнал данного условия поступает с (п+1)-го выхода дешифратора итераций на информационный вход И2 БПМУ 15. Если это условие не выполняется (п итераций БПУ еще не истекло), то по стрелке Нет БПУ производит очередное нараш вание адреса блока 3 и счетчика 13 номеров сигналами Y2 и Y3, очищает сдвиговый регистр 12 сигналом Y14 и возвращается на- адрес 2. Так как счетчик 13 номеров - счетчик по модулю 3, то после очередного наращивания его содержимого он из состояния 1 О (запись результата) возвращается в состояние О О - выдача адреса первого операнда в новом цикле. Изменение адреса блока 3 приводит к изменению адреса операнда и знака, выдаваемого из коммутатора 9. Таким образом продолжается выполнение второго цик ла обработки.

Если п итераций истекло и условие D; 1 выполняется, то по стрелке Да из пятого адреса БПМУ 15 переходит в седьмой адрес, где проверяется условие D 1. Это условие представляет собой сигнал, поступающий извне на вход 17 выбора режима анализатора и информационный вход И 8 БПМУ 15, и означает продолжение вычисления энергетического спектра Уолша или начало .выво да коэффициентов Уолша.

Если на входе 17 анализатора сигнал равен логической 1 и условие D 1 выполняется, то БПМУ 15 по стрелке Да переходит на ветку (В) микропрограммы (фиг.6) вычисления энергетического спектра Уолша. Если же на входе 17 - логический О, то БШ-1У 15 по стрелке Нет производит чтение первого коэффициента Уолша в буферный регистр, вьэдавая сигналы Y5 и Y10. При зтом информация из блока 4 памяти по информационной шине поступает ка информационный выход 16 анализа- Topaj а сигнал Y10 может быть использован для стробировакия приемки 7 са информации кз анализатора.

В следующих двух тактах БПМУ 15 последовательно нараащвает дважды сигналом Y2 адрес блока 3, переходя безусловно из: адреса 8 в адрес 9 и даттее в адрес 10.

В адрес 10 БМПУ 15 проверяет условие Dy 1 , приходящее с выхода блока 3 на информационный вход И 6 ВПШ 15. Если указанное условие не вьтолняется, то.БПМУ 15 возвращается на адрес 8 для вьщачи из анализатора следу ощего коэффициента Уолша. Если же условие выполняется, то это означает, что все 2 коэффи- хщентов Уолша уже выданы из анализатора и по стрелке Да БПМУ 15 переходит в начало А микропрограммы БПУ,

257106

Энергетический спектр Уолша определяется как сумма квадратов четных и нечетных козффициентов Уолша одной частости. Учитывая, что анализатор реализует алгоритм БПУ с упорядочением по Уолшу (по частости) коэффициентов, вычисление энергетического спектра в нем сводится к вы- 1Q числению суммы квадратов соседних коэффициентов Уолша, упорядоченных по частости в ячейках блока 4 памяти.

Алгоритм вычисления энергетического спектра в анализаторе (фиг.6) за5

0

5

0

5

0

5

0

5

к-пючается в вычислении квадратов всех 2 коэффициентов Уолша на (п+1)-й итерации и вычисление суммы содержимого соседних (начиная с первой) ячеек блока 4 памяти на (п+2)--й итерации. Эти ячейки содержат квадраты коэффициентов Уолша, вычисленные на предьщущей (п+1)-й итерации.

Начинается вычисление энергетического спектра с чтения коэффициента Уолша из нулевого адреса буфера результата. При этом из БПМУ 15 вьдаются сигналы Y5, Y10, а также Y12 Y14, БПМУ 15 переходит на адрес 11 в котором Y18 разрешается передача анализируемого бита буферного регистра 5 выхода мультиплексора 7 на вход И 6, производится занесение частичного произведения в СР сигналом Y15 и в конце такта наращивается счетчик на сигналом Y11.

БМПУ 15 переходит на. адрес 12, в котором анализируется сигнал переполнения счетчика 14 на входе И 5 (условие D 1), т.е. сигнал окончания анализа всех битов операнда и окончания операции квадратирования. При невыполнении указанного условия БПМУ 15 производит сдвиг на один бит накопленного в сдвиговом.регистре 10 частного произведения сигналом Y16 и возвращается в адрес 11 для дальнейшего накопления частичных произведений. При переполнении сче- |чика 14 по условию D4 1 осуществляется выход БМПУ 15 из цикла умножения, вьщаются сигналы Y17 и Y6, осуп;ествляющие запись квадрата коэффициента Уолша в ту же ячейку вместо коэффициента Уолша, а также наращивается адрес блока 3 сигналом Y2.

БШУ 15 переходит на адрес 13, из которого по выполнению условия DO - О переходит в адрес 14, наращи-,

7

вая при этом адрес блока 3 на +1, что приводит к наращиванию адреса выхода блока 3 на +1, По адресу 14 производится анализ условия D, 1 сигнала на входе И 3 БМПУ 15, приходящего с (п+2)-го выхода дешиф- ратора 12. Если указанное условие не наступило, то (п+1)-я итерация не закончена, а БШУ 15 возвращает- ся на адрес 11 для извлечения из блока 4 памяти и квадратирования следующего коэффициента Уолша. По окончании (п+1)-й итерации (D 1) БМПУ 15 производит чтение первого операнда (квадрата) сигналом Y5,занесение его в буферный регистр 5 сигналом Y10, а также очищает сдвиговый регистр 10 сигналом Y14,

. После этого БМПУ 15 переходит на адрес 15, в котором заносит операнд из буферного регистра 5 в сдвиговый регистр сигналом Y15, наращивает адрес блока 3 на +1 сигналом Y2 и переходит на адрес 16. С адре- са 16 БМПУ 15 безусловно переходит на адрес 17, наращиваемый адрес блока 3 еще раз сигналом Y2. Это приводит к изменению адреса операнда на +1. В адрес 17 БМПУ 15 прОизво- дит чтение вт.орого операнда (kвaдpa та) из соседней ячейки и занесение его в буферный регистр 5 сигналами Y5, Y10 и переходит в адрес 18, откуда безусловно переходит в адрес 19, производя занесение суммы квадратов в сдвиговый регистр 10 сигналом Y15. На адресе 19 БШУ 15 производит запись сигналами Y6, Y17 суммы квадратов соседних коэффициентов Уолша (энергетическую компоненту спектра Уолша) из сдвигового регистра 10.в четную ячейку блока 4 памяти, из которой извлекался второй операнд. В следующих двух адресах .20 и 21 БМПУ 15 очищает сдвиговый регистр 10 сигналом Y14 и дважды наращивает адрес блока 3, подготавливая в нем адрес следующего операнда. При этом БМПУ 15 переходит на адрес 22, где проверяется наличие на входе И 4 БМПУ 15 сигнала с (п+3)-го выхода дешифратора 12 (условие Dj 1). Если данное условие не выполняется, то БМПУ 15 во вращается на адрес 15 продолжать управление вычислением энергетических компонент спектра. Если при очредной проверке условие Вз выпол

5

0 5 о

5

0

5

0

5

10

няется, это означает, что вычисление энергетических компонент сйектра Уолша закончено и БМПУ 15 по стрелке Да переходит на начало С микропрограммы вывода энергетических компонент спектра Уолша (фиг.7).

Управление выводом энергетических компонент спектра Уолша начинается с чтения нулевого адреса буфера результата с помощью сигнала Y5 и занесения его в буферный регистр 5 сигналом Y10, который может быть использован для стробирования внешнего приемника информации из анализатора.

Далее БМПУ 15 производит четырехкратное наращивание адреса блока 3 сигналом Y2, переходя последовательно в .адреса 24-27. Это приводит к нарацщванию на два адреса операнда. В адресе 27 производится анализ сигнала на входе И 4 БМПУ 15 с (п+3)- го выхода дешифратора 12 (условие D, 0 ). Если это условие не вы- полняется, то это приводит к возврату БМПУ 15 на адрес 23 и повторению чтения буфера результата с адреса (где А, - адрес третьего буфера на предыдущем цикле чтения) с помощью, сигнала Y5 и занесению его в буферный регистр 5 сигналом Y10. Далее повторяется четырехкратное наращивание адреса блока 3 сигналом Y2 в адресах 24-27.При выполнении условия DJ О на очередном цикле БМПУ 15 по стрелке Да переходит в начало (точка А граф- схемы на фиг.5), после чего- начинается новый цикл вычисления спектра для новых данных, накопленных на втором буфере.

Формула изобретения

1. Цифровой анализатор спектра Уолша речевых сигналов, содержащий блок постоянной памяти, блок памяти, буферный регистр, счетчик итераций, сдвиговый регистр, блок элементов И и аналого-цифровой преобразователь, информационный вход которого является информационным входом анал.изато- ра, первый выход блока постоянной памяти подключен к адресному входу бло-- ка памяти, отличающийся тем, что, с целью повышения быстро- действия, в него введенысумматор-вы- читатель, счетчик номеров, дешифратор итераций, счетчик, мультиплек

91

сор, блок микропрограммного управления и коммутатор, выход которого подключен к управляющему входу сумматора вычитателя, выход которого подключен к информационному входу сдвигового регистра, выход которого соединен с информационным выходом аналого-цифрового преобразовате и подключен к входу первого операнда сумматора-вычитателя, информационным входам блока памяти и буфер- ного регистра, выход которого подключен к первому входу блока элементов И и первому информационному входу мультиплексора, выход, которого подключен к второму входу блска элементов И, выход которого подключен к входу второго операнда сумматора-вычитателя, выход блока памяти подключен к информационному входу б.уфериого регистра и является ин- 1:)ор.мационным выходом анализатора,информационный выход счетчика итераци подключен к входу дешифратора итераций, выход которого подютючен к первому адресному входу блока постоянной памяти, второй выход которого подключен к информационыог-су входу коммутатора,.выход переноса счетчика итераций подключен к второму адресиомз входу блока постоянной памяти, третий адресный вход которого под1С1шчен к информационному выходу счетчика номеров, выход счетчика подключен к второму, информационному входу мультиплексора, выводы блока микропрограммного управления с первого по двенадцатый подключены соответственно к четвертому и пятому адресным входам блока постоянной памяти, счетному входу и входу разрешения выдачи счетчика номеров,- входам управления чте1шем и записью блока памяти, входу запуска преобра зования и входу чтения аналого-цифрового преобразователя5 входу обнуления и тактовому входу буферного .регистра, счетному входу и входу обнупенил счйтчика, тринадцатый выход блока микропрограммного управления подключен к входу обнуления счетчика итераций и счетчика номеров и шестому адресному входу блока постоянной памяти , выходы блока мик ponporpatiMHoro управления с четьгрнад цатого по девятнадцатый подюггачены соответственно к входу обнуления, входу разрешения записи,, тактовому

0

5

0

5

71

0

5

0

5

0

5

О О

входу и входу разрешения чтения сдвигового регистра, управляющим входам мультиплексора и коммутатора, выход окончания преобразования аналого-цифрового преобразователя подключен к первому входу условий блока микропрограммного управления,второй, третий и четвертый входы условий которого подключены соответственно к второму,третьему и четвертому выходам дешифратора итераций, выход переноса счетчика подключен к пятому входу условий блока микропрограммного управления, шестой вход условий которого соединен с счетным входом счетчика итераций и подключен к третьему выходу блока постоянной памяти, выход переноса счетчика номеров подключен -к седьмому входу условий блока микропрограммного управления,восьмой вход условий и вход запуска которого являются соответственно входом выбора режима и входом запуска анализатора.

2. Анализатор по пИ, о т л и - чающий с. я тем, что блок микропрограммного управления содержит мультиплексор, триггер, первый и второй регистры, первый и второй генераторы тактовых импульсов и узел постоянной памяти, первый выход которого подключен к информационному входу первого регистра и первому информационному входу второго регистра, входы разрешения считывания которых подключны к второму выходу узла постоянной памяти, третий и чет-, вертый выходы которого подключены соответственно к второму информационному входу второго регистра и управляющему входу мультиплексора, вы-. ход которого подключен к входам младших разрядов .первого и второго регистров, пятьш выход узла постоянной памяти подключен к установочному входу триггера, выход которого соединен с входом разрешения чтения узла постоянной памяти и тактовьм входом первого регистра, выход которого соединен с первым выходом второго регистра и подгатючен к адресному входу узла постоянной памяти, выход первого генератора тактовых импульсов подключен к тактовому входу второго регистра и тактовому входу триггера, инф.ормационный вход которого является первым информационным входом блока, входами условий с второго по восьмой

которого являются информационные входы соответственно с первого по седьмой мультиплексора, выходы второго регистра с второго по седьмой являются выходами соответственно с первого по шестой блока, седьмым- выходом которого является выход второго генератора тактовых импульсов, выходы второго регистра с: восьмого по девятнадцатый являются выходами соответственно с восьмого по дeвятнaдцaтьrtl блока, входом запуска которого является установочный вход второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Синтаксический анализатор | 1987 |

|

SU1439594A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

Изобретение относится к вычислительной технике, а именно к средствам отработки речевых сигналов с использованием преобразования Уолша, и может найти применение в системах автоматического распознавания, речи. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в устройство входят информационный вход, аналого-цифровой преобразователь, блок логической памяти, блок памяти, буферный регистр, блок элементов И, мультиплексор, сумматор-вы- читатель, коммутатор, сдвиговый регистр, счетчик итераций, .дешифратор итераций, счетчик номеров, счетчик, блок микропрограммного управления. 1 3.п. ф-лы, 8 ил. (Л

У7У8

3

/5

18

/7

41 у

fV

1

. 1

УН У13 У15 W7 i19

0ta.Z

1-я ит. n,tO) г-я ит.

f-tIO)

Йл

«

3-11 (jm

) .

ii-e um.

JxlOl

(i saein cafU) Witffl sofW yN.,/xffl - caffyj Wxffl saf{3f (8 - cgfffl - Wx/« caf Aj (9) saefS} (( Jx(ft). 3cnf} Jx(it} - caeffJ

x(t3) - jcfjT;

VA(T( oaf fT/ Wxr«) «o/W

С, Начало) ,.oSl8 J

L

. 00...

До

Htm

У5, yW

Нет

М7

йа

У 2

У2

Нет

У5,ЩУ12.У1

Фиг. 6

У 6, У Л

йа

tt, У15.

У 2, У14

Ла

У2

У2

Ла

У 5, У10

Him

иЗ ОТ

(НачалоЛ гот Aun- i J

/La

Адр. fAtOJ

i

( Offjffflam j Фае. 8

| Цифровой анализатор спектра речевого сигнала | 1982 |

|

SU1126969A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-23—Подача