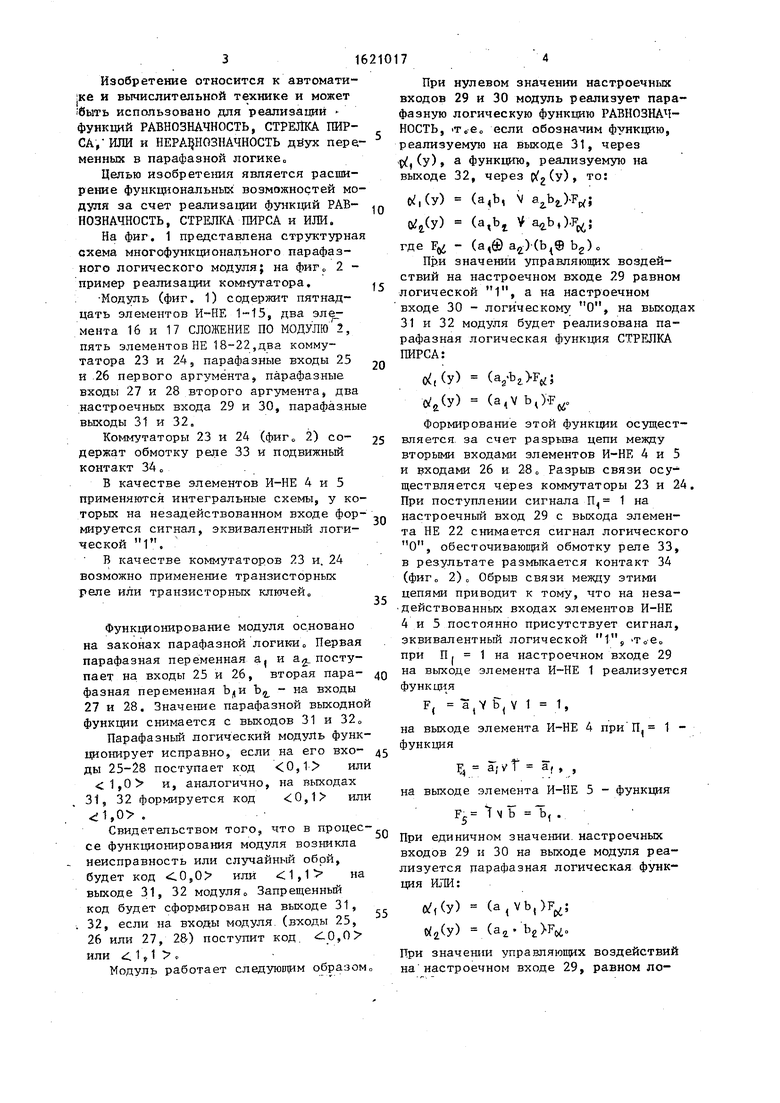

Фиг.1

Изобретение относится к автомати- |ке и вычислительной технике и может быть использовано для реализации - функций РАВНОЗНАЧНОСТЬ, СТРЕЛКА ПИРСА , ИЛИ и НЕРАВНОЗНАЧНОСТЬ дйух пере,- менных в парафазией логике.

Целью изобретения является расширение функциональных возможностей модуля за счет реализации функций РАВ- НОЗНАЧНОСТЬ, СТРЕЛКА ПИРСА и ИЛИ.

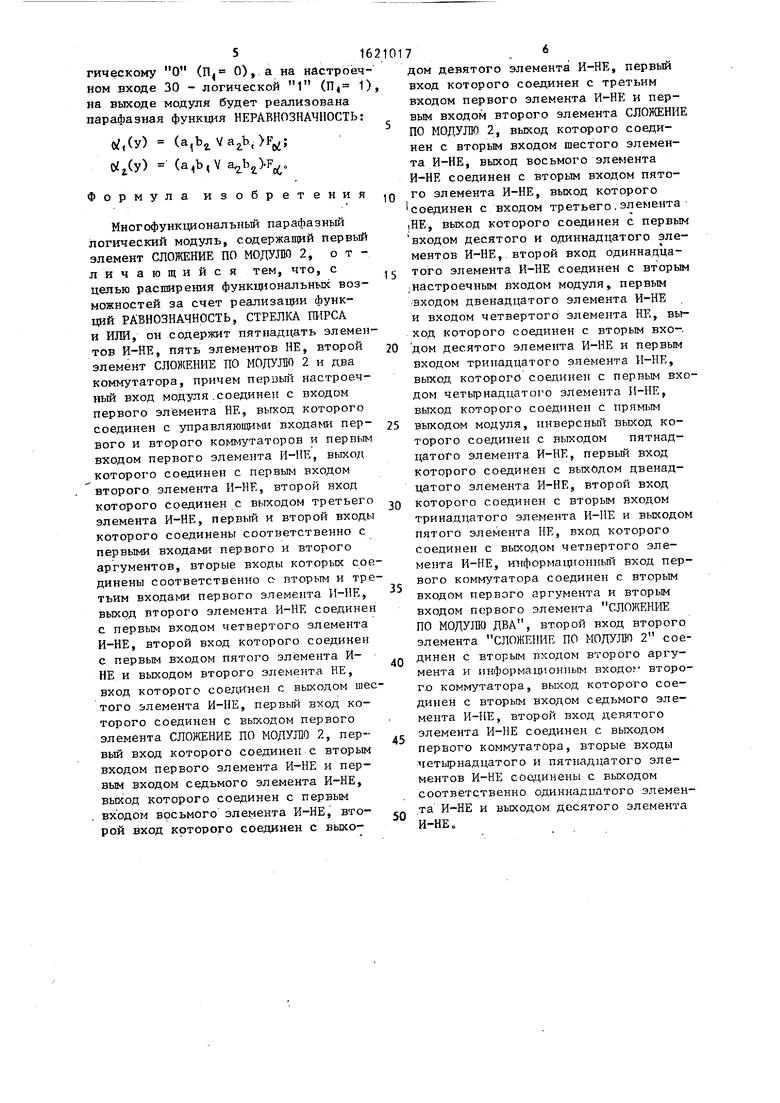

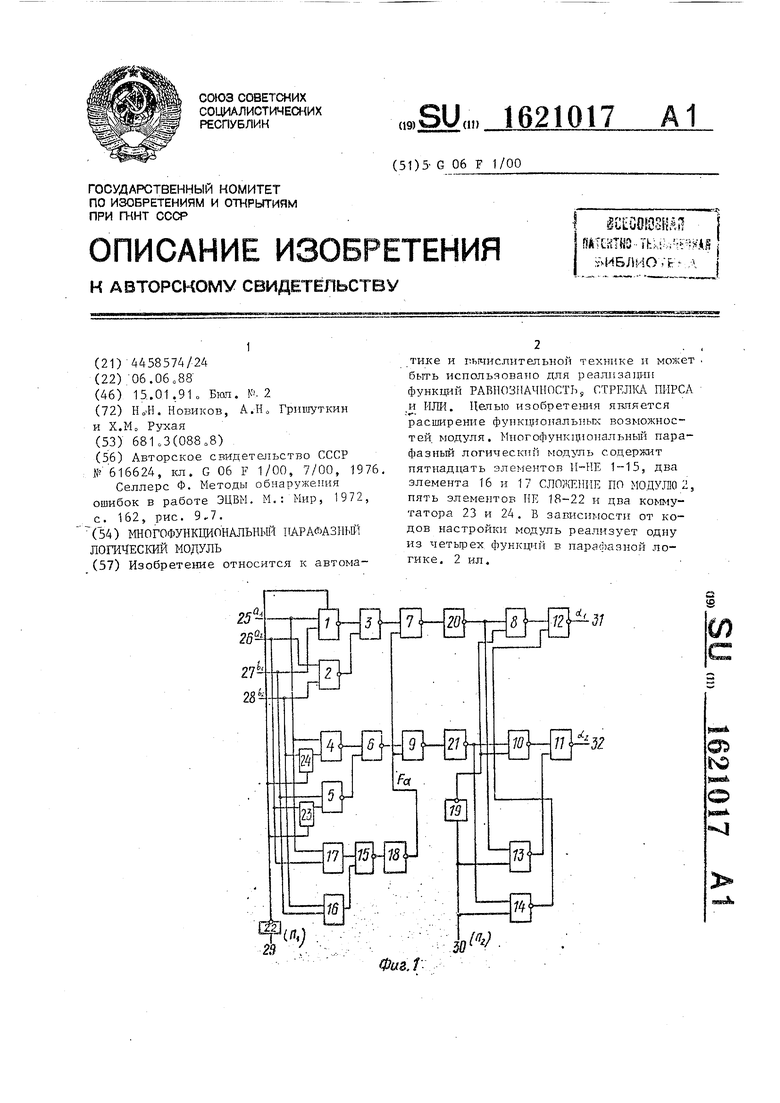

На фиг. 1 представлена структурная схема многофункционального парафаз- ного логического модуля; на фигс 2 - пример реализации коммутатора.

Модуль (фиг. 1) содержит пятнадцать элементов И-НЕ 1-15, два элег мента 16 и 17 СЛОЖЕНИЕ ПО МОДУЛИ), пять элементов НЕ 18-22,два коммутатора 23 и 24s парафазные входы 25 и 26 первого аргумента, парафазные входы 27 и 28 второго аргумента, два настроечных входа 29 и 30, парафазные выходы 31 и 32.

Коммутаторы 23 и 24 (фиг 2) со- держат обмотку реле 33 и подвижный контакт 34„

В качестве элементов И-НЕ 4 и 5 применяются интегральные схемы, у которых на незадействованном входе формируется сигнал, эквивалентный логической 1.

В качестве коммутаторов 23 и. 24 возможно применение транзисторных реле или транзисторных ключей

Функционирование модуля основано на законах парафазией логики Первая парафазная переменная а, и a поступает на входы 25 и 26, вторая пара- фазная переменная Ъ - на входы 27 и 28. Значение парафазией выходной функции снимается с выходов 31 и 32„

Парафазный логический модуль функционирует исправно, если на его вхо- ды 25-28 поступает код 0,1 или 1,0 и, аналогично, на выходах

31,32 формируется код 0,1 или

1,0 .

Свидетельством того, что в процессе функционирования модуля возникла неисправность или случайный обой, будет код С.О,0 или 1,1 на выходе 31, 32 модуля„ Запрещенный код будет сформирован на выходе 31,

32,если на входы модуля (входы 25, 26 или 27, 28) поступит код 10,0 или 1,1 о

Модуль работает следующим образом

Q

5

0

з

0

При нулевом значении настроечных входов 29 и 30 модуль реализует пара- фазную логическую функцию РАВНОЗНАЧНОСТЬ, Tce0 если обозначим функцию, реализуемую на выходе 31, через ,( (у), а функцию, реализуемую на выходе 32, через (у) , то:

Ci,(y а,Ъ, V агЬь).Ры; огг(у) m U,bt V aub,).

где % - (a,® ae)(b{® Ь2)0

При значении управляющих воздействий на настроечном входе 29 равном логической 1, а на настроечном входе 30 - логическому О, на выходах 31 и 32 модуля будет реализована парафазная логическая функция СТРЕЛКА ПИРСА:

) 0/г(у) (аЛ b)-F

Формирование этой функции осуществляется за счет разрыва цепи между вторыми входами элементов И-НЕ 4 и 5 и входами 26 и 28 о Разрыв связи осуществляется через коммутаторы 23 и 24. При поступлении сигнала П 1 на настроечный вход 29 с выхода элемента НЕ 22 снимается сигнал логического О, обесточивающий обмотку реле 33, в результате размыкается контакт 34 (фиго 2)0 Обрыв связи между этими цепями приводит к тому, что на незадействованных входах элементов И-НЕ 4 и 5 постоянно присутствует сигнал, эквивалентный логической т0е0 при П - 1 на настроечном входе 29 на выходе элемента И-НЕ 1 реализуется функция

F, atYb, Y 1 1,

на выходе элемента И-НЕ 4 при П( 1 - функция

$ a/v-t а, , ,

на выходе элемента И-НЕ 5 - функция F5 Т Ч Ъ Т, .

При единичном значении настроечных входов 29 и 30 на выходе модуля реализуется парафазная логическая функция ИЛИ:

U/, (у) (,); Й2(у) (а2.

При значении управляющих воздействий на настроечном входе 29, равном ло-

51

гическому О (П, 0), а на настроечном входе 30 - логической 1 (П, 1 на выходе модуля будет реализована парафазная функция НЕРАВНОЗНАЧНОСТЬ:

tf«(y) a,bt Vajb,; (у) (a,b,V .

Формула изобретения

Многофункциональный парафазный логический модуль, содержащий первый элемент СЛОЖЕНИЕ ПО МОДУЛЮ 2, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации функций РАВНОЗНАЧНОСТЬ, СТРЕЛКА ПИРСА и ИЛИ, он содержит пятнадцать элементов И-НЕ, пять элементов НЕ, второй элемент СЛОЖЕНИЕ ПО МОДУЛЮ 2 и два коммутатора, причем перлый настроечный вход модуля соединен с входом первого элемента НЕ, выход которого соединен с управляющими входами пер- вого и второго коммутаторов и первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И-НЕ, первый и второй входы которого соединены соответственно с первыми входами первого и второго аргументов, вторые входы которых соединены соответственно с вторым и третьим входами первого эпемента И-НЕ, выход второго элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, второй вход которого соединен с первым входом пятого элемента И- НЕ и выходом второго элемента НЕ, вход которого соединен с выходом шестого элемента И-НЕ, первый вход которого соединен с выходом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2, пер- вый вход которого соединен с вторым входом первого элемента И-НЕ и первым входом седьмого элемента И-НЕ, выход которого соединен с первым входом восьмого элемента И-НЕ, вто- рой вход которого соединен с выхо

0

0 5 Q 5 5 л

0

7.

дом девятого элемента И-НЕ, первый вход которого соединен с третьим входом первого элемента И-НЕ и первым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2, выход которого соединен с вторым входом шестого элемента И-НЕ, выход восьмого элемента И-НЕ соединен с вторым входом пятого элемента И-НЕ, выход которого соединен с входом третьего,элемента (НЕ, выход которого соединен с первым входом десятого и одиннадцатого элементов И-НЕ, второй вход одиннадцатого элемента И-НЕ соединен с вторым настроечным входом модуля, первым входом двенадцатого элемента И-НЕ и входом четвертого элемента НЕ, выход которого соединен с вторым входом десятого элемента И-НЕ и первым входом тринадцатого эпемента И-НЕ, выход которого соединен с первым входом четырнадцатого элемента И-НЕ, выход которого соединен с прямым выходом модуля, инверсный выход которого соединен с выходом пятнадцатого элемента И-НЕ, первый вход которого соединен с выходом двенадцатого элемента И-НЕ, второй вход которого соединен с вторым входом тринадцатого элемента И-ПЕ и выходом пятого элемента НЕ, вход которого соединен с выходом четвертого элемента И-НЕ, информационный вход первого коммутатора соединен с вторым входом первого аргумента и вторым входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, второй вход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 соединен с вторым входом второго аргумента и информационным входог второго коммутатора, выход которого соединен с вторым входом седьмого элемента И-НЕ, второй вход девятого элемента И-НЕ соединен с выходом первого коммутатора, вторые входы четырнадцатого и пятнадцатого элементов И-НЕ соединены с выходом соответственно одиннадиатого элемента И-НЕ и выходом десятого элемента И-НЕ „

&W

p/jjJ

-Hotf5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1983 |

|

SU1167601A1 |

| Универсальный логический модуль | 1983 |

|

SU1148024A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| Универсальный логический модуль | 1987 |

|

SU1476457A1 |

| Универсальный логический модуль | 1985 |

|

SU1252770A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1247858A1 |

| Универсальный логический модуль | 1983 |

|

SU1161938A1 |

| Дешифратор с контролем | 1987 |

|

SU1524184A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

| Многофункциональный логический элемент | 1982 |

|

SU1064472A1 |

Изобретение относится к автоматике и гычислительной технике и может быть использовано для везли за шш функций РАВНОЗНАЧНОСТЬ, ГГРГЛКА ПИРСА и ПЛИ. Цепью изобретения является расширение функциональных возможностей модуля. Многофункциональный пара- фазный логический модуль содержит пятнадцать пе ентов И-НГ 1-15, два элемента 16 и 17 СПОКГНИЕ ПО МОДУ ДО 2, пять элементов НГ 18-22 и два коммутатора 23 и 24. В зависимости от кодов настройки модуль реализует одну из четырех функции в паразитной по- гике. 2 ил.

i

L.

UJ

фуг 2

| Элемент ассоциативной матрицы | 1976 |

|

SU616624A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М.: Мир, 1972, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-01-15—Публикация

1988-06-06—Подача