1

(21)4256911/24-24

(22)04.06.87

(46) 23.11.89. Бюл. К- 43 (72) И.Н.Новиков, Х.М.Рухая, А.Н.Гришуткин и К.Ш.Пхакадзе

(53)681.3 (088.8)

(56)Авторское свидетельство СССР № 1038934, кл. Н 03 М 7/22,

G 06 F 11/26, 1982.

(54)ДЕШИФРАТОР С КОНТРОЛЕМ

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств с парафазной лоП 1516 I I

№И-тП

15

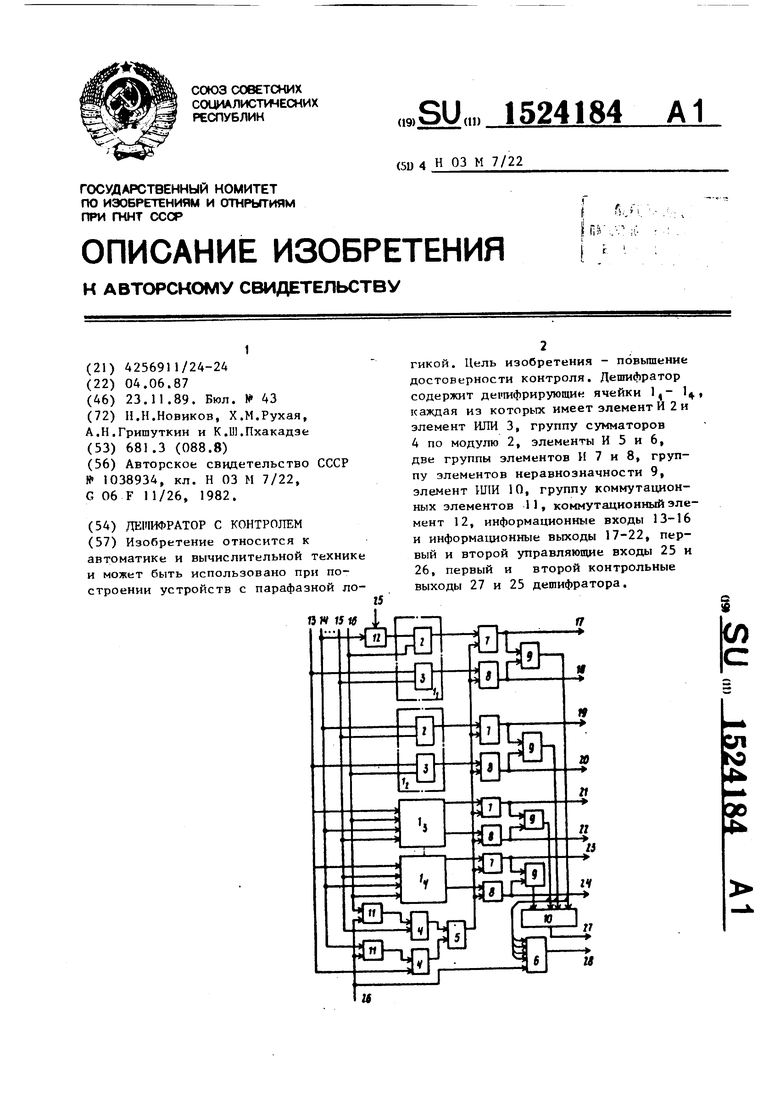

гикой. Цель изобретения - повышение достоверности контроля. Дешифратор содержит дершфрирующие ячейки 1,- Ц каждая из которых имеет элемент И 2 и элемент ИЛИ 3, группу сумматоров 4 по модулю 2, элементы И 5 и 6, две группы элементов И 7 и 8, группу элементов неравнозначности 9, элемент Ш1И 10, группу коммутационных элементов И, коммутационный элемент 12, информационные входы 13-16 и информационные выходы 17-22, первый и второй управляюпше входы 25 и 26, первый и второй контрольные выходы 27 и 25 дешифратора.

I I

-тП

i (Л

:п

N9

.

и

Изобретение относится к автоматике и вычислительной технике и може быть использовано при построении устройства с парафлзной ложкой.

Целью изобретения является повышение достоверности контроля.

На чертеже представлена функциональная схема дешифратора для случая двухразрядного входного кода.

Дешифратор сод -ржит дешифрирующие ячейки 1 - 14., каждая из которых имеет элемент И 2 и элемент ИЛИ 3, группу сумматоров 4 по модулю два элементы И 5 и 6, две группы эле- ментов И 7 и 8, группу элементов РАВНО: НАЧ1ЮСТЬ 9, элемент ИЛИ Ш, группу коммутационных элементов 1 1 , коммутационный элемент 12, информационные входы 13 -16 и информа- ционные выходы 17-24, первый и второ управляющие входы 25 и 26, первый 27 и второй 28 контрольные выходы дешифратора.

Дешифратор работает следующим об- разом.

На прямые 13 и 15 и инверсные 14 и 16 информационные входы подается входной код в прямой и инверсной форме. В том случае, когда входные комбинации на входах 13 и 1 fS удовлетворяют требован1 ян швс.рсии, на выходах сумматоров А формируются едпиичтие синалы и единичный С1 гпалс выхода элемента И 5откр п.ч. Т элементы и 7 и8. С помощью элементов t НОЗНАЧНОСТЬ 9 контролируется парафа3нос 1 ь выходного кода. При отсутствии искажений во входном и выходном кодах Tia выходе элемента ИЛИ 10 контрольный сигнал имеет нулевое значение. В случае нарушения условия парафазности во входном или выходном коде по крайней мере на выходе одного из сумматоров 4 появляется нулевой сигнал, что приводит к формированию нулевых сигналов на выходах элементов И 3, 7 и 8. В результате на выходах элементов РАВНОЗНАЧНОСТЬ 9 возникают единичные сигналы, которые через элемент ИЛИ 10 поступают на контрольный выход 27. При нару1пенип парафазности выходного кода единичный сигнал возникает на выходах одного или нескольких элементов РАВНОЗНАЧНОСТЬ 9 . Единичный сигнал на контрольном выходе 27 возникает также при наличии в устройстве одиночных неисправностей типа const 1 или const О на выходах

Q

0

5

5

0

5

0

элементов 1, 2, 3,7 ив, одиночных неисправностей типа const О на выходах элементов 4 и 5, одиночных неисправностей типа const 1 на выходах элементов 9 и 10.

Для того, чтобы проверить отсутствие неисправностей типа const О, на выходе элементов 9 и 10 на выходном воздействии О,1; 0,1 , которое подается соответственно на выходы 13-16, подается управляющий сигнал на вход 25. При подаче этого сигналь разрывается цепь коммутационным элементом 12 между входом 14 и элементом И 2. В этом случае на выходах 17 и 18 возникает нулевой код(0,0), который фиксируется элементом РАВНОЗНАЧНОСТЬ 9 и на выходе 27 появляется единичный сигнал. Для того, чтобц проверить отсутствие неисправностей типа const 1 на выходе элементов 4 и 5 и const О на выходе элементов 9 и 10, на управляющий вход 26 подается сигнал. По этой управляющей команде коммутационные элементы разрывают связь между инверсными входами дешифратора и вторьП 5и входами сумматоров 4 по модулю два. В этом с выхода элемента И 5 снимается сигнал логического О, т.е. на выходах 17-24 формируется нулевой код, а на выходе 27 - единичный сигнал. На выходе 28 формируется единичный сигнал, свидетельствующий о работоспособности всей группы эле- ментов 9, Если при подаче сигнала на управляющие входы 25 и 26 на выхо де 27 сигнал логической 1 не формируется, то это свидетельствует о наличии неисправности в устройстве. Выход 28 используется только тогда, когда подается управляющий сигнал на вход 26.

Формула изобретения

Дешифратор с контролем, содержащий дешифрирующие ячейки, входы которых, кроме первого входа первой дещифрирующей ячкзйки, подключены к соответствующим информационным входам дешифратора, группу сумматоров по модулю два, первые входы которых подключены к одноименным прямым информационным входам дешифратора, отличающийся тем, что, с целью повышения достоверности контроля, в Него введены элементы

И, группы элементов И, группы коммутационных элементов, группа элементов РАВНОЗИАШЮСТЬ, элемент ИЛИ и коммутационный элемент, вход которого соединен с первым инверсным информационным входом дешифратора, выход - с первым входом первой деширирующей ячейки, первый и второй выходы каждой дешифрирующей ячейки соединены с первыми входами одноименных элементов И первой и второй группы соответственно, выходы которых являются соответствующими пара- фазными выходами дешифратора и сое- динены с входами одноименных элементов РАВНОЗНАЧНОСТЬ группы, выходы которых соединены с соответствующими входами элемента ИЛИ и первого элемента И, входы коммутационных эле-

ментов группы соединены с одноимен ными инверсными информационными входами дешифратора, выходы - с вторыми входами одноименных сумматоров по модулю два группы, выходы которых соединены с соответствующими входами второго элемента И, выход которого подключен к объединенным вторым входам элементов И первой и второй групп, управляющий вход коммутационного элемента, объединенные управляющие входы коммутационных элементов группы и последний вход первого элемента И являются соответственно первым и вторым управляющими входами дешифратора, выходы первого элемента И и элемента ИЛИ являются соответственно первым и вторым контрольным выходом дешифратора,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля счетчиков | 1988 |

|

SU1548787A1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

| Перестраиваемый шифратор | 1989 |

|

SU1651384A1 |

| Устройство для выделения остатка по переменному модулю | 1984 |

|

SU1270774A2 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Дешифратор на @ входов с контролем | 1982 |

|

SU1038934A1 |

| Устройство аналого-цифрового преобразования с самоконтролем | 1989 |

|

SU1695498A1 |

| Устройство для функционального контроля вычислительных машин | 1983 |

|

SU1134943A1 |

| Многофункциональный парафазный логический модуль | 1988 |

|

SU1621017A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств с парафазной логикой. Цель изобретения - повышение достоверности контроля. Дешифратор содержит дешифрирующие ячейки 1.1-1.4, каждая из которых имеет элемент И 2 и элемент ИЛИ 3, группу сумматоров 4 по модулю 2, элементы И 5 и 6, две группы элементов И 7 и 8, группу элементов неравнозначности 9, элемент ИЛИ 10, группу коммутационных элементов 11, коммутационный элемент 12, информационные входы 13-16 и информационные выходы 17-22, первый и второй управляющие входы 25 и 26, первый и второй контрольные выходы 27 и 25 дешифратора. 1 ил.

Авторы

Даты

1989-11-23—Публикация

1987-06-04—Подача