f

Изобретение относится к вычислительной технике и автоматике и предназначено для реализации всех логических функций двух переменных, а также функций одноразрядного двоичного сумматора.

Цель изобретения - расширение функциональных возможностей для реализации функции одноразрядного двоичного сумматора.

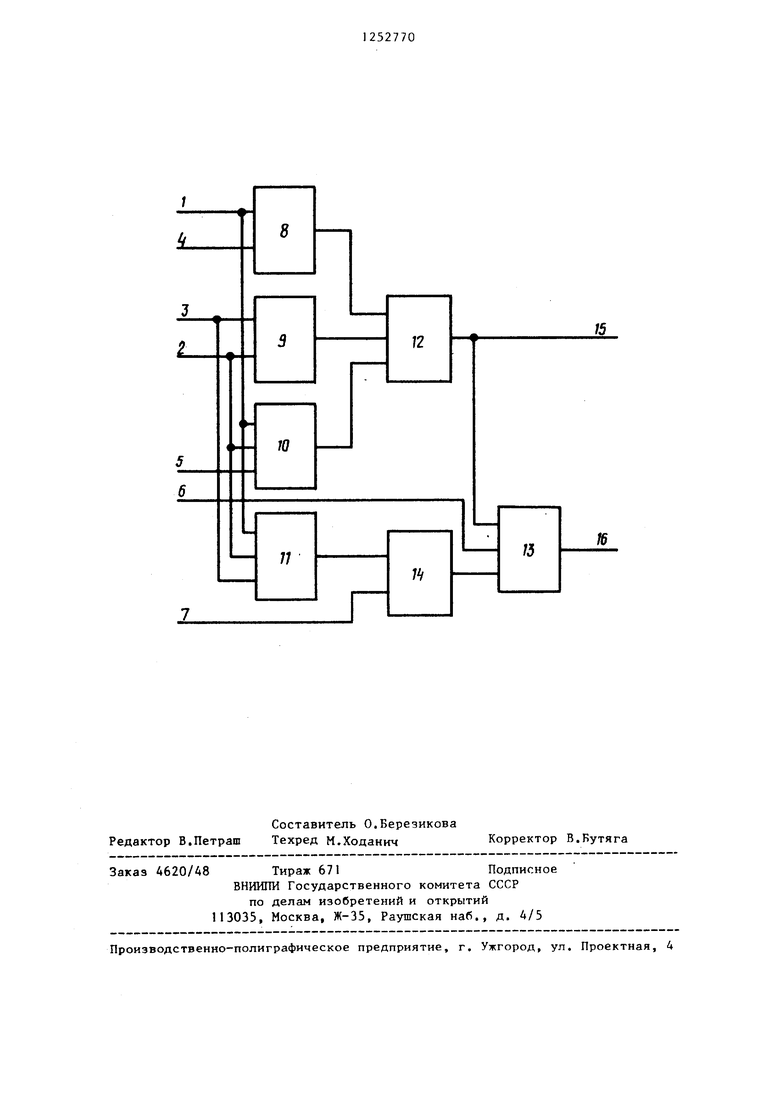

На чертеже представлена функциональная схема универсального логического модуля.

Модуль содержит информационные входы 1 и 2, настроечные входы 3-7, элементы И 8-10, элемент РАВНОЗНАЧ НОСТЬ 11 и два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 12 и 13, элемент И U. Выходы элементов 8-10 подключены к

527701

входам элемента 12, а элемента 11 - к первому входу элемента 14, входы элемента 13 подключены к выходам элементов 12 и 14 и к настро- 5 ечному входу 6, выходы элементов 12 и 13 являются выходами 15 и 16 модуля соответстгенно.

Универсальный логический модуль

О работает в двух режимах.

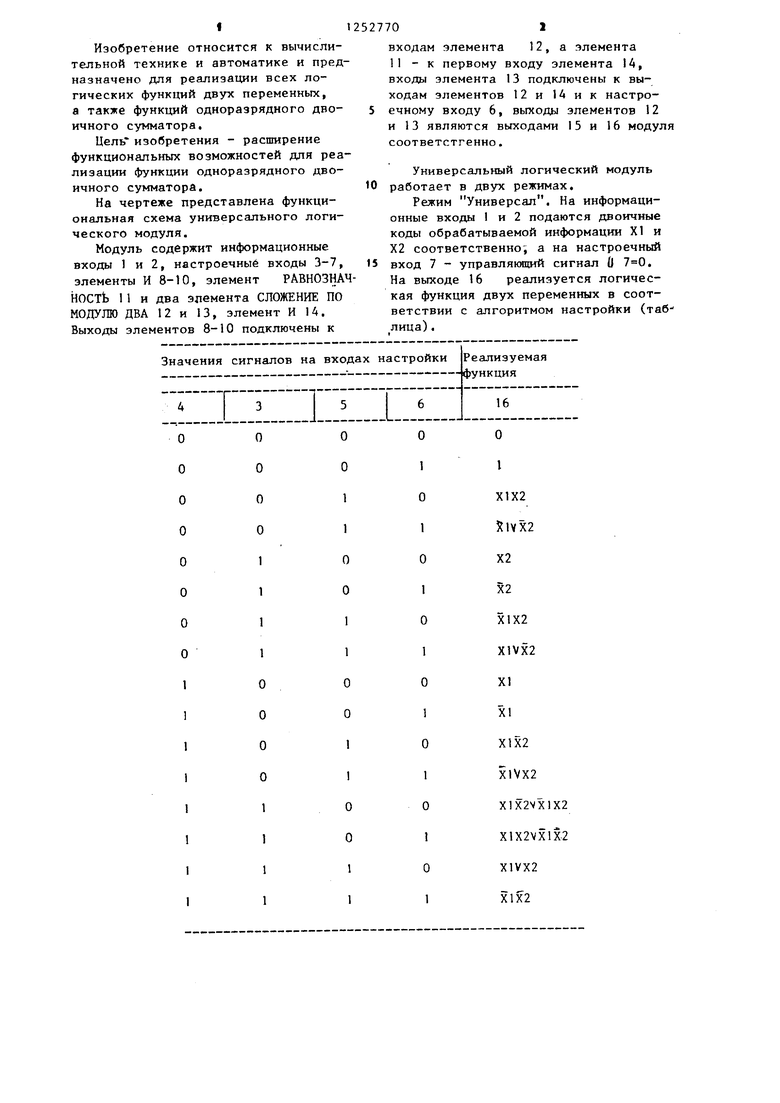

Режим Универсал. На информационные входы I и 2 подаются двоичные коды обрабатываемой информации XI и Х2 соответственно а на настроечный

5 вход 7 - управляющий сигнал О . На выходе 16 реализуется логическая функция двух переменных в соответствии с алгоритмом настройки (таблица) .

Режим Сумматор. На информационные входы 1 и 2 подаются двоичные коды обрабатываемой информации XI и Х2 соответственно,на настроечный вход 7 - управляющий сигнал U 7. Значение сигнала переноса из предыдущего разряда Р подается на настроечные входы 4 и 3; на настроечный вход 5 подается сигнал U , а на настроечный вход 6 - сигнал И . При этом на выходе 16 формируется сигнал суммы S P6 X16 X2, а на выходе 15 - сигнал переноса в следующий разряд ,,.

Таким образом, универсальный ло-. гический модуль в режиме Универсал реализует все логические функции двух переменных, а в режиме Сумматор выполняет функцию полного одноразрядного двоичного сумматора и об- ладает при этом рядом преимуществ. Модуль прост в управлении настроечные сигналы принадлежат множеству ) перевод модуля из режима Универсал в режиме Сумматор осу- ществляется изменением управляющего сигнала только на одном настроечном входе. Кроме того, так как всякая логическая функция и функция суммы снимаются с одного выхода, при использовании модуля в арифметико- логических устройствах не требуется дополнительный выходной коммутатор, что упрощает конструкцию АЛУ.

Применение данного модуля позво- лит упростить конструкцию вычислительного устройства и частично унифицировать его состав, возложив на модуль функции универсала и сумматора. Формула изобретения

Универсальный логический модуль, содержащий элементы И, РАВНОЗНАЧНОСТ

и СЛОЖЕНИЕ ПО МОШ ЛЮ ДВА, причем первый информационный яход модуля соединен с первым входом первого элемента И, второй вход которого является первым настроечным входом модуля, выход первого элемента И соединен с первьнч входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, второй вход которого соединен с выходом второго элемента И, первый вход которого является вторым информационным входом модуля, а второй вход второго элемента И соединен с вторым информационным входом модуля и первым входом элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом третьего элемента И, второй вход которого является третьим настроечным входом модуля, отличающийся тем что, с целью расширения функциональных возможностей для реализации функции одноразрядного двоичного сумматора, модуль содержит дополнительно элементы И и СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, причем первый и второй входы четвертого элемента И соединены с первьм и вторым информационными входами модуля соответственно, а тр етий вход четвертого элемента И является четвертым настроечным входом модуля, выход четвертого элемента И соединен с первым входом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, второй вход которого является пятым настроечным входом модуля, а третий вход второго элемента СЛО- ЖЕНШ- ПО МОДУЛЮ ДВА соединен с выходом третьего элемента И, выходы первого и второго элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА являются выходами модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1789976A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1282112A1 |

| Устройство для выделения симметрических булевых функций | 1991 |

|

SU1833859A1 |

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Многофункциональный логический модуль | 1983 |

|

SU1109735A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Универсальный логический модуль | 1987 |

|

SU1476457A1 |

Изобретение относится к вычислительной технике и автоматике и предназначено для выполнения операции суммирования одноразрядных двоичных чисел и реализации всех логических функций дпух переменных. Целью изобретения является расширение функциональных возможностей универсального логического модуля за счет выполнения операции суммирования. Поставленная цель достигается тем, что модуль содержит два информационных и пять настроечных входов, элемент РАВНОЗНАЧНОСТЬ, четыре элемента И и два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и имеет два выхода, на одном из которых могут быть получены любые логические функции двух пе- ременньрс при работе модуля в режиме Универсал и функция суммы при работе в режиме Сумматор, а на другом - функция переноса при работе модуля в режиме Сумматор. Достоинством модуля является разделение информационных и настроечных входов, простота настройки, малая сложность и высокое быстродействие, возможность реализации на одном выходе любых логических функций двух переменных и сигнала суммы при выполнении операции суммирования одноразрядных двоичных чисел. 1 ил, 1 табл. (Л KD СП vj

Редактор В.Петраш

Составитель О.Березикова Техред И.Ходанич

Заказ 4620/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор В.Бутяга

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1972 |

|

SU433476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональный модуль | 1978 |

|

SU700864A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для разбрызгивания крахмалосодержащей массы | 1957 |

|

SU109663A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1983 |

|

SU1161938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-01-09—Подача