-Л

SO

«.V

8

Изобретение относится к вычислительной технике и может быть использовано в мультипроцессорных вычислительных системах (МВС) для управлени запуском пакетов программ, состав- пенных из независимых заданий полъэо ватенейо

Целью изобретения является расширение области применения устройства за счет учета времени решения пакета программе

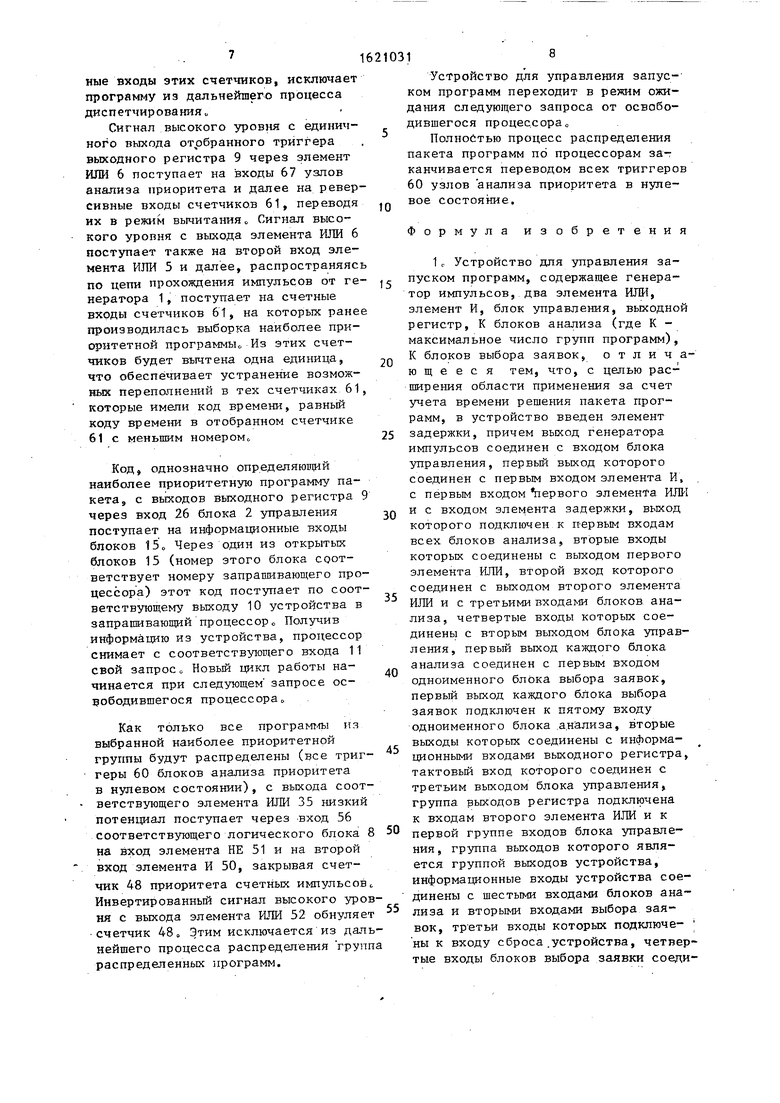

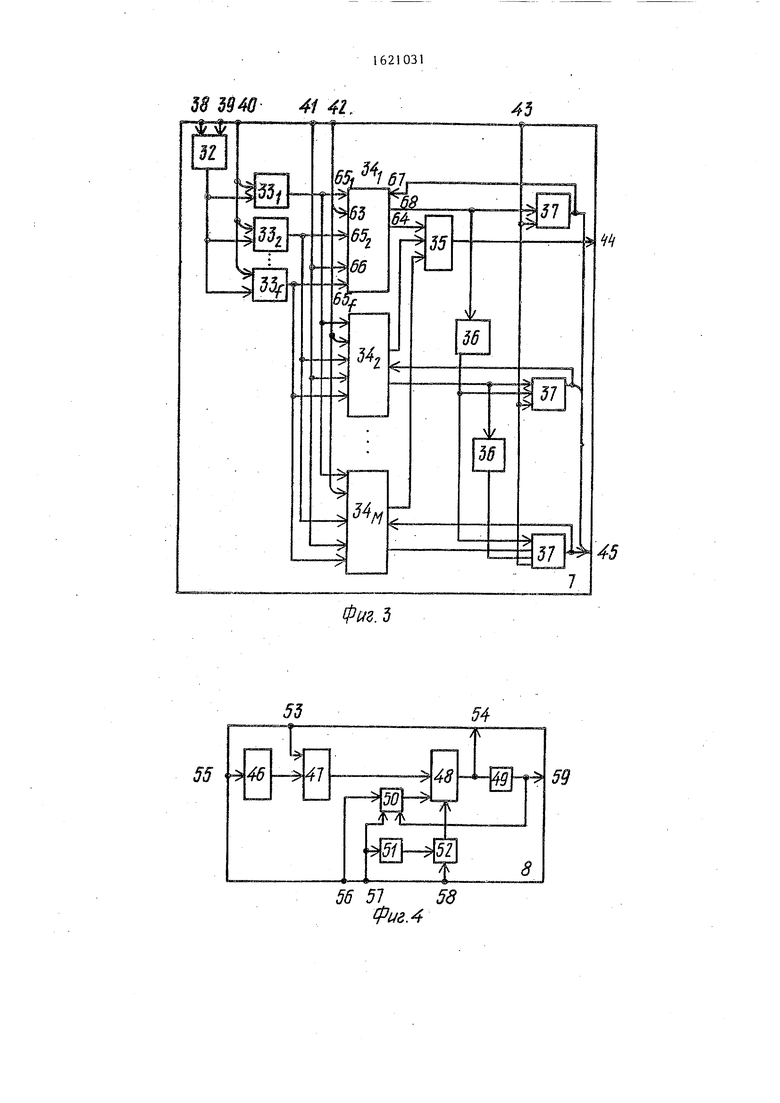

На фиг о 1 приведена структурная схема устройства для управления запуском программ; на фигс 2 - схема блока управления; на фиг„ 3 - схема блока анализа; на фиг 4 - схема логического блока; на фиг„ 5 - схема узла анализа приоритета.

Устройство содержит генератор 1 импульсов, блок 2 управления, элемен И 3, элемент 4 задержки, элемент ИЛИ 5, элемент ИЛИ 6, блоки 7 анализа, логические блоки 8, выходной регистр 9, группу выходов 10 устрой- ства, группу кодовых входов 11 устройства, информационные входы 12 устройства, вход 13 сброса устройства, вход 14 запуска устройства„

Блок 2 управления содержит группу блоков элементов И 15, элемент И 16, элемент ИЛИ 17, элемент НЕ 18, групп элементов И 19, группу элемент о-в ИЛИ.20, дешифратор 21, счетчик 22, элемент И 23, генератор 24 импульсов группу выходов 25, входы 26-28, выход 29 группу входов 30, выход 31.

Блок 7 анализа содержит элемент И 32, группу элементов И 33, группу узлов 34 анализа приоритета, элемент ИЛИ 35, группу элементов НЕ 36, группу элементов И 37, входы 38-43, выходы 44, 45.

Логический блок содержит регистр 46 приоритета, группу блоков элементов И 47, счетчик 48, элемент НЕ 49, элемент И 50, элемент НЕ 51, элемент ИЛИ 52, вход 53, выход 54, входы 55- 58, выход 59.

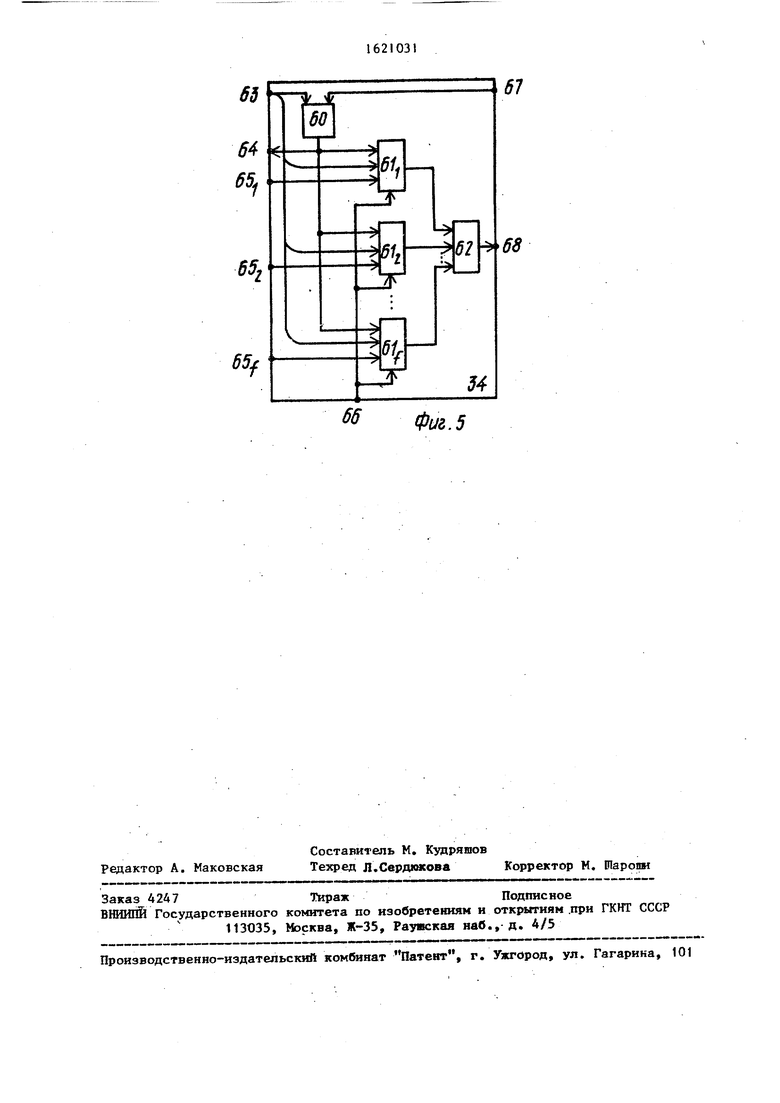

Узел 34 анализа приоритета содержит триггер 60, группу счетчиков 61, элемент ИЛИ 62, группу входов 63, первый выход 64, группу входов 65, вход 66, вход 67, выход 68„

Перед началом решения пакета программ от центрального процессора в устройство заносится исходная информация. Сигнал, i-оступающий от цент

0

5

0 5

0 5

0

$

0

рального процессора, через вход 12 устройства заносит в регистры 46 логических блоков 8 приоритета групп программ, составляющих реализуемый пакет„ Этим же сигналом через входы 42 блоков 7 анализа, входы 63 узлов 34 анализа приоритета триггеры 60 узлов 34 анализа приоритета переводятся в единичное состояние для программ, которые входят в решаемый пакет, а в счетчики-61 заносятся времена решения программ на различных типах процессоров„ Регистры 46 приоритета, триггеры 60, счетчики 61 времени составляют регистровую память устройства. Через вход 13 устройства от центрального процессора поступает сигнал низкого уровня, который через входы 57 логических блоков 8 и элементы ИЛИ 52 устанавливает в О счетчики 48„ В момент полного заполнения отобранного поля регистровой памяти через вход 14 устройства от центрального процессора сигнал высокого уровня поступает на управляющие входы групп блоков 47 для перезаписи информации из регистров 46 в счетчики 48„ Устройство готово к работе

После записи исходной информации на единичном выходе триггеров 60 узлов 34, которые переведены в единичное состояние, устанавливаются высокие потенциалыо Они открывают счетчики 61 для счетных импульсов„ У счетчиков 61 после занесения информации триггеры переполнения находятся в нулевом состоянии о С их единичных выходов на входы элементов ИЛИ 62 подаются низкие потенциалы. Если хотя бы один из триггеров 60 находится в единичном состоянии, то с выхода соответствующего элемента ИЛИ 35 снимается высокий потенциал, который, поступаягчерез вход 56 соответствующего логического блока 8 на второй вход элемента И 50, открывает его для счетных импульсов„ В этом случае устройство работает следующим образом.

Освободившийся от вычислительной работы процессор по соответствующему входу 11 посылает запрос о готовности к реализации очередной программы пакета о При этом на одном из входов 30 блока управления, номер которого соответствует номеру, запрашивающего процессора, появляется высокий по-

D1

тенциал, который поступает на первый вход одного из элементов И 19. С генератора 24 импульсов через открытый элемент И 23 на счетный вход счетчика 22 поступают счетные импульсы С помощью счетчика 22 и дешифратора 21 организуется циклический просмотр элементов И 19 на предмет наличия на их первых входах высоких потенциалов„ Это осуществляется путем подачи на вторые входы элементов И 19 кода, дешифрованного дешифратором 21 о Когда на входах элемента И 1 будут высокие потенциалы (это спи- детельствует о том, что запрашивает процессор с соответствующим номером) на выходе этого элемента II 19 появляется высокий потенциал, который поступает на элемент ИЛИ 7 и далее, инвертируясь элементом НЕ 18, закрывает для счетных импульсов элемент И 23. Сигнал низкого уровня через выход 29 блока 2 поступает также на управляющий вход выходного регистра 9, разрешая тем самым производить па него запись. Высокий потенциал с выхода элемента ИЛИ 17 открывает для счетных импульсов с генератора 1 импульсов элемент И 16. Высокий по тенциал с выделенного элемента И 19 поступает также на вход элемента ИЛИ 20, соответствующего типу запрашивающего процессора о Сигнал высокого уровня с этого элемента ИЛИ по соответствующему выходу 31 блока управления через соответствующий вход 41 поступает на первые входы соот- ветствуклшх запросившему процессору элементов И 33 блока 7 анализа, от- крывая их для прохождения сигналов через вторые входы, С выхода 27 блока 2 счетные импульсы от генератора через открытый на время существования запроса от процессора элемент 16 и через элемент И 3 поступают на первый вход элементов И 50 и далее (для открытых элементов И 50) на счетные входы счетчиков 48 „ Подсчет импульсов в счетчиках продолжается до момента появления сигнала переполнения на выходе счетчика, в котором был записан наибольший приоритет По этому сигналу однозначно определяется старшая по приоритетности группа программ Сигнал переполнения, инвертируемый элементом НЕ 49, закрывает для счетных импульсов эле- мент И 50 и элемент И 3. Сигнал

д 0 5 Q 5 0

5

316

переполнения с выхода счетчика 48 поступает также через выход 59 логического блока 8 на второй вход соответствующего элемента И 32 соответст-} вующего блока 7 анализа, открывая этот элемент для счетных импульсов с генератора 1 ., Счетные импульсы, пройдя элемент ИЛИ 5, элемент И 32 и предварительно открытый в выбранной группе элемент И 33, поступают через соответствуюпчте входы 65 узлов 34 анализа приоритета на счетные входы счетчиков 61,

Подсчет импульсов в счетчиках 61 продолжается до момента появления сигнала переполнения на выходе хотя бы одного счетчика 61, в котором было записано нанбольпее яремя (в группе может находиться несколько программ с одинаковым временем выполнения) 0 Высокий потенциал с каждого отобранного счетчика 61 поступает через элемент ПЛИ 62 m второй вход соответствующего элемента И 37 о Инвертируемый соответствуэтгптм элементом НЕ 36 низкий потенциал закрывает -элементы И 37 для РССХ последующих у шов 34 анализа приоритета. На первые входы всех .элементов И 37 через лишил 4 задержки поступают импульсы от генератора 1/ с помошью которых осуществляется однозначный выбор только однofi программы (программы с. меньшим номс .ром) из совокупности программ, имеющих одинаковое максимальное время выполнения, Это обеспечивается выбором такого времени задержки импульсов линией 4 задержки, которое равно суммарному времени всех переходных процессов, происходящих по одному импульсу генератора 1 от момента поступления его на первый вход элемента 1 ЛИ 5 до момента появления низких потенциалов на входах элементов И 37 с выходов соответствующих элементов НЕ 36.,

Сигнал высокого уровня с отобранного элемента И 37 поступает на единичный вход соответствующего разряда выходного регистра 9.

Этот же сигнал через вход 66 соответствующего узла 34 анализа приоритета поступает на нулевой вход триггера 60, сбрасывая его в О Сигнал низкого уровня с единичного выхода триггера 60, обнуляя счетчики 61 времени и запирая тем самым счетные входы этих счетчиков, исключает программу из дальнейшего процесса диспетчированияо

Сигнал высокого уровня с единичного выхода отобранного триггера выходного регистра 9 через элемент ИЛИ 6 поступает на входы 67 узлов анализа приоритета и далее на реверсивные входы счетчиков 61, переводя их в режим вычитания о Сигнал высокого уровня с выхода элемента ИЛИ 6 поступает также на второй вход элемента ИЛИ 5 и далее, распространяясь по цепи прохождения импульсов от генератора 1, поступает на счетные входы счетчиков 61, на которых ранее производилась выборка наиболее приоритетной программно Из этих счетчиков будет вычтена одна единица, что обеспечивает устранение возможных переполнений в тех счетчиках 61, которые имели код времени, равный коду времени в отобранном счетчике 61 с меньшим номеромо

Код, однозначно определяющий наиболее приоритетную программу пакета, с выходов выходного регистра 9 через вход 26 блока 2 управления поступает на информационные входы блоков 15 „ Через один из открытых блоков 15 (номер этого блока соответствует номеру запрашивающего процессора) этот код поступает по соответствующему выходу 10 устройства в запрашивающий процессор Получив информацию из устройства, процессор снимает с соответствующего входа 11 свой запрос , Новый цикл работы начинается при следующем запросе освободившегося процессора„

Как только все программы из выбранной наиболее приоритетной группы будут распределены (все триггеры 60 блоков анализа приоритета в нулевом состоянии), с выхода соответствующего элемента ИЛИ 35 низкий потенциал поступает через вход 56 соответствующего логического блока 8 50 на вход элемента НЕ 51 и на второй вход элемента И 50, закрывая счетчик 48 приоритета счетных импульсовс Инвертированный сигнал высокого уров1 о Устройство для управления запуском программ, содержащее генератор импульсов, два элемента ИЛИ, элемент И, блок управления, выходно регистр, К блоков анализа (где К - максимальное число групп программ), К блоков выбора заявок, отлич ющееся тем, что, с целью расширения области применения за счет учета времени решения пакета программ, в устройство введен элемент задержки, причем выход генератора импульсов соединен с входом блока управления, первый выход которого соединен с первым входом элемента И с первым входом первого элемента ИЛ и с входом элемента задержки, выход которого подключен к первым входам всех блоков анализа, вторые входы которых соединены с выходом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и с третьими входами блоков анализа, четвертые входы которых соединены с вторым выходом блока управ ления, первый выход каждого блока анализа соединен с первым входом одноименного блока выбора заявок, первый выход каждого блока выбора заявок подключен к пятому входу одноименного блока анализа, вторые выходы которых соединены с информационными входами выходного регистра тактовый вход которого соединен с третьим выходом блока управления, группа выходов регистра подключена к входам второго элемента ИЛИ и к первой группе входов блока управления , группа выходов которого является группой выходов устройства, информационные входы устройства сое динены с шестыми входами блоков ана

ня с выхода элемента ИЛИ 52 обнуляет 55 лиэа и вторыми входами выбора зая

210318

Устройство для управления запуском программ переходит в режим ожидания следующего запроса от освободившегося процессора

Полностью процесс распределения пакета программ по процессорам заканчивается переводом всех триггеров 60 узлов анализа приоритета в нулевое состояние.

10

5

0

5

0

5

0

0

Формула изобретения

1 о Устройство для управления запуском программ, содержащее генератор импульсов, два элемента ИЛИ, элемент И, блок управления, выходной регистр, К блоков анализа (где К - максимальное число групп программ), К блоков выбора заявок, отличающееся тем, что, с целью расширения области применения за счет учета времени решения пакета программ, в устройство введен элемент задержки, причем выход генератора импульсов соединен с входом блока управления, первый выход которого соединен с первым входом элемента И, с первым входом первого элемента ИЛИ и с входом элемента задержки, выход которого подключен к первым входам всех блоков анализа, вторые входы которых соединены с выходом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и с третьими входами блоков анализа, четвертые входы которых соединены с вторым выходом блока управления, первый выход каждого блока анализа соединен с первым входом одноименного блока выбора заявок, первый выход каждого блока выбора заявок подключен к пятому входу одноименного блока анализа, вторые выходы которых соединены с информационными входами выходного регистра, тактовый вход которого соединен с третьим выходом блока управления, группа выходов регистра подключена к входам второго элемента ИЛИ и к первой группе входов блока управления , группа выходов которого является группой выходов устройства, информационные входы устройства соединены с шестыми входами блоков ана

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления запуском программ | 1980 |

|

SU877540A1 |

| Устройство диспетчеризации электронной вычислительной машины | 1982 |

|

SU1030802A1 |

| Устройство для распределения заданий процессором | 1990 |

|

SU1705827A1 |

| Устройство для моделирования гибких производных систем | 1988 |

|

SU1631551A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство приоритета | 1984 |

|

SU1242953A1 |

| Многоканальное устройство диспетчеризации | 1989 |

|

SU1689950A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| УСТРОЙСТВО ПАКЕТНОЙ ОБРАБОТКИ ЗАПРОСОВ | 1992 |

|

RU2035065C1 |

счетчик 48 о Этим исключается из дальнейшего процесса распределения группа распределенных программ.

вок, третьи входы которых подкпюче- ны к входу сброса.устройства, четвертые входы блоков выбора заявки соеди

йены с входом запуска устройства, пятые входы блоков выбора заявок соединены с выходом элемента И, вторые выходы блоков выбора заявок соединены с входами элемента И, группа кодовых входов устройства соединена с второй группой входов блока управления ,

2 о Устройство по п. 1, отличающееся тем, что блок управления содержит группу блоков элементов И, два элемента И, элемент ИЛИ, элемент НЕ, группу элементов И, группу элементов ИЛИ, дешифратор, счетчик, генератор импульсов, причем группа выходов блока соединена с выходами блоков элементов И группы, информационные входы которых соединены с первой группой входов блока, червый выход которого соединен г вы-

25

26 21 28

29 ЬО

0

5

0

ходом первого элемента И, первый вход которого соединен с первым входом блока, второй вход первого элемента И подключен к входу элемента НЕ и к выходу элемента ИЛИ, входы которого соединены с управляющими входами блоков элементов И группы, с выходами элементов И группы и с входами элементов ИЛИ, группы выходов которых соединены с вторым выходом блока управления, третий выход блока соединен с выходом элемента НЕ и с первым входом второго элемента И, второй вход которого соединен с выходом генератора импульсов, выход второго элемента И соединен со сметным входом счетчика, выходы которого соединены с входами дешифратора, выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с второй группой входов блока0

.2

31

3§40 41 4L

Фм.З

53

55 46

41

56 51 58 Фиг .4

45

54

48

г

59

z

А

51

/

8

65

64 65,

65,

65f

67

68

66

Фиг. 5

| Устройство для управления запуском программ | 1972 |

|

SU468240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1991-01-15—Публикация

1989-01-19—Подача