ел С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетей систем массового обслуживания | 1990 |

|

SU1758652A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1552196A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| Устройство для сбора и анализа данных о работе информационно-вычислительной системы | 1990 |

|

SU1795476A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1702386A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1223244A1 |

| Устройство для моделирования систем "человек-машина | 1983 |

|

SU1088005A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

Изобретение относится к вычислительной технике и может найти применение в ЭВМ для динамического управления распределением производительности на основе адаптации к условиям внешней среды. Целью изобретения является расширение области применения устройства за счет возможности адаптивно изменять приоритеты потоков заявок на основе потребных ресурсов ЭВМ. В устройство введены счетчик 28, а в каждый канал - второй счетчик 3, пять регистров 4,8,9,11,12,14, второй сумматор 7, блок элементов запрета 8, блок умножения 10, пять элементов задержки 15-19. Использование устройства позволит повысить качество распределения производительности ЭВМ при изменяющихся интенсивно- стях потоков. 1 ил.

Изобретение относится к вычислительной технике и может найти применение в ЭВМ для динамического управления распределением производительности на основе адаптации к условиям внешней среды.

Известно устройство для распределения заданий процессорам, содержащее блок памяти, элементы ИЛЙ-НЕ. блок перебора перестановок, элементы памяти и дешифратор. Недостатком этого устройства является то, что в нем не может производиться динамическое распределение запросов между процессорами с учетом их загруженности.,

Наиболее близким к изобретению является устройство для распределения заданий процессорам, содержащее формирователь импульсов, два триггера. Два элемента задержки, группу блоков элементов И. блок регистров, дешифратор, блок элементов ИЛИ, группу сумматоров, генератор импульсов, элемент И, элемент ИЛИ-НЕ, элемент ИЛИ, группу выходных триггеров.

Это устройство позволяет распределять задания процессором с учетом выполнимости директивных сроков. Недостатком устройства является невозможность его использования для адаптивного изменения приоритетов потокам заявок на основе потребных ресурсов ЭВМ.

Цель изобретения - расширение области применения устройства за счет возможности адаптивно изменять приоритеты потокам заявок на основе потребных ресурсов ЭВМ.

Поставленная цель достигается тем, что в устройство для распределения заданий процессорам, содержащее каналы, каждый из которых включает первый регистр; первый счетчик, первый сумматор, а также триггер, генератор импульсов, первый элемент И, первый элемент ИЛИ. три элемента задержки, причем выход генератора импульVJ

О

ел

00

N3 vj

сов подключен к первому входу элемента И, второй вход которого подключен к выходу триггера, а выход - к счетным входам первого счетчика каналов, выход первого элемента задержки подключен через второй элемент задержки к единичному входу триггера, введены - счетчик, а в каждый канал - второй счетчик, пять регистров, второй сумматор, блок элементов запрета, блок умножения, пять элементов задержки, причем вход адаптивного управления устройства подключен к входам записи первых регистров каналов и к входу первого элемента задержки, выход которого подключен к входам разрешения записи первых счетчиков всех каналов и к входу третьего элемента задержки, выход которого подключен к входам обнуления счетчика, триггера и к входам обнуления первых и вторых сумматоров и блоков умножения каналов, выход первого элемента задержки J -ro 0 1 ,.... п; п - число каналов) канала подключен к j-му входу элемента ИЛИ, выход которого подключен к счетному входу счетчика, выход которого подключен к информационным входам вторых регистров всех каналов, а в каждом канале счетный вход второго счетчика является информационным входом устройства, выход второго счетчика подключен к информационному входу третьего регистра, выход которого подключен к информационному входу первого регистра, к первым информационным входам первого и второго сумматоров, второй информационный вход первого сумматора подключен к выходу первого регистра, а выход к второму информационному входу второго сумматора, первый и второй выходы которого подключены к соответствующим входам блока элементов запрета, выход которого подключен к информационному входу четвертого регистра, выход которого подключен к первому входу блока умножения, второй вход которого подключен к выходу пятого регистра, а выход к информационному входу шестого регистра, выход которого подключен к информационному входу первого счетчика, выход переполнения которого подключен к входу первого элемента задержки и к входу разрешения записи второго регистра, выход которого является выходом устройства, вход адаптивного управления устройства соединен с входом управления записью первого регистра и через второй элемент задержки к входу управления записью третьего регистра, выход второго элемента задержки через третий элемент задержки подключен к входу обнуления второго счетчика, а через четвертый элемент задержки к входу управления записью четвертого регистра и к входу пятого элемента задержки, выход которого подключен к входу управления записью шестого регистра.

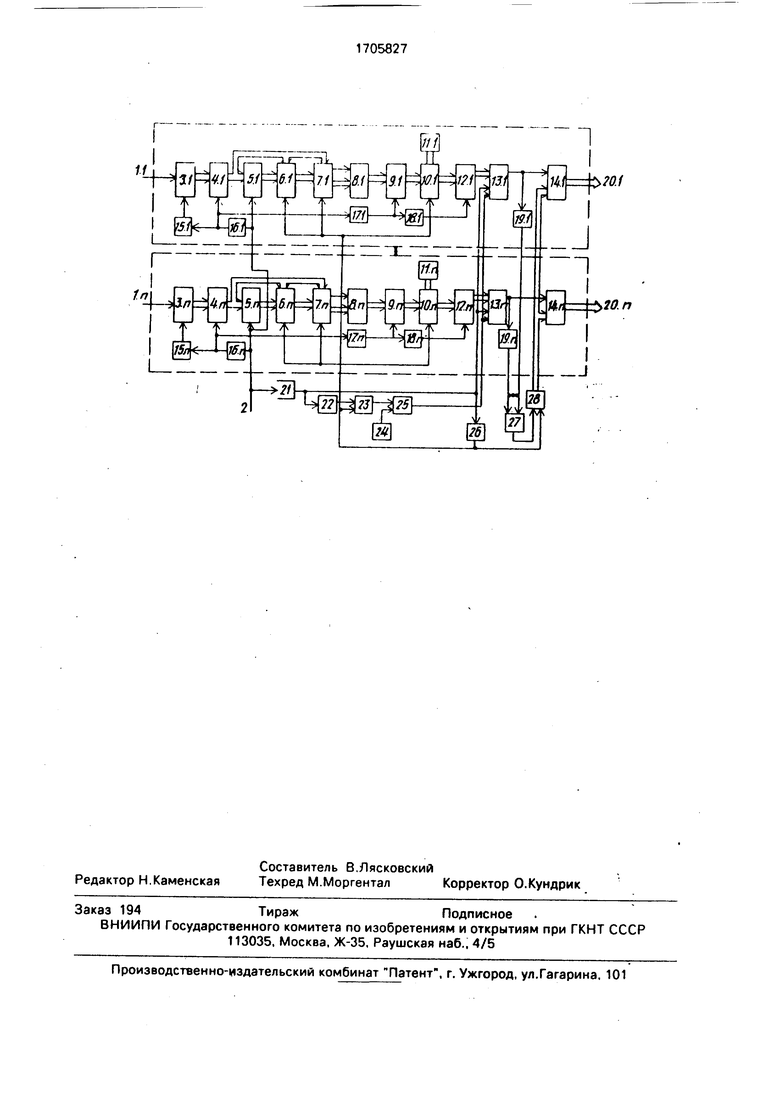

Структурная схема устройства приведена на чертеже.

Устройство содержит группу входов 1.1 -1.п вход управления 2,п каналов, каждый из которых включает счетчик 3, регистры 4,5, сумматоры 6, 7, блок элементов запрета 8,

0 регистр 9, блок умножения 10, регистры 11, 12 счетчик 13, регистр 14, элементы задержки 15-19, кроме того устройство содержит группу выходов 20.1-20.п, элементы задержки 21, 22, триггер 23, генератор импульсов

5 24, элемент И 25, элемент задержки 26, элемент ИЛИ 27, счетчик 28.

Устройство работает следующим образом.

В исходном состоянии, когда в систему

0 не поступают заявки на обслуживание, все счетчики, сумматоры, регистры 4,5,9.12,14.. триггер обнулены. В регистре 11.к записан код среднего времени обслуживания в системе заявки из k-го потока г (k 1,п).

5При появлении заявки k-ro типа в системе, импульс поступает на вход 1 .k устройства. На вход 2 устройства импульсы подаются через период адаптации, который задается заранее. Таким образом, в счетчи0 ках 3 каналов на момент сигнала адаптивного управления, поступающего по входу 2, содержится число заявок соответствующего типа, поступивших за данный интервал обслуживания.

5 Рассмотрим работу устройства при поступлении импульса по входу 2 на примере первого канала, так как работа остальных каналов аналогична.

Импульс со входа 2 поступает на входы

0 регистров 5 и элементов задержки 16 каналов, а также на вход элемента задержки 21 устройства. По сигналу разрешения записи на регистр 5.1 содержимое регистра 4.1, в котором записан код числа заявок первого

5 типа, поступивших за предыдущий период адаптации (очевидно, что для первого периода в регистрах 4.1 нулевой код), переписывается на регистр 5.1.

Импульс, задерживаясь в элементе

0 16.1, поступает на вход разрешения записи регистра 4,1 и разрешает перепись содержимого счетчика 3.1, в котором записано число заявок первого типа, поступивших за данный период адаптации, на регистр 4.1.

5 Также импульс с элемента 16.1 через элемент задержки 15.1 поступает на вход обнуления счетчика 3.1 и на вход элемента задержки 17.1. Выходы регистра 5,1 так подключены к входу сумматора 6.1, что на последний поступает обратный код числа,

записанного в регистре 5.1. На второй вход сумматора 6.1 поступает прямой код числа, записанного в регистре 4.1. Таким образом, в сумматоре 6.1 производится операция вычитания от числа заявок первого типа, по- ступивших в данном цикле, числа заявок этого же типа, поступивших в предыдущем цикле управления ДМ NI 1 этом возможно получение как положительного так и отрицательного результата ДМгл Этот результат поступает на первый вход сумматора 7.1, на второй вход которого поступает код числа Mr Таким образом, на сумматоре 7.1 производится операция.

KlP) + ДмК еслиМ мРН

N01 {

) - Дм(и иначе.

/«

Ni+r также может быть как положительным, так и отрицательным. Знаковый разряд сумматора 7.1 является управляющим сигналом для блока элементов запрета 8.1. Если Nn-г1 0, то значение знакового разряда сумматора 7.1 равно 0 и код NJ+I поступает на информационный вход регистра 9.1. в противном случае на этот вход поступает нулевой код. Импульс, задержанный в элементе 17,1 на время выполнения операций в сумматорах 6.1. 7.1, поступает на вход разрешения записи регистра 9.1, а также на вход элемента задержки 18.1. В блоке умножения 10.1 производится вычисление прогнозируемой загрузки ЭВМ перпеЗм -М-м тГО.

вым потоком по формуле Импульс, задержанный в элементе 18.1 на время выполнения операции умножения, поступает на вход разрешения записи регистра 12.1.

Таким образом, в регистрах 12 каналов формируются значения Si-н . Импульс со входа 2, задержанный в элементе 21 на время формирования значений . поступает на входы разрешения записи счетчиков 13 каналов, а также, через элемент задерж- ки 22, на вход установки триггера 23 в единичное состояние. Высокий потенциал с единичного выхода триггера 23 поступает на первый вход элемента И 25 и разрешает прохождение импульсов с генератора 24 на счетные входы счетчиков 13 каналов. При этом первым переполнится тот канал, код прогнозируемой загрузки которого больше. Импульс с выхода переполнения данного счетчика поступает на вход разрешения записи регистра 14.канала. Код счетчика 28 перепишется в регистр 14 канала. Импульс с выхода счетчика 13 канала, проходя через элемент задержки 19 канала и элемент ИЛИ

5 0

5

0

5

0

5

0

0-

5

27, поступает на счетный вход счетчика 28, увеличивая его состояние на единицу. Запись в регистры 14 других каналов будет производиться аналогичным образом в порядке возрастания кодов в регистрах 12 соответствующих каналов.Таким образом, на выходах устройства 20.1-20.п будут записаны коды приоритетов потоков заявок на рассматриваемый период обслуживания. Меньший код соответствует большому приоритету. Следует заметить, что на ряде выходов 20.1-20.П коды могут совпадать. В этом случае соответствующие потоки имеют одинаковый приоритет. Импульс, задержанный в элементе 26 на время назначения приоритетов потоком (время на переполнение счетчиков 14) обнуляет сумматоры 16,7, блоки умножения 10 каналов, триггер 23, счетчик 28, приводя устройство в исходное состояние.

Работа устройства в последующих циклах управления приоритетами аналогична вышеописанной.

Применение устройства позволяет повысить, качество распределения производительности ЭВМ при изменяющихся интенсивностях потоков.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее каналы, каждый из которых включает первый регистр, первый счетчик, первый сумматор, а также триггер, генератор импульсов, первый элемент И, первый элемент ИЛИ, три элемента задержки, причем выход генератора импульсов подключен к первому входу элемента И, второй вход которого подключен к выходу триггера, а выход - к счетным входам первых счетчиков каналов, выход первого элемента задержки подключен через второй элемент задержки к единичному входу триггера, отличающееся тем, что, с целью расширения области применения за счет возможности адаптивно изменять приоритеты потокам заявок на основе потребных ресурсов ЭВМ, оно дополнительно содержит счетчик, а каждый канал - второй счетчик, пять регистров, второй сумматор, блок элементов запрета, блок умножения, пять элементов задержки, причем вход адаптивного управления устройства подключен к входам разрешения записи первых регистров каналов и к входу первого элемента задержки, выход которого подключен к входам разрешения записи первых счетчиков всех каналов и к входу третьего элемента задержки, выход которого подключен к входам обнуления счетчика, триггера и к входам обнуления первых и вторых сумматоров и блоков умножения каналов, выход

первого элемента задержки J-ro Q - 1 ...n, n - число каналов) канала подключен к )-му входу элемента ИЛИ, выход которого подключен к счетному входу счетчика, выход которого подключен к информационным входам вторых регистров всех каналов, в каждом канале счетный вход второго счетчика является информационным входом устройства, выход второго счетчика подключен к информационному входу третьего регистра, выход которого подключен к информационному входу первого регистра и к первым информационным входам первого и второго сумматоров, второй информационный вход первого сумматора подключен к выходу первого регистра, а выход - к второму информационному входу второго сумматора, первый и второй выходы которого подключены к соответствующим входам блока элементов запрета, выход которого подключен к информационному входу четвертого регистра, выход которого подключен к первому входу блока умножения, второй вход которого подключен к выходу пятого регистра, а выход - к информационному входу шестого регистра, выход которого подключен к информационному входу первого счетчика, выход переполнения которого подключен к входу первого элемента задержки и к входу разрешения записи второго регистра, выход которого является выходом устройства.

вход адаптивного управления устройства соединен с входом управления записью первого регистра и через второй элемент задержки к входу управления записью третьего регистра, выход второго элемента

задержки через третий элемент задержки подключен к входу обнуления второго счетчика, а через четвертый элемент задержки - к входу управления записью четвертого регистра и к входу пятого элемента задержки,

выход которого подключен к входу управления записью шестого регистра.

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1619273A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-15—Публикация

1990-02-05—Подача