(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЗАПУСКОМ

I

Устройство относится к вычислительной технике и может быть использовано в однородных мультипроцессорных вычислительных системах (МВС) для управления запуском пакетов программ, имеющих между собой информационные связи.

Известно устройство для управления запуском программ, содержащее злеменТЬ1 ИЛИ, группы триггеров очередности, элементы И записи и: вьщачи, распределители импульсов, шифратор и регистр

D.

Устройство позволяет организовать запуск программ, не имеющих информационных связей, в ВС в порядке поступления запросов на их реализацию, однакр не учитьшает приоритета запросов и не позволяет организовать запуск программ, имеющих информационные связи.

Наиболее близким по техническому решению к предлагаемому является приоритетное устройство, содержащее блок управления, генератор импульсов, перПРОГРАММ

вый элеменТ ИЛИ, п-разрядный регистр заявок, п-разрядный выходной регистр, k Логических блоков, группу элементов И 2.

Известное устройство позволяет организовать приоритетную обработку запросов на включение прбграмм, однако не обеспечивает запуск программ, имеющих.информационшчш связи, и, кроме того, при вьфаботке решения не учи10тывает временные характеристики реализуемых программ, что приводит к неэффективному использованию машинного времени в многопроцессорных ВС.

Цель изобретения - расширение

15 функциональных возможностей устройства за счет обеспечения автоматического выбора для запуска программы из пакета одновременно реализуемых на многопроцессорной ВС программ, имею20щих информационные связи.

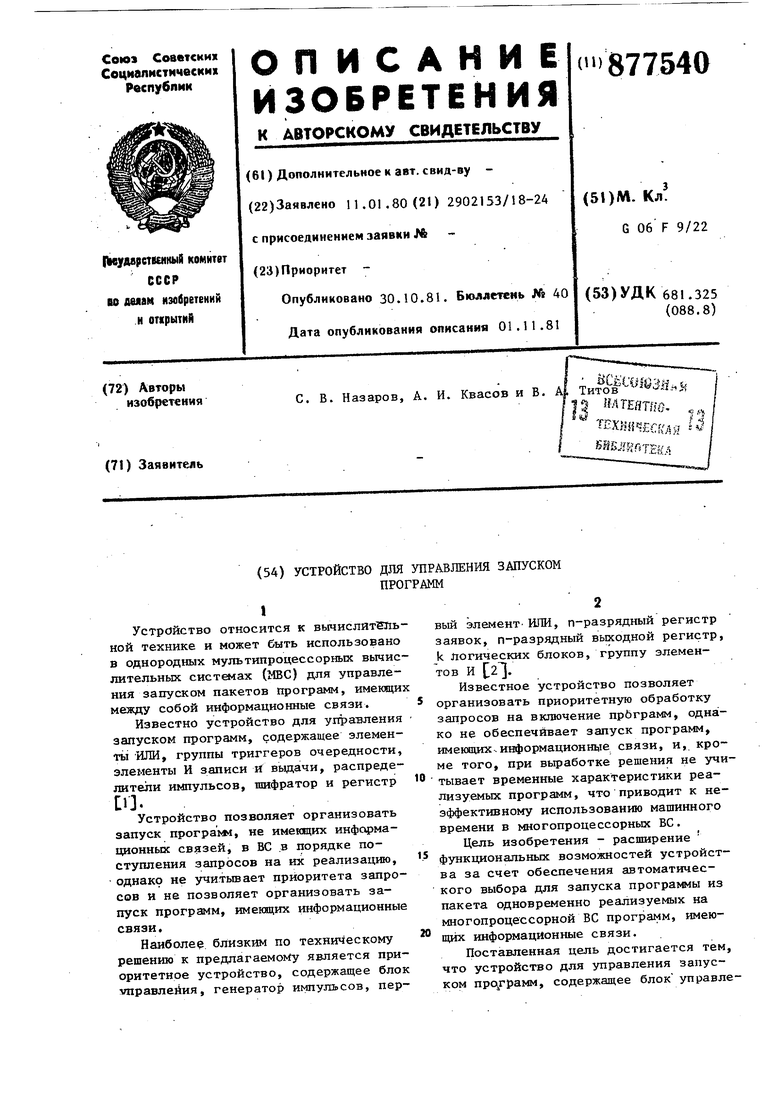

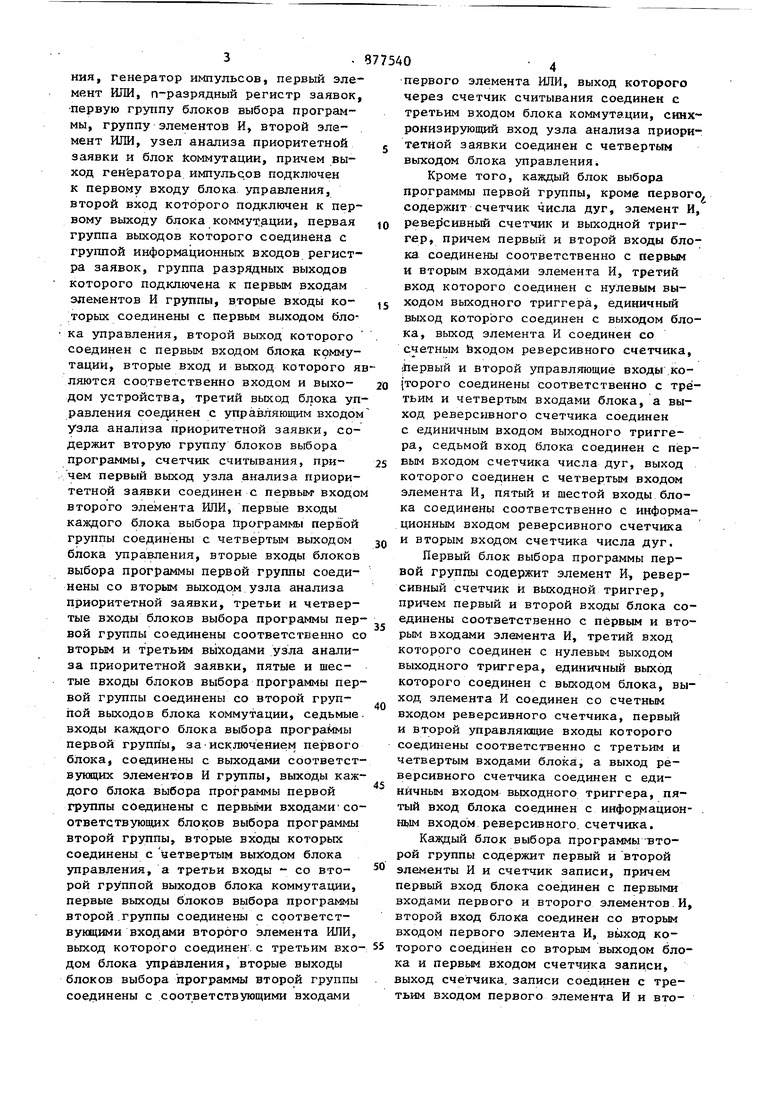

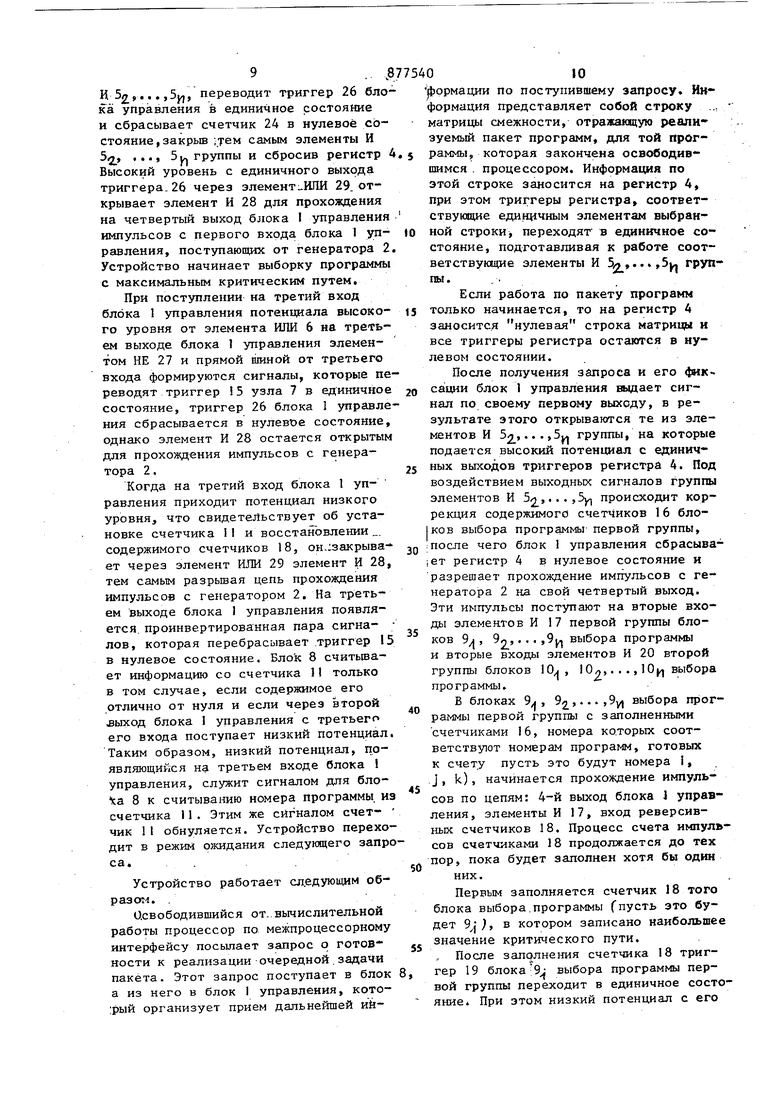

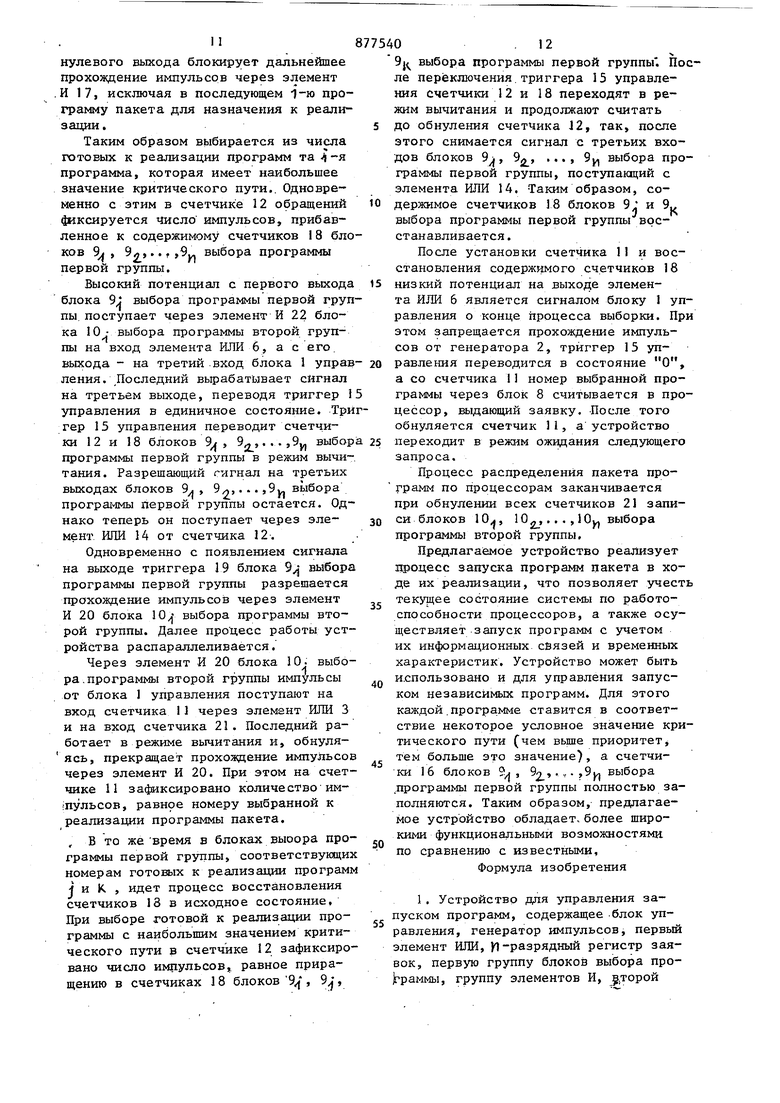

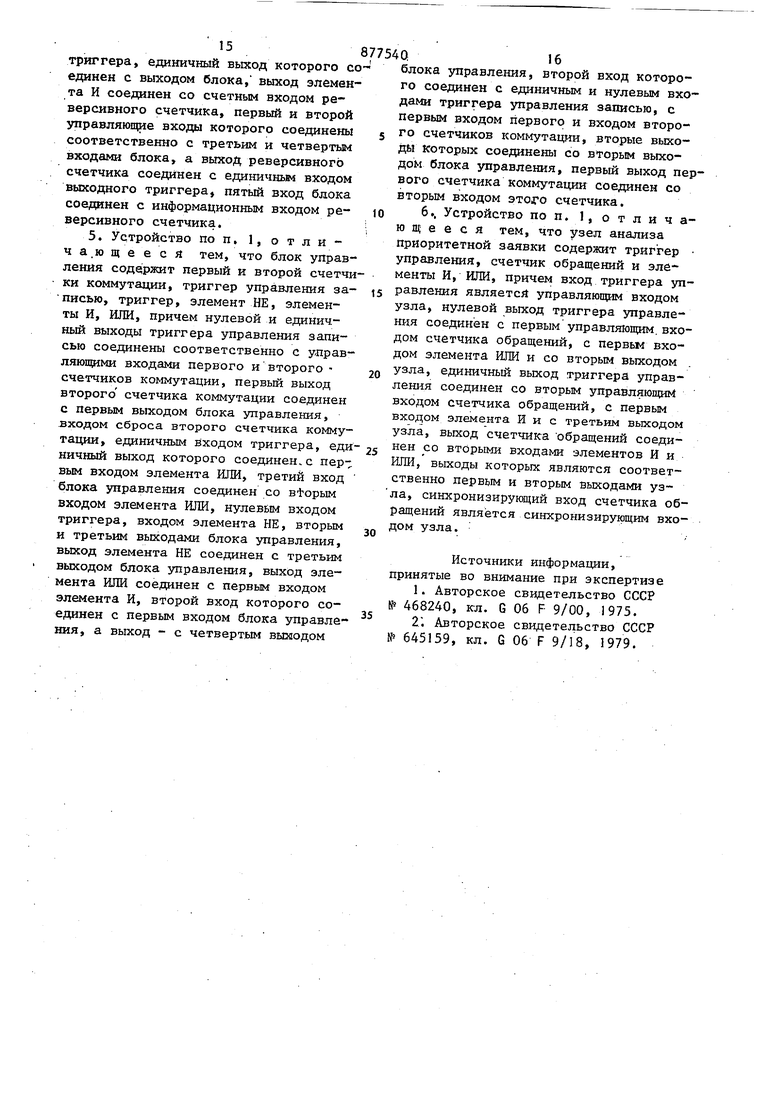

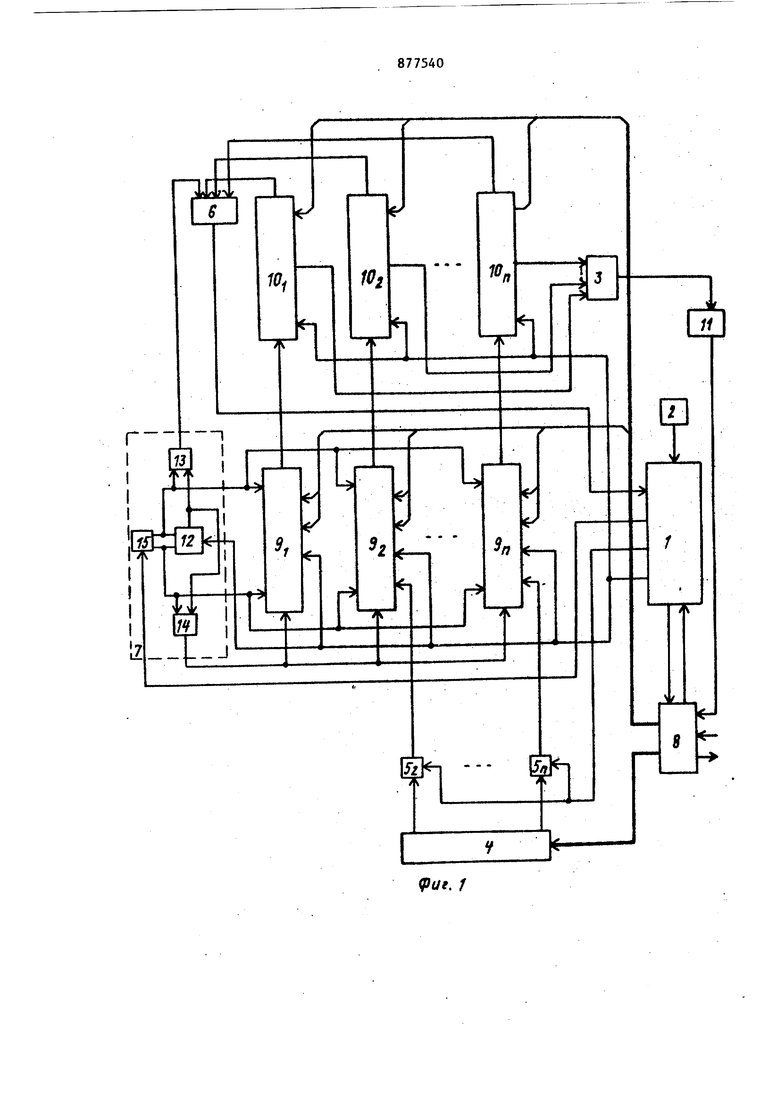

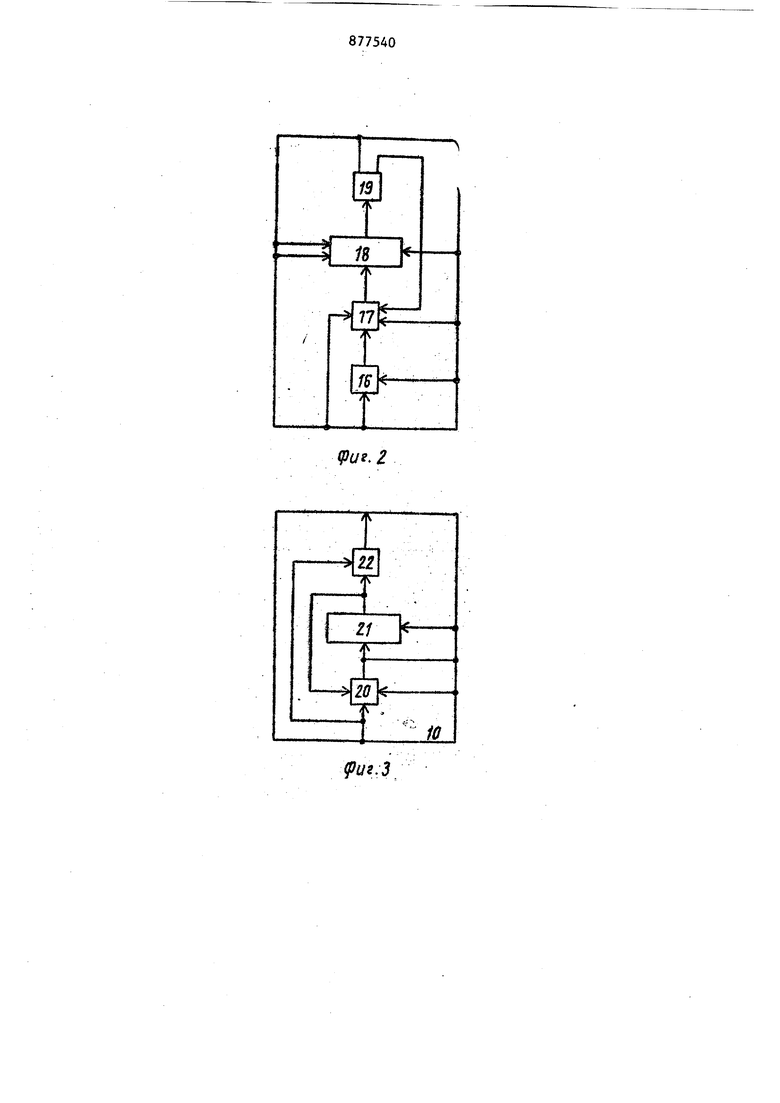

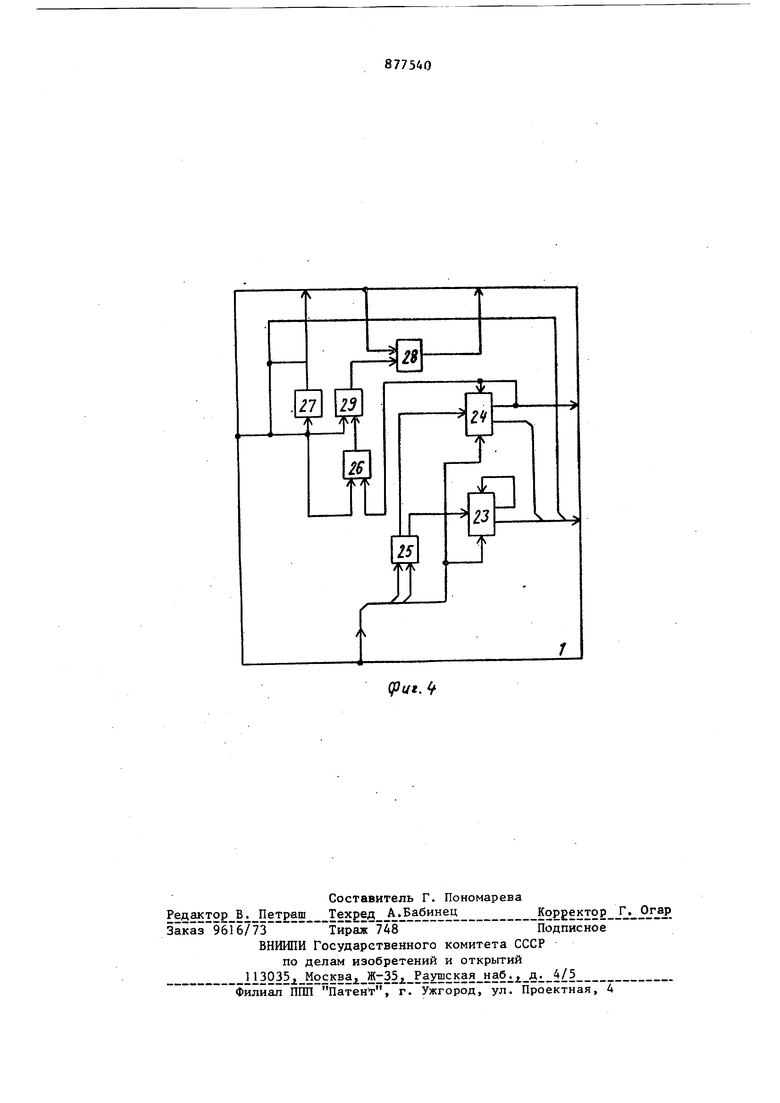

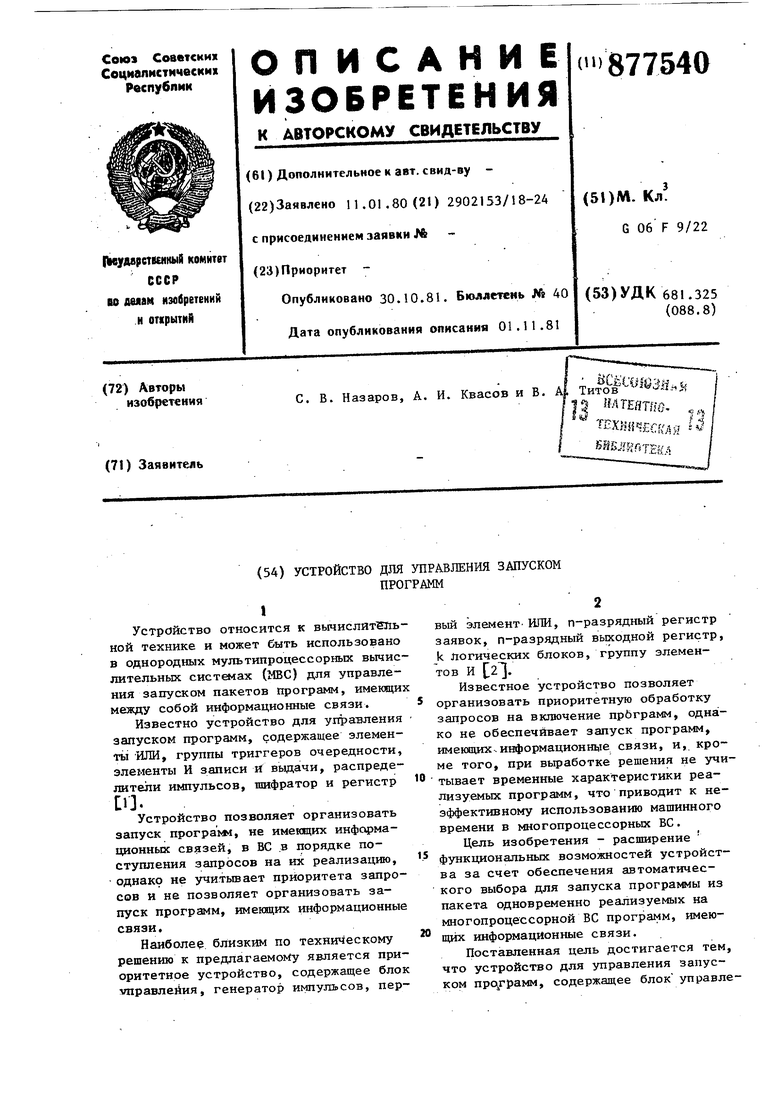

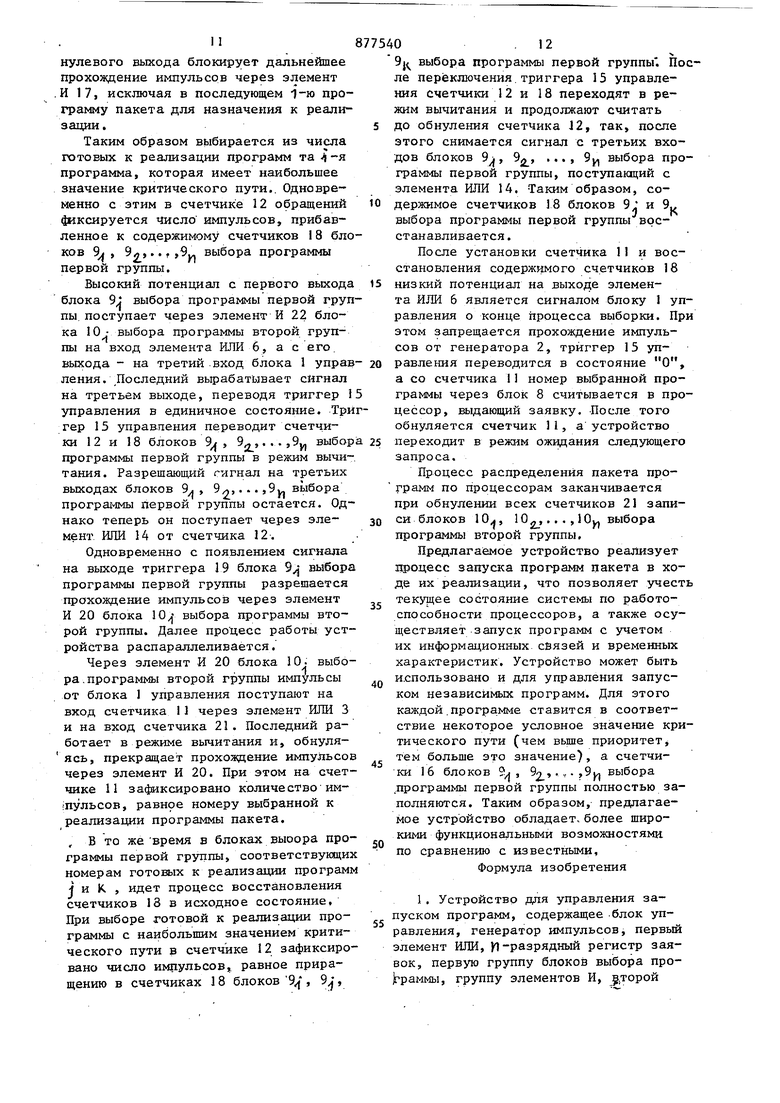

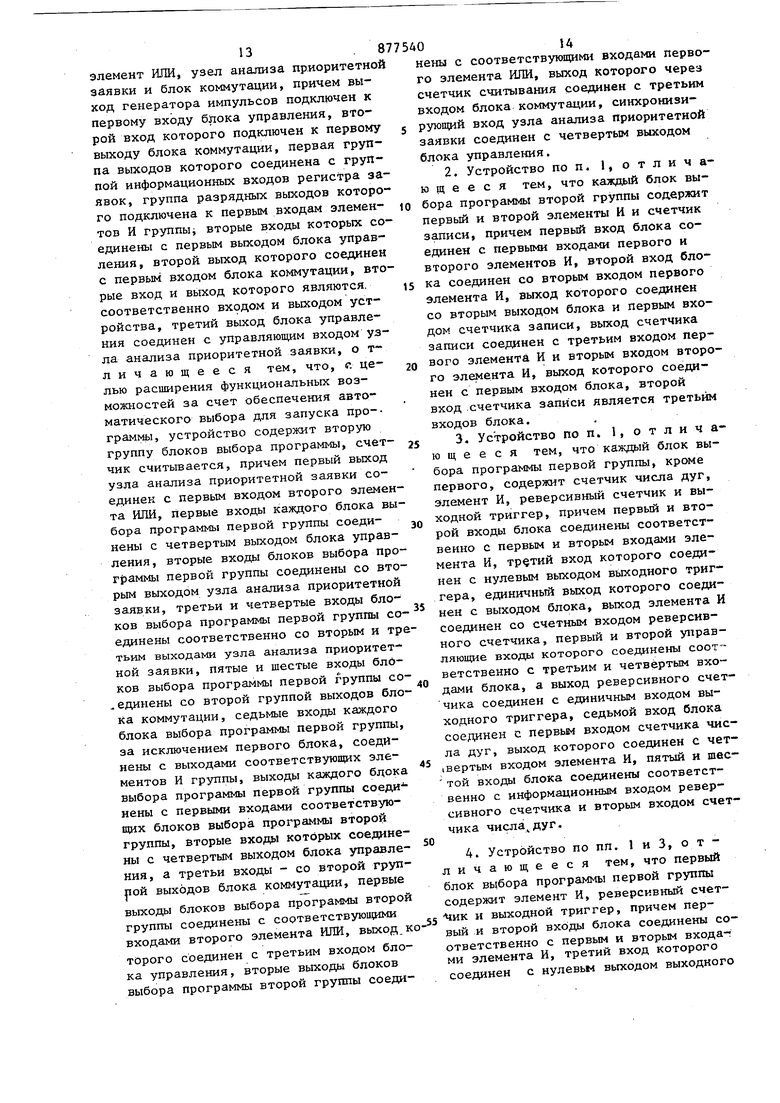

Поставленная цель достигается тем, что устройство для управления запуском про.грамм, содержащее блок управления, генератор импульсов, первьш элемент ИЛИ, п-разрядный регистр заявок, первую группу блоков выбора программы, группу элементов И, второй элемент ИЛИ, узел анализа приоритетной заявки и блок {соммутации, причем выход генератора. импульсов подключен к первому входу блока управления, второй вход которого подключен к первому выходу блока коммутации, первая группа выходов которого соединена с группой информационных входов регистра заявок, группа разрядных выходов которого подключена к первьм входам элементов И группы, вторые входы которых соединены с первым выходом бло ка управления, второй выход которого соединен с первым входом блока крммутации, вторые вход и выход которого я ляются соответственно входом и выходом устройства, третий выход блока уп равления соединен с управляющим входом узла анализа приоритетной заявки, содержит вторую группу блоков выбора программы, счетчик считывания, причем первый выход узла анализа приоритетной заявки соединен с первым- входо второго элемента ИЛИ, первые входы каждого блока выбора программы первой группы соединены с четвертым выходом блока управления, вторые входы блоков выбора программы первой группы соединены со вторым выходом узла анализа приоритетной заявки, третьи и четвертые входы блоков выбора программы пер вой группы соединены соответственно с вторым и третьим выходами узла анализа приоритетной заявки, пятые и шестые входы блоков выбора программы пер вой группы соединены со второй группой вьгходов блока коммутации, седьмые входы каждого блока выбора программы первой группы, за иск;лючением первого блока, соединены с выходами соответст вукнцих элементов И группы, выходы каж дого блока выбора программы первой группы соединены с первыми входамисо ответствующих блоков выбора программы второй группы, вторые входы которых соединены с четвертым блока управления, а третьи входы - со второй группой выходов блока коммутации, первые выходы блоков выбора программы второй .группы соединены с соответствугацими входами второго элемента ИЛИ, выход которого соединен , с третьим вхо дом блока управления, вторые выходы блоков выбора программы второй группы соединены с соответствующими входами 0 первого элемента ИЛИ, выход которого через счетчик считывания соединен с третьим входом блока коммутации, синхронизирующий вход узла анализа приоритетной заявки соединен с четвертым выходом блока управления. Кроме того, каждый блок выбора программы первой группы, кроме первого. содерж11т счетчик числа дуг, элемент И, реверсивный счетчик и выходной триггер, причем первый и второй входы блока соединены соответственно с первым и вторым входами элемен.та И, третий вход которого соединен с нулевым выходом выходного триггера, единичный выход которого соединен с выходом блока, выход элемента И соединен со счетным йходом реверсивного счетчика, первый и второй управляющие входы .коJToporo соединены соответственно с третьим и четвертым входами блока, а выход реверсивного счетчика соединен с единичным входом выходного триггера, седьмой вход блока соединен с первым входом счетчика числа дуг, выход которого соединен с четвертым входом элемента И, пятый и шестой входы блока соединены соответственно с информационным входом реверсивного счетчика и вторым входом счетчика числа дуг. Первый блок выбора программы первой группы содержит элемент И, реверсивный счетчик и выходной триггер, причем первый и второй входы блока соединены соответственно с первым и вторым входами элемента И, третий вход которого соединен с нулевым выходом выходного триггера, единичный выход которого соединен с выходом блока, выход элемента И соединен со счетным входом реверсивного счетчика, первый и второй управляюцие входы которого соединены соответственно с третьим и четвертым входами блока, а выход реверсивного счетчика соединен с единичным входом вькодного триггера, пятый вход блока соединен с информацион- . ным входом реверсивно.го. счетчика. Каждый блок выбора программы -второй группы содержит первый и второй элементы И и счетчик записи, причем первый вход блока соединен с первыми входами первого и второго элементов И, второй вход блока соединен со вторым входом первого элемента И, выход которого соединен со вторым выходом блока и первым входом счетчика записи, выход счетчика, записи соединен с третьим входом первого элемента И и вторым входом второго элемента И, выход которого соединен с первъм входом блока, второй вход счетчика записи является третьим входом блока. Блок- управления содержит первый и второй счетчики коммутации, триггер, управления записью, триггер, элемент НЕ, элементы И, ШТИ, причем нулевой и единичный выходы триггера управления записью соединены соответствейно с управляющими, входами первого и второго счетчиков коммутации, первый выход второго счетчика коммутации соединен с первым выходом блока управ ления, входом сброса второго счетчика коммутации, единичным входом триггера, единичный выход которого соединен с первым входом элемента ШТИ, . третий вход блока управления соединен со вторым входом элемента ИЛИ, нулевым входом триггера, вхрдом элемента НЕ, вторым и третьимвыходами управления, выход элемента НЕ соединен с третьим выходом блока управления, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого соединен с первым входом блока управления, а выход - с четвертым вькодом блока управления, второй вход которого соединен с единичным и нулевым входами триггера управления записью, с первым входом первого и входом второго счетчиков коммутации, вторые выходы которых соединены со вторым выходом блока управления, первый выход первого счетчика коммутации соеди нен со вторым входом этого счетчика. Узел анализа приоритетной заявки содержит триггер управления, счетчик обращений и элементы И, ИЛИ, причём вход триггера управления является управляющим входом узла, нулевой вькод триггера управления соединен с первым управляющим входом счетчика обращений ,с первым входом элемента ИЛИ и со вторым выходом узла, единичный выход , триггера управления соединен со вторьм управляющим входом счетчика обращений, с первь1м входом элемента Икс третьим выходом узла, выход счетчика обращений соединен со вторьнда входами элементов И и ИЛИ, выходы которых являются соответственно первым и вторым выходами узла, синхронизирующий вход счетчика .обращений является .синхронизи рующим входом узла. . В основу работы данного устройства положен принцип составления плана. реализации информационно связанного набора программ с учетом их приоритета. При этом приоритет кавдой программы определяется величиной критического nyTHj. в графе, представляющем структуру, пакета программ по правилу: чем больше величина критического пути от вершины графа, соответствукщей данной программе, до конечной вершины, тем выше ее приоритет. На фиг 4 1 приведена структурная схема устройства для управления запуском программ; на фиг. 2 - функциональная схема блока выбора программы первой группы; на фиг. 3 - функциональная схема блока выбора программы второй группы:} на фиг. А - функциональная схема блока управления. Устройство содержит блок 1 управления генератор 2 импульсов, первый элемент ИЛИ 3, И-разрядный регистр 4 заявок, группу элементов ИЗ-, 5,,..., 5и, второй элемент ИЛИ 6, узел 7 анализа приоритетной заявки, блок.8 коммутации, первая группа блоков 9 , 1 «. выбора программы, вторая группа блоков 10,;j, Ю,..., Ю) выбора программы, счетчик 11 считывания, Узел 7 содержит счетчик 12 обращений, элемент И 13, элемент ИЛИ 14, триггер 15 управления. Блок 9 выбора программы первой группы содержит счетчик 16 числа дуг, элемент И 17, реверсивный счетчик 18, выходной триггер 19. Блок 10 выбора программы второй группы содержит первый элемент И 20, счетчик 21 записи, второй элемент И 22, Перед началом решения пакета программ с .информационными связями по междупроцессорному интерфейсу от центрального процессора МВС в устройство со второй группы выходов блока 8 под управлением блока 1 управления заносится исходная информация в счетчи 21 записи, реверсивные счетчики 18 и счетчики 16 числа дуг. В счетчики 21 записи, работающие как вычитаклцие, заносятся номера программ пакета в соответствии с номерами логических путей для соответствующих программ пакета, представляемого ориентированньм взвешенным графом, в котором веса вершин равны временамреализации программ; в счетчики 16 числа дуг заносятся значения, дополнения которых до полной емкости счетчиков равны количеству дуг, входящих в вершину, представляющую соответствующую программу пакета. Кроме того, перед, а чалом работы все триггеры устройства, счетчики II я 12 и регистр 4 устанавливаются в н левое состояние (цепи сброса от блока 1 управления к этим элементам на фиг. 1 не показаны). После записи исходной информации на выходе счётчиков J6 числа дуг, за полненных до полной емкости, устанав ливаются вщсокие отенциалы. Номера блоков 9 (1 « 1,п) выбора программы первой.группы; включающих эти счет, чики, соотве А-вуют номерам программ пакета, которые готовы к счету Гвер пины графа, соответствующие этим про граммам, не имеют входных дуг). Считается, что программа пакета, имеющая номер 1, всегда готова к счету. Информация о структуре графа, представляющего пакет реализуемых програм в виде матрицы смежности и весов вершин графа хранится в памяти МВС. Содержимое счетчиков 18 первой .группы блоков 9 после занесения исходной информации таково, что на их Выходах действует низкий потенциал, т,е. счетчики не заполнены (их емкость выбирается большей возможного максимального значения критического )пути в пакетах реализуемых программ Поэтому на выходах блоков 9 первой группы действует низкий потенциал, а на четвертых входах элементов И 17 действует высокий потенциал. На выходах счетчиков 21 записи блоков 10 второй группы действуют высокие потенциалы ( низкие потенциалы только у счетвиков с нулевым содержанием) , которые по одному входу подготавливают к работе элементы И 22. Триггер 15 управления находится в нулевом состоянии и своим высокий потенциалом с нулевого выхода настра ивает счетчик 2 обращений и счетчики 18 блоков 9 выбора программы первой группы к работе на сложение. Высокий потенциал на нулевом выходе тр гера 15 управления через элемент ИЛИ подготавливает к работе по третьему входу элемент И I7 первой группы бло КОВ У: ,.,. ,9 выбора программы через 9. их третьи .входы. Блок 1 управления содержит первый счетчик 23 коммутации, второй счетчик 24 коммутации, триггер .25 управл ния записью, триггер 26, элемент НЕ элемент И 28, элемент ИЛИ 29, Блок управления работает следующим образом. Перед началом решения пакета программ блок 1 зшравления управляет занесением исходной информации в устройство. С блока 8 на второй вход блока I управления поступает сигнал, который переводит триггер 25 в нулевое состояние. Сигнал высокого уровня с нулевого выхода триггера 25 открывает для счетных импульсов счетчик коммутации 23, сигнал низкого уровня на первом входе счетчика 24 запирает его для счетных импульсов. С первого выхода блока 8 через второйг вход блока управления на третьи входы счетчиков 23 и 24 начинают поступать счетные импульсы, каждый из которых является синхронизирующим к бай ту информации, поступающему на второй вход блока коммутации 8 из межпроцессорного интерфейса. Значение номера поступающего байта информации со второго выхода счетчика 23 через второй выход блока управления поступает в блок 8, где производится дешифрация этого номера для выбора линий связи передачи, поступившей из интерфейса информации. Когда вся исходная информация занесена в устройство, первый счетчик 23 переполняется. С Первого выхода счетчика 23 сигнал высокого уровня поступит на второй вход счет чика 23, сбрасывая его в нулевое cov стояние. Блок управления работу по приведению устройства в исходное со.утояние заканчивает. Устройство переходит в режим ожидания запроса на про грамму от освободившегося процессора. При поступлении запроса от процессора сигнал со второго входа блока 1 управления переводит триггер 25 в единичное Состояние, тем самым подготавливая к работе счетчик 24 и выключая счетчик 23, Занесение информации о строке матрицы из общей оперативной памяти через интерфейс в регистр 4 сопровождается также побайтной синхровдЕзацией, Синхроимпульсы с блока 8 через второй вход блока I управления .поступают на третий счетный вход второго счетчика 24,В блоке 8 происходит дешифрация сигнала, поступаклцвго со второго выхода блока управления. При полном заполнении регистра 4 информацией счетчик 24 переполняется. С первого выхода второго счетчика 24 вырабатывается высокий потенциал, который поступает на первый вход блока 1 управления, открывает группу элементов 9. И 52,... ,5j, переводит триггер 26 бло ка управления в единичное состояние и сбрасывает счетчик 24 в нулевое состояние , закрью ;тем самым элементы И 5, ,.., группы и сбросив регистр Высокий уровень с единичного выхода триггера.26 через элемент-ИЛИ 29. открывает элемент И 28 для прохождения на четвертый выход блока I управления импульсов с первого входа блока 1 управления, поступающих от генератора 2 Устройство начинает выборку программы с максимальным критическим путем. При поступлении на третий вход блока 1 управления потенциала высокого уровня от элемента ИЛИ 6 на третьем выходе блока 1 управления элемен том НЕ 27 и прямой шиной от третьего входа формируются сигналы, которые пе реводят триггер 5 узла 7 в единичное состояние, триггер 26 блока 1 управле ния сбрасывается в нулевое состояние однако элемент И 28 остается открытым для прохождения импульсов с генератора 2. Когда на третий вход блока 1 управления приходит потенциал низкого уровня, что свидетельствует об установке счетчика 1 1 и восстановлении „. содержимого счетчиков 18, он.:закрывает через элемент ИЛИ 29 элемент И 28 тем самым разрьшая цепь прохождения импульсов с генератором 2. На третьем выходе блока 1 управления появляется, проинвертированная пара сигналов, которая перебрасывает .триггер 15 в нулевое состояние. Блок 8 считьюает информацию со счетчика 1 только в том случае, если содержимое его отлично от нуля и если через второй эыход блока I управления с третьего его входа поступает низкий потенциал Таким образом, низкий потенциал, появляющийся на третьем входе блока управления, служит сигналом для блоsa 8 к считыванию номера программы, и счетчика 11. Этим же сигналом счетчик 11 обнуляется. Устройство перехо дит в режим ожидания следующего запро са. . Устройство работает следующим образом . . Освободившийся от..вьиислительной работы процессор по межпроцессорному интерфейсу посылает запрос о готоВ ности к реализации очередной.задачи пакета. Этот запрос поступает в блок а из него в блок 1 управления, кото:рый организует прием дальнейшей ий010| ррмации по поступившему запросу. Информация представляет собой строку матрицы смежности, отражакщум реализуемый пакет программ, для той программы, которая закончена освободив шимся процессором. Информация по этой строке заносится на регистр 4, при этом триггеры регистра, соответствующие единичным элементам выбранной строки, переходят в единичное состояние, подготавливая к работе соот ветствуюцие элементы И 5л,.-.,5 группы. . Если работа по пакету программ только начинается, то на регистр 4 заносится нулевая строка матрицы и все триггеры регистра остаются в нулевом состоянии. После получения запроса и его фиксации блок 1 упрапления выдает сигнал по своему первому выходу, в результате этого открываются те из элементов И 5, ...,5и группы, на которые подается высокий потенциал с единичных выходов триггеров регистра 4. Под воздействием выходных сигналов группы элементов И 5,,,,,5у) происходит коррекция содержимого счетчиков 16 блоков выбора программы первой группы, после чего блок 1 управления сбрасывает регистр 4 в нулевое состояние и разрешает прохождение импульсов с генератора 2 на свой четвертый выход. Эти импульсы поступают на вторые входы элементов И 17 первой группы блоков 9л , 9о9|л выбора программы и вторые входы элементов И 20 второй группы блоков lOj , 10л,..., 10| выбора программы В блоках 9 J , 92,...,9yj выбора программы первой группы с заполненными счетчиками 16, номера ко.торых соответствуют номерам программ, готовых к счету пусть это будут номера i, j, k), начинается прохождение импульсов по цепям: 4-й выход блока J управления, элементы И 17, вход реверсивных счетчиков 18. Процесс счета импульсов счетчиками 18 продолжается до тех пор, пока будет заполнен хотя бы один Первым заполняется счетчик 18 того блока выбора.программы fпусть это будет 9;), в котором записано наибольшее значение критического пути. После заполнения счетчика 18 триггер 19 блока-9: выбора программы первой группы переходит в единичное состояние. При этом низкий потенциал с его

улевого выхода блокирует дальнейшее прохождение импульсов через элемент 17, исключая в последующем 1-ю программу пакета для назначения к реализации ,5

Таким образом выбирается из числа готовых к реализации программ та -я рограмма, которая имеет наибольшее значение критического пути.. Одновременно с этим в счетчике 12 обращений Ю фиксируется число импульсов, прибавенное к содержимому счетчиков 18 блоков 9i , 9л,.., ,9.- выбора программы первой группы.

Высокий потенциал с первого выхода 15 блока 9J выбора программы первой групы, поступает через элемент И 22 блока 10 -выбора программы второй группы на вход элемента ИЛИ 6, а с его. выхода - на третий .вход блока 1 управ- 20 ения. Последний вьфабатывает сигнал на третьем выходе, переводя триггер 15 правления в единичное состояние. Триггер 15 управления переводит счетчики 12 и 18 блоков 9/, 9rt, .., выбора 25 программы первой группы в режим вычитания. Разрешающий сигнал на третьих выходах блоков 9, 9л,...,9., выбора програ1 1мы первой группы остается. Однако теперь он поступает через эле- зо мент ИЛИ 14 от счетчика 12.

Одновременно с появлением сигнала на выходе триггера 19 блока выбора программы первой группы разрешается прохождение импульсов через элемент И 20 блока выбора программы второй группы. Далее процесс работы устройства распараллеливается.

Через элемент И 20 блока 10. выбора, программы второй группы импульсы . от блока 1 управления поступают на вход счетчика I1 через элемент РШИ 3 и на вход счетчика 21. Последний работает в режиме вычитания и, обнуляясь, прекращает прохождение импульсов через элемент И 20. При этом на счетчике 11 зафиксировано количество им;пульсов, равное номеру выбранной к реализации программы пакета.

В то жеВремя в блоках выоора программы первой группы, соответствующих номерам готовых к реализации программ -f и К. , идет процесс восстановления счетчиков 18 в исходное состояние, При выборе готовой к реализации программы с наибольшим значением критического пути в счетчике 12 зафиксировано число импульсов, равное приращению в счетчиках 18 блоков9 , 9,,

9j выбора программы первой группы. Поле пер включения. триггера 15 управления счетчики 12 и 18 переходят в режим вычитания и продолжают считать до обнуления счетчика J2, так, после этого снимается сигнал с третьих входов блоков 9, 9, выбора программы первой группы, поступакщий с элемента ИЛИ 14. Таким образом, содержимое счетчиков 18 блоков 9 и 9., выбора программы первой группы восстанавливается.

После установки счетчика 11 и восстановления содержимого счетчиков 18 низкий потенциал на выходе элемента ИЛИ 6 является сигналом блоку 1 управления о конце процесса выборки. Пр этом запрещается прохождение импульсов от генератора 2, триггер 15 управления переводится в состояние О, а со счетчика 11 номер выбранной программы через блок 8 считывается в процессор, изщающий заявку. После того обнуляется счетчик И, а устройство переходит в режим ожидания следующего запроса.

Процесс распределения пакета программ по процессорам заканчивается при обнулении всех счетчиков 21 записи блоков 10, 10„,,.,,10у. выбора программы второй группы.

Предлагаемое устройство реализует процесс запуска программ пакета в ходе их реализации, что позволяет учест текущее состояние системы по работоспособности процессоров, а также осуществляет запуск программ с учетом их информационных связей и временных характеристик. Устройство может быть и.спользовано и для управления запуском независимых программ. Для этого каждой .програ.мме ставится в соответствие некоторое условное значение критического пути (чем выше приоритетj тем больше это значение), а счетчики 16 блоков 9, ) выбора .программы первой группы полностью заполняются. Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями, по сравнению с известными.

Формула изобретения

1. Устройство для управления запуском программ, содержащее .блок управления, генератор импульсов, первый элемент ИЛИ, Я-разрядный регистр заявок, первую группу блоков выбора про)граммы, группу элементов И, р.торой элемент ИЛИ, узел анализа приоритетно заявки и блок коммутации, причем выход генератора импульсов подключен к первому входу блока управления, второй вход которого подключен к первому выходу блока коммутации, первая группа выходов которого соединена с группой информационных входов регистра за явок, группа разрядных выходов которо го подключена к первым входам элементов И группыi вторые входы которых со единены с первым выходом блока управления, второй выход которого соединен с первым входом блока коммутации, вто рые вход и выход которого являются, соответственно входом и выходом устройства, третий выход блока управления соединен с управляющими входом узла анализа приоритетной заявки, о т личающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения автоматического выбора для запуска про-граммь, устройство содержит вторую группу блоков выбора программы, счетчик считывается, причем первый выход узла анализа приоритетной заявки соединен с первым входом второго элемен та ИЛИ, первые входы каждого блока вы бора программы первой группы соединены с четвертым выходом блока управления, вторые входы блоков выбора про граммы первой группы соединены со вто рым выходом узла анализа приоритетной заявки, третьи и четвертые входы блоков выбора программы первой группы со единены соответственно со вторым и тр тьим выходами узла анализа приоритетной заявки, пятые и шестые входы блоков выбора программы первой группы со единены со второй группой выходов бло ка коммутации, седьмые входы каждого блока выбора программы первой группы, за исключением первого блока, соединены с выходами соответствующих элемеитов И группы, выходы каждого бдока выбора программы первой группы соединены с первыми входами соответствующих блоков выбора программы второй группы, вторые входы которых соединены с четвертым выходом блока управления, а третьи входы - со второй групрой выходов блока коммутации, первые выходы блоков выбора программы второй группы соединены с соответствуюи№1ми входами второго элемента ИЖ, выход ко торого соединен с третьим входом блока управления, вторые выходы блоков выбора программы второй группы соедиОнены с соответствующими входами первого элемента ИЛИ, выход которого через счетчик считывания соединен с третьим входом блока коммутации, синхронизирующий вход узла анализа приоритетной заявки соединен с четвертым выходом блока управления. 2.Устройство по п. 1, отличающееся тем, что каждый блок выбора программы второй группы содержит первьй и второй элементы И и счетчик записи, причем первый вход блока соединен с первыми входами первого и второго элементов И, второй вход блока соединен со вторым входом первого элемента И, выход которого соединен со вторым выходом блока и первым входом счетчика записи, выход счетчика записи соединен с третьим входом первого элемента И и вторым входом второго элемента И, выход которого соединен с первым входом блока, второй вход .счетчика записи является третьим входов блока. . 3.Устройство по п. 1, отличающееся тем, что каждый блок выбора программы первой группь, кроме первого, содержит счетчик числа дуг, элемент И, реверсивный счетчик и выходной триггер, причем первый и второй входы блока соединены соответственно с первым и вторым входами элемента И, третий вход которого соединен с нулевым выходом выходного триг гера, единичный выход которого соединен с выходом блока, выход элемента И соединен со счетным входом реверсивного счетчика, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым вхо дами блока, а выход реверсивного счетчика соединен с единичным входом выходного триггера, седьмой вход блока соединен с первьм входом счетчика числа дуг, выход которого соединен с четвертым входом элемента И, пятый и тестой входы блока соединены соответственно с информационным входом реверсивного счетчика и вторым входом счетчика числа дуг. 4. Устройство по пп. 1 и 3, о т ичающееся тем, что первый лок выбора программы первой группы одержит элемент И, реверсивный счетик и выходной триггер, причем перый и второй входы блока соединены сответственно с первым и вторым входаи элемента И, третий вход которого оединен с нулевьм выходом выходного триггера, единичный выход которого со единен с выходом блока, выход элемента И соединен со счетным входом реверсивного счетчика, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым входами блока, а выход реверсивного счетчика соединен с единичньм входом выходного триггера, пятый вход блока соединен с информационным входом реверсивного счетчика. 5. Устройство по п, 1, о т л и ча.ющееся тем, что блок управления содержит первый и второй счетчи ки коммутации, триггер управления записью, триггер, элемент НЕ, элементы И, ИЛИ, причем нулевой и единичный выходы триггера управления записью соединены соответственно с управляющими входами первого и второго счетчиков коммутации, первый выход второго счетчика коммутации соединен с первым выходом блока управления, .входом сброса второго счетчика коммутации, единичным ёходом триггера, еди ничный выход которого соединение первым входом элемента ИЛИ, третий вход блока управления соединен со вфорым входом элемента ИЛИ, нулевым входом триггера, входом элемента НЕ, вторым и третьим выходами блока управления, выход элемента НЕ соединен с третьим выходом блока управления, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого соединен с первым входом блока управления, а выход - с четвертым выходом блока управления, второй вход которого соединен с единичным и нулевым входами триггера управления записью, с первым входом первого и входом второго счетчиков коммутации, вторые выходы которых соединены со вторым выходом блока управления, первый выход первого счетчика коммутации соединен со вторым входом этого счетчика. 6., Устройство поп. 1, отличающееся тем, что узел анализа Приоритетной заявки содержит триггер управления, счетчик обращений и элементы И, ИЛИ, причем вход триггера управления является управляющим входом узла, нулевой выход триггера управления соединён с первым управляющим, входом счетчика обращений, с первьм входом элемента ИЛИ и со вторым выходом узла, единичный выход триггера управления соединен со вторым управляющим входом счетчика обращений, с первым входом элемента И и с третьим выходом узла, выход счетчика обращений соединен со вторыми входами элементов И и ИЛИ, выходы которых являются соответственно nepBbiM и вторьпу выходами узла, синхронизирущий вход счетчика обращений является синхронизирующим входом узла. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 468240, кл. G Об F 9/00, 1975. 2. Авторское свидетельство СССР № 645159, кл. G 06 F 9/18, 1979.

9ue. 1

Я 18

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления запуском программ | 1989 |

|

SU1621031A1 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ПАКЕТОВ ИНФОРМАЦИИ | 1994 |

|

RU2075778C1 |

| Многоканальный коммутатор | 1983 |

|

SU1086447A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Устройство для коммутации сообщений | 1983 |

|

SU1157556A1 |

| Устройство для обмена данными в вычислительной системе | 1984 |

|

SU1251090A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1341639A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

аг.2

(put,

Авторы

Даты

1981-10-30—Публикация

1980-01-11—Подача