ФигЛ

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано для измерения длительности двуполярных пе- риодическнх импульсных сигналов.

Цель изобретения - повышение точности при измерении длительности сим- (метричных биполярных импульсов в условиях помех.,

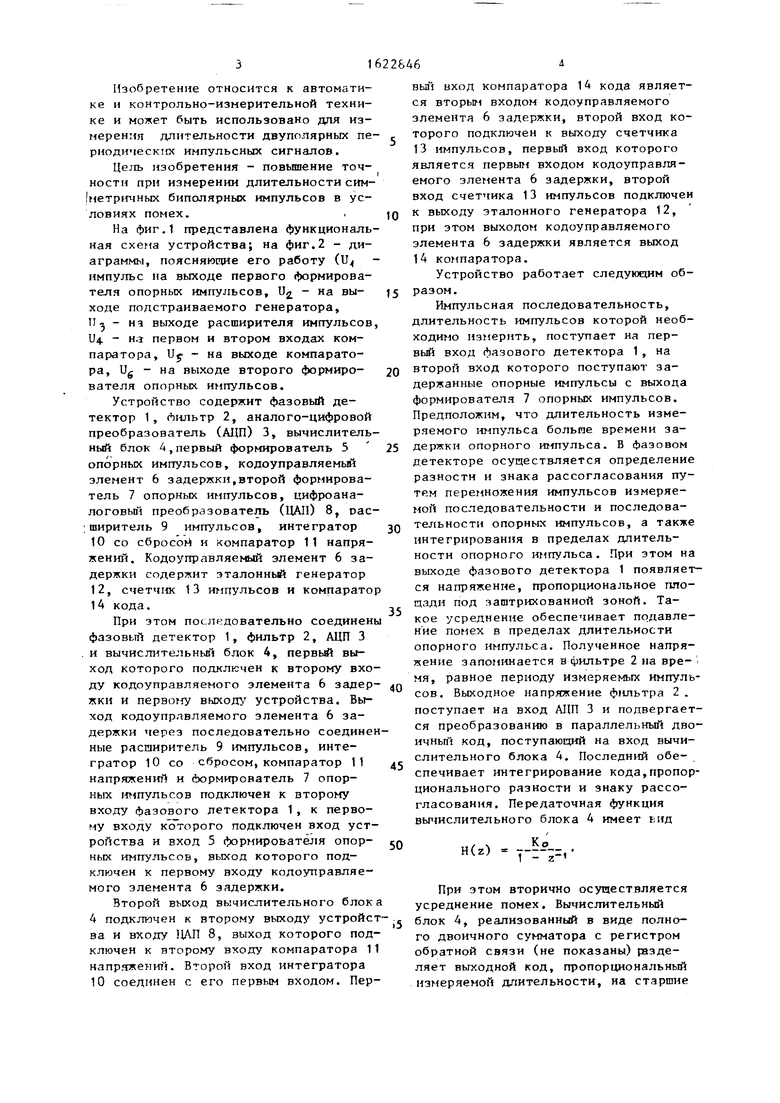

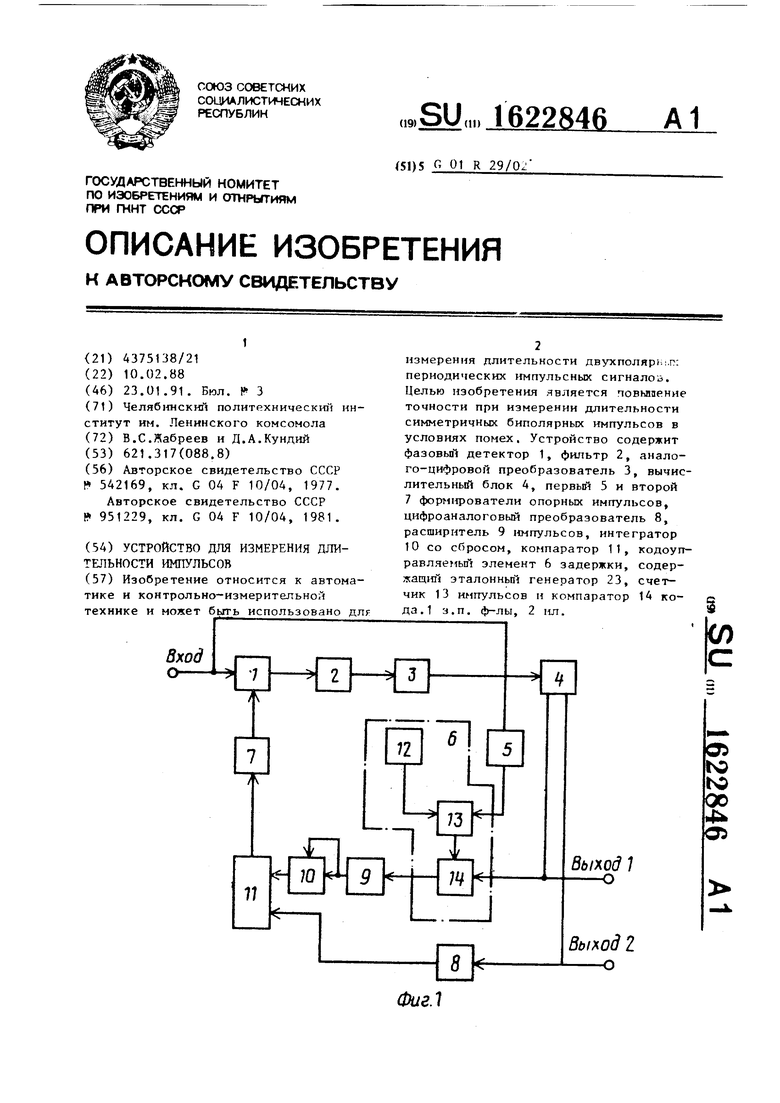

На фиг.1 представлена функциональная схема устройства; на фиг.2 - диаграммы, поясняющие его работу (U - импульс на выходе первого формирователя опорных импульсов, Uj. - на вы- ходе подстраиваемого генератора, 13 на выходе расширителя импульсов, U. - H.J первом и втором входах компаратора, Uy - на выходе компаратора, Ug - на выходе второго формиро- вателя опорных импульсов.

Устройство содержит фазовый детектор 1, Лильтр 2, аналого-цифровой преобразователь (АЦП) 3, вычислительный блок 4,первый формирователь 5 опорных импульсов, кодоуправляемый элемент 6 задержки,второй формирователь 7 опорных импульсов, цифроана- логовый преобразователь (ЦА11) 8t рас- ;ширитель 9 импульсов, интегратор 10 со сбросом и компаратор 11 напряжений. Кодоуправляемый элемент 6 задержки содержит эталонный генератор 12, счетчик 13 импульсов и компаратор 14 кода.

При этом последовательно соединены фазовый детектор 1, фильтр 2, АЦП 3 и вычислительный блок 4, первый выход которого подключен к второму входу кодоуправляемого элемента 6 задер- жки и первому выходу устройства. Выход кодоупрлвляемого элемента 6 задержки через последовательно соединенные расширитель 9 импульсов, интегратор 10 со сбросом, компаратор 11 напряжений и Формирователь 7 опорных импульсов подключен к второму входу фазового детектора 1, к первому входу которого подключен вход устройства и вход 5 формирователя опор- ных импульсов, выход которого подключен к первому входу кодоуправляемого элемента 6 задержки.

Второй выход вычислительного блока 4 подключен к второму выходу устройст ва и входу ЦАП 8, выход которого подключен к второму входу компаратора 11 напряжений. Второй вход интегратора 10 соединен с его первым входом. Пер

Q

5 0

0

Q п

5

вый вход компаратора 14 кода является вторым входом кодоуправляемого элемента 6 задержки, второй вход которого подключен к выходу счетчика

13импульсов, первый вход которого является первым входом кодоуправляемого элемента 6 задержки, второй вход счетчика 13 импульсов подключен к выходу эталонного генератора 12, при этом выходом кодоуправляемого элемента 6 задержки является выход

14компаратора.

Устройство работает следующим образом.

Импульсная последовательность, длительность импульсов которой необходимо измерить, поступает на первый вход фазового детектора 1, на второй вход которого поступают задержанные опорные импульсы с выхода формирователя 7 опорных импульсов. Предположим, что длительность измеряемого импульса больше времени задержки опорного импульса. В фазовом детекторе осуществляется определение разности и знака рассогласования путем перемножения импульсов измеряемой последовательности и последовательности опорных импульсов, а также интегрирования в пределах длительности опорного импульса. При этом на выходе фазового детектора 1 появляется напряжение, пропорциональное площади под заштрихованной зоной. Такое усреднение обеспечивает подавление помех в пределах длительности опорного импульса. Полученное напряжение запоминается в фильтре 2 на вре- мя, равное периоду измеряемых импульсов. Выходное напряжение фильтра 2 . поступает на вход АЦП 3 и подвергается преобразованию в параллельный двоичный код, поступающий на вход вычислительного блока 4. Последний обеспечивает интегрирование кода,пропорционального разности и знаку рассогласования. Передаточная функция вычислительного блока 4 имеет вид

нЫ

Ко Т

При этом вторично осуществляется усреднение помех. Вычислительный блок 4, реализованный в виде полного двоичного сумматора с регистром обратной связи (не показаны) разделяет выходной код, пропорциональный измеряемой длительности, на старшие

и младшие разряды, поступающие и ч первый и второй выходы вычислительного блока 4. Старшие разряды кода поступают на первый вход компаратора кода 14. Задержка опорного импульса осуществляется путем подсчета импульсов эталонного генератора 12, импульсы которого поступают на второй вход счетчика 13, при этом подсчет числа импульсов продолжается до момента равенства выходного кода счетчика 13 старшим разрядам кода, пропорционального измеряемой длительности. Момент равенства фиксируется компаратором 14 кода, на выходе которого появляется задержанный опорный импульс (фиг.2, U2).Опорный импульс расширяется в расширителе 9 (фиг.2, Uj) и поступает на оба входа интегратора 10 со сбросом. По положительному переходу задержанного опорного импульса на выходе интегратора 10 со сбросом появляется линейно возрастающее напряжение, по отрицательному фронту происходит сброс интегратора 10 и напряжение на его выходе линейно убывает (фиг.2,

и4).

Проинтегрированный импульс поступает на первый вход компаратора 11 напряжений, на второй вход которого поступает напряжение с выхода ЦАП 8, пропорциональное младшим разрядам кода, пропорционального измеряемой длительности, поступающего на вход преобразователя 8. Момент равенства напряжений фиксируется компаратором 11 напряжений (фиг.2, U), выходной импульс которого поступает на вход формирователя 7 опорных импульсов, где его длительность формируется равной длительности заднего фронта измеряемого импульса. Таким образом,задержанный опорный импульс (фиг.2,и) время задержки которого равно и)м.

.ет.р. ,мл.р (Фиг.2) поступает на второй вход Фазового детектора 1, осуществляющего выделение разности и знака рассогласования.При этом измеряемый импульс поступает на вход формирователя 5 опорных импульсов, формирующего опорный импульс, подлежащий задержке, по переднему фронту измеряемого импульса. Импульс с выхода формирователя 5 поступает на первый вход счетчика 13 импульсов, осуществляя сброс счетчика в нулевое

состояние, чем обеспечивается синхронизация процесса измерения.

Таким образом, при положительной разности рассогласования время задержки опорного импульса должно увеличиться. . Если на следующем периоде измеряемых импульсов разность рассогласования на станет равной 0, то

процесс работы устройства повторяется. Если на каком-либо периоде измеряемых импульсов разность рассогласования станет равной 0, то операции, производимые в этом случае вычисли5 тельным блоком 4, не изменят выход- f ного кода, представляющего результат измерения длительности импульсов входной последовательности. Это говорит о том, что задержка опорного

0 импульса точно соответствует длительности измеряемого импульса.

Формула изобретения

5 1 Устройство для измерения длительности импульсов, содержащее фазовый детектор, выход которого подключен к входу фильтра, и вычислительный блок, отличающееся тем,

0 что, с целью повышения точности при измерении длительности повторяющихся симметричных биполярных импульсов в условиях помех, в него введены аналого-цифровой преобразователь, первый формирователь опорных импульсов, циф- роаналоговый преобразователь, кодо- управляемый элемент задержки и последовательно соединенные расширитель импульсов, интегратор со сбросом, .

5

компаратор напряжений и второй формирователь опорных импульсов, выход которого подключен к второму входу фазового детектора, первый вход которого объединяет вход устройства и

вход первого формирователя опорных импульсов, выход которого подключен к первому входу одоуправляемого элемента задержки, ВТОРОЙ вход которого подключен к первому выходу вычислительного блока, являющемуся первым выходом устройства, второй выход устройства подключен к второму выходу вычислительного блока и входу циф- роаналогового преобразователя, выход

которого подключен к второму входу компаратора напряжений, вход аналого-цифрового преобразователя подключен к выходу Фильтра, а выход - к входу вычислительного блока, второй вход

интегратора соединен с его первым входом, при этом выход кодоуправляе- мого элемента задержки подключен к входу расширителя импульсов.

2. Устройство по п.1, отличающееся тем, что кодоуправ- ляемый элемент задержки содержит эталонный генератор, счетчик импульсов и компаратор кода, первый вход котоU Г

Ilull

рого является вторым входом кодоуп- равляемого элемента задержки, а второй вход подключен к выходу счетчика импульсов, первый вход которого является первым входом кодоуправляемого элемента задержки, второй вход счетчика импульсов подключен к выходу эталонного генератора, при этом выходом кодоуправляемого элемента задержки является выход компаратора кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель дифференциальной фазы | 1980 |

|

SU1104436A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| Ультразвуковой дефектоскоп | 1981 |

|

SU978035A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПЕРЕМЕННОГО ТОКА ПРОМЫШЛЕННОЙ ЧАСТОТЫ | 2008 |

|

RU2368910C1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Устройство для измерения частотных характеристик канала связи | 1986 |

|

SU1381723A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1119050A1 |

| Устройство для контроля деградации МДП-структур | 1990 |

|

SU1783454A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано для измерения длительности двухполярь;.г: периодических импульсных сигналов. Целью изобретения является повышение точности при измерении длительности симметричных биполярных импульсов в условиях помех. Устройство содержит фазовый детектор 1, фильтр 2, аналого-цифровой преобразователь 3, вычислительный блок 4, первый 5 и второй 7 формирователи опорных импульсов, цифроаналоговый преобразователь 8, расширитель 9 импульсов, интегратор 10 со сбросом, компаратор 11, кодоуп- равляемый элемент 6 задержки, содержащий эталонный генератор 23, счетчик 13 импульсов и компаратор 14 кода. 1 з.п. ф-лы, 2 ил. (/)

TjQtert

г

Uifl С

Ц)Н С.

з

2 Т, г.

«ол

«У,

Г .

г

Г«/|И

-I

Uifl С

Ц)Н С. Tfl

О г/}Л

| Способ автокомпенсационного измерения длительности повторяющихся импульсов | 1975 |

|

SU542169A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Измеритель временных интервалов | 1981 |

|

SU951229A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-01-23—Публикация

1988-02-10—Подача