1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Целью изобретения является повышение быстродействия преобразователя путем уменьшения времени переходных процессов при ступенчатом изме- нении сдвига фазы и амплитуды компенсационных напряжений.

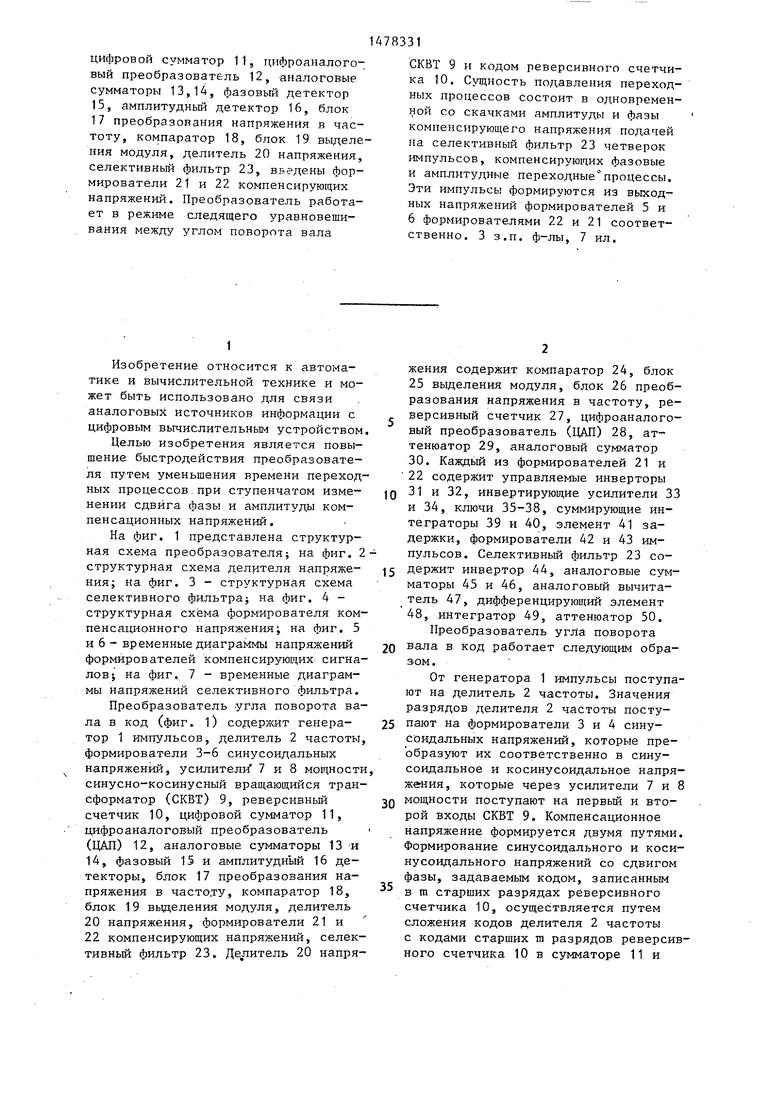

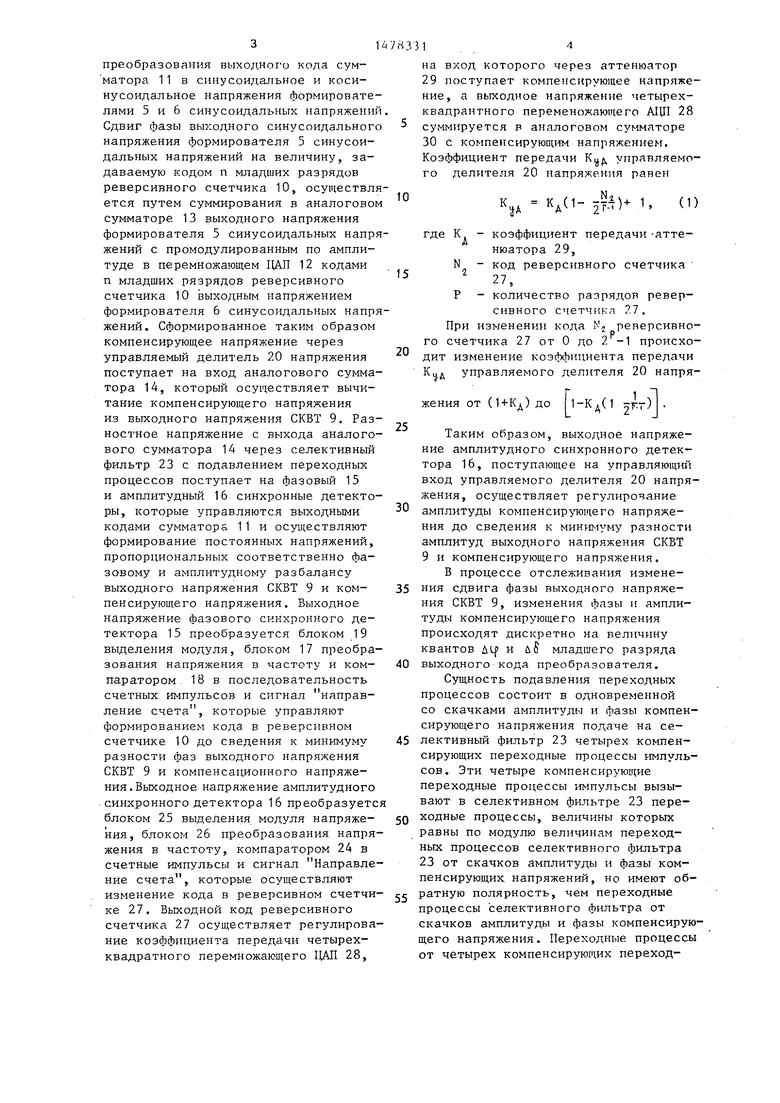

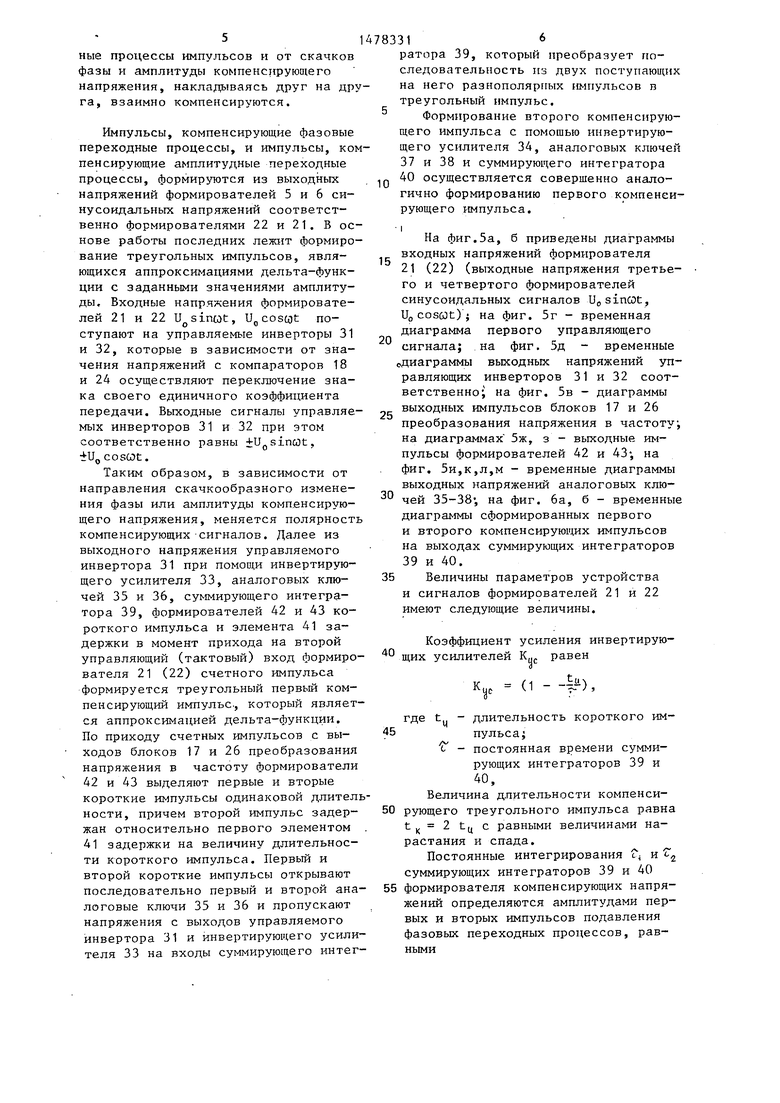

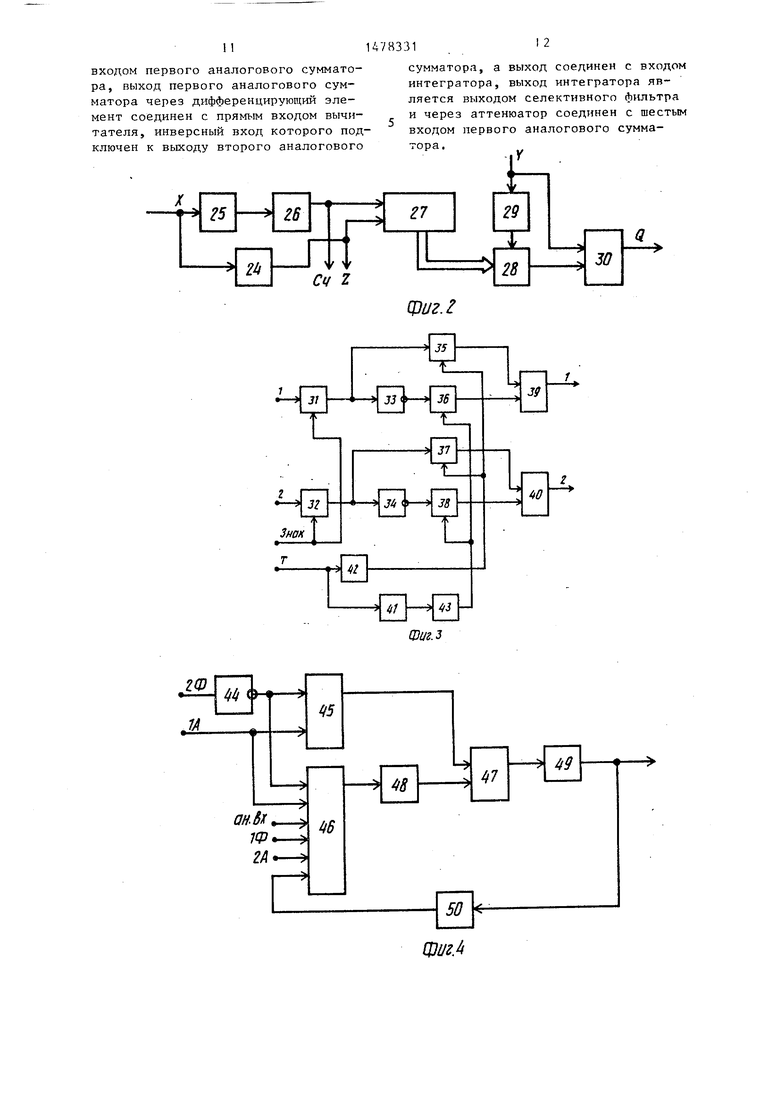

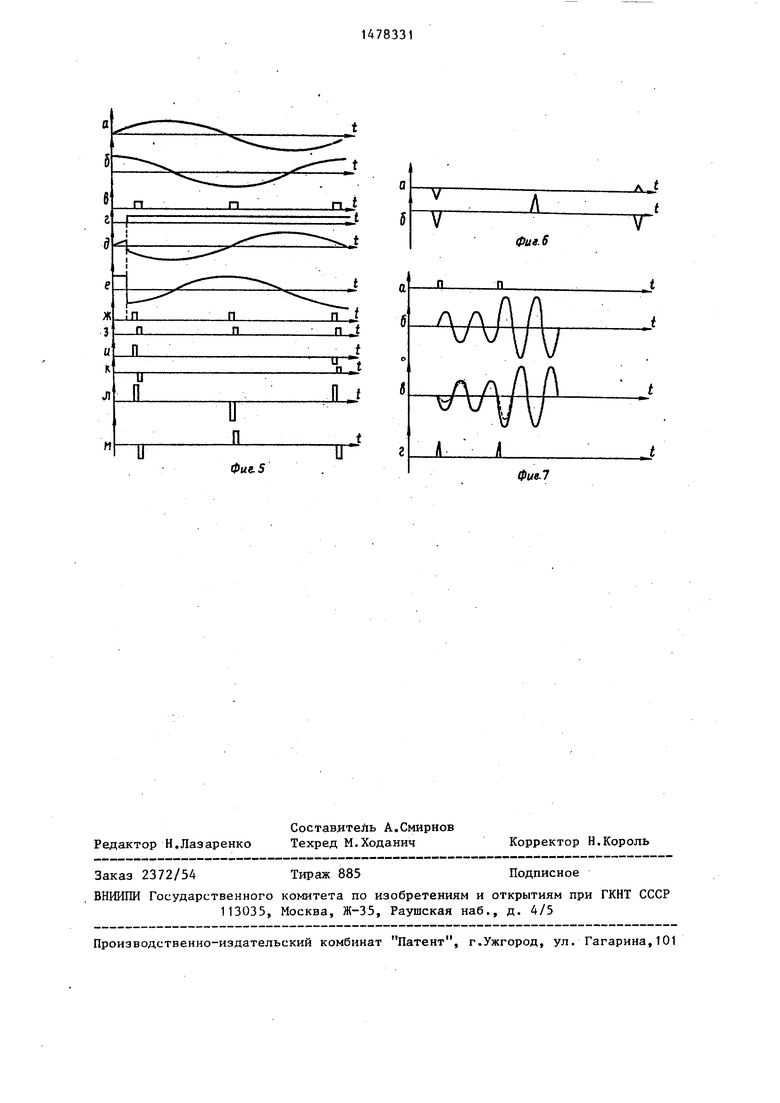

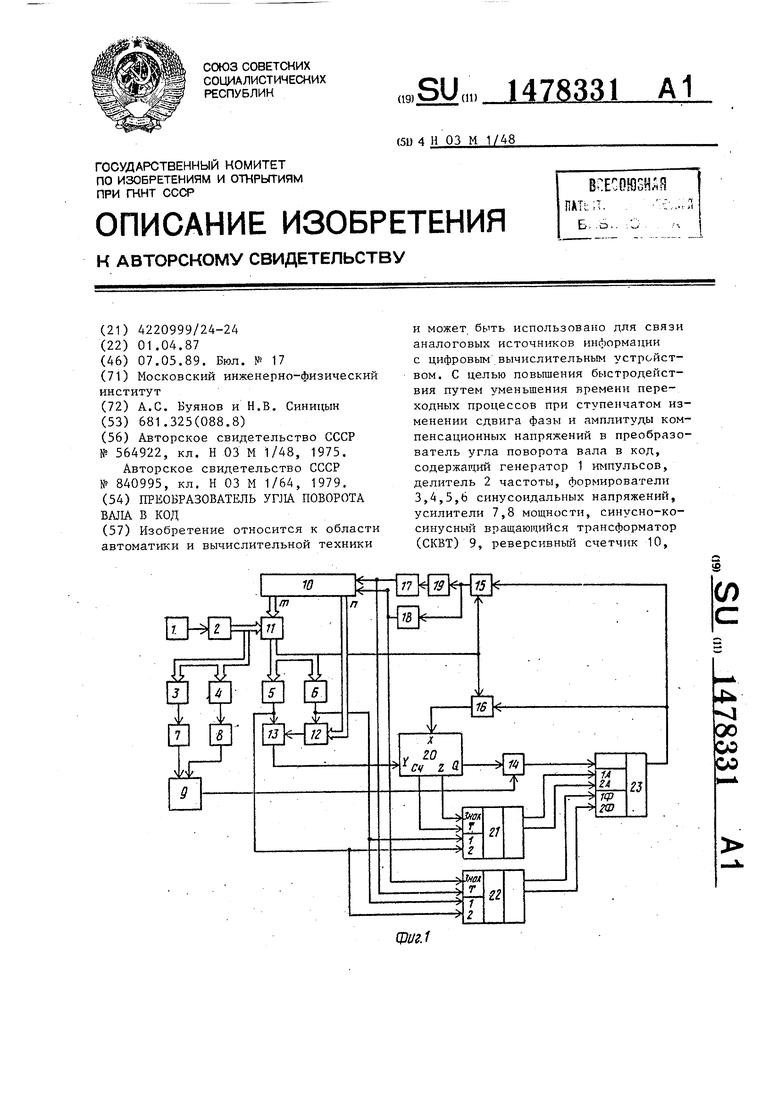

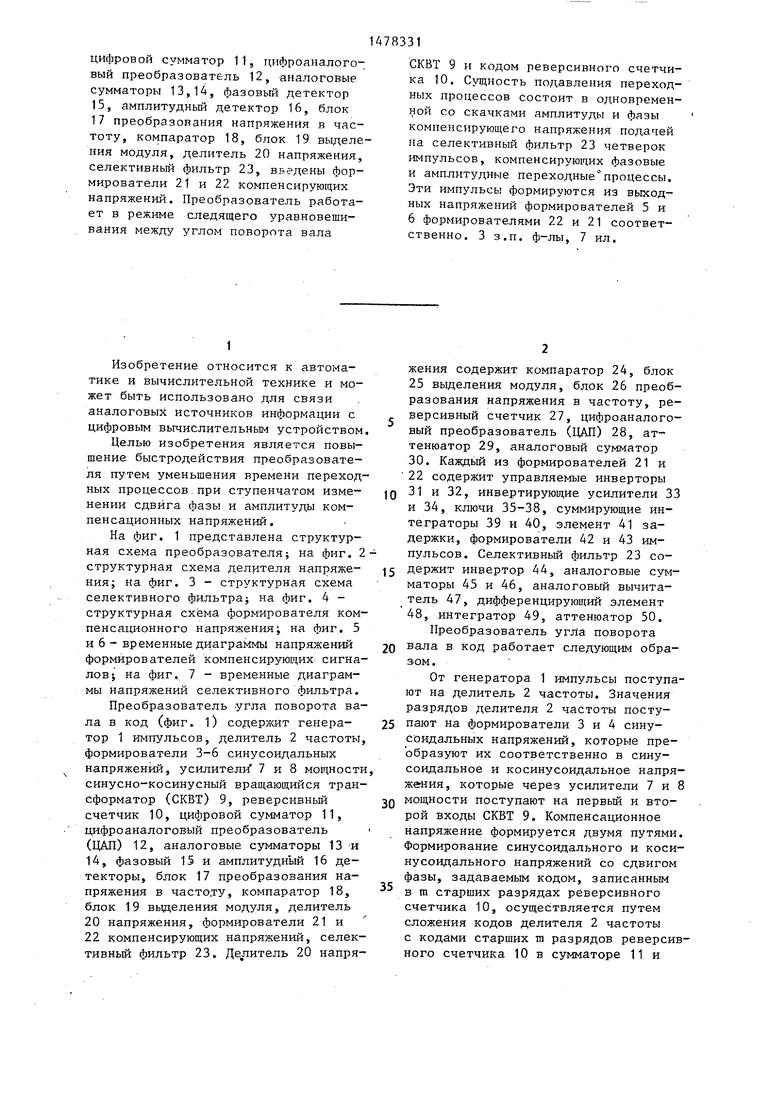

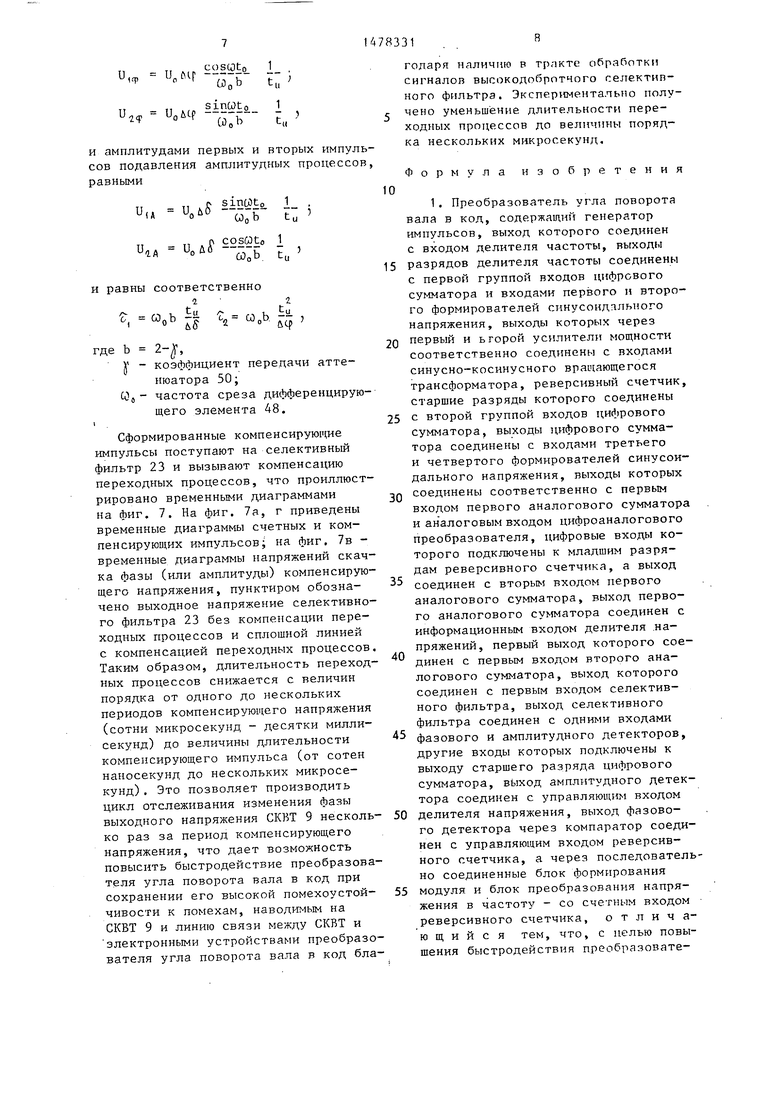

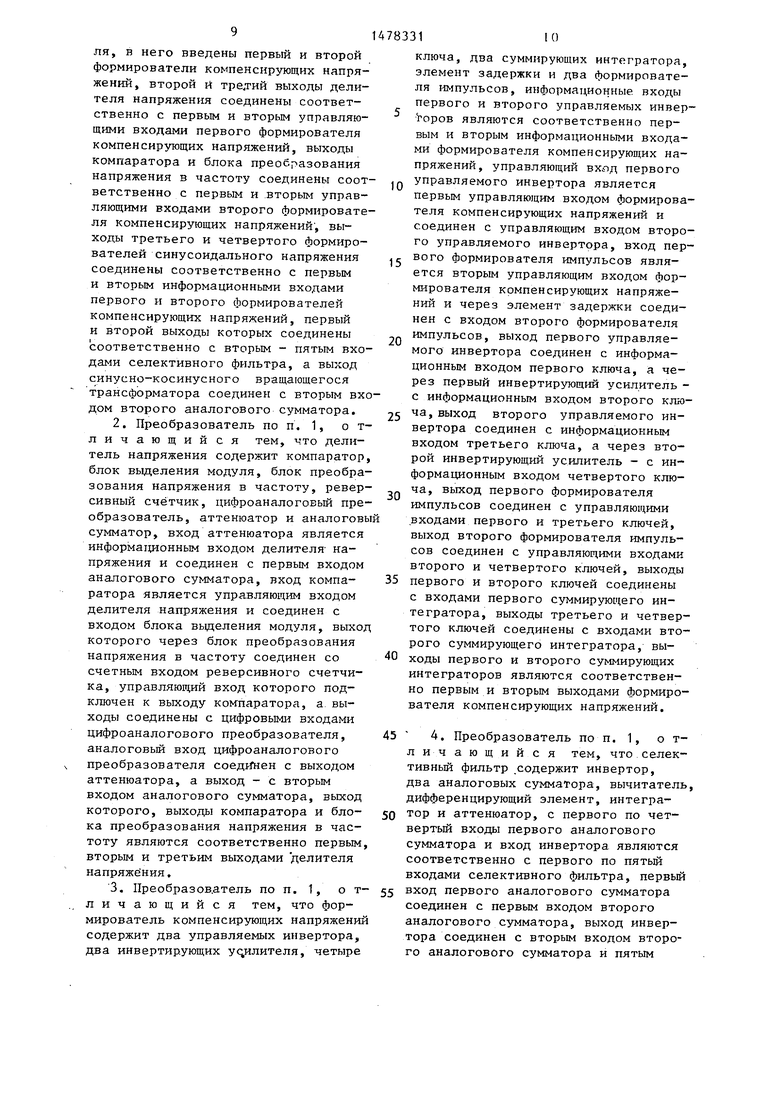

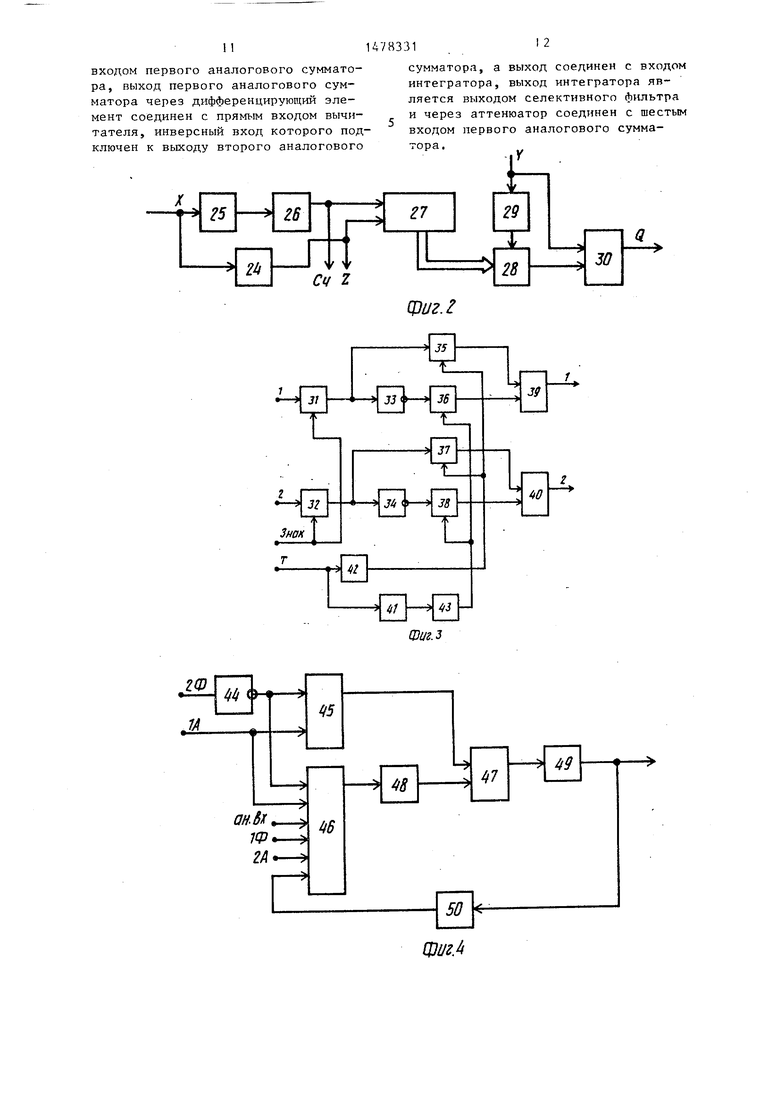

На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 структурная схема делителя напряже- ния; на фиг. 3 - структурная схема селективного фильтра; на фиг. 4 - структурная схема формирователя компенсационного напряжения на фиг. 5 и 6 - временные диаграммы напряжений формирователей компенсирующих сигналов , на фиг. 7 - временные диаграммы напряжений селективного фильтра.

Преобразователь угла поворота вала в код (фиг. 1) содержит генера- тор 1 импульсов, делитель 2 частоты, формирователи 3-6 синусоидальных напряжений, усилители 7 и 8 мощности синусно-косинусный вращающийся трансформатор (СКБТ) 9, реверсивный счетчик 10, цифровой сумматор 11, цифроаналоговый преобразователь (ЦАП) 12, аналоговые сумматоры 13 и 14, фазовый 15 и амплитудный 16 детекторы, блок 17 преобразования напряжения в часто.ту, компаратор 18, блок 19 выделения модуля, делитель 20 напряжения, формирователи 21 и 22 компенсирующих напряжений, селективный фильтр 23. Делитель 20 напря

Q

0

5 0

5

жения содержит компаратор 24, блок 25 выделения модуля, блок 26 преобразования напряжения в частоту, реверсивный счетчик 27, цифроаналого- вый преобразователь (ЦАП) 28, аттенюатор 29, аналоговый сумматор 30. Каждый из формирователей 21 и 22 содержит управляемые инверторы 31 и 32, инвертирующие усилители 33 и 34, ключи 35-38, суммирующие интеграторы 39 и 40, элемент 41 задержки, формирователи 42 и 43 импульсов. Селективный фильтр 23 содержит инвертор 44, аналоговые сумматоры 45 и 46, аналоговый вычита- тель 47, дифференцирующий элемент 48, интегратор 49, аттенюатор 50.

Преобразователь угла поворота вала в код работает следующим образом.

От генератора 1 импульсы поступают на делитель 2 частоты. Значения разрядов делителя 2 частоты поступают на формирователи 3 и 4 синусоидальных напряжений, которые преобразуют их соответственно в синусоидальное и косинусоидальное напряжения, которые через усилители 7 и 8 мощности поступают на первый и второй входы СКВТ 9. Компенсационное напряжение формируется двумя путями. Формирование синусоидального и коси- нусоидального напряжений со сдвигом фазы, задаваемым кодом, записанным в m старших разрядах реверсивного счетчика 10, осуществляется путем сложения кодов делителя 2 частоты с кодами старших m разрядов реверсивного счетчика 10 в сумматоре 11 и

преобразования выходного кода сумматора 11 в синусоидальное и коси- нусоидальное напряжения формирователями 5 и 6 синусоидальных напряжений Сдвиг фазы выходного синусоидального напряжения формирователя 5 синусоидальных напряжений на величину, задаваемую кодом п младших разрядов реверсивного счетчика 10, осуществляется путем суммирования в аналоговом сумматоре 13 выходного напряжения формирователя 5 синусоидальных напряжений с промоделированным по амплитуде в перемножающем ЦАП 12 кодами п младших рязрядов реверсивного счетчика 10 выходным напряжением формирователя 6 синусоидальных напряжений. Сформированное таким образом компенсирующее напряжение через управляемый делитель 20 напряжения поступает на вход аналогового сумматора 14, который осуществляет вычитание компенсирующего напряжения из выходного напряжения СКВТ 9. Разностное напряжение с выхода аналогового сумматора 14 через селективный фильтр 23 с подавлением переходных процессов поступает на фазовый 15 и амплитудный 16 синхронные детекторы, которые управляются выходными кодами сумматора 11 и осуществляют формирование постоянных напряжений, пропорциональных соответственно фазовому и амплитудному разбалансу выходного напряжения СКВТ 9 и компенсирующего напряжения. Выходное напряжение фазового синхронного детектора 15 преобразуется блоком 19 выделения модуля, блоком 17 преобразования напряжения в частоту и компаратором 18 в последовательность счетных импульсов и сигнал направление счета, которые управляют формированием кода в реверсивном счетчике 10 до сведения к минимуму разности фаз выходного напряжения СКВТ 9 и компенсационного напряжения. Выходное напряжение амплитудного синхронного детектора 16 преобразуется блоком 25 выделения модуля напряжения, блоком 26 преобразования напряжения в частоту, компаратором 24 в счетные импульсы и сигнал Направление счета, которые осуществляют изменение кода в реверсивном счетчике 27. Выходной код реверсивного счетчика 27 осуществляет регулирование коэффициента передачи четырех- квадратного перемножающего ЦАП 28,

на вход которого через аттенюатор

29поступает компенсирующее напряжение, а выходное напряжение четырех- квадрантного переменожающего АЦП 28 суммируется в аналоговом сумматоре

30с компенсирующим напряжением. Коэффициент передачи управляемого делителя 20 напряжения равен

К

N,

а

К,(1- rЈi)+ 1

со

где К - коэффициент передачи -аттенюатора 29,

N - код реверсивного счетчика 27,

Р - количество разрядов реверсивного счетчика 7. При изменении кода N/. реверсивного счетчика 27 от 0 до 2 -1 происхо- дит изменение коэффициента передачи Кпд управляемого делителя 20 напряжения от (1 + Кд) до М-КД(1 )

Таким образом, выходное напряжение амплитудного синхронного детектора 16, поступающее на управляющий вход управляемого делителя 20 напряжения, осуществляет регулирование амплитуды компенсирующего напряжения до сведения к минимуму разности амплитуд выходного напряжения СКВТ 9 и компенсирующего напряжения. В процессе отслеживания изменения сдвига фазы выходного напряжения СКВТ 9, изменения фазы и амплитуды компенсирующего напряжения происходят дискретно на величину квантов дц и ufi младшего разряда

выходного кода преобразователя.

Сущность подавления переходных процессов состоит в одновременной со скачками амплитуды и фазы компенсирующего напряжения подаче на селективный фильтр 23 четырех компенсирующих переходные процессы импульсов. Эти четыре компенсирующие переходные процессы импульсы вызывают в селективном фильтре 23 пере-

ходные процессы, величины которых равны по модулю величинам переходных процессов селективного фильтра 23 от скачков амплитуды и фазы компенсирующих напряжений, но имеют обратную полярность, чем переходные процессы селективного фильтра от скачков амплитуды и фазы компенсирующего напряжения. Переходные процессы от четырех компенсирующих переходные процессы импульсов и от скачков фазы и амплитуды компенсирующего напряжения, накладываясь друг на друга, взаимно компенсируются.

Импульсы, компенсирующие фазовые переходные процессы, и импульсы, компенсирующие амплитудные переходные процессы, формируются из выходных напряжений формирователей 5 и 6 синусоидальных напряжений соответственно формирователями 22 и 21. В основе работы последних лежит формирование треугольных импульсов, являющихся аппроксимациями дельта-функции с заданными значениями амплитуды. Входные напряжения формирователей 21 и 22 Uosinwt, U0coscot поступают на управляемые инверторы 31 и 32, которые в зависимости от значения напряжений с компараторов 18 и 24 осуществляют переключение знака своего единичного коэффициента передачи. Выходные сигналы управляемых инверторов 31 и 32 при этом соответственно равны +U sincot. ±U0cosCdt:.

Таким образом, в зависимости от направления скачкообразного изменения фазы или амплитуды компенсирующего напряжения, меняется полярность компенсирующих сигналов. Далее из выходного напряжения управляемого инвертора 31 при помощи инвертирующего усилителя 33, аналоговых ключей 35 и 36, суммирующего интегратора 39, формирователей 42 и 43 короткого импульса и элемента 41 задержки в момент прихода на второй управляющий (тактовый) вход формирователя 21 (22) счетного импульса формируется треугольный первый компенсирующий импульс, который является аппроксимацией дельта-функции. По приходу счетных импульсов с выходов блоков 17 и 26 преобразования напряжения в частоту формирователи 42 и 43 выделяют первые и вторые короткие импульсы одинаковой длительности, причем второй импульс задержан относительно первого элементом 41 задержки на величину длительности короткого импульса. Первый и второй короткие импульсы открывают последовательно первый и второй аналоговые ключи 35 и 36 и пропускают напряжения с выходов управляемого инвертора 31 и инвертирующего усилителя 33 на входы суммирующего интегратора 39, который преобразует последовательность из двух поступающих на него разнополярпых импульсов в треугольный импульс.

Формирование второго компенсирующего импульса с помошыо инвертирующего усилителя 34, аналоговых ключей 37 и 38 и суммирующего интегратора 40 осуществляется совершенно аналогично формированию первого компенсирующего импульса.

5

На фиг.5а, б приведены диаграммы входных напряжений формирователя 21 (22) (выходные напряжения третьего и четвертого формирователей синусоидальных сигналов U0sincot, U0coswt)j на фиг. 5г - временная диаграмма первого управляющего сигнала; на фиг. 5д - временные сдиаграммы выходных напряжений управляющих инверторов 31 и 32 соответственно; на фиг. 5в - диаграммы выходных импульсов блоков 17 и 26 преобразования напряжения в частоту, на диаграммах 5ж, з - выходные импульсы формирователей 42 и 43; на фиг. 5и,к,л,м - временные диаграммы выходных напряжений аналоговых ключей 35-38, на фиг. 6а, б - временные диаграммы сформированных первого и второго компенсирующих импульсов на выходах суммирующих интеграторов 39 и 40.

5 Величины параметров устройства и сигналов формирователей 21 и 22 имеют следующие величины.

Коэффициент усиления инвертирующих усилителей Кцс равен

о

(1 - )

к,

где ty - длительность короткого им- пульса;

V - постоянная времени суммирующих интеграторов 39 и 40,

Величина дпительности компенси- рующего треугольного импульса равна t к 2 иц с равными величинами нарастания и спада.

Постоянные интегрирования с и суммирующих интеграторов 39 и 40 формирователя компенсирующих напряжений определяются амплитудами первых и вторых импульсов подавления фазовых переходных процессов, равными

U0ftir

COSUto

00b

TI - n wn sinwto 1

U - иГь- tu

и амплитудами первых и вторых импульсов подавления амплитудных процессов, равными

- v« - ;;

и„ if Ј i

0)Qb

равны соответственно г

Л

М Ъ -i. Q°b

v °b S

где b 2-fi,

коэффициент передачи аттенюатора 50;

С00 - частота среза дифференцирующего элемента 48.

Сформированные компенсирующие импульсы поступают на селективный фильтр 23 и вызывают компенсацию переходных процессов, что проиллюстрировано временными диаграммами на фиг. 7. На фиг. 7а, г приведены временные диаграммы счетных и компенсирующих импульсов; на фиг. 7в - временные диаграммы напряжений скачка фазы (или амплитуды) компенсирующего напряжения, пунктиром обозначено выходное напряжение селективного фильтра 23 без компенсации переходных процессов и сплошной линией с компенсацией переходных процессов. Таким образом, длительность переходных процессов снижается с величин порядка от одного до нескольких периодов компенсирующего напряжения (сотни микросекунд - десятки миллисекунд) до величины длительности компенсирующего импульса (от сотен наносекунд до нескольких микросекунд) . Это позволяет производить цикл отслеживания изменения фазы выходного напряжения СКВТ 9 несколько раз за период компенсирующего напряжения, что дает возможность повысить быстродействие преобразователя угла поворота вала в код при сохранении его высокой помехоустойчивости к помехам, наводимым на СКВТ 9 и линию связи между СКВТ и электронными устройствами преобразователя угла поворота вала в код бла0

5

0

5

0

5

0

5

0

5

годаря наличию в тракте обработки сигналов высокодобротчого селективного фильтра. Экспериментально получено уменьшение длительности переходных процессов до величины порядка нескольких микросекунд.

Формула изобретения

1. Преобразователь угла поворота вала в код, содержащий генератор импульсов, выход которого соединен с входом делителя частоты, выходы разрядов делителя частоты соединены с первой группой входов цифрового сумматора и входами первого и второго формирователей синусоид-яльного напряжения, выходы которых через первый и ьгорой усилители мощности соответственно соединены с входами синусно-косинусного вращающегося трансформатора, реверсивный счетчик, старшие разряды которого соединены с второй группой входов цифрового сумматора, выходы цифрового сумматора соединены с входами третьего и четвертого формирователей синусоидального напряжения, выходы которых соединены соответственно с первым входом первого аналогового сумматора и аналоговым входом цифроаналогового преобразователя, цифровые входы которого подключены к младшим разрядам реверсивного счетчика, а выход соединен с вторым входом первого аналогового сумматора, выход первого аналогового сумматора соединен с информационным входом делителя напряжений, первый выход которого соединен с первым входом второго аналогового сумматора, выход которого соединен с первым входом селективного фильтра, выход селективного фильтра соединен с одними входами фазового и амплитудного детекторов, другие входы которых подключены к выходу старшего разряда цифрового сумматора, выход амплитудного детектора соединен с управляющим входом делителя напряжения, выход фазового детектора через компаратор соединен с управляющим входом реверсивного счетчика, а через последовательно соединенные блок формирования модуля и блок преобразования напряжения в частоту - со счетным входом реверсивного счетчика, отличающийся тем, что, с целью повышения быстродействия преобразовате

9

ля, в него введены первый и второй формирователи компенсирующих напряжении, второй и тре„тий выходы делителя напряжения соединены соответственно с первым и вторым управляющими входами первого формирователя компенсирующих напряжений, выходы компаратора и блока преобразования напряжения в частоту соединены соответственно с первым и вторым управляющими входами второго формирователя компенсирующих напряжений, выходы третьего и четвертого формирователей синусоидального напряжения соединены соответственно с первым и вторым информационными входами первого и второго формирователей компенсирующих напряжений, первый и второй выходы которых соединены соответственно с вторым - пятым входами селективного фильтра, а выход синусно-косинусного вращающегося трансформатора соединен с вторым вхдом второго аналогового сумматора.

2.Преобразователь по п. 1, отличающийся тем, что делитель напряжения содержит компаратор блок выделения модуля, блок преобразования напряжения в частоту, реверсивный счётчик, цифроаналоговый преобразователь, аттенюатор и аналогов сумматор, вход аттенюатора является информационным входом делителя- напряжения и соединен с первым входом аналогового сумматора, вход компаратора является управляющим входом делителя напряжения и соединен с входом блока выделения модуля, выхо которого через блок преобразования напряжения в частоту соединен со счетным входом реверсивного счетчика, управляющий вход которого подключен к выходу компаратора, а выходы соединены с цифровыми входами цифроаналогового преобразователя, аналоговый вход цифроаналогового преобразователя соединен с выходом аттенюатора, а выход - с вторым входом аналогового сумматора, выход которого, выходы компаратора и блока преобразования напряжения в частоту являются соответственно первым вторым и третьим выходами делителя напряжения.

3.Преобразов.атель по п. 1, отличающийся тем, что формирователь компенсирующих напряжени содержит два управляемых инвертора, два инвертирующих усилителя, четыре

0

5

0

8331

10

ключа, два суммирующих интегратора, элемент задержки и два формирователя импульсов, информационные входы первого и второго управляемых инверторов являются соответственно первым и вторым информационными входами формирователя компенсирующих напряжений, управляющий вхлд первого управляемого инвертора является первым управляющим входом формирователя компенсирующих напряжений и соединен с управляющим входом второго управляемого инвертора, вход первого формирователя импульсов является вторым управляющим входом формирователя компенсирующих напряжений и через элемент задержки соединен с входом второго формирователя импульсов, выход первого управляемого инвертора соединен с информационным входом первого ключа, а через первый инвертирующий усилитель - с информационным входом второго клю- 5 ча выход второго управляемого инвертора соединен с информационным входом третьего ключа, а через второй инвертирующий усилитель - с информационным входом четвертого ключа, выход первого формирователя

0

5

0

5

0

5

импульсов соединен с управляющими входами первого и третьего ключей, выход второго формирователя импульсов соединен с управляющими входами второго и четвертого ключей, выходы первого и второго ключей соединены с входами первого суммирующего интегратора, выходы третьего и четвертого ключей соединены с входами второго суммирующего интегратора, выходы первого и второго суммирующих интеграторов являются соответственно первым и вторым выходами формирователя компенсирующих напряжений.

4. Преобразователь по п. 1, отличающийся тем, что селективный фильтр .содержит инвертор, два аналоговых сумматора, вычитатель, дифференцирующий элемент, интегратор и аттенюатор, с первого по четвертый входы первого аналогового сумматора и вход инвертора являются соответственно с первого по пятый входами селективного фильтра, первый вход первого аналогового сумматора соединен с первым входом второго аналогового сумматора, выход инвертора соединен с вторым входом второго аналогового сумматора и пятым

входом первого аналогового сумматора, выход первого аналогового сумматора через дифференцирующий элемент соединен с прямым входом вычи- тателя, инверсный вход которого подключен к выходу второго аналогового

сумматора, а выход соединен с входом интегратора, выход интегратора является выходом селективного фильтра и через аттенюатор соединен с шестым входом первого аналогового сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2008 |

|

RU2365032C1 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1751850A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1095213A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1985 |

|

SU1295521A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения быстродействия путем уменьшения времени переходных процессов при ступенчатом изменении сдвига фазы и амплитуды компенсационных напряжений в преобразователь угла поворота вала в код, содержащий генератор 1 импульсов, делитель 2 частоты, формирователи 3,4,5,6 синусоидальных напряжений, усилители 7,8 мощности, синусно-косинусный вращающийся трансформатор (СКВТ) 9, реверсивный счетчик 10, цифровой сумматор 11, цифроаналоговый преобразователь 12, аналоговые сумматоры 13, 14, фазовый детектор 15, амплитудный детектор 16, блок 17 преобразования напряжения в частоту, компаратор 18, блок 19 выделения модуля, делитель 20 напряжения, селективный фильтр 23, введены формирователи 21 и 22 компенсирующих напряжений. Преобразователь работает в режиме следящего уравновешивания между углом поворота вала СКВТ 9 и кодом реверсивного счетчика 10. Сущность подавления переходных процессов состоит в одновременной со скачками амплитуды и фазы компенсирующего напряжения подачей на селективный фильтр 23 четверок импульсов, компенсирующих фазовые и амплитудные переходные процессы. Эти импульсы формируются из выходных напряжений формирователей 5 и 6 формирователями 22 и 21 соответственно. 3 з.п. ф-лы, 7 ил.

фигА

п

n

n Л

U f

n ,J

JLJ

Фиг. 5

Фив. 7

| Автоклав для пропитки пористых изделий | 1975 |

|

SU564922A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1987-04-01—Подача