1

(21)4398693/21

(22)29.03.88

(46) 07.03.9b Бюл. № 9

(71)Харьковский авиационный институт им. Н.Е.Жуковского

(72)В.А.Писарев, Л.А.Краснов, В.И.Шульгин и А.П.Каркж

(53)621 317(088.8)

(56)Авторское свидетельство СССР № 1013867, кл. С 01 R 23/00, 1983.

Авторское свидетельство СССР № 868690, кл G 04 F 10/00, 1981.

(54)УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ

(57)Изобретение относится к радноиз- мерительной технике и может быть использовано для измерения частоты

при анализе радиолокационной информации в системах связи, телеметрии,

системах радионавигации и технике траекторных измерений. Целью изобретения является повышение достоверности. Устройство для измерения частоты содержит формирователь 1 пересечений нуля, формирователь 2 чисел, соответствующих командам пересечений нуля, последовательно соединенные блок 3 управления,блоки 4 и 5 памяти, последовательно соединенные буферный регистр 6,решающий блок 7 и накапливающий сумматор 8. Повышение достоверности достигается тем, что оценка периода (частоты) измеряемого сигнала формируется по приходу каждого сигнала пересечения нуля. При этом уменьшается смещение оценки информационного параметра, повышается час- тотасреза , 4 ил.

S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения периода и его производной | 1980 |

|

SU868690A1 |

| Адаптивный измеритель параметров сигнала | 1981 |

|

SU970251A1 |

| Устройство для магнитно-импульсной обработки деталей | 1973 |

|

SU470251A1 |

| Адаптивный цифровой измеритель параметров сигнала | 1981 |

|

SU1013867A1 |

| Цифровой панорамный измеритель частоты | 1980 |

|

SU930150A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Устройство для оценки достоверности результатов измерений | 1987 |

|

SU1441441A1 |

| Устройство для цифровой обработкиСигНАлОВ | 1979 |

|

SU834559A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

СЭ

со со

со о

СП

Фиг 1 .

Изобретение относится к радиоизмерительной технике и предназначено для измерения частоты при анализе радиолокационной информации в системах связи, телеметрии, системах радионавигации и технике траекторных измерений.

Цель изобретения - повышение достоверности.

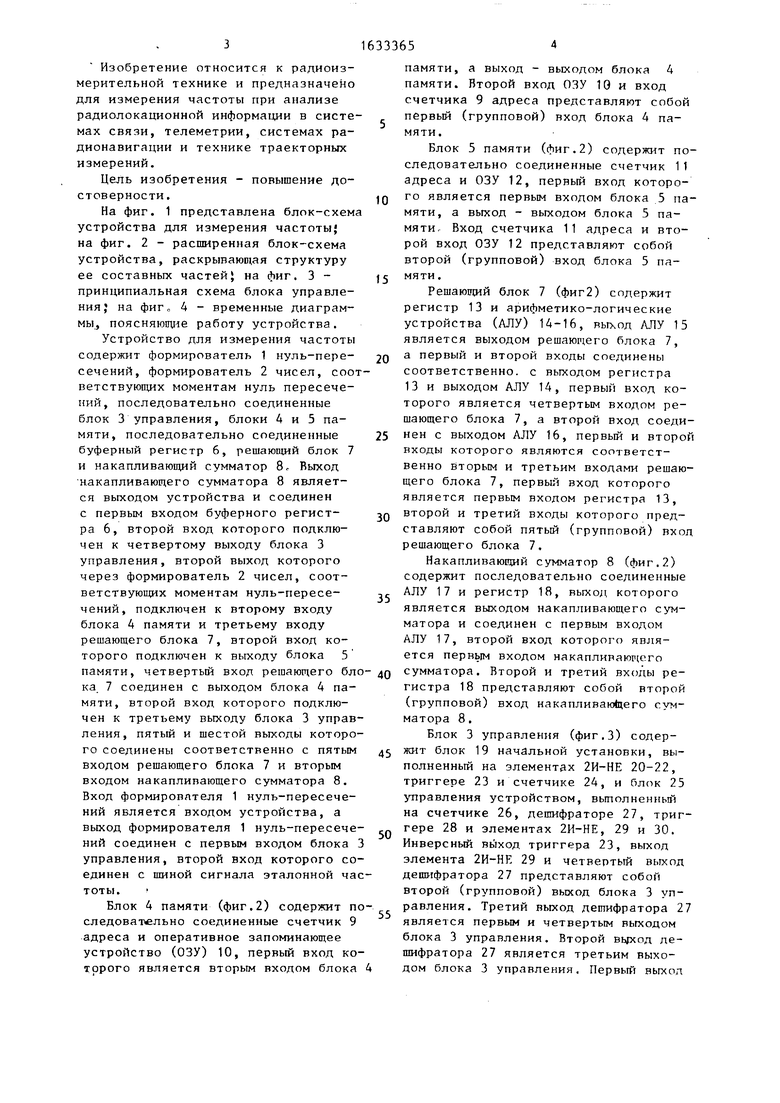

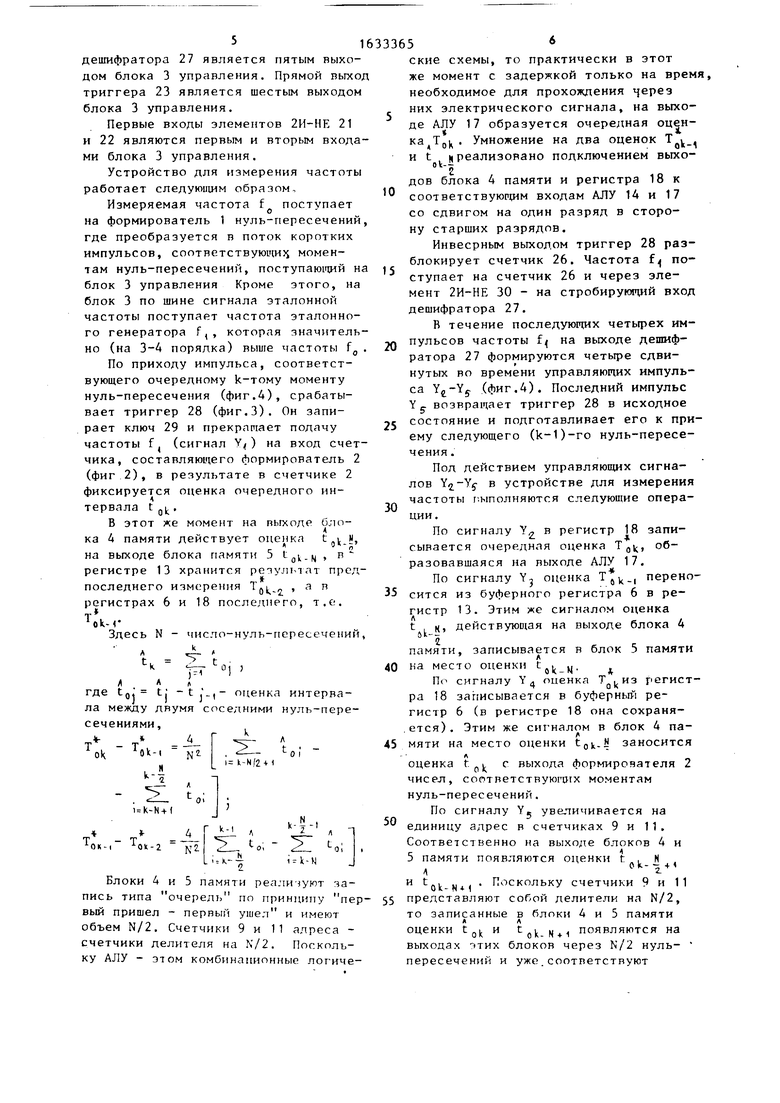

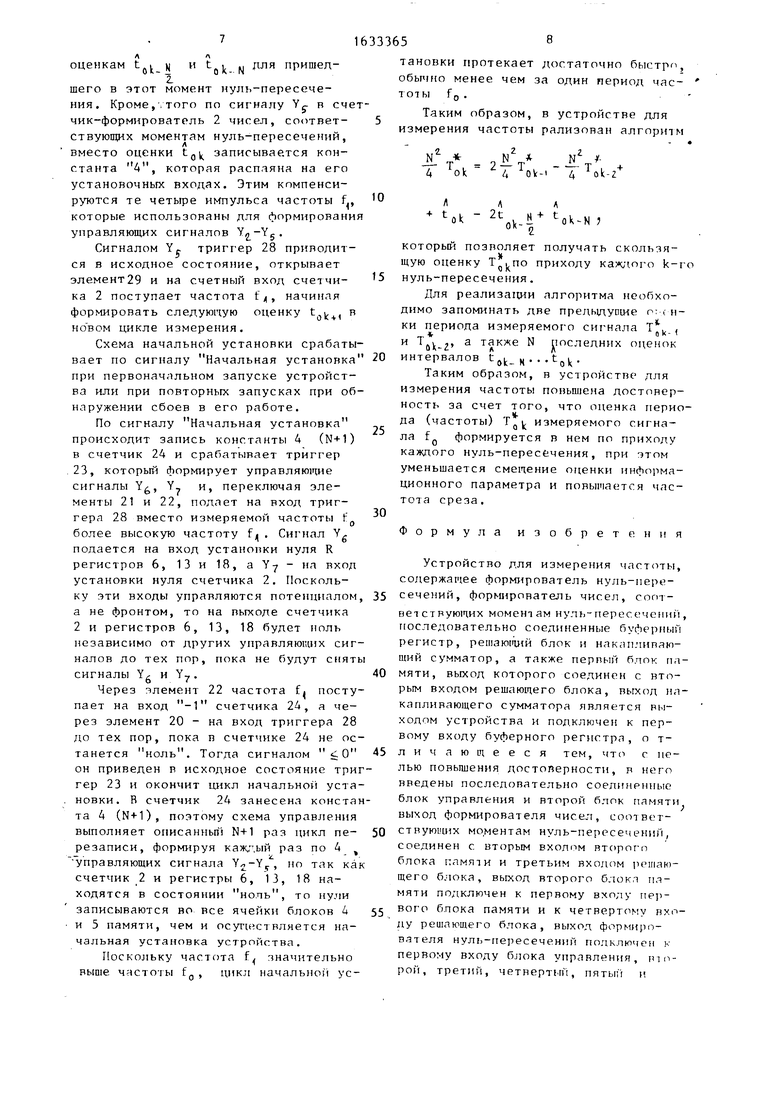

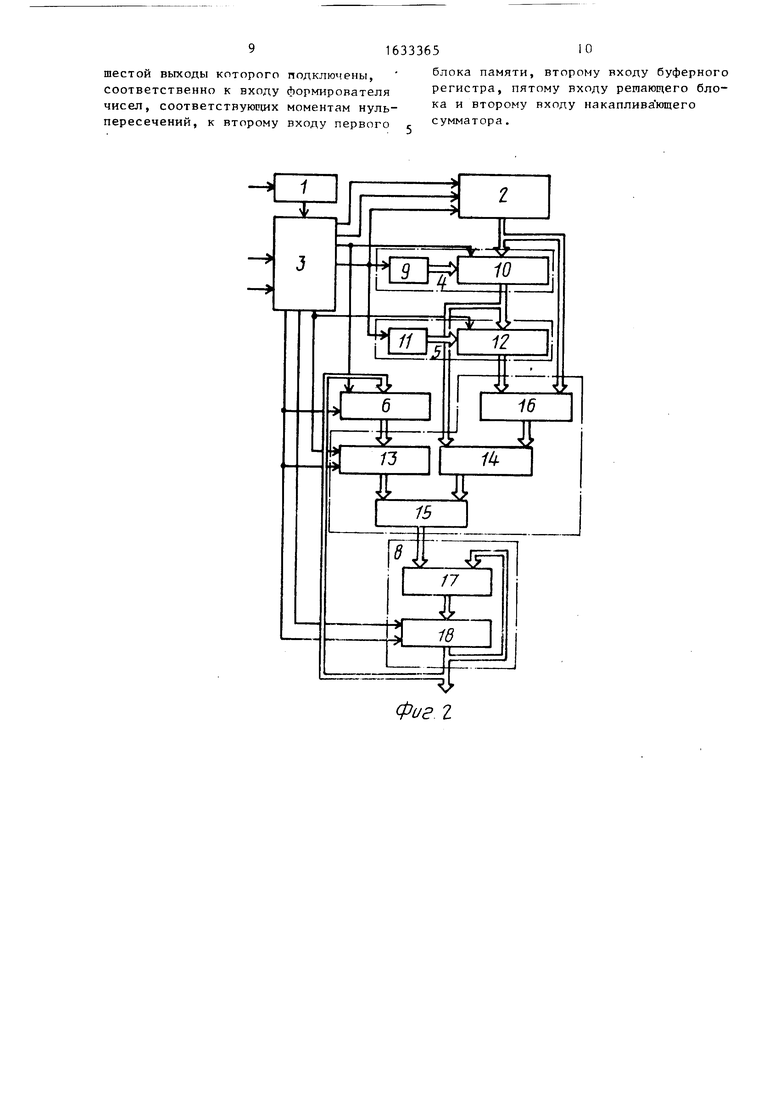

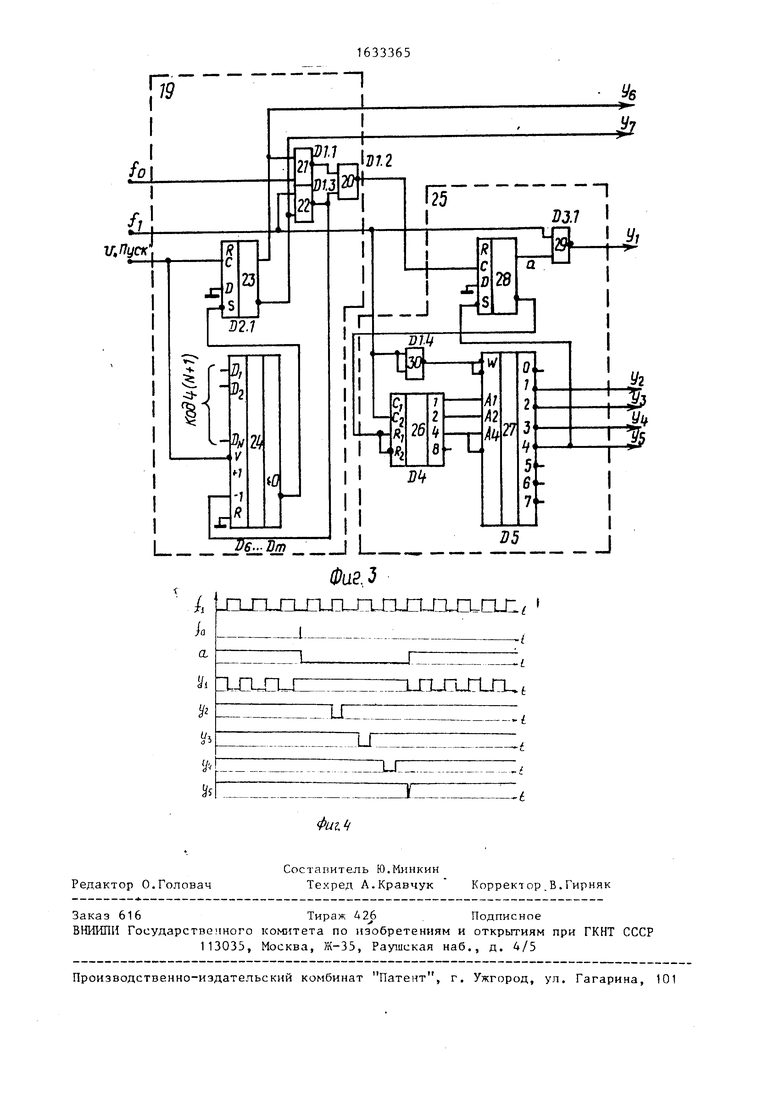

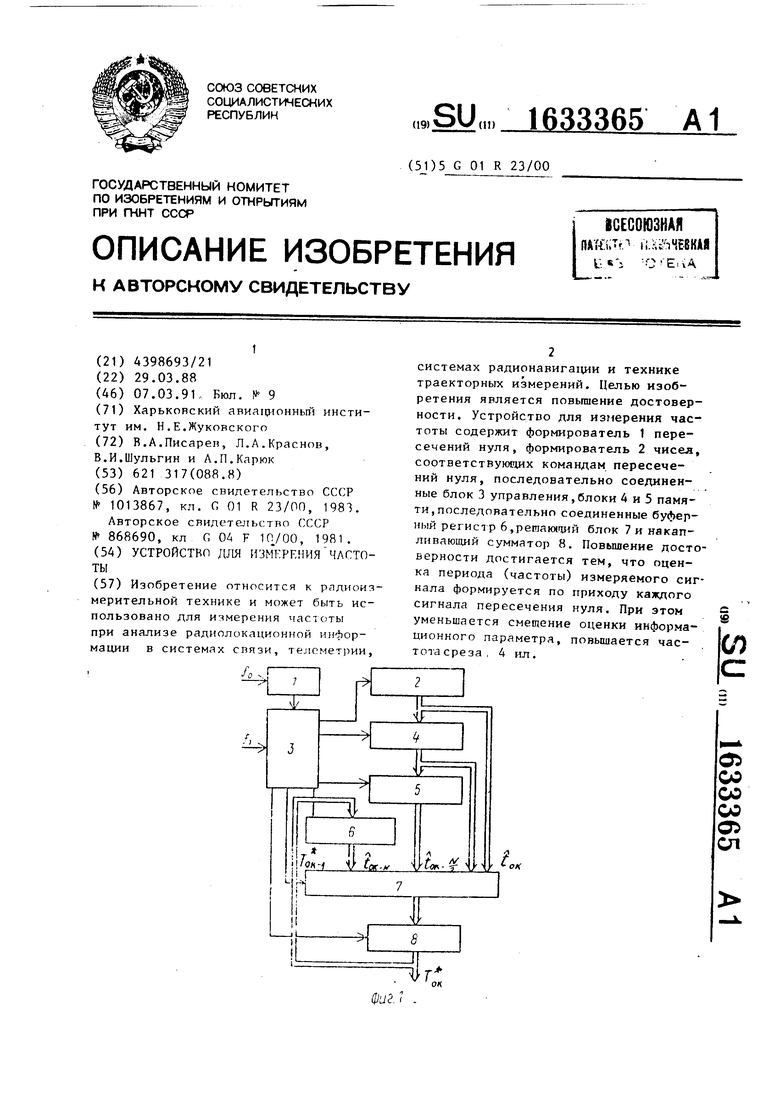

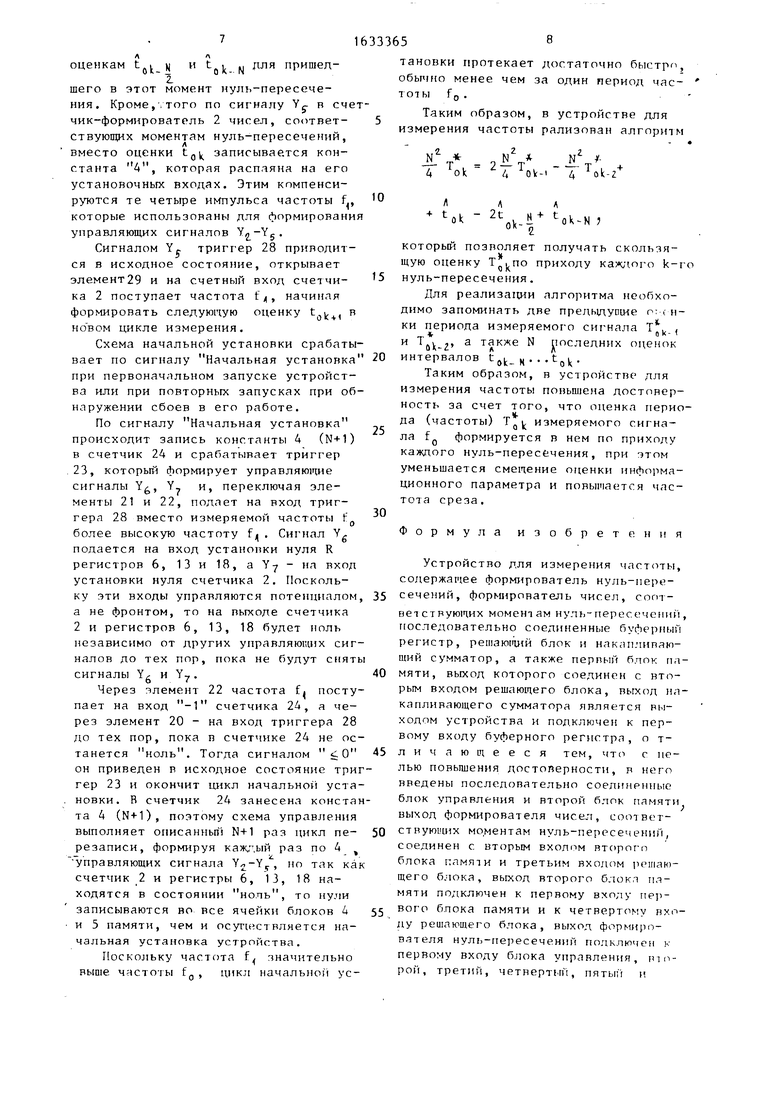

На фиг. 1 представлена блок-схема устройства для измерения частоты; на фиг. 2 - расширенная блок-схема устройства, раскрывающая структуру ее составных частей на фиг. 3 - принципиальная схема блока управления; на фиг„ 4 - временные диаграм- мы3 поясняющие работу устройства.

Устройство для измерения частоты содержит формирователь 1 нуль-пере- сечений, формирователь 2 чисел, соответствующих моментам нуль пересечений, последовательно соединенные блок 3 управления, блоки А и 5 памяти, последовательно соединенные буферный регистр 6, решающий блок 7 и накапливающий сумматор 8, Выход накапливающего сумматора 8 является выходом устройства и соединен с первым входом буферного регист- ра 6, второй вход которого подключен к четвертому выходу блока 3 управления, второй выход которого через формирователь 2 чисел, соответствующих моментам нуль-пересе- чений, подключен к второму входу блока 4 памяти и третьему входу решающего блока 7, второй вход которого подключен к выходу блока 5 памяти, четвертый вход решающего бло ка 7 соединен с выходом блока 4 памяти, второй вход которого подключен к третьему выходу блока 3 управления, пятый и шестой выходы которого соединены соответственно с пятым входом решающего блока 7 и вторым входом накапливающего сумматора 8. Вход формирователя 1 нуль-пересечений является входом устройства, а выход формирователя 1 нуль-пересече- ний соединен с первым входом блока 3 управления, второй вход которого соединен с шиной сигнала эталонной частоты.

Блок 4 памяти (фиг.2) содержит последовательно соединенные счетчик 9 адреса и оперативное запоминающее устройство (ОЗУ) 10, первый вход которого является вторым входом блока

5 ,.

5

памяти, а выход - выходом блока 4 памяти. Второй вход ОЗУ 10 и вход счетчика 9 адреса представляют собой первый (групповой) вход блока 4 памяти.

Блок 5 памяти (фиг.2) содержит последовательно соединенные счетчик 11 адреса и ОЗУ 12, первый вход которого является первым входом блока 5 памяти, а выход - выходом блока 5 памяти. Вход счетчика 11 адреса и второй вход ОЗУ 12 представляют собой второй (групповой) вход блока 5 памяти.

Решающий блок 7 (фиг2) содержит регистр 13 и арифметико-логические устройства (АЛУ) 14-16, выход АЛУ 15 является выходом решающего блока 7, а первый и второй входы соединены соответственно, с выходом регистра 13 и выходом АЛУ 14, первый вход которого является четвертым входом решающего блока 7, а второй вход соединен с выходом АЛУ 16, первый и второй входы которого являются соответственно вторым и третьим входами решающего блока 7, первый вход которого является первым входом регистра 13, второй и третий входы которого представляют собой пятый (групповой) вход решающего блока 7,

Накапливающий сумматор 8 (фиг.2) содержит последовательно соединенные АЛУ 17 и регистр 18, выход которого является выходом накапливающего сумматора и соединен с первым входом АЛУ 17, второй вход которого является первым входом накапливающего сумматора. Второй и третий входы регистра 18 представляют собой второй (групповой) вход накапливающего сумматора 8.

Блок 3 управления (фиг.З) содержит блок 19 начальной установки, выполненный на элементах 2И-НЕ 20-22, триггере 23 и счетчике 24, и блок 25 управления устройством, выполненный на счетчике 26, дешифраторе 27, триггере 28 и элементах 2И-НЕ, 29 и 30. Инверсный выход триггера 23, выход элемента 2И-НЕ 29 и четвертый выход дешифратора 27 представляют собой второй (групповой) выход блока 3 управления. Третий выход дешифратора 27 является первым и четвертым выходом блока 3 управления. Второй выход дешифратора 27 является третьим выходом блока 3 управления. Первый выход

дешифратора 27 является пятым выходом блока 3 управления. Прямой выхо триггера 23 является шестым выходом блока 3 управления.

Первые входы элементов 2И-НЕ 21 и 22 являются первым и вторым входами блока 3 управления.

Устройство для измерения частоты работает следующим образом,

Измеряемая частота f поступает на формирователь 1 нуль-пересечений где преобразуется в поток коротких импульсов, соответствующих, моментам нуль-пересечений, поступающий н блок 3 управления Кроме этого, на блок 3 по шине сигнала эталонной частоты поступает частота эталонного генератора f(, которая значительно (на 3-4 порядка) выше частоты f0

По приходу импульса, соответствующего очередному k-тому моменту нуль-пересечения (фиг.4), срабатывает триггер 28 (фиг.З). Он запирает ключ 29 и прекращает подачу частоты f (сигнал Y, ) на вход счетчика, составляющего формирователь 2 (фиг 2), в результате в счетчике 2 фиксируется оценка очередного интервала С .

В этот же момент на выходе блока 4 памяти действует оценка t ,, N

на выходе блока памяти

оценка

сЛ-N

Чвпредрегистре 13 хранится результат последнего измерения Toki , а п регистрах 6 и 18 последнего, т.е.

Tok-r

Здесь N - число-нуль-пересечений

k

А

t. Т t.

-Г 01

-

где

АЛл

t0j t: -tj ,- оценка интервала между двумя соседними нуль-пересечениями,

Т- - lul-

д

N

1 k-N|2 + 1

О I

Г

(

о

K-i

- Т

ОК-2

J

N2.

k-l

-5N9

Uk-ц

за- перБлоки 4 и 5 памяти реали уют пись типа очередь по принципу вый пришел - первый ушел и имеют объем N/2. Счетчики 9 и 11 адреса - счетчики делителя на N/2. Поскольку АЛУ - этом комбинационные логиче

5

0

5

0

ские схемы, то практически в этот же момент с задержкой только на время, необходимое для прохождения через них электрического сигнала, на выходе АЛУ 17 образуется очередная оценка АТо1 . Умножение на два оценок Т

и t ц реализовано подключением выхоOV Ј

дов блока 4 памяти и регистра 18 к соответствующим входам АЛУ 14 и 17 со сдвигом на один разряд в сторону старших разрядов.

Инвесрным выходом триггер 28 разблокирует счетчик 26. Частота f поступает на счетчик 26 и через элемент 2И-НЕ 30 - на стробирующий вход дешифратора 27.

В течение последующих четырех импульсов частоты f на выходе дешифратора 27 формируются четыре сдвинутых во времени управляющих импульса

-г

Y- возвращает триггер 28

Ye-Yj. (фиг.4). Последний импульс

возвращает триггер 2В в исходное состояние и подготавливает его к приему следующего (k-l)-ro нуль-пересечения .

Пол действием управляющих сигналов в устройстве для измерения частоты г.ыполняются следующие операции.

По сигналу Y в регистр 18 записывается очередная оценка Т0и, об0

разовавшаяся на выходе АЛУ 17.

По сигналу Y оценка Tek, перено- 5 сится из буферного регистра 6 в регистр 13. Этим же сигналом оценка

t к, действующая на выходе блока 4

sk-

памяти, записывается в блок 5 памяти 0 на место оценки (.

По сигналу Y оценка То)из регист- 18 записывается в буферный рерагистр

18 она

сохраня- па6 (в регистре

ется). Этим же сигналом в блок 4 5 мяти на место оценки t.N заносится

А

оценка t а с выхода формирователя 2 чисел, соответствующих моментам нуль-пересечений.

По сигналу Y5 увеличивается на единицу адрес в счетчиках 9 и 11. Соответственно на выходе блоков 4 5 памяти появляются оценки

А

и Поскольку счетчики 9 и 11 5 представляют собой делители на N/2, то записанные в блоки 4 и 5 памяти

А

оценки tok и tok N + 1 появляются на выходах ттих блоков через N/2 нуль- пересечений и уже соответствуют

и

4t-4+,

оценкам t ц и i для пришед 2.

шего в этот момент нуль-пересечения. Кроме,-, того по сигналу Yg- в счетчик-формирователь 2 чисел, соответствующих моментам нуль-пересечений, вместо оценки 10 записывается константа 4, которая распаяна на его установочных входах. Этим компенсируются те четыре импульса частоты f., которые использованы для формирования управляющих сигналов

Сигналом YC триггер 28 приводится в исходное состояние, открывает элемент29 и на счетный вход счетчика 2 поступает частота f, начиная

оценку tolui в

тановки протекает достаточно быстрп, обычно менее чем за один период часТ ОТЫ Г0 .

Таким образом, в устройстве для измерения частоты рализован алгоритм

2 NZ N2 1-Т - 9 - Т -Ј т j.

Lok г д V- 4 Tok-z

10

ok

2Vf ok-N,

15

который позволяет получать скользящую оценку Т .по приходу каждого k-r

нуль-пересечения.

Для реализации алгоритма необходимо запоминать две предыдущие о-. ( нформировать следующую новом цикле измерения.

Схема начальной установки срабатывает по сигналу Начальная установка 20 интервалов t0|c N . . . tQ

Таким образом, в устройстве для измерения частоты повышена достоверки периода измеряемого сигнала и Т.. ,, а также N последних оценок

О К I-

при первоначальном запуске устройства или при повторных запусках при обнаружении сбоев в его работе.

По сигналу Начальная установка происходит запись константы 4 (N+1) в счетчик 24 и срабатывает триггер 23, который формирует управляющие сигналы YЈ, Y- и, переключая элементы 21 и 22, подает на вход триггера 28 вместо измеряемой частоты более высокую частоту f . Сигнал Yg подается на вход установки нуля R регистров 6, 13 и 18, a Yy - на вход установки нуля счетчика 2. Посколь25

30

ность за счет того, что оценка перио да (частоты) Тд измеряемого сигнала f формируется в нем по приходу каждого нуль-пересечения, при этом уменьшается смещение оценки информационного параметра и повышается частота среза.

Формула изобретения

Устройство для измерения частоты, содержащее формирователь нуль-переку эти входы управляются потенциалом, 35 сечений, формирователь чисел, соот- а не фронтом, то на выходе счетчика 2 и регистров 6, 13, 18 будет ноль независимо от других управляющих сигналов до тех пор, пока не будут сняты

ветствующих моментам нуль-пересечений последовательно соединенные буферный регистр, решающий блок и накапливающий сумматор, а также первый блок памяти, выход которого соединен с вторым входом решающего блока, выход накапливающего сумматора является выходом устройства и подключен к первому входу буферного регистра, о т- личающееся тем, ч TCI с целью повышения достоверности, в него введены последовательно соединенные блок управления и второй блок памяти выход формирователя чисел, соответствующих моментам нуль-пересечений, соединен с вторым входим второго блока памяти и третьим входом решающего блока, выход второго блока памяти подключен к первому входу первого бпока памяти и к четвертому входу решающего блока, выход формирователя нуль-пересечений подключен к первому входу блока управления, второй, третий, четвертый, пятый и

сигналы Y6 и Y.

Через элемент 22 частота f поступает на вход -1 счетчика 24, а через элемент 20 - на вход триггера 28 до тех пор, пока в счетчике 24 не останется ноль. Тогда сигналом с 0 он приведен в исходное состояние триггер 23 и окончит цикл начальной установки. В счетчик 24 занесена константа 4 (N+1), поэтому схема управления выполняет описанный N+1 раз цикл пе- резаписи, формируя каждый раз по 4 % управляющих сигнала Y2-Y, но так как счетчик 2 и регистры 6, 13, 18 находятся в состоянии нопь, то нули записываются во все ячейки блоков 4 и 5 памяти, чем и осуществляется начальная установка устройства.

Поскольку частота f значительно

выше частоты f

о

цикл начальной установки протекает достаточно быстрп, обычно менее чем за один период часТ ОТЫ Г0 .

Таким образом, в устройстве для измерения частоты рализован алгоритм

2 NZ N2 1-Т - 9 - Т -Ј т j.

Lok г д V- 4 Tok-z

10

ok

2Vf ok-N,

который позволяет получать скользящую оценку Т .по приходу каждого k-ro

нуль-пересечения.

Для реализации алгоритма необходимо запоминать две предыдущие о-. ( нинтервалов t0|c N . . . tQ

ки периода измеряемого сигнала и Т.. ,, а также N последних оценок

О К I-

ность за счет того, что оценка периода (частоты) Тд измеряемого сигнала f формируется в нем по приходу каждого нуль-пересечения, при этом уменьшается смещение оценки информационного параметра и повышается частота среза.

Формула изобретения

Устройство для измерения частоты, содержащее формирователь нуль-пересечений, формирователь чисел, соот-

ветствующих моментам нуль-пересечений, последовательно соединенные буферный регистр, решающий блок и накапливающий сумматор, а также первый блок памяти, выход которого соединен с вторым входом решающего блока, выход накапливающего сумматора является выходом устройства и подключен к первому входу буферного регистра, о т- личающееся тем, ч TCI с целью повышения достоверности, в него введены последовательно соединенные блок управления и второй блок памяти выход формирователя чисел, соответствующих моментам нуль-пересечений, соединен с вторым входим второго блока памяти и третьим входом решающего блока, выход второго блока памяти подключен к первому входу первого бпока памяти и к четвертому входу решающего блока, выход формирователя нуль-пересечений подключен к первому входу блока управления, второй, третий, четвертый, пятый и

шестой выходы которого подключены, соответственно к входу формирователя чисел, соответствующих моментам нуль- пересечений, к второму входу первого

-

1633365Ю

блока памяти, второму входу буферного регистра, пятому входу решающего блока и второму входу накапливающего сумматора.

Фиг I

Ј °i

ГЧ

-

Авторы

Даты

1991-03-07—Публикация

1988-03-29—Подача