(54) УСТРОЙСТВО ДЛЯ ЦИФРОВСЙ .ОБРАБОТКИ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой панорамный измеритель частоты | 1980 |

|

SU930150A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Измеритель коэффициента шума | 1988 |

|

SU1524014A1 |

| Цифровой обнаружитель-измеритель частоты | 1988 |

|

SU1597760A2 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Цифровой панарамный измеритель частоты | 1982 |

|

SU1048420A1 |

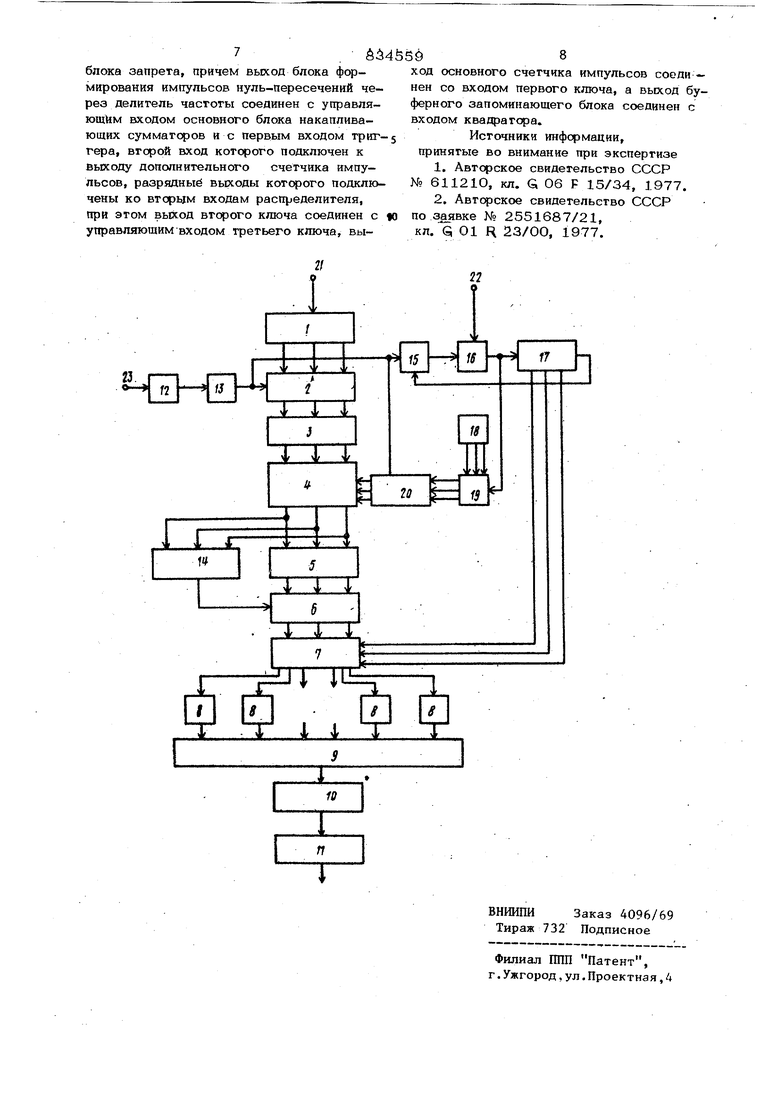

Изобретение относится к радиоизмери- гельной технике и может быть использова но в радиолокации, радионавигации и, в частности, в радиотехнических системах траектсрных измерений для измерения .час тоты и запаздывания радиримпульснсто сигнала. Известно устройство обработки сигналов, содержащее М каналов преобразовани сигналов в цифровую форму, квадратурный генератор, генератор дискретизации, вычислитель, квадратор; интерполятор fl. Недостатком устройства является снижение точности измерения частоты при уменьшении длительности радиоимпульсног входного сигнала. Наиболее близкий по техническсй сущности к предлагаемому устройству цифровой панорамный измеритель частоты содержит последовательно соединенные генератор тактовых импульсов, счетчик импул сов, стробицируемый дешифратор, запоминающий блок, блок сумматоров, квадратор и решающий блок, а также блок формирования, импульсов нулей, выход которого подключен к первому входу стробируемого дешифратора Гз. Недостстком устройства является нвэ- кая точность измерения частоты коротко го радиоимпульса в случае, если момент прихода его точно не известен, так как в этом случае устройство должно орт анвзовывать измерения на временном интервале, значительно превышающем длителЕ носгь информационного импульса. Цель изобретения - повышение точности измерений несущей частоты сигнала известной формы при случайном времени его прихода. Поставленная цель достигается тем, что в устрсАство для цифровой обработки сигналов, содержащее основной запсм ннающий блок, блок формирования импульсов нуль-пересечений, основной счетчик импульльсов, основной блок накапливающих сумматоров, квадратор, выход которого подключен ко входу решающего блока, дополнительно введены последовательно соеднненные делитель частоты, первый ключ, буферный регистр, блок вычитания, блок сравнения, блок загфета, распределитель, блоки накапливающих сумматоров и буферный запоминающий блок, последовательно соединенные триггер, втqэoй ключ и счетчик импульсов, а также последовательно соединенные запоминающий блок и третий ключ, выходы которого через основной бло накапливающих сумматоров подключены ко вторым рходам блока вычитания, выходы КОТОР9ГО через основной запоминающий блок соединены с входами блока запрета, причем выход блока формирования импульсов нуль-пересечений через делитель частоты .соединения с управляпющим входом блока накапливающих сумматоров и с первым входом триггера, второй. вход которого подключен к выходу дополнительного счетчика импульсов, разрядные выходы которого подключены ко вторым входам рас-пределителя, при этом выход второго ключа соединен с управляющим входом тре тьего ключа, выход основного счетчика импульсов соединен со входом первого ключа, а выход буферного запоминающего блока соединен с входом квадратора. На чертеже представлена структурная схема устройства для цифровой обработки сигналов. Устройство для цифровой обработки сиг налов содержит счетчик 1, первый ключ 2 буферный регистр 3, блок 4 вычитания, запоминающий блок 5, блок 6 запрета, распределитель 7, блоки 8 накапливаююших сумматоров, буферный запоминающий блок 9, квадратор Ю, решающий блок 11 блок 12 фсрмирования импульсов нуль-пересечений, делитель 13 частоты, блок 14 сравнения, триггер 15, второй ключ 16, дополнительный счетчик 17, дополнительный запоминающий блок 18, третий ключ 19, блок 2О накапливающих сумматоров. На чертеже также показаны шины 21 и 22 опорной и тактовой частоты, щина 23 измерительного сигнала. Устройство работает следующим обраэом. В момент начала измерения О счетчик 1, счетчик 17 и блоки 8 накапливающих сумматоров находятся в йсход ном состоянии О. На входы счетчика 1 ключа 16 начинают поступать с шин 21 н 22 импульсы счетной и гактовсй частот В течение интервала наблюдения Т Т на mmiy 23 формирователя 12 поступает измерительный сигнал 0(t), представляюший собой аддитивную смесь узкопсяосной помехи ri(fc) и импульснся о ян ормационного радиосигнала S (-t) известной формы длительностью Т, .Формирователь 12 вырабатывает короткие импульсы в моменты положительного перехода измеительного .сигнала через нулевую ось амплитуд, которые делителем 13 прореживаются в п раз, п выбирается из условия -I W Импульс с выхода делителя 13 открывает на короткий временной Интервал ключ 2, через который в буферный регистр 3 с выхода счетчика 1 переписьшается число, зарегистрированное им от начала интервала наблюдения до соответствующего нуль-пересечений; i . Одновременно импульсом устанавливается в состо« «е 0° блок 2О накапливающих сумматфов, а триггер 15 в состояние 1.Ключ 16 открывается и через него на счетный вход счетчика 17 я на управляющий вход ключа 19 начинают поступать импульсы тактовой частоты. Счетчик 17, ведущий счет по модулю М, формирует на своих выходах управляющий код для адресных шин распределителя 7. При полном заполнении счетчика- 17 вьфабатывается сигнал, который устанавливает триггер 15 в состояние О и ключ 16 закрьшается. Тактовая частота в предлагаемом устройстве для цифрового анализа сигналов выбирается так, чтобы полное заполнение счетчи- ка 17 всегда завершалось до прихода очередного импульса нуль-пересечения с выхода делителя 13. В момент прихода импульса нуль-пересечения с выхода целителя 13 триггер 15 устанавливается б состояние 1, вследствие чего ключ 16 открывается. Первьгй пришедщий импульс тактовой частоты поступает на вход счетчика 17, а также открьшает на время .,т ключ 19, -41ч , В результате в блоке 20 накапливающих сумматоров путем сложения с содержимым формируется вычитаемое tT, аргумента импульсной характеристики, которое с помощью блока 4 вьинтания вычитается из содержимого буферного регистра 3. Результат вычитания, определжпощий строки данных запоминающего блока 5, поступает rjta адресные шины запоминающего блока 5, вследствие чего гфойзводнтся чтение нужной строки данных. Если блок 6 запрета открыт, данные через блок загпэета н распределитель 7 поступают на вход первого из блоков S накааливаю щих сумматоров, где и осуществляется сложение. Блок б запрета, управляемый блоком 11 сравнения, закрыт в случае, если вы численный аргумент импульсной характер стики X ) не удовлетворяет хотя бы одному из условий ; При закрытом блоке 6 запрета данные на 1вход одного из блоков 8 накапливающих сумматоров соответствующего анализи руемой задержки д С , не поступают. С приходом очередного тактового импульса содержимое счетчика 17 увеличивается на 1, а константа, формируемая в блоке 20 накапливающих сумматоров, - н величину шага изменения задержки Ди . К адресным шинам распределителя 7 прикладывается следующее (по отношению к предыдущему показанию счетчика 17) дво ичное число, вследствие чего выход распределителя подключается ко входу очередного из блоков 8 накапливающих сумматоров, С помощью блока 4 вычитания формируется адрес читаемой строки данны которая (в случае, если блок 6 запрета открыт) суммируется с содержимым очеродного из блоков 8 накапливающих сумматоров. Блок 6 запрета как и на предыдущем этапе закрыт лищь в случае невыполнения ограничений, накладываемых н аргумент импульсной характеристики. Описанная процедура для фиксированног нуль-пересечения смеси сигнала и шума t пoвтqэяeтcя для всех М анализируемы значений задержки, С учетом аппаратурной задержки после прихода М-гр тактово го импульса счетчик 17 ведущий счет по модулю И и триггер 15 устанавливаются в положение О и ключ 16 закрьшается. Ус1-ройстпо переходит в режим ожидания прихода очередного импульса нуль-Пересе чения с выхода делителя 13. С приходом очередного импульса цикл формирований аргумента импульсной характеристики для различных дискретных задержек проверки выполнения условий на сфсрмироваиный аргумент и сложения данных соответ ствующих строк запоминающего блока 5 с содержимым блоков 8 накапливающих сумматсров повторяется. По окончании интервала наблюдения Тц отсчет1)Г комплексного выходного эф фекта ) о всем М частотам переписьтаются из FIOKOB 8 накапливающих сумматоров в буферный запоминающий блок 9. В квадраторе Ю на основе каждого комплексного отсчета ) формируется действительный отсчет вькодного эффекта Т(Те ), .после чего цикл накопления комплексных отсчетов выходного эффекта повторяется на следующем интервале наблюдения, Вычисленные отсчеты .{ ( )} переписываются далее в решающий блок 11, где на основе энализа всех отсчетов делается вывод о присутствии информационного импульсного сигнала в один из дискретных моментов времени Т интервала наблюдения на одной из Ntf анализируемых частот. Таким путем формируется искомая оценка задержки и несущей частоты измерительного сигнала. Устройство обеспечивает повьпиение точности измерения несущей частоты сигнала известной формы при неизвестном времени его прихода. Структура предлагаемого устройства позволяет организовать (при приемлемом на практике аппаратурном объеме) высокоточные измерения в реальном масштабе времени с быстродействием, близким к быстродействию аналоговьк измерителей. Формула изобретения Устройство для цифровой обработки сигналов, содержащее основной запоминающийблок, блок формирования импульсов нульпересечений, основной счетчик импульсоб, основной блок накапливающих сумматоров, квадратор, выход которого подключен ко входу решающего блока, отличающееся тем, что, с целью повышения точности измерения несущей частоты ctir- нала известной формы при случайном времени его прихода, в него дополнительно введены последовательно соединенные де- литель частоты, первый ключ, буферный регистр, блок вычитания, блок сравнения, блок запрета, распределитель, блоки накапливающих сумматоров и буферный з.апоминающий блок, последовательно соединеные триггер, второй ключ и Дополнитель- ый счетчик импульсов, а также пос ледоательно соединенные запоминающий блок третий ключ, выходы которого через осовной блок накапливающих сумматоров одключены ко вторым входам блока выитания, выходы которого через основной апоминающий блок соединены с входами блока запрета, причем выход блока формирования импульсов нуль-пересечений че рез делитель частоты соединен с управляющим входом основного блока накапливающих сумматоров и с первым входом триггера, второй вход которого подключен к выходу дополнительного счетчика импульсов, разрядные вькоды которого подключены ко вторым входам распределителя, при этом выход второго ключа соединен с управляющим входом третьего ключа, выe59 ход основного счетчика импульсов соединен со входом первого ключа, а выход буферного запоминающего блока соединен с входом квадратсра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 611210, кл. G, 06 F 15/34, 1977. 2.Авторское свидетельство СССР по заявке № 2551687/21, кп. Q 01 Н 23/00, 1977.

Авторы

Даты

1981-05-30—Публикация

1979-05-10—Подача