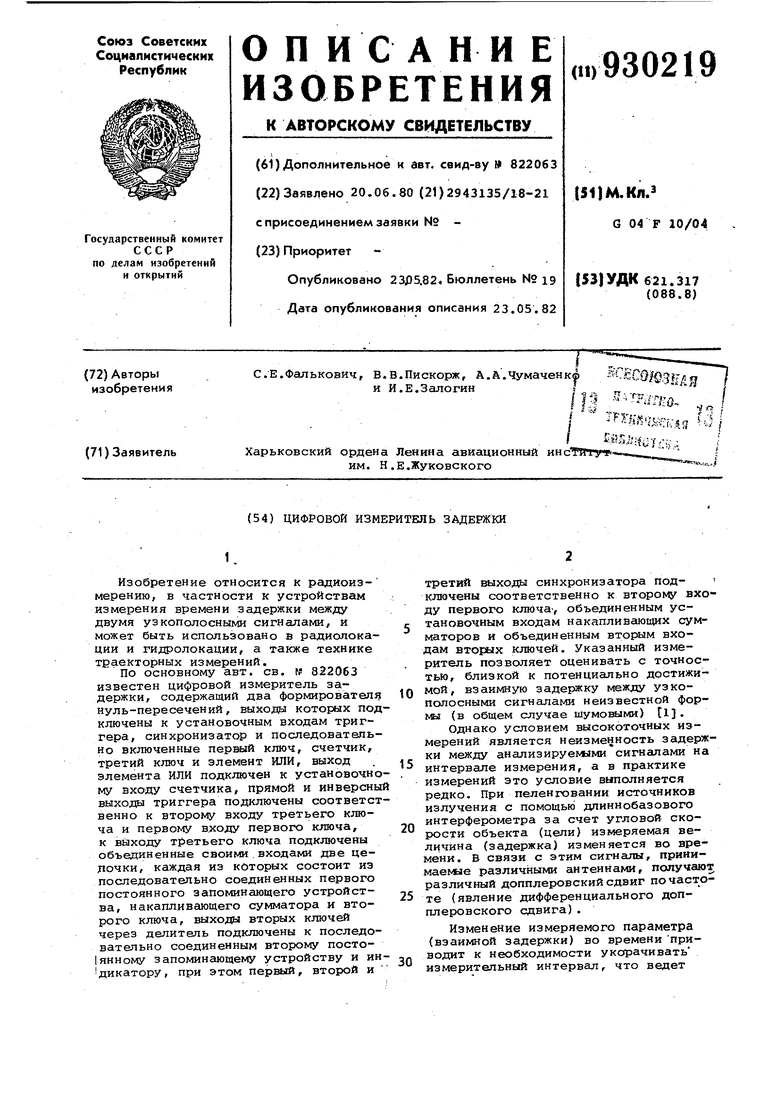

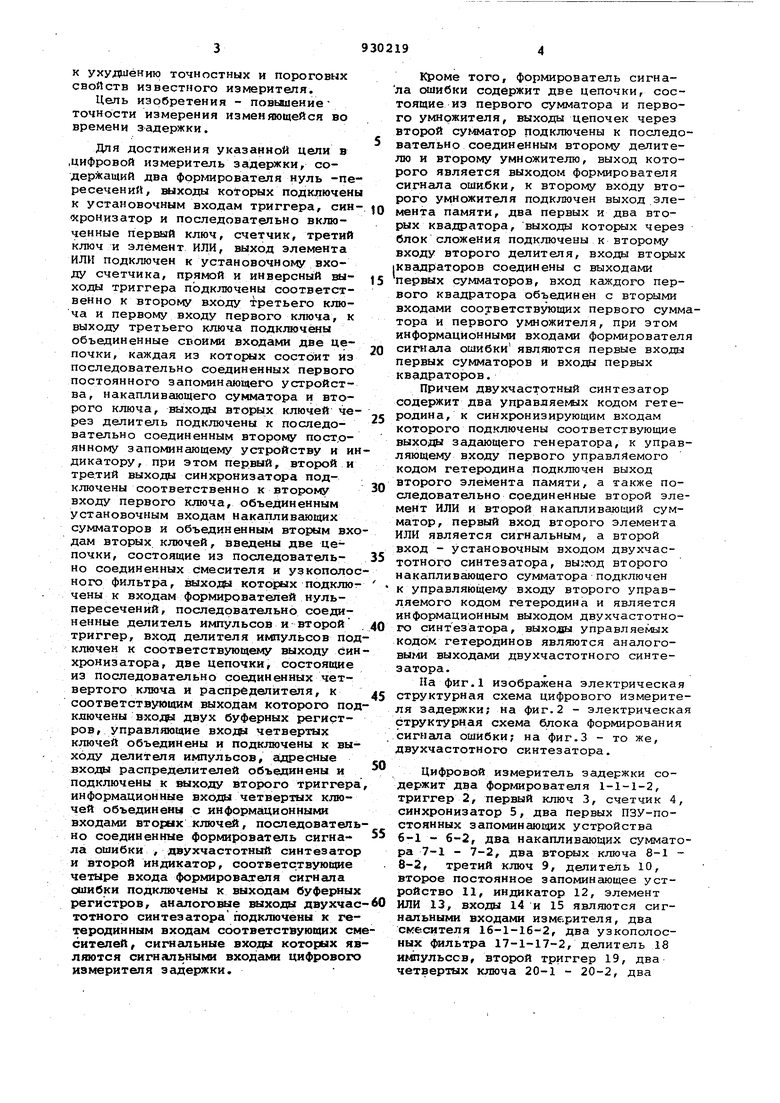

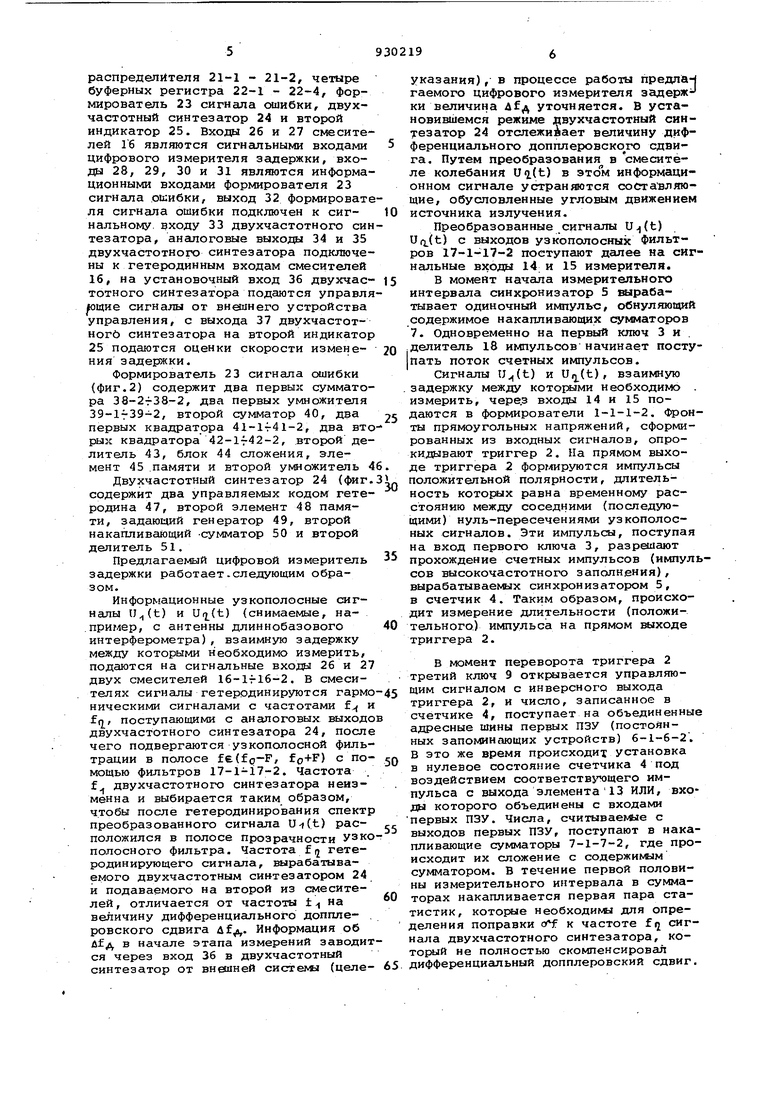

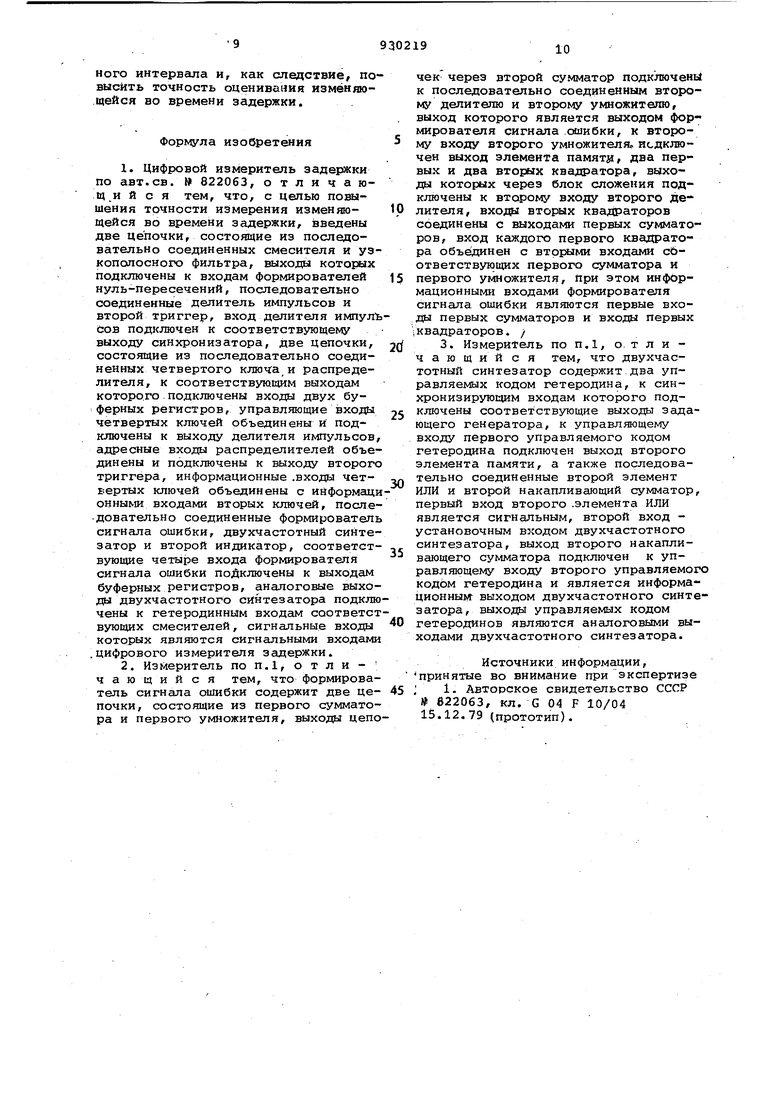

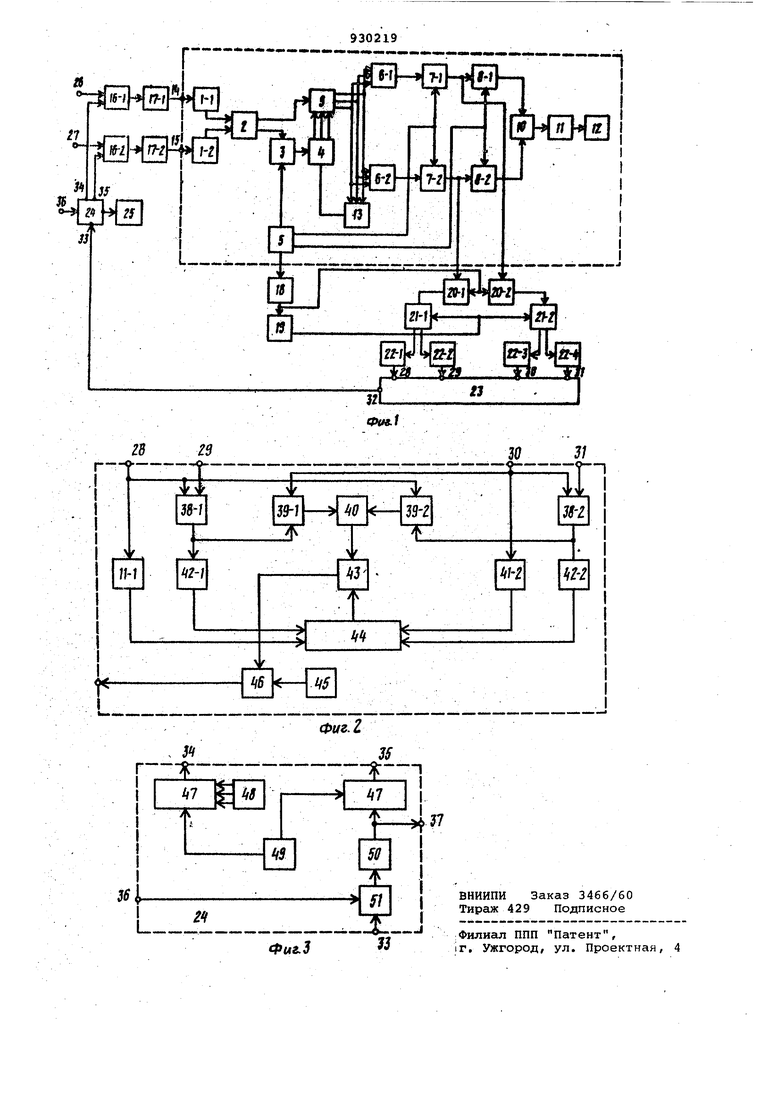

к ухудшению точностных и пороговых свойств известного измерителя. Цепь изобретения - повышениеточности измерения изменяющейся во времени з-адержки. Для достижения указанной цели в .цифровой измеритель задержки, содержащий два форг-гарователя нуль -пересечений, шлходы которых подключены к установочным входам триггера, сии«ронизатор и последовательно включенные первый ключ, счетчик, третий ключ и элемент ИЛИ, выход элемента ИЛИ подключен к установочному входу счетчика, прямой и инверсный выходы триггера подключены соответственно к второму входу третьего ключа и первому входу первого ключа, к выходу третьего ключа подключены объединенные своими входами две цепочки, каждая из которых состоит из последовательно соединенных первого постоянного запоминающего устройства, накапливающего сумматора и второго ключа, выходы вторых ключей через делитель подключены к последовательно соединенным второму постоянному запоминающему устройству и ин дикатору, при этом первый, второй и третий выходы синхронизатора подключены соответственно к второму входу первого ключа, объединенным установочным входам накапливающих сумматоров и объединенным вторым вхо дам вторых ключей, введены две цепочки, состоящие из последовательНо соединенных смесителя и узкополо ного фильтра, выходы которых подключены к входам формирователей нульпересечений, последовательно соединенные делитель импульсов и второй триггер, вход делителя импульсов под ключен к соответствзЮщему выходу син хронизатора, две цепочкиj состоящие из последовательно соединенных четвертого ключа и распределителя г к соответствующим выходам которого по ключены входа двух буферных регистров, управляющие входы четвертых ключей объединены и подключены к вы ходу делителя импульсов, адресные входы распределителей объединены и подключены к выходу второго триггер информационные входы четвертых ключей объединены с информационными входами вторых ключей, последовател но соединенные формирователь сигнала ошибки , двухчастотный синтезато и второй индикатор, соответствующие четыре входа1 формировгцгеля сигнала сшибки подключены к выходам буферны регистров, аналоговые выходы двухча тотного синтезатораподключены к ге теродинным входам соответствующих с сителей, сигнальные входы которых я ляются cигнaльны в входами цифровог измерителя задержки. Кроме того, формирователь сигнаа схиибки содержит две цепочки, состоящие из первого сумматора и первого умножителя, выходы цепочек через второй cy Ф1aтpp подключены к последовательно соединенным второму делителю и второму умножителю, выход которого является выходом формирователя сигнала ошибки, к второму входу второго умножителя подключен выход элемента памяти, два первых и два вторых квадратора, выходы которых через блок сложения подключены к второму входу второго делителя, входы вторых Квадраторов соединены с выходами первых сумматоров, вход каждого первого квадратора объединен с вторыми входами соответствующих первого сумматора и первого умножителя, при этом информационными входами формирователя сигнала ошибки являются первые входы первых сумматоров и входы первых квадраторов. Причем двухчастотный синтезатор содержит Два yпpaвляe лыx кодом гетеродина, к синхронизирующим входам которого подключены соответствующие выходы задающего генератора, к управляющему входу первого управляемого кодом гетеродина подключен выход второго элемента памяти, а также последовательно соединенные второй элемент ИЛИ и второй Накапливающий сумматор, первый вход второго элемента ИЛИ является сигнальным, а второй вход - установочным входом двухчастотного синтезатора, второго накапливающего cyMr-iaxopa подключен к управляюще1 1у входу второго управляемого кодом гетеродина и является информационным выходом двухчастотного синтезатора, выходы управянег ых кодом гетеродинов являются аналогоВЫГ/1И выходами двухчастотного синтезатора. На фиг.1 изображена электрическая структурная схема цифрового измерителя задержки; на фиг.2 - электрическая структурная схема блока формирования сигнала ошибки; на фиг.З - то же, двухчастотного синтезатора. Цифровой измеритель задержки содержит два фop 4иpoвaтeля 1-1-1-2, триггер 2, первый ключ 3, счетчик 4, синхронизатор 5, два первых ПЗУ-постоянных запоминающих устройства 6-1 - 6-2, два накапливающих сумматора 7-1 - 7-2, два вторых ключа 8-1 8-2, третий ключ 9, делитель 10, второе постоянное запоминающее устройство 11, индикатор 12, элемент ИЛИ 13, входы 14 И 15 являются сигнальными входами измерителя, два смесителя 16-1-16-2, два узкополосных фильтра 17-1-17-2, делитель 18 импульссв, второй триггер 19, два четвертых ключа 20-1 - 20-2, два распределителя 21-1 - 21-2, четыре буферных регистра 22-1 - 22-4, формирователь 23 сигнала ошибки, двухчастотный синтезатор 24 и второй индикатор 25. Входы 26 и 27 смесите лей Гб являются сигнальными входами цифрового измерителя задержки, входы 28, 29, 30 и 31 являются информа ционными входами формирователя 23 сигнала ошибки, выход 32 формироват ля сигнала ошибки подключен к сигнальному. входу 33 двухчастотного си тезатора, аналоговые выходы 34 и 35 двухчастотного синтезатора подключе ны к гетеродинным входам смесителей 16, на установочный вход 36 двухчас тотного синтезатора подаются управл щие сигналы от внвинего устройства управления, с выхода 37 двухчастотногЪ синтезатора на второй индикато 25 подаются оценки скорости изменения задержки. Формирователь 23 сигнала ошибки {фиг.2) содержит два первых суммато ра 38-2-:-38-2, два первых умножителя 39-lf39-2, второй сумматор 40, два первых квадратора 41-1-;-41-2, два вт рых квадратора 42-lf42-2, второй де литель 43, блок 44 сложения, элемент 45 .памяти и второй умножитель Двухчастотный синтезатор 24 (фиг содержит два управляемых кодом гете родина 47, второй элемент 48 памяти, задающий генератор 49, второй накапливающий -сумматор 50 и второй делитель 51. Предлагаемый цифровой измеритель задержки работает.следующим образом. Информационные узкополосные сигналы n(t) и U() (снимаемые, на.пример, с антенны длиннобазового интерферометра), взаимную задержку между которыми необходимо измерить, подаются на сигнальные входы 26 и 27 двух смесителей 16-lfl6-2. В смесителях сигнсшы гетеродинируются гармо ническими сигналами с частотами f и ffj, поступающими с ангшоговых выходо двухчастотного синтезатора 24, после чего подвергаются узкополосной фильтрации в полосе f6{f(j-F, fo+F) с помощью фильтров 17-1-17-2. Частота f. двухчастотного синтезатора неизменна и выбирается таким образом, чтобы после гетеродинирования спектр преобразованного сигнала tJ-iCt) расположился в полосе прозрачности Узко полосного фильтра. Частота f(j гетеродинирующеГо сигнгша, вырабатываемого двухчастотным синтезатором 24 и подаваемого на второй из смесителей , отличается от частоты ± на величину дифференциального допплеровского сдвига д. Информация об дfд в начале этапа измерений заводит ся через вход 36 в двухчастотный синтезатор от внешней системл (целе- указания) , в процессе работы предлагаемого цифрового измерителя задерж ки величина Afд уточняется. В установившемся режиме явухчастотный синТезатор 24 отслеживает величину дифференциального допплеровско го сдвига. Путем преобразования в смесителе колебания (t) в информационном сигнале устраняются составляющие, обусловленные угловым движением источника излучения. Преобразованные сигналы U(t) Ui(t) с выходов узкополосных фильтров 17-1-17-2 поступают далее на сигнальные входы 14 и 15 измерителя. В момент начала измерительного интервала синхронизатор 5 нарабатывает одиночный импульс, обнуляющий содержимое накапливающих суладаторов 7. Одновременно на первый ключ 3 и |Делитель 18 импульсов начинает посту|пать поток счетных импульсов. Сигналы tJ(t) и Uij(t), взаимную задержку между котогжлми необходимо . измерить, чере.з входы 14 и 15 подаются в формирователи 1-1-1-2. Фронты прямоугольных напряжений, сформированных из входных сигналов, опрокидывают триггер 2. На прямом выходе триггера 2 формируются импульсы положительной полярности, длительность которлх равна временному расстоянию между соседними (последующими) нуль-пересечениями узкополосных сигналов. Эти импульсы, поступая на вход первого ключа 3, разрешают прохождение счетных импульсов (импульсов высокочастотного заполнения), выpaбaтывae ыx синхронизатором 5, в счетчик 4. Таким образом, происходит измерение длительности (положительного,) импульса на прямом выходе триггера 2. В момент переворота триггера 2 третий ключ 9 открывается управляющим сигналом с инверсного выхода триггера 2, и число, записанное в счетчике 4, поступает на объединенные адресные шины первых ПЗУ (постоянных запоминающих устройств) 6-1-6-2. В это же время происходи-г установка в нулевое состояние счетчика 4 под воздействием cooтвeтcтв oщeгo импульса с выхода элемента 13 ИЛИ, входы которого объединены с входами первых ПЗУ. Числа, считываегЛле с выходов первых ПЗУ, поступают в накапливающие сумматоры 7-1-7-2, где происходит их сложение с содержимым сумматором. В течение первой половины измерительного интервала в сумматорах накапливается первая пара статистик, которые необходимы для опрееления поправки а к частоте f ij сигнала двухчастотного синтезатора, который не полностью скомпенсировгш дифференциальный допплеровский сдвиг. Б момоит времени, равный половине измерительного интервала, с выхода делителп 18 импульсов на управляющие входы ключей 20-1-20-2 поступает короткий иишульс, и первая пара статис тик через ключи 20-1-20-2 и распределители 21-1-21-2 переписывается в два буферных регистра 22. Импульс с выхода делителя 18 также (с аппаратурной задержкой) изменяет состояние второго (счетного) триггера 19. Триггер изменяет свое-электрическое состояние, на адресные входы распределителей поступает потенциал определенного уровня, в результате чего выходы распределителей подключаются к входам двух других буферных регистров. После записи первых двух статистик (сформированных на половине измерительного интервала) в буферные регистры, работа цифрового измерителя продолжается аналогично описанной, до окончания измерительного интервала. После второй половины измерительного интервала делитель 18 шшульсов снова вырабатывает импуль и во вторую пару буферных регистров переписывается две другие статистик из накапливающих сумматоров 7-1-7-2 Одновременно на управляющие входы вт рых ключей 8-1-8-2 подается сигнал о синхронизатора 5, в результате чего те же статистики (чисЛа), накопленные в сумматорах 7-1-7-2, поступают на входы делителя 10. Результат де ления, воздействуя на ещресные шины второго ПЗУ 11, обусловливает выбор ку числа из соответствующей его стро ки. Данное число, являющееся резуль татом измерения взаимной задержки между двумя сигналами на измеритель ном интервале, поступает на устройс во индикатор 12, После этого формирователь 23 сиг нала ошибки, представляющий собой вычислительный цифровой блок, согла но заданному алгоритму по четырем статистикам, хранящимся в бу ферных регистрах, формирует в цифровом виде поправку к частоте гетеродинирующегр. сигнала, вырабатываемого дву счастотным синтезатором 24. Эта поправка (сигнал ошибки) поступает и- -вход 33 двухчастотно/о синтезж .-В резул тате коррекции частота ff гетеродинирующего сигнала изменяется таким образом, чтобы На следующем измерительном интервале более полно скомпенсировать мешайщий параметр - диф ференциальный допплеровский сдвиг м ду принимаемыми сигналами,,

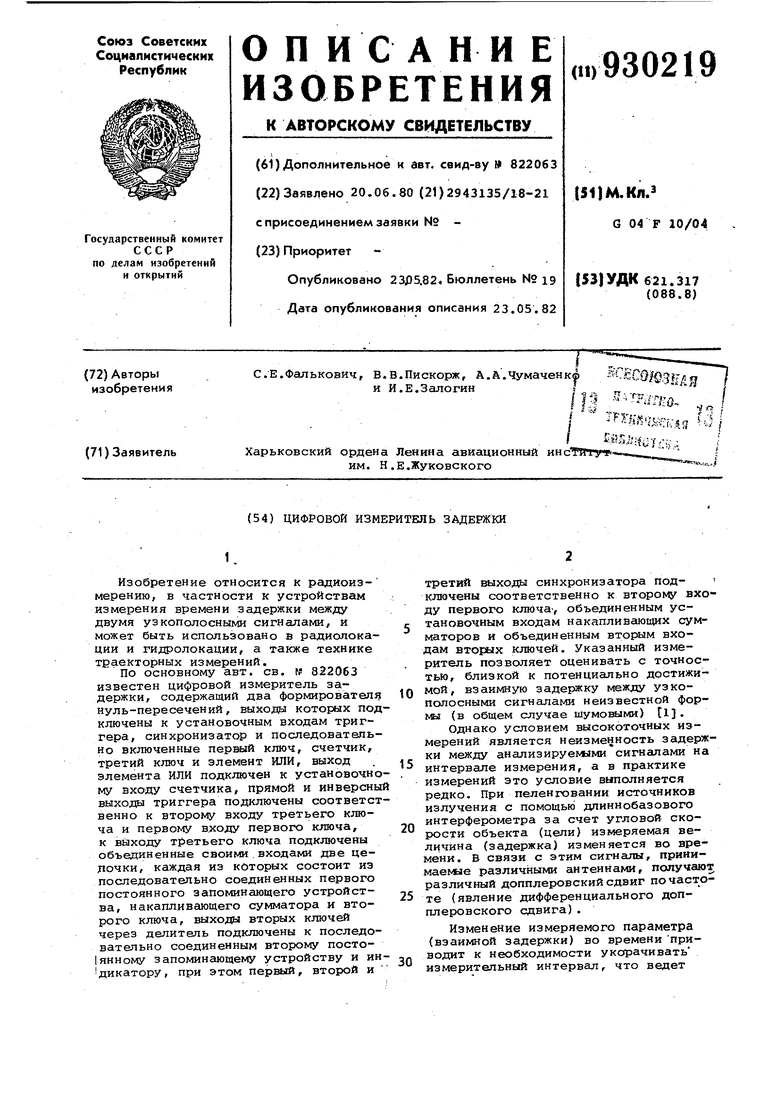

Формирователь сигнала ошибки рабо-Таким образом,- за счет совместноtaeT образом.го измерения задержки сигнала и скоФормирователь 23 сигнала-ошибкирости ее изменения удается существенв цифровом виде реализует алгоритм 65но увеличить длительности измеритель(19) форгдарования поправки к измеренному ранее значению скорости изменения задержки То-Действительная 3с и мнимая Зд составляющие комплексного выходного эффекта , сформированного на полном интервале наблюдения te (-Т/2, Т/2), поступают на входы формирователя 23 соответственно 26 и 30. На два других входа 29 и 31 поступают из буферных регистров 22-2-и 22-4 статистики 3 и 3 соответственно. В первых сумматорах 38-2-38-2 формируются разности соответственно. Умножение на константу. 2 величин 0 f 15 выполняется неявно (на шины су1Ф1аторов запаиваются разрядные шины входов 29 и 31 со сдвигом на один разряд в сторону старших разрядов). С помощью двух первых умножителей 39-1-39-2 и второго сумглатора 40 форг-шруется числитель дроби (19), а с помощью двух первых квадраторов 41, двух вторых квадраторов 42 и cxei4J 44 сложения знаменатель дроби. Результат деления двух чисел с выхода второго делите,ля 43 через второй умножитель 46 пересылается в блок двухчастотного синтезатора 24. С помощью второго умножителя 46 выполняется умн.ожение на константу 2JfpT, которая хранится в элементе 45 памяти, Двухчастотный синтезатор 24 при реализации его согласно блок-схеме на фиг.З работает следующим образом. Высокостабильный монохроматический сигнал задающего генератора 49 поступает в управляемые кодом гетеродинны синтезаторы 47, где на базе этого задающего сигнала вырабатываются два стабильных монохромавических колебания с частотами и f i соответственно. На управляющие шины первого гетеродина 47 из второго элемента 48 памяти подается неизменный во времени код, поэтому частота fi не изменяется во времени. Частота f/ji второго из гетеродинов 47 определяется содержимым Накапливающего сумматора 50. в начале этапа измерений через вход 36 и второй элемент ИЛИ в накапливающий сумматор 50 засылается априорная информация о скорости изменения задержки LQ (или о дифференциальном допплеровском сдвиге д ). После каждого единичного измерения частоты f Г1 Уточняется за счет сигнала ошибки, поступающего из формирователя 23 сигнала ошибки через вход 33 и второй элемент ИЛИ. Уточненное значение f (или Т ) через выход 37 поступает на второй индикатор 25. ного интервала и, как следствие, по высить точность оценивания изменяющейся во времени задержки. Формула изобретения 1.Цифровой измеритель задержки по авт.св. 822063, отличающ.и и с я тем, что, с целью повышения точности измерения изменяющейся во времени задержки, введены две цепочки, состоящие из последовательно соединенных смесителя и уз кополосного фильтра, выходы KOTOIMX подключены к входам формирователей нуль-пересечений, последовательно соединенные делитель импульсов и второй триггер, вход делителя импулъ бов подключен к соответствующему выходу синхронизатора, две цепочки, состоящие из последовательно соединенных четвертого ключа и распределителя, к соответствующим выходам которо.го подключены входы двух буферных регистров, управляющие входы четвертых ключей объединены и подключены к выходу делителя импульсов адресные входы распределителей объединены и подключены к выходу второго триггера, информационные .входы четвертых ключей объединены с информаци онными входами вторых ключей, после довательно соединенные формирователь сигнала ошибки, двухчастотный синтезатор и второй индикатор, соответствующие четыре входа формирователя сигнала ошибки подключены к выходам буферных регистров, аналоговые выходы двухчастотного синтезатора подклю чены к гетеродинным входам соответст вующих смесителей, сигнальные входы которых являются сигнальными входами .цифрового измерителя задержки. 2.Измеритель по п.1, о т л и чающийся тем, что формирователь сигнала ошибки содержит две цепочки, состоящие из первого сумматора и первого умножителя, выходы цепо чек через второй сумматор подключены к последовательно соединенным второму делителю и второму умножителю, выход которого является выходом формирователя сигнала ошибки, к вторюму входу второго умножителя, подключен выход элемента памяту, два первых и два вторых квалзатора, выходы которых через блок сложения подключены к второму входу второго делителя, входы вторых квадраторов соединены с выходами первых сумматоров, вход каждого первого квадратора объединен с вторыми входами сбответствующих первого сумматора и первого умножителя, йри этом информационными входами формирователя сигнала ошибки являются первые входы первых сумматоров и входы первых квадраторов. / 3. Измери Сель по п.1, о. т л и чающийся тем, что двухчастотный синтезатор содержит два управляемых кодом гетеродина, к синхронизирующим входам которого подключены соответствующие выходы задающего генератора, к управляющему входу первого управляемого кодом гетеродина подключен выход второго элемента памяти, а также последовательно соединенные второй элемент ИЛИ и второй накапливающий сумматор, первый вход второго .элемента ИЛИ является сигнальным, второй вход установочным входом двухчастотного синтезатора, выход второго накапливающего сумматора подключен к управляющему входу второго управляемого кодом гетеродина и является информационным- выходом двухчастотного синтезатора, выходы управляемых кодом гетеродинов являются аналоговыми выходами двухчастотного синтезатора. Источники информации, принятые во внимание при экспертизе ; 1. Авторское свидетельство СССР № 622063, кл. G 04 F 10/04 15.12.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| Устройство для цифровой обработкиСигНАлОВ | 1979 |

|

SU834559A1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Система передачи и приема информации с многоосновным кодированием | 1989 |

|

SU1642590A1 |

| Цифровой измеритель задержки | 1979 |

|

SU822063A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

| Цифровой измеритель частоты | 1988 |

|

SU1684710A1 |

гъ

гв

Фиг. 2

. 54

W

3:

Авторы

Даты

1982-05-23—Публикация

1980-06-20—Подача