1

(21)4607740/21

(22)21.11.88

(46) 30.03.91. Бюл. № 12

(71)Азербайджанский институт нефти и химии им.М.Азизбекова

(72)И.М.Абдуллаев, А.Я.Исмаилов, Г.К.Гладков и Р.Н.Аллахвердиев

(53)621.317.7(088.8)

(56)17-ратрядный АПП с максимальI ной частотой преобразования 4 МГц,- Экспресс-информация. Сер. Приборы и элементы автоматики и вычислительной техники, 1987, № 46, с.9-17.

Авторское свидетельство СССР № 1422168, кл. G 01 R 19/25, 1986.

(54)ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АНАЛОГОВОЙ ВЕЛИЧИНЫ

(57)Изобретение относится к цифровой измерительной технике. С целью повышения точности измерения и упрощения

усилитель-ограничитель 8, линия 9 задержки, блок 10 совпадения знаков, буферный регистр 7. Блоком 1 выборки-хранения из измеряемого сигнала производятся выборки, которые интегрируются интегратором 4, преобразуются аналого-цифровым преобразователем (АЦП) 5 в код, который поступает на запись в регистр 7 и цифроаналоговый преобразователь (ЦАП) 6, с выхода которого сигнал поступает на вычитатель 2. Сигнал с вычислителя 3 обрабатывается усилителем 8 и поступает на входы блока 10, задерживаясь линией 9 на один такт. При совпадении знаков сигналов на входах блока 10 вырабатывается сигнал записи результата из-4 мерения в регистр 7. Многократное . повторение тактов работы позволяет осуществить цифровую фильтрацию. 2

5S

(л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения речевых сигналов | 1989 |

|

SU1626393A1 |

| Цифровое устройство формирования огибающей выходных сигналов передатчиков радиолокационных систем | 2018 |

|

RU2711507C2 |

| Устройство для компенсации временных искажений в аппарате магнитной записи | 1989 |

|

SU1607010A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Устройство для измерения температуры | 1990 |

|

SU1742640A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2012036C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для спектрально-временного анализа сигналов | 1989 |

|

SU1711109A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство слежения за информационной дорожкой носителя оптической записи | 1988 |

|

SU1638724A1 |

О5 00 00

оэ ел

Фиг.1

Изобретение относится к цифровой измерительной технике и предназначено для повышения точности цифровых измерителей аналоговых величин.

Целью изобретения является повышение точности измерения и упрощение цифрового измерителя аналоговой величины.

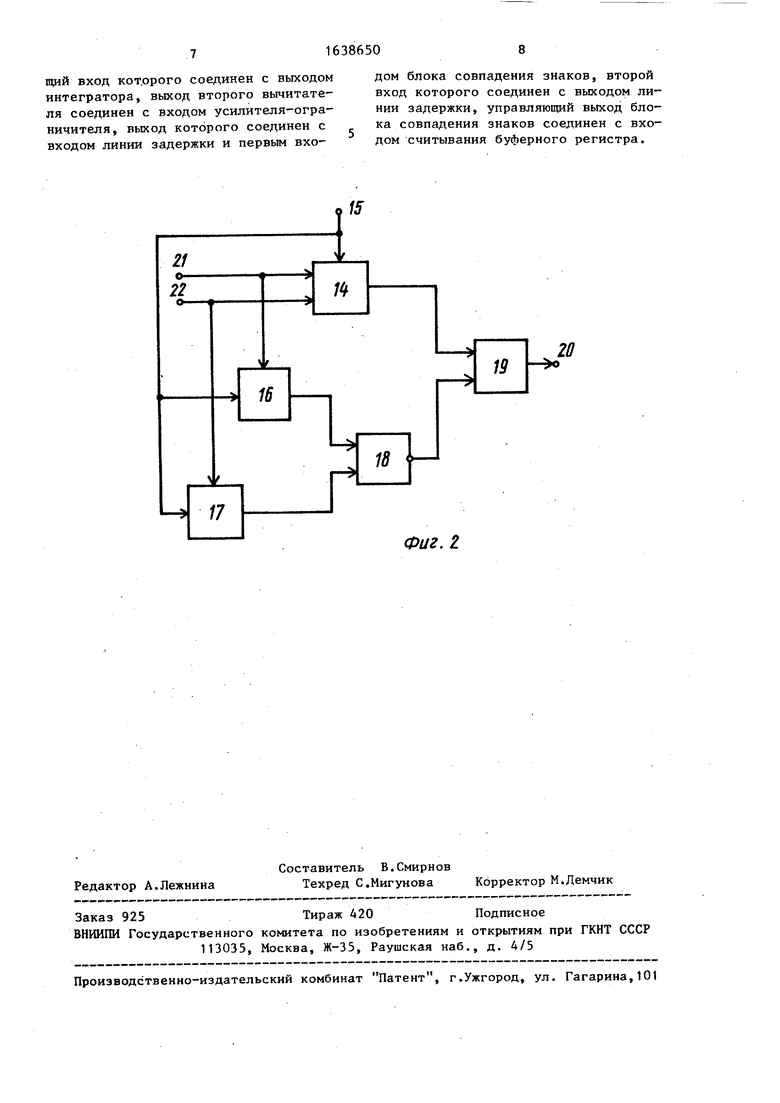

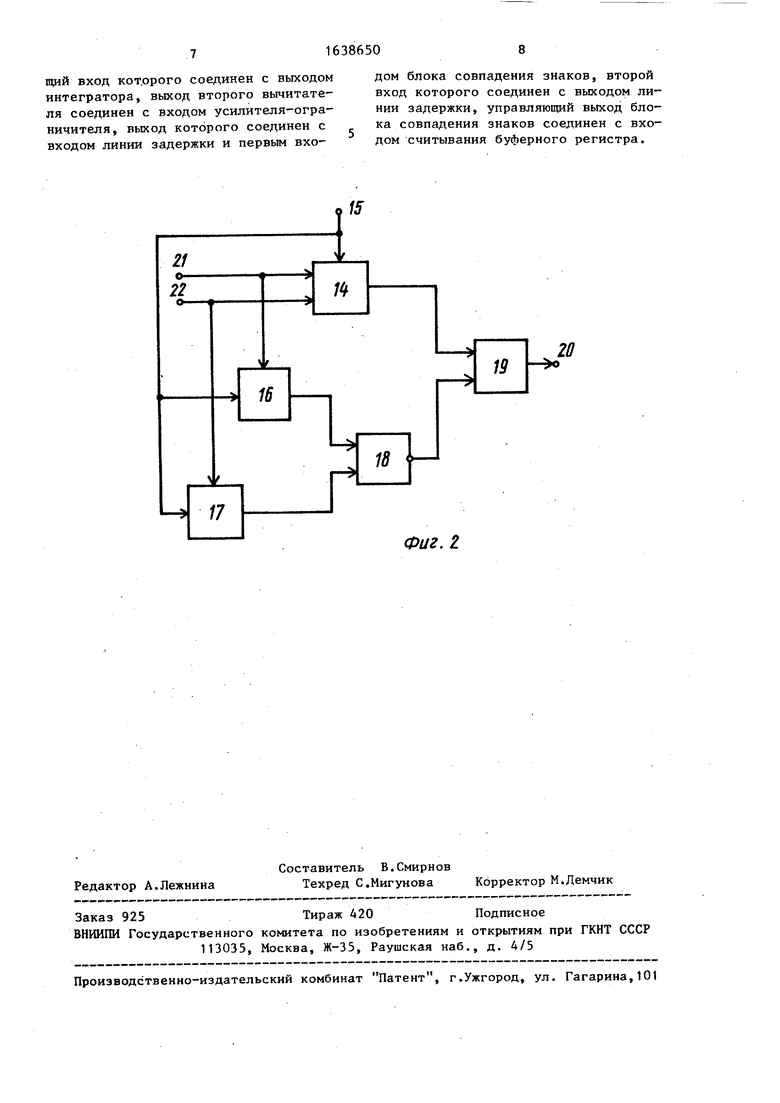

На фиг. 1 приведена функциональ- нал схема предлагаемого измерителя; на фиг. 2 - схема блока совпадения знаков.

Цифровой измеритель аналоговой величины содержит блок 1 выборки- хранения, выход которого соединен с неинвертирующими входами вычитателей 2 и 3. Выход вычитателя 2 через интегратор 4 соединен с инвертирующим входом вычитателя 3 и входом знало- го-цифрового преобразователя (АЦП) 5 выход которого соединен с входами цифроаналогового преобразователя (ЦАП) 6 и буферного регистра 7. Выход ЦАП 6 соединен с инвертирующим входом вычитателя 2. Выход вычитателя 3 через усилитель-ограничитель 8 соединен с входом линии 9 задержки и первым входом блока 10 совпадения знаков, второй вход которого со- единен с выходом линии 9 задержки. Управляющий выход АЦП 5 соединен с входом сброса буферного регистра 7, вход считывания которого соединен с выходом блока 10 совпадения знаков, управляющий вход которого соединен с управляющими входами АПП 5, ЦАП 6 и блока 1 выборки-хранения, входом записи буферного регистра 7 и шиной 11 тактового сигнала. Вход блока 1 вы- борки-хранения соединен с входом 12. Выход буферного регистра 7 соединен с выходом 13.

Блок 10 совпадения знаков (фиг.2) содержит элемент И 14, первый вход которого соединен с управляющим входом 15 и первыми входами блоков 16 17 сдвига уровня. Выходы последних соединены с соответствующими входами элемента ИЛИ-НЕ 18, выход которого соединен с первым входом элемента ИЛИ 19. Выход элемента ИЛИ 19 соединен с управляющим выходом 20, второй вход - с выходом элемента И 14, первый вход которого соединен с вт рым входом блока 16 сдвига уровня и первым входом 21 блока 10, второй вход 22 которого соединен с вторыми

входами блока 17 сдвига уровня и элемента И 14.

Цифровой измеритель аналоговой величины работает следующим образом.

В первый такт работы (все блоки находятся в исходном - нулевом - состоянии) блок 1 выборки-хранения из измеряемой величины X делает выборку X длительности Ј , а ЦАП 6 формирует аналоговый сигнал X, YQ, эквивалентный погрешности Ј нуля АЦП 5. Сигнал Х( вычитается из выборки X. , и разностный сигнал Z | X - X, X, - Ј0 интегрируется интегратором 4 в течение времени ЈQ.

В результате на выходе интегратора 4 в первый такт имеется сигнал

о

L «Vj x,4)dt

о °

с

Ј u

-i х,-ee),

(о

где с, - постоянная времени интегратора 4.

Полагаем, что коэффициент пропорциональности CQ /Ј - 1 и амплитуда выходных импульсов блока 1 выборки- хранения за время 0 не изменяется в силуЈ0«Т0, где Т0 - интервал дискретизации величины X.

На выходе АЦП 5 получается первый скорректированный результат

1, +е, х, + л е,, (2)

где i Ј, Ј, - 60 конечная разность первого порядка погрешности АЦП 5 в первом такте преобразования;

С(- реализация погрешности АЦП 5 в первом такте преобразования.

Код Y , записывается во входной регистр ЦАП 6.

Параллельно с сигналом Z 4 форми- руется также сигнал Z ( X - 1 бо который с выхода вычитателя 3 сигналов через усилитель-ограничитель 8 поступает одноврем чно на входы линии 9 задержки и блока 10 совпадения знаков. Однако, поскольку этот сигнал задерживается линией 9 задержки на время Т0, равное интервалу дискретизации во времени, в

первом такте блок 10 совпадения знаков не реагирует на данный сигнал.

Во втором такте измерения блок 1 выборки-хранения из измеряемой величины X делает выборку Х2, ЦАП 6 формирует аналоговый сигнал Y, , эквивалентный выходному коду Y АЦП 5 в предыдущем такте, код Y с выхода АНП 5 записывается в буферный регистр 7 сигналом Запись.

На выходе интегратора 4 согласно выражению (1) формируется сигнал 1,

хгХ2 +

1,

выходе вычитателя X, - 1„ 6, .

X Ј С( ,

3 - сигнал

а на

iЧ -г Сигнал

Z

.г, проходя через усилитель-ограничитель 8, в блоке 10 совпадения знаков сравнивается по знаку с выходным сигналом Z . Ј0 линии 9 задержки. При этом, если сигналы Z и Zi имеют одинаковую полярность, на выходе блока 10 совпадения знаков формируется управляющий сигнал Считывание и содержимо Y , буферного регистра 7 как годный результат предыдущего измерения передается на выход 13 устройства.

Выходной сигнал 12 интегратора 4 подвергается аналого-цифровому преобразованию, и на выходе АЦП 5 формируется код

Y, 1,

+ +Л 6г,(3)

де

С2 реализация погрешности АЦП 5 во втором такте преобразования, Јг - Ј, - конечная разд ег

ность первого порядка по-35 цифрового преобразователя, управгрешности АПП 5 во втором такте преобразования.

Сигналом Готов, соответствующим кониу преобразования в АЦП 5, формируется управляющий сигнал Сброс, и показание буферного регистра 7 сбрасывается на нуль, а также код YЈ записывается во входном регистре ПАП 6. Далее по мере поступления импульсов от шины 11 тактовых импульсов с

40

45

ляющий вход которого соединен с уп равляющими входами блока выборки- хранения, цифроаналогового преобра зователя и шиной тактовых сигналов вход аналого-цифрового преобразова теля соединен с выходом интегратор второй вычитатель, отличающийся тем, что, с целью повышения точности измерения и упрощения устройства, в него дополнительн введены усилитель-ограничитель, лин задержки, блок совпадения знаков и буферный регистр, выход которого яв ляется выходом устройства, а вход соединен с выходом аналого-цифровог преобразователя, управляющий выход которого соединен с входом сброса б ферного регистра, вход записи котор го соединен с управляющим входом блока совпадения знаков и шиной так товых сигналов, выход блока выборки хранения соединен с неинвертирующим входом второго вычитателя, инвертиру

списанный выше

частотой f0 1/Т0

процесс повторяется периодически.

Блок 10 совпадения знаков работае следующим образом.

Если выходные сигналы усилителя- ограничителя 8 и линии 9 задержки имеют одновременно положительную полярность, то на выходе элемента И 14 получается сигнал 1, который через элемент ИЛИ 19 вырабатывает сигнал Считывание. В случае, когда входные сигналы одновременно имеют

10

отрицательную полярность, сигнал на выходе элемента И 14 отсутствует, а на выходе элемента ИЛИ-НЕ 18 присутствует сигнал, который,проходя через элемент ИЛИ 19, формируется в сигнал Считывание. В других сочетаниях полярностей сигналов от блоков 8 и 9 сигнал Считывание отсутствует. Для обеспечения совместимости входов элемента ИЛИ 19 входные сигналы элемента ИЛИ-НЕ 18 с помощью блоков 16 и 17 сдвига уровней переводятся в область положительной логики. Поэтому при отрицательных полярностях выходных сигналов блоков 8 и 9 сдвинутые в положительную полярность выходные сигналы блоков 16 и 17 будут иметь уровни, близкие к нулевому уровню, и поэтому на выходе элемента ИЛИ-НЕ 18 только в этом случае будет иметь место единичный сигнал.

15

20

Формула изобретения

Цифровой измеритель аналоговой величины, содержащий блок выборки-хранения, вход которого является входом устройства, а выход соединен с неинвертирующим входом первого вычитателя, инвертирующий вход которого соединен с выходом цифро- аналогового преобразователя, вход которого соединен с выходом аналого

0

5

0

5

ляющий вход которого соединен с управляющими входами блока выборки- хранения, цифроаналогового преобра-1- зователя и шиной тактовых сигналов, вход аналого-цифрового преобразователя соединен с выходом интегратора, второй вычитатель, отличающийся тем, что, с целью повышения точности измерения и упрощения устройства, в него дополнительно введены усилитель-ограничитель, линия задержки, блок совпадения знаков и буферный регистр, выход которого является выходом устройства, а вход соединен с выходом аналого-цифрового преобразователя, управляющий выход которого соединен с входом сброса буферного регистра, вход записи которого соединен с управляющим входом блока совпадения знаков и шиной тактовых сигналов, выход блока выборки- хранения соединен с неинвертирующим входом второго вычитателя, инвертирующий вход которого соединен с выходом интегратора, выход второго вычитате- пя соединен с входом усилителя-ограничителя, выход которого соединен с входом линии задержки и первым вхо21

о2L

п

16

дом блока совпадения знаков, второй вход которого соединен с выходом линии задержки, управляющий выход блока совпадения знаков соединен с входом считывания буферного регистра.

19

-

20

Фиг. 2

Авторы

Даты

1991-03-30—Публикация

1988-11-21—Подача