поминается в оперативном запоминающем устройстве (ОЗУ) 3. Считывание ординат сигнала и ОЗУ 3 осуществляется с задержкой. Для обеспечения высокой точности воспроизведения ординаты сигнала восстанавливаются цифроаналого- вым преобразователем (ЦАП) 14, За счет разбиения интервала днскретиза-

ции на мелкие деления, равные ступеньке ЦАП 14, обеспечивается высокая-точность задержки аналогового- сигнала. Для устранения выбросов 1Щ 14 на его выходе включены блок 15 выборки и хранения и сглаживающий фильтр 16, 1 з.п, ф-лы, 2 ил„

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНЫЙ КАНАЛ ГИДРОАКУСТИЧЕСКОЙ ЦИФРОВОЙ ПРИЕМНОЙ СИСТЕМЫ | 1994 |

|

RU2077066C1 |

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых вычислительных комплексах, устройствах автоматики и связи как аналоговая линия задержки. Изобретения позволяет повысить точность воспроизведения. Это достигается тем, что аналоговый сигнал преобразуется аналого-цифровым преобразователем 2 в код, который запоминается в оперативном запоминающем устройстве (ОЗУ) 3. Считывание ординат сигнала из ОЗУ 3 осуществляется с задержкой. Для обеспечения высокой точности воспроизведения ординаты сигнала восстанавливаются цифроаналоговым преобразователем (ЦАП) 14. За счет разбиения интервала дискретизации на мелкие деления, равные ступеньке ЦАП 14, обеспечивается высокая точность задержки аналогового сигнала. Для устранения выбросов ЦАП 14 на его выходе включен блок 15 выборки и хранения и сглаживающий фильтр 16. 1 з.п. ф-лы, 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в аналого-цифровых вычислительных комплексах, устройствах автоматики и связи, как аналого-цифровая линия задержки.

Целью изобретения является повышение точности воспроизведения.

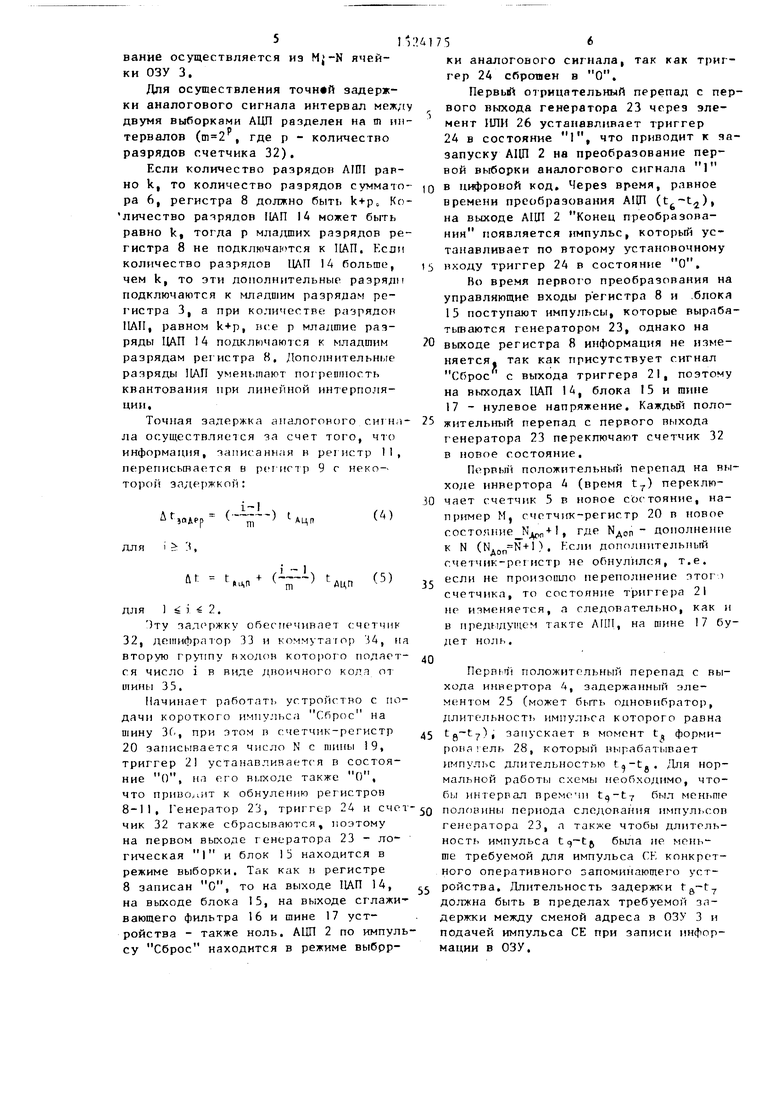

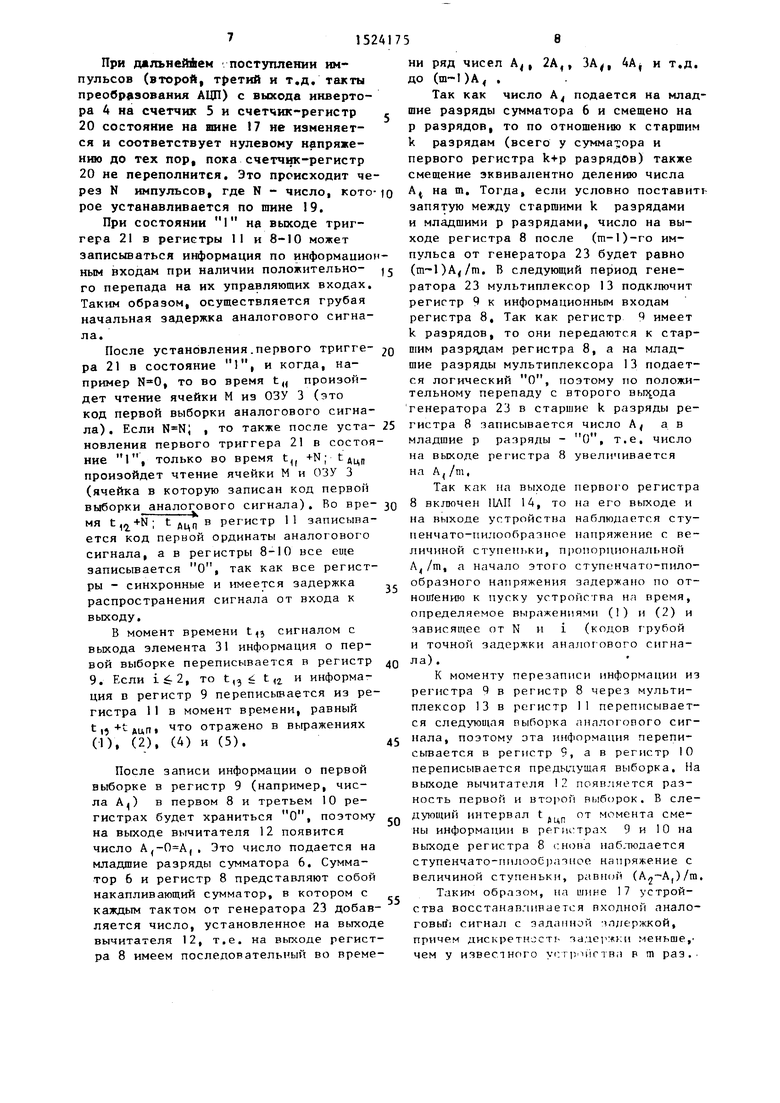

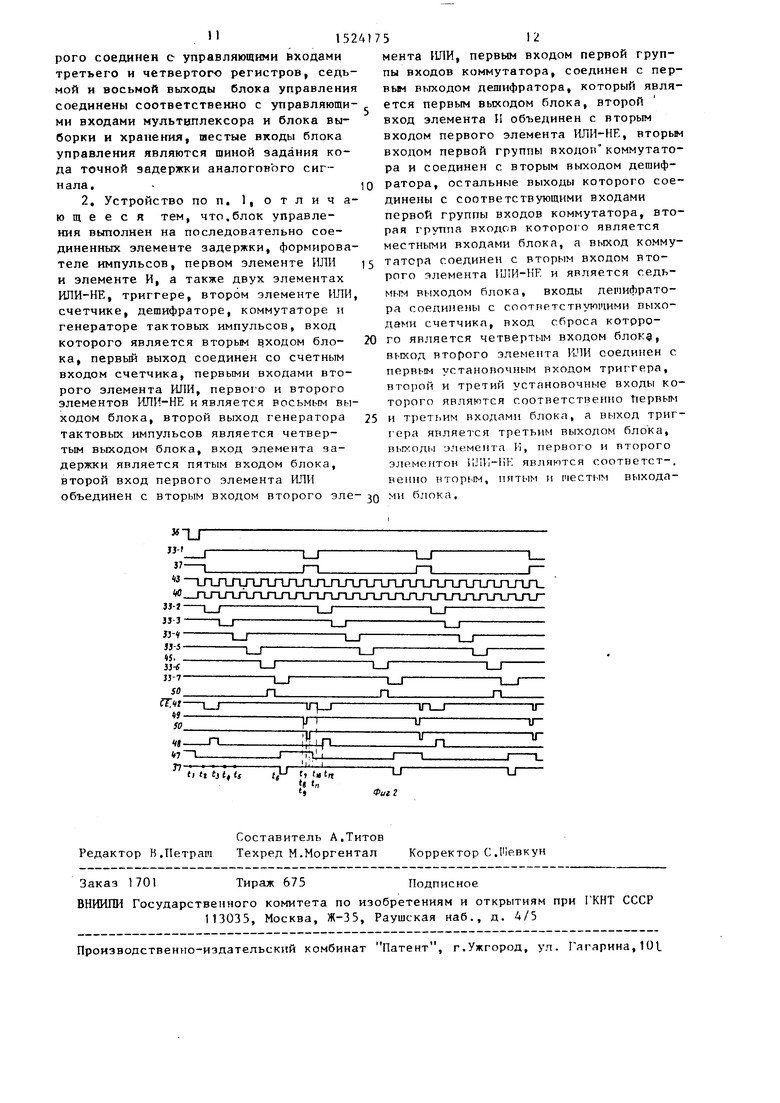

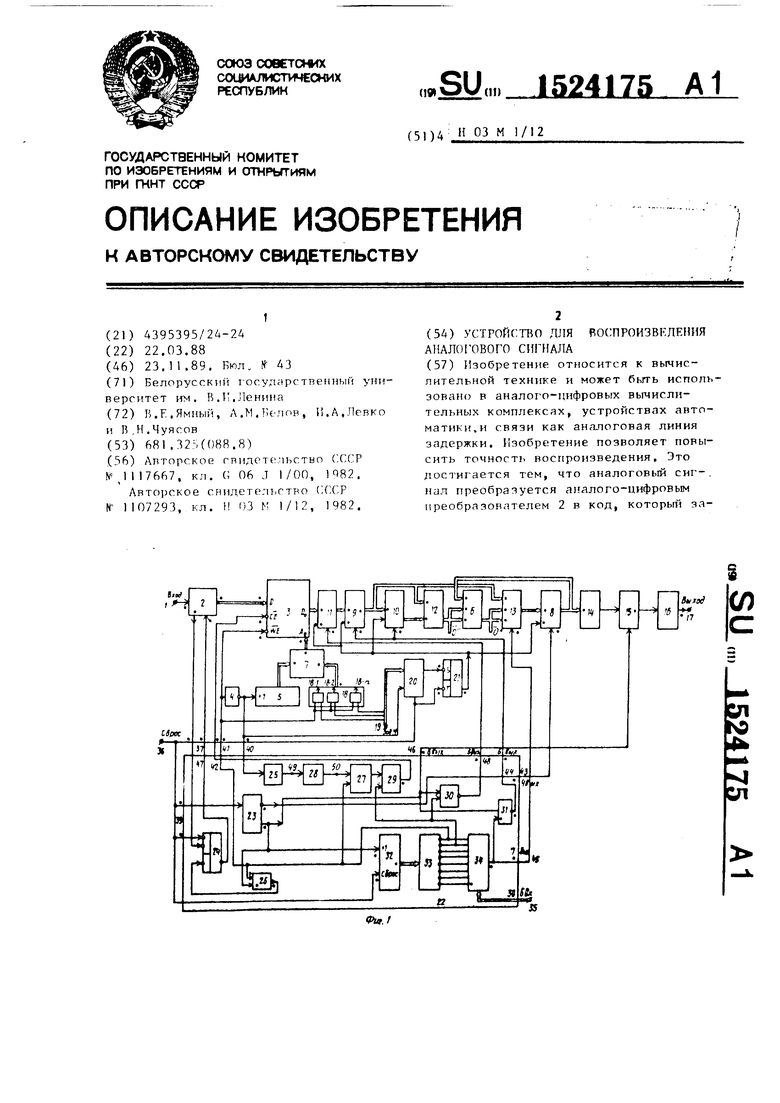

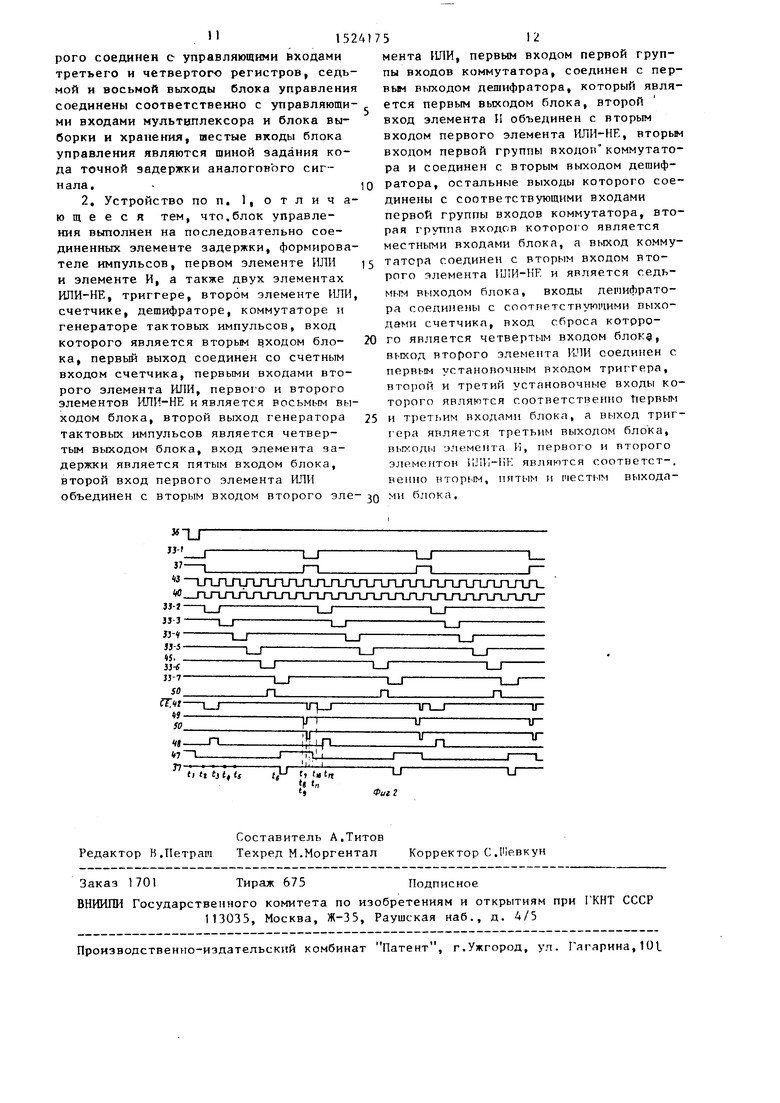

На фиг.1 приведена функциональная схема устройства; на фиг,2 - эпюры напряжений в характерны} точках блока управления, поясняющие прин цип действия устройства.

Устройство содержит входную ши- иу 1, аналого-цифровой преобразователь (АЦП) 2, оперативное запоминающее устройство (ОЗУ) 3, инвертор 4, счетчик 5, сумматоры 6 и 7, регистры 8-11, вычитатель 12, мультиплексор 13, цифроаналоговый преобразователь (ЦАП) 14, блок 15 выборки и хранения, сглаживающий фильтр 16, выходную ши- иу 17, п элементов И 18, шину 19 задания цифрового кода грубой задержки аналогового сигиала, счетчик-регистр 20, триггер 21, блок 22 управления, который содержит генератор 23-тактовых импульсов, триггер 24, элемент 25 задержки, элементы ИЛИ 26 и 27, формирователь 28 импульсов, элемент И 29, элементы ИЛИ-НЕ 30 и 31, счетчик 32, дешифратор 33, коммутатор 34, -шину 35 задания кода точной задержки аналогового сигиала, шину 36 Сброс, входы 37-40.блока 22, выходы 41-48 блока 22, выход 49 элемента 25, выход 50 формирователя 28.

На фиг,2 представлены эпюры 37-50 сигналов на входах и выходах блока 2 И его элементов.

Устройство работает следующим образом,

Для задания определенной задержки аналогового сигнала устанавливают

код грубой задержки t, по шине 19 и код точной задержки At, по шине 35, при этом суммарная задержка t5aдep, определяемая этими кодами, равна

() t., tft. iflliili

АЦГГ

(I)

WAep для i 5 3,

tK,Aep () t,,, i MniiilU(3)

для ,

где N - число, соответствующие грубой задержке, представленное по шине 19 в виде дополнительного двоичного числа, причем N может изменяться от

0до Q, где Q - объем ОЗУ З; АЦП время между двумя выборками

аналогового сигнала в АЦП 2J - коэффициент пересчета счетчика 32 (или количество выходов дешифратора 33); двоичное число, соответствующее коду точной задержки, устанавливаемое по шине 35, причем i может изменяться от

1до т.

Минимальная задержка аналогового сигнала в устройстве равна

m

).

(3)

При суммировании в сумматоре 7 двух чисел - адреса ОЗУ 3 ячейки, в которую записывается текущая выборка, и числа N получаем на выходе сумматора 7 двоичный код адреса ОЗУ 3, смещенный влево.

Таким образом осуществляется грубая задержка аналогового сигнала, так как очередная выборка аналогового сигнала, преобразованная АЦП 2, запи- сьгоается в М; ячсл ку ОЗУ 3, а считы-

5I ,

вание осуществляется из Mj-N ячейки ОЗУ 3.

Для осушествления точней задержки аналогового сигнала интервал между двумя выборками АЦП разделен на m интервалов (, где р - количество разрядов счетчика 32).

Если количество разрядов ЛШ1 рар- но k, то количество разрядов сумма1о- ра 6, регистра 8 должно быть k-t-p, Ко- личество разрядов ПАП 14 может быть равно k, тогда р мла;щих разрядов регистра 8 не подключаются к ПАП. Если количество разрядов ЦАП 14 больше, чем k, то эти дополнительные разряди подключаются к младшим разрядам регистра 3, а при количестве разрядог( ПАП, равном k+p, вс.е р младшие разряды ЦАП 14 подключаю ся к младшим разрядам регистра 8. Дополнительные разряды ПАП уменьшают пог-репиюсть квантования при линейной интерполяции.

Точная задержка апалогового сигнала осуществляе1ся за счет того, что информация, записанная н регистр 11, п€феписьтается в рег ипр 9 г неко-- Topoi i задержкой:

u jOiPp ( , ) АЦП

для

i :.

й

(-)

m

АЦП

для 1 i & 2,

Зту зал(ржку обеспечивпет счетчик 32, дешифратор 33 и коммутатор 34, яа вторую группу Г1ХОДОВ которого подается число i в виде двоичного кода от шины 35.

Начинает рпботат1 устройство с подачи короткого импульса Сброс на шину ЗС., при этом в счетчик-регистр 20 записывается число N с шипы 19, триггер 21 устанавливается в состояние о, н,1 его выходе также О, что приводит к обнулению регистров 8-11. Генератор 23, триггер 24 и счетчик 32 также сбрасываются, поэтому на первом выходе генератора 23 - лорежиме выборки. Так как в регистре 8 записан О, то на выходе ЦАП 14, на выходе блока 15, на выходе сглаживающего фильтра 16 и шине 17 устройства - также ноль. АЦП 2 по импульсу Сброс находится в режиме выбрр ,

у

- -

: 41756

ки аналогового сигнала, так как триггер 24 сброиен в О.

Первый отрицательный перепад с пер- , вого выхода генератора 23 через элемент 1ШИ 26 устанавливает триггер 24 в состояние 1, что приводит к яа- запуску АЦП 2 на преобразование первой выборки аналогового сигнала 1

Q в цифровой код. Через время, равное времени преобразования АЦП () на выходе АЦП 2 Конец преобразования появляется импульс, который устанавливает по второму установочному

15 нходу триггер 24 в состояние О.

Во время первого преобразования на управляющие входы регистра 8 и .блока 15 поступают импульсы, которые выраба- тьшаются генератором 23, однако на

20 выходе регистра 8 информация не изменяется, так как присутствует сигнал Сброс с выхода триггера 21, поэтому на выходах ЦАП 14, блока 15 и шине 17 - нулевое напряжение. Каждьп поло25 жительный перепад с первого выхода генератора 23 переключают счетчик 32 в новое состояние.

ПерпьпЧ положительный перепад на выходе инвертора 4 (время t.) переклю30 чает счетчик 5 в новое сос-тояние, например М, счетчик-регистр 20 в новое cocTo.niine N,n+1, где Nдc,n - дополнение к N (N. дополнительный счетчик-регистр не обнулйлся, т.е.

,г если не произопшо переполнение зтог i счетчика, то состояние триггера 21 не изменяется, а следовательно, как и в предыдущем такте ЛИП, на шине 17 будет ноль.

40

Перпьп положительный перепад с выхода инвертора 4, задержанный элементом 25 (может быть одновибратор, длительность импульса которого равна

45 запускает в момент t, форми- ропл ель 28, который вырабатывает И1-1пульс длительностью . Для нормальной работ1 1 схемы необходимо, чтобы интервал времечи был меньше

50 половины периода следования импульсов генератора 23, а также чтобы длительность импульса tg-tg была не hsenb- ше требуемой для импульса CF. конкретного оперативного запоминающего уст55 ройства. Длительность задержки , должна быть в пределах требуемой задержки между сменой адреса в ОЗУ 3 и подачей импульса СЕ при записи информации в ОЗУ.

При дАльнеййем поступлении импульсов (второй, третий и т.д. такты преобразования АЦП) с выхода инвертора 4 на счетчик 5 и счетчик-регистр 20 состояние на вшне 17 не изменяется и соответствует нулевому напряжению до тех пор, пока счетчик-регистр 20 не переполнится. Это происходит через N импульсов, где N - число, кото рое устанавливается по шине 19.

При состоянни 1 на выходе триггера 21 в регистры II и 8-10 может записываться ин})0рмация по информаиио ным входам прн наличии положительно- го перепада на их управляющих входах. Таким образом, осуществляется грубая начальная задержка аналогового сигнала.

После установления.первого тригге- ра 21 в состояние 1, и когда, например , то во время t,, произойдет чтение ячейки М из ОЗУ 3 (это код первой выборки аналогового сигнала). Если , то также после уста- новленин первого триггера 21 в состоя нне 1, только во время t,, +N; произойдет чтение ячейки М и ОЗУ 3 (ячейка в которую записан код первой выборки аналогового сигнала). Во вре- мя t,+N; t дцр в регистр 11 записыиа- ется код первой ординаты аналогового сигнала, а в регистры 8-10 все еще записывается О, так как все регистры - синхронные и имеется задержка распространения сигнала от входа к выходу.

В момент времени сигналом с выхода злемента 31 информация о первой выборке переписывается в регистр 9. Если , то t,3 t,2. и информация в регистр 9 переписьюается из регистра 11 в момент времени, равный что отражено в вьфажениях (1), (2), (4) и (5).

После записи информации о первой выборке в регистр 9 (например, числа А,) в первом 8 и третьем 10 регистрах будет храниться О, поэтому иа выходе вычитателя 12 появится число ,, Это число подается на младшие разряды сумматора 6. Сумматор 6 и регистр 8 представляют собой накапливающий сумматор, в котором с каждым тактом от генератора 23 добавляется число, установленное на выход вычитателя 12, т.е. на выходе регистра 8 имеем последовательный во времени ряд чисел А, 2А,, ЗА, 4А и т.д

до (Ш-ОА .

Так как число А подается на младшие разряды сумматора 6 и смещено на р разрядов, то по отношению к старшим k разрядам (всего у сумма гора и первого регистра k+p разрядов) также смещение эквивалентно делению числа А на т. Тогда, если условно поставит запятую между старшими k разрядами и младшими р разрядами, число на выходе регистра 8 после (m-l)-ro импульса от генератора 23 будет равно (). В следующий период генератора 23 мультиплексор 13 подключит регистр 9 к информационным входам регистра 8, Так как регистр 9 имеет k разрядов, то они передаются к старшим разрядам регистра 8, а на младшие разряды мультиплексора 13 подается логический О, поэтому по положительному перепаду с второго генератора 23 в старшие k разряды регистра 8 записывается число А а в младшие р разряды - О, т.е. число на выходе регистра 8 увеличивается на ,

Так как иа выходе первого регистра 8 включен ПАП 14, то на его выходе и на выходе устройства наблюдается сту- пенчато-пи.чообразное напряжение с величиной ступеи1,ки, П1юпорцмональной , а начало этого ступенчато-пилообразного напряжения задержано по отношению к пуску устройства на время, определяемое выражениями (1) и (2) и зависящее от Ни (кодов грубой и точной задержки аналогового сигнала).

К моменту перезаписи информации из регистра 9 в регистр 8 через мультиплексор 13 в регистр 11 переписывается следующая выборка аналогового сигнала, поэтому эта информация перепи- сьтается в регистр 9, а в регистр 10 переписывается преды;;ущая выборка. На выходе вычитателя 12 появляется разность первой и второй выборок. В следующий интервал t от момента смены информации в регш;трах 9 и 10 на выходе регистра 8 снова наблюдается ступенчато-г1илооб1)а1ное напряжение с величиной ступеньки, равной (,)/т

Таким образом, иа шине 17 устройства восстанав. 1ирается входной анало- говьп сигнал с заданной -шдержкой, причем дискретность та,иер:«К11 меньше, чем у известного у1:т1) М1ства в m раз,.

5

Величина ступеньки между соседними выборками также меньше по сравнению г известным устройством. Уменьшение величины ступеньки приводит к уменьшению погрешности восстановления аналогового сигнала, а при заданной погрешности такое качество устройства можно использовать для того, чтобы уменьшить количество выборок на определен- JQ ный интервал сигнала, что при заданном и равном с известным объеме ОЗУ приводит к увеличению задержки аналогового сигнала и увеличению точности уставки задержки за счет уменьшения ее дискретности.

Восстановленный ступенчато-пилообразный аналоговый сигнал, проходя блок 15, дополнительно фильтруется за счет отключения выхода от входа в 20 блоке 15 во время переходного процесса ЦАП 14. Далее этот ступенчато-пилообразный сигнал сглаживается фильтром 16 для уменьшения высокочастотных шумов и подводится к шине 17 устройст- 25 ва.

Включение элемента 25 задержки и формирователя 28 импульсов необходимо для формирования записыпающего импульса СЕ в ОЗУ 3 (фиг. 2), С помо1дью зо элемента 27 и элемента 28 формируется полный сигнал СЕ для записи информации в ОЗУ 3 и чтения ее из ОЗУ,

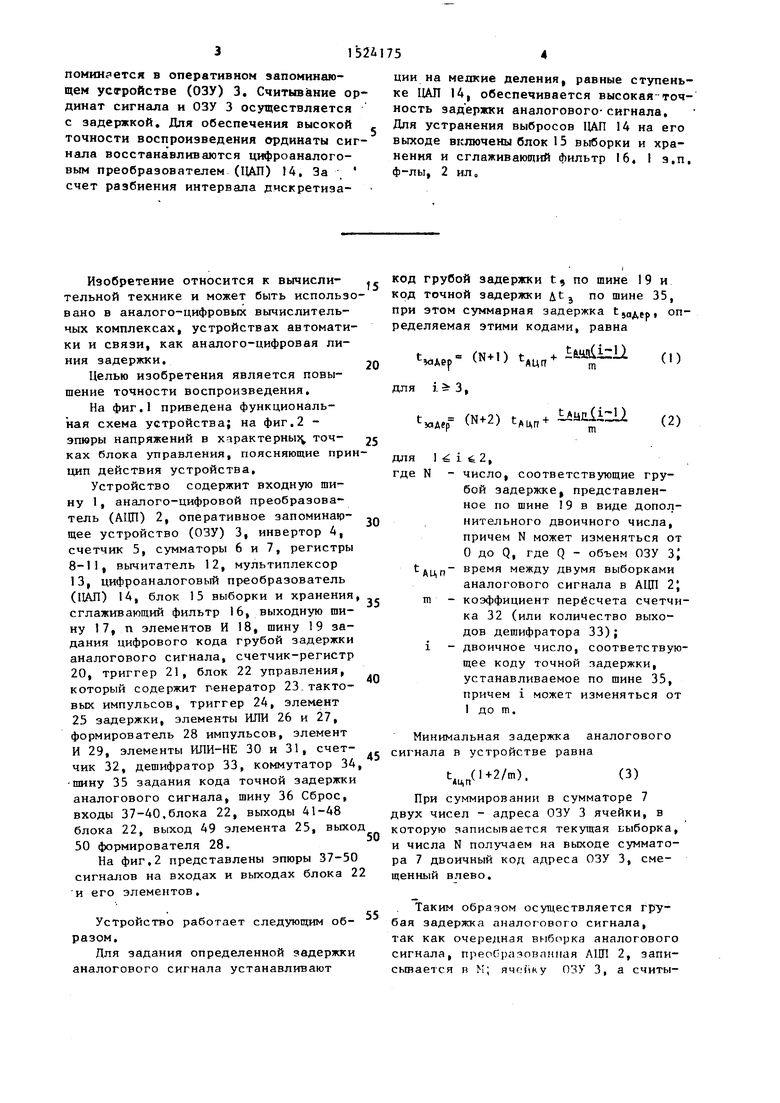

Формула изобретения

НОИ, выходы соединены с соответствующими входами данных оперативного запоминающего устройства, мультиплексор информационные выходы которого соединены с соответствующими информационными входами первого регистра, выходы которого соединены с соответствующей входами цифроанапогового преобразователя, два счетчика, три элемента И, триггер, отличающееся тем что, с целью повыщения точности воспроизведения, в него введены блок управления, вычитатель, блок выборки и хранения, сглаживающий фильтр, два сумматора, инвертор, элементов И, второй, третий и четвертый регистры, один из счетчиков вьтолнен в виде счетчика-регистра, при этом выходы оперативного замыкающего устройства

10

5

JQ

20 25

о

5

5

0

через последовательно соединенные второй, третий и четвертый регистры, вычитатель, первый сумматор соединены с ин4 ормациог{Н1.гми входами мультиплексора, вторые информационные входы мулыиплексора и первого сумматора являются шиной логического нуля, третьи информацион1гые входы мультиплексора объединены соответственно с вторыми информационными входами вычитателя и первыми информагпюнными входами четвертого регистра, третьи информационные входы первого сумматора объединены соответственно с входами цифроана- логового преобразователя, выход которого соединен с информационным входом блока выборки и хранения, выход которого соединен с входом сглаживающего фильтра, выход которого является выходной тиной, выход Конец преобразования аналого-цифрового преобразователя соединен с первым входом блока управления, второй, третий и четверть входы которого объединены с управляющим входом счетчика-регистра, первым установочным входом триггера и ЯВЛЯЮ7СЯ тиной Сброс, счетные входы счетч ка-рег-истра и счетч - ка объединены с пятым входом блока уг рпвления и соединен с выходом инвертора, пход которого объединен с входом записи-чтения оперативного запоминающего устрО 1Ства, входами п элементов И и соединен с первым выходом блока управления, второй и третий выходы которого соединены соответственно с управляющими входами оперативного запоминающего устройствами аналого-пифророго преобразователя, адресные входы оперативного запоминающего устройства соединены с соответствуюрщми выходами второго сумматора, первые и вторые входы которого соедине ы соответственно с выходами счетчика и п элементов И, вторые входы которых объединены с соответствующими информационнь ми входами счетчика-регистра и являются щи- ной задания кода грубой задержки аналогового сигнала, выход счетчика-регистра соединен с вторь м установочным входом триггера, выход которого соединен с входа(и Сброс первого, второго, третьего и четвертого регистров, управляющие входы первого и второго регистров соединены соответственно с четверть М и пятым выходами блока управления, шестой выход кото 1152

рого соединен с управляющими входами третьего и четвертого регистров, седьмой и восьмой выходы блока управления соединены соответственно с управляющими входами мультиплексора и блока выборки и хранения, шестые вкоды блока управления являются щнной задания кода точной задержки аналогового снг- нала. -

2, Устройство по п. 1, отличающееся тем, что.блок управления вьтолнен на последовательно соединенных элементе задержки, формирователе импульсов, первом элементе ИЛИ и элементе И, а также двух элементах ИЛИ-НЕ, триггере, втором элементе ИЛИ, счетчнке, дешифраторе, коммутаторе п генераторе тактовых импульсов, вход которого является вторым входом бло- ка, первый выход соединен со счетным входом счетчика, первыми входами второго элемента ИЛИ, первог о и второго элементов ИЛИ-НЕ и является восьмым выходом блока, второй выход генератора тактовых импульсов является четвертым выходом блока, вход элемента задержки является пятым входом блока, второй вход первого элемента ИЛИ объедииен с вторым входом второго эле-

JJ- I

371

TnJTJTJTJTJTJTJTJTJTJTJTTLnjlJTJ

W

512

мента ИЛИ, первым входом первой группы входов коммутатора, соединен с пер- Bbw выходом дешифратора, который является первым выходом блока, второй вход элемента И объединен с вторым входом первого элемента ИПИ-НЕ, вторым входом первой группы входов коммутатора и соединен с вторым выходом дешифратора, остальные выходы которого соединены с соответствующими входами первой группы входов коммутатора, вторая группа входов которого является местными входами блока, а выход коммутатора соединен с вторым входом второго элемента ИЛИ-НЕ и является седьмым выходом блока, входы дешифратора соединены с соотпетствующими выходами счетчика, вход сброса которого является четвертым входом блок, выход второго элемента ИПИ соединен с первым установочным входом триггера, второй и третий установочные входы которого являются соответственно Первым и третьим входами блока, а выход триггера является третьим выходом блока, выходы элемента И, первого и второго элементов UJUI-HK являются соответст-. венно вторым, пятым и шестым выходами блока.

| Устройство для автоматической разгрузки синхронных машин при их перегрузке | 1956 |

|

SU117667A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-22—Подача