Изобретение относится к электросвязи, преимущественно к передаче речевых сообщений, и может быть использовано при разделении речевых сигналов в дуплексных системах связи.

Цель изобретснияч - повышение точности разделения каналов передачи и приема путем уменьшения времени адаптации.

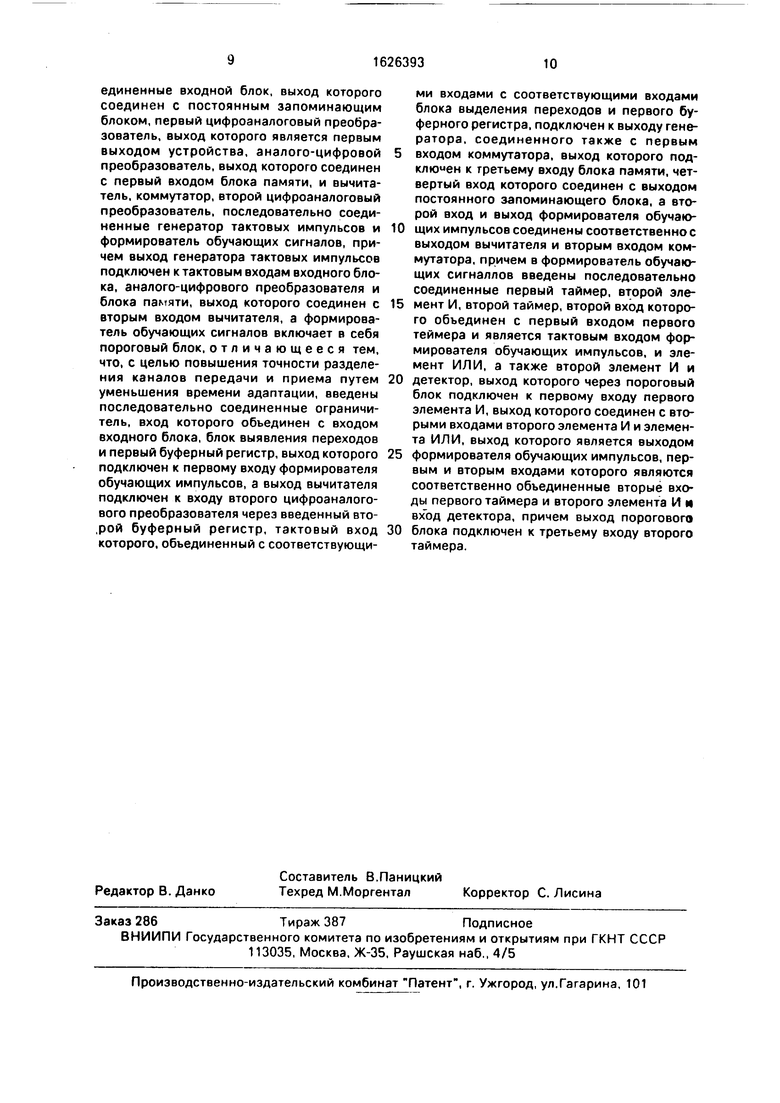

На чертеже приведена структурная схема устройства для разделения речевых сигналов.

Устройство содержит входной блок 1, коммутатор 2, первый цифро-аналоговый преобразователь (ЦАП) 3, аналого-цифровой преобразователь (АЦП) 4, формирователь 5 обучающи: сигналов, блок б памяти, генератор 7 тактовых сигналов, вычитатель 8, первый 9 и второй 10 буферный регистры, второй цифро-анагоговий преобразователь 11, усилитель-ограничитель 12, блок 13 выявления переходов, постоянный запоминающий блок (ПЗБ) 14, детектор 15, пороговый блок 16, первый 17 и второй 18 элементы И, первыйтаймер 19, элемент ИЛИ 20 и второй таймер 21.

Работа устройства осуществляется следующим образом.

Процесс работы может быть разбит на следующие ситуации: присутствует передаваемый сигнал U (t) 0 , отсутствует принимаемый сигнал y(t) 0; присутствует передаваемый сигнал U(t); присутствует принимаемый игнал y(t); отсутствует передаваемый сигнал U(t) 0; присутствует при- нимаемый сигнал y(t); оба гигнала отсутствует.

Настройка устройства производится только в первом случае. В остальных случаях механизм адаптации заблокирован, а из блока 6 памяти только считываются образцу подаваемого сигнала.

Рассмотри работу устройства в первом случае более подробно.

Пусть на вход входного блока 1 поступает сигнал U(t), который на его выходе превращается в квантованный по амплитуде и во времени сигнал Ui(KjAt) , где KAt - дискретный момент времени. Сигнал Ui(KjAt) в первом ЦАП 3 превращается в аналоговую величину g(t), которая в гтвисимости от состояния подключенного канала связи оказывается преобразованной в соответствии с входными параметрами канала связи. В ЦАП 4 производится квантование сигнала по уровню и во времени. При этом сигнал на выходе АЦП 4 и сигнал на выходе входного блока 1 связаны соотношением

gi(KAt)U(KjAt)xZE,(KAt),(1)

где ZЈx(KAt)- отсчет импульсной реакции входных параметров канала связи. Символ Х-означает операцию свертки.

Учитывая линейность операции сверт- к ц, можно сказать, что комбинации Ui(KAt) на выходе входного блока 1 соответствует двоичная комбинация сигнала gi(KAt) на выходе АЦП 4. Аналогично можно написать, что

U2(K2At)(t2)(K2Ajt) из(КзДг)(1з)(КзД1)

(2)

un(KnAt)(tn)(KnAt)

Сигнал g(ti) с выхода первого ЦАП 3 далее поступает в сторону противоположной станции. Как было сказано, принимаемый

сигнал отсутствует, т.е. y(t) 0.

Отсчеты передаваемого сигнала Ui(KAt) поступают одновременно на вход постоянного запоминающего блока 14, Аналитически амплитуда характеристика может

быть описана следующим образом

1 UM1KC

0

UnopXl

U.

U макс

1-НпА

1 + In Unop/rr 1-) UHHC

„pMl-j H-IS

UUMCUnoo

1 +lnA

I 1

(3)

Характеристика, соответствующая выражению (3), является квазилогарифмической, так как имеет линейный участок для самых малых амплитуд. Здесь Unop - коэффициент компрессии (Unop 87,6). Если передаваемый сигнал Ui(KAt) лежит в

пределах -Unop U(KAt)Ui0p , то каждому входному значению Ui(KAt)ex однозначно соответствует выходное значение Ui(KAt)Bbix , так как на данном участке амплитудная характеристика будет линейной.

Если жеUj(KAt)-Цюр , либо Ui(KAt)Uiop до амплитудная характеристика будет нелинейной. В этом случае не будет однозначного соответствия между двоичноя комбинацией, поступающей на

вход ПЗБ 14, и двоичной комбинацией, получаемой на его выходе, т.е. ПЗБ 14 по существу представляет собой компрессор, позволяющий сжимать динамический диапазон. Но в предлагаемом техническом решении сжимается не сам передаваемый сигнал U(t), а сигналы адресации для управления работой блока 6 памяти. Компрессия сигналов адресации необходима для улучшения работы устройства при различных характеристиках передаваемого сигнала. Как

показывает теория связи, при передаче речевых сигналов сжатия динамического диапазона существенно улучшается отношение сигнал/шум при передаче малых уровней передаваемых речевых сигналов. А малые передаваемые уровни сигналов U(t) являются наиболее вероятными. Таким образом, если передаваемый сигнал лежит в пределах линейного участка работы ПЗБ 14, то адресация блока 6 памяти сохраняется линейной.

В случае передачи сигнала U(t), больше сигнала Unop(lU(t)l miopll . то отсчеты сигнала IU(t)r меньше значения lUnopI . Тогда помимо дискретного представления сигнала U(t) производится выделение переходов через нуль сигнала. С этой целью передаваемый сигнал U(t) поступает на усилитель-ограничитель 12, усиливающий и ограничивающий передаваемый сигнал. Данная операция необходима для правильного определения перехода сигнала через нуль. Далее сигнал U(t) с выхода усилителя- ограничителя 12 поступает на вход блока 13 выявления переходов.

Сигнал с выхода блока 13 поступает на вход последовательного первого буферного регистра 9, назначение которого учесть задержку преобразования сигналов U(t) вс входном блоке 1, первом ЦАП 3 и АЦП 4 (сигнал задерживается на 4 тактовых интервала периода выборки). Сигнал с выхода первого буферного регистра 9 далее поступает на вход формирователя 5 обучающих сигналов, где данный сигнал запускает первый таймер 19 и кратковременно открывает второй элемент И 18. Тактовые импульсы с выхода генератора 7 поступают в формирователе обучающих сигналов на вход первого таймера 19. Последний начинает изменять свое состояние от минимального возможного до максимального. До тех пор, пока на вход входного блока 1 и усилителя-ограничителя 12 поступает сигнал, первый таймер 19 периодически обнуляется, не достигнув максимально возможного состояния. Если же U(t) 0, то спустя некоторой промежуток времени первый таймер 19 достигает своего максимального состояния, на его выходе появится логический нуль, закрывающий первый элемент И 17, который будет открыт только тогда, когда сигнал U(t) & 0, т.е. выдерживается первое условие. Второе условие первой ситуации y(t) 0 проверяется с помощью блока 6 памяти, вычитателя 8, детектора 15, порогового блока 16 и второго элемента И 18.

В случае, если на вход входного блока 1 поступает сигнал U(t), который превращается в нулевую двоичную цифровую комбинацию 000...002, то в это же время на входе блока 13 будет также присутствовать сигнал, отмечающий переход сигнала U(t) через нуль. Сигнал Uo(KAt) проходит через ПЗБ 14 без изменения и тем самым в блоке 6 памяти указывается нулевой адрес, из которого вначале считывается содержимое. Так как в начале сеанса связи блок 6 был обнулен, то из ячейки памяти с нулевым адресом считывается нуль, который поступает на один из входов 8 вычитания. При поступлении на вход первого ЦАП 3 сигнала Uo(KAt) , на его выходе будет сигнал, близкий к нулю, тогда и на выходе АЦП 4 будет сигнал go(KAt) 0.

Если из канала связи сигнала y(t) не будет, то на выходе АЦП 4 будем наблюдать лишь одну состаляющую go(KAt) . Если же из канала связи приходит сигнал y(t) &Q , то на выходе АЦП 4 будем наблюдать сигнал, равный go(KAt)+yi(KAt) 0 . Итак, в

случае принимаемого сигнала, т.е. y(t) 0, на выходе вычитателя 8 будем иметь сигнал, равный

Lo(KAt)go(KAt)(KAt). (4) Сигнал с выхода вычитателя 8 поступает на вход детектора 15, где производится преобразование по абсолютно величине. Таким образом, все отсчеты, имеющие положительный знак, проходят через детектор 15

без изменения, а все отрицательные отсчеты -Lj(KAt) превращаются в детектор 15 в сигнал +Lj(KAt) . Сигнал с выхода детектора 15 далее поступает на вход порогового блока 16, имеющего порог срабатывания

Nnop.

Если ILi(KAt) Nnop , то на выходе порогового блока 16 будет логическая единица. В случае, если I Lj(KAt) I Nnop , то на выходе порогового блока 16 логический

нуль. Во втором элементе И 18 сравниваются два сигнала. Первый из них - сигнал с выхода первого буферного регистра 9, который отмечает переходы сигнала U(t) через нуль. Вторым сигналом является сигнал с

выхода порогового блока 16, проверяющий отсутствие принимаемого сигнала, т.е. y(t) 0. При совпадении этих событий на выходе второго элемента И 18 появляется короткий строб импульса положительной полярности,

который поступает на вход первого элемента И 17, который срабатывает, если первый таймер 19 не достиг своего максимального состояния, т.е. U(t) 0 . В этом случае запускается второй таймер 21.

Второй таймер 21, сработав, выдает логическую единицу на своем выходе, которая поступает на вход элемента ИЛИ 20, на второй вход которого выдается сигнал с выхода второго элемента И 18, Таким образом, элемент ИЛИ 20 блокирует прохождение сигнала управления с выхода второго 21 таймера на время совпадения первой части, т.е., если входной блок 1 генерирует сигнал U(t) 0. Блокировка необходима для того, чтобы принудительно в нулевую ячейку блока памяти записать отклик канала связи go(KAt) . Такая запись необходима для того, чтобы независимо от состояния блока 6 памяти жестко проверять отсутствие принимаемого сигнала. Время работы второго таймера 21 выбирается из условия

Ттаймера21 туг- i(5)

где fn - нижняя частота передаваемого сигнала.

Режимом работы блока 6 памяти управляет сигнал с выхода коммутатора 2. Сигналом управления работы коммутатора 2 является выходной сигнал генератора 7, т.е. частота дискретизации Fg. При поступлении с выхода генератора 7 логического нуля коммутатор 2 коммутирует на управляющий вход блока 6 памяти сигнал логического нуля. По данному сигналу из блока 6 памяти вначале считывается информация по адресу, поступающему с выхода ПЗБ 14. Если сигнал управления работой коммутатора 2 равен логической единице, то коммутатор 2 коммутирует выходной сигнал элемента ИЛИ 20 на вход управления блока 6. Таким образом, если второй таймер 21 срабатывает, то это означает полное выполнение условий первой ситуации, и в блок 6 памяти по соответствующим адресам записываются отклики канала связи на двоичные цифровые комбинации. Так, в ячейку памяти Ui(KAt) згписывается отклик канала gi(KAt) , в ячейку памяти l)2(KAt) - g2(KAt) и т.д. При записи образцов gi(KAt) постоянно контролируется выполнение условия работы, контроль необходим, чтобы в блок 6 памяти совместно с откликами канала связи не записалась помеха в виде отсчетов принимаемого сигнала. Подтверждение выполнения условия делает формирователь 5.

Рассмотрим поведение системы в случае выполнения вторых условий.

В случае присутствия передаваемого U(t) и принимаемого y(t) сигналов механизм подстройки будет заблокирован. В самом деле,пусть на временном интервале t n на вход входного блока 1 поступает сигнал U(tn), а из канала связи приходит сигнал

0

y(tn). Тогда на выходе входного блока 1 будет сигнал Ui(KnAt), а на выходе АЦП 4 - сигнал gi(KnAt)+yj(KnAt) . Данный сигнал поступает на один из входов вычитателя 8. Из блока 6 памяти выводится отклик канала связи gi(KmAt) на цифровую комбинацию Ui(KmAt) . На выходе вычитателя 8 будем наблюдать следующую картину

L,(KAt)gi(KnAt)+yi(KnAt)-gl(KnAt) Yj(KnAt)(6)

Таким образом, на выходе вычитателя 8 будет принимаемый сигнал yj(KnAt) , который по окончании цикла расчета вначале 5 записывается во второй буферный регистр 10 в виде двоичного параллельного числа, а затем преобразуется jo втором ЦАП 11 в аналоговую величину y(t) и выдается потре- бителю. Так как сигналы U(t)0n 0 У() О , то на выходе первого таймера 19 будет логический нуль. Следовательно, первый 17 и второй 18 элементы И будут закрыты и запись в блок 6 памяти не будет. В этом режиме производится только считывание 5 информации из блока 6.

Блокировка записи отсчетов Li(KAt) в блок 6 памяти производится по третьему входу во втором таймере 21. Сигнал с выхода порогового блока 16. равный логическому 0 нулю, переводит второй таймер 21 в выключенное состояние. В этом случае на первый вход элемента ИЛИ 20 поступает логический нуль и тем самым сразу же блокируется запись новых образцов сигнала в блок 6 5 памяти.

Рассмотрим поведение устройства при выполнении третьего и четвертого условий. При этом четвертое условие является частным случаем третьего, Если передаваемый 0 сигнал не передается, т.е. U(t) 0, то не будет переходов через нуль. Следовательно, первый таймер 19 достигнет своего максимального значения и на его выходе будет логический нуль. Превый элемент И 17 будет 5 закрыт в записи в блок 6 памяти не будет, из него будет только считываться информация. Пусть из канала связи приходит сигнал y(t|). На выходе АЦП 4 будет сигнал YL()

На выходе вычитателя 8 наблюдаем тот

0 же сигнал YL(KLAI) , так как не нулевой

отсчет Uo(KAt) из блока 6 памяти выводится

go(KAt)0

LL(KLAt)YL(KLAt)(KLAt) (7) Таким образом, в одной полосе частот 5 огранизовано два направления передачи и непрерывная подстройка устройства в паузах речевого сигнала.

Формула изобретения Устройство для разделения речевых сигналов, содержащее последовательно соединенные входной блок, выход которого соединен с постоянным запоминающим блоком, первый цифроаналоговый преобразователь, выход которого является первым выходом устройства, аналого-цифровой преобразователь, выход которого соединен с первый входом блока памяти, и вычита- тель. коммутатор, второй цифроаналоговый преобразователь, последовательно соединенные генератор тактовых импульсов и формирователь обучающих сигналов, причем выход генератора тактовых импульсов подключен к тактовым входам входного блока, аналого-цифрового преобразователя и блока памяти, выход которого соединен с вторым входом вычитателя, а формирователь обучающих сигналов включает в себя пороговый блок, отличающееся тем, что, с целью повышения точности разделения каналов передачи и приема путем уменьшения времени адаптации, введены последовательно соединенные ограничитель, вход которого объединен с входом входного блока, блок выявления переходов и первый буферный регистр, выход которого подключен к первому входу формирователя обучающих импульсов, а выход вычитателя подключен к входу второго цифроаналого- вого преобразователя через введенный второй буферный регистр, тактовый вход которого, объединенный с соответствующими входами с соответствующими входами блока выделения переходов и первого буферного регистра, подключен к выходу генератора, соединенного также с первым

входом коммутатора, выход которого под- клюиен к третьему входу блока памяти, четвертый вход которого соединен с выходом постоянного запоминающего блока, а второй вход и выход формирователя обучающих импульсов соединены соответственно с выходом вычитателя и вторым входом коммутатора, причем в формирователь обучающих сигналлов введены последовательно соединенные первый таймер, второй элемент И, второй таймер, второй вход которого объединен с первый входом первого теймера и является тактовым входом формирователя обучающих импульсов, и элемент ИЛИ, а также второй элемент И и

детектор, выход которого через пороговый блок подключен к первому входу первого элемента И, выход которого соединен с вторыми входами второго элемента И и элемента ИЛИ, выход которого является выходом

формирователя обучающих импульсов, первым и вторым входами которого являются соответственно объединенные вторые входы первого таймера и второго элемента И и вх од детектора, причем выход порогового

блока подключен к третьему входу второго таймера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2223599C2 |

| Устройство для разделения сигналов двух направлений | 1989 |

|

SU1658393A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

Изобретение относится к электросвязи, преимущественно к передаче речевых сообщений, и может быть использовано при разделении речевых сигналов в дуплексных системах связи. Целью изобретения является повышение точности разделения путем уменьшения времени адаптации. Устройство содержит входной блок 1, коммутатор 2, первый цифроаналоговый преобразователь (ЦАП) 3, аналого-цифровой преобразователь 4, формирователь 5 обучающих сигналов, блок 6 памяти, генератор 7 тактовых импульсов, вычиталель 8, первый буферный регистр 9, второй буферный регистр 10,второй ЦАП 11, усилитель-ограничитель 12, блока 13 выявления переходов, постоянный запоминающий блок 14, детектор 15, пороговый блок 16, первый 17 и второй 18 элементы И, первый 19 и второй 21 таймеры, элемент ИЛИ 20. Поставленная цель достигается благодаря непрерывной подстройке устройства в паузах речевого сигнала. 1 ил. -s Ј Qs N5 ( СО ю GJ

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1390803A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-02-07—Публикация

1989-02-23—Подача