У

е

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ отбраковки КМОП интегральных схем по уровням надежности | 1985 |

|

SU1269061A1 |

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| СПОСОБ РАЗБРАКОВКИ КМОП МИКРОСХЕМ, ИЗГОТОВЛЕННЫХ НА КНД СТРУКТУРАХ, ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2010 |

|

RU2444742C1 |

| СПОСОБ ИСПЫТАНИЙ НА НАДЕЖНОСТЬ ИЗДЕЛИЙ ЭЛЕКТРОННОЙ ТЕХНИКИ | 1991 |

|

RU2100817C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ СТОЙКОСТИ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ И БЛОКОВ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИХ ИЗЛУЧЕНИЙ | 2012 |

|

RU2504862C1 |

| СПОСОБ РАЗБРАКОВКИ КМОП МИКРОСХЕМ, ИЗГОТОВЛЕННЫХ НА КНД СТРУКТУРАХ, ПО СТОЙКОСТИ К РАДИАЦИОННОМУ ВОЗДЕЙСТВИЮ | 2007 |

|

RU2364880C1 |

| Способ определения стойкости к радиационным и температурным воздействиям наноэлектронного резонансно-туннельного диода (РТД) на основе многослойных AlGaAs (алюминий, галлий, арсеникум) полупроводниковых гетероструктур | 2015 |

|

RU2606174C1 |

| Способ проведения многофакторных эквивалентно-циклических испытаний | 2021 |

|

RU2783770C1 |

| СПОСОБ ПРОВЕДЕНИЯ ИСПЫТАНИЙ НА СТОЙКОСТЬ СЛОЖНОФУНКЦИОНАЛЬНЫХ МИКРОСХЕМ К СТАТИЧЕСКОМУ ДЕСТАБИЛИЗИРУЮЩЕМУ ВОЗДЕЙСТВИЮ | 2018 |

|

RU2686517C1 |

| СПОСОБ РАЗДЕЛЕНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПО РАДИАЦИОННОЙ СТОЙКОСТИ И НАДЕЖНОСТИ | 2003 |

|

RU2254587C1 |

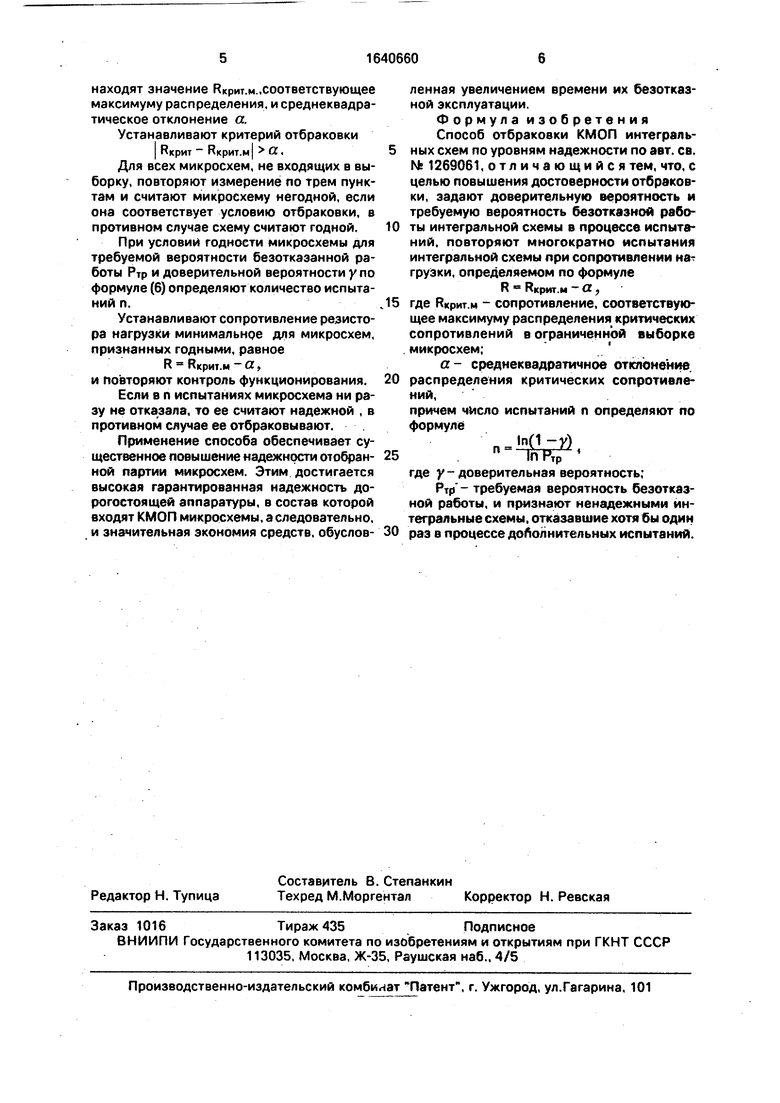

Изобретение i позволяет повысить точность отбраковки путем уменьшения ошибки первого рода, определяющей долю элементов пониженного качества, попавших в класс повышенного качества. Цель изобретения - повышение достоверности отбраковки. Отбраковку осуществляют по величине переменного резистора 2 нагрузки, включенного в цепь источника 1 питания последовательно с испытуемой микросхемой 3. Критическим считается сопротивление, при котором наступает функциональный отказ испытуемой микросхемы, регистрируемый блоком 4 функционально- параметрического контроля. В способе оптимизировано число испытаний для достижения заданной надежности. 1 ил.

Оч

&

о

Os

о

ю

Изобретение относится к технической диагностике и является усовершенствованием изобретения по авт. св. № 1269061.

Цель изобретения - повышение достоверности отбраковки.

Сущность способа основана на том, что функционирование микросхем контролируют методом функционально-параметрического контроля, а под отказом микросхемы понимают функциональный отказ, т.е. в процессе испытаний контролируют величину выходного напряжения на i-м выходе микросхемы через время задержки 1К после подачи на вход микросхемы сигнала логического нуля или логической единицы. Под функциональным отказом понимают отклонение выходного напряжения логической единицы в меньшую, а логического нуля в большую сторону по сравнению с заданными в технических условиях.

Параметр считается соответствующим норме, если выходное напряжение микросхемы через время tK соответствует заданному в технических условиях. Включение резистора нагрузки в цепь питания микро- схемы и увеличение его сопротивления приводит к тому, что, начиная с некоторого критического значения (Ркрит) сопротивления резистора нагрузки, микросхема перестает срабатывать, т.е. у нее наступает функцио- нальный отказ в приведенном выше смысле.

Таким образом, для отбраковки микросхемы определенной серии выбирают контрольную партию. Осуществляют проверку функционирования каждой микросхемы партии в процессе увеличения сопротивления резистора нагрузки с шагом 100 - 300 Ом. Определяют величину критического сопротивления нагрузки каждой микросхемы из партии. По результатам измерений строят гистограмму распределения Вкрит. По гистограмме определяют наиболее вероятное значение Вкрит.м в контрольной партии и его среднеквадратическое отклонение

.32

а

крит. (1)

где . - дисперсия распределения.

Микросхемы считают ненадежными, если выполняется условие

| Ккрит. - Нкрит.м а.(2)

Эти микросхемы отбраковывают.

Задача повышения достоверности отбраковки сводится к выбору из отобранной совокупности изделий тех из них, которые составляют класс повышенного качества.

По результатам отбора исходим из того, что в процессе дальнейших испытаний отобранные микросхемы должны работать безотказно. Определим количество испытаний,

5

0 5 0

5 0

5 0

5

0

5

(5)

(6)

которые необходимо произвести с каждой микросхемой, чтобы гарантировать требуемую вероятность безотказной работы Ртр при заданной доверительной вероятности у и нижней границе ее изменения Руд

Известно, что при проведении испытаний по биноминальной схеме при отсутствии отказов в процессе испытаний

Ру (1-у,О)

где п - минимальное количество испытаний.

Для определения количества минимально необходимых испытаний положим Ру Ртр.

При этом условии соотношение (3) принимает вид

РтР(1-у)1/п(4)

Логарифмируя неравенство (4), получим

KiT

° - ID Ртр

Ограничиваясь минимальным значением п, получим

n-K1-X)t

. 1П Ртр

откуда и следует формула изобретения.

На чертеже показана схема реализации способа.

На схеме обозначены источник 1 питания, переменный резистор 2 нагрузки, испытуемая микросхема 3, блок 4 функционально-параметрического контроля, например стенд контроля интегральных схем Повод.

Напряжение питания с источника 1 подается на последовательно соединенные резистор 2 нагрузки и испытуемую микросхему 3. С блока 4 функционально-параметрического контроля подают на входы интегральной микросхемы напряжение логического нуля и логической единицы. Одновременно блок 4 регистрирует напряжение на соответствующих выходах испытуемой логической микросхемы через время задержки сигнала tt. Этим достигается проверка функционирования микросхемы.

Способ осуществляется следующим образом.

Изменяют величину сопротивления резистора нагрузки через 100 - 300 Ом. При каждом значении сопротивления резистора нагрузки осуществляют проверку функционирования и регистрируют величину сопротивления резистора нагрузки, при котором наступает функциональный отказ микросхемы. Это сопротивление считается Икрит. Далее повторяют измерение Якрит для каждой микросхемы ограниченной выборки. По данным измерений строят гистограмму распределения значений Ркрит По гистограмме

находят значение Ркрит.м..соответствующее максимуму распределения, и среднеквадра- тическое отклонение а.

Устанавливают критерий отбраковки

| °крит - Нкрит.м О,

Для всех микросхем, не входящих в выборку, повторяют измерение по трем пунктам и считают микросхему негодной, если она соответствует условию отбраковки, в противном случае схему считают годной.

При условии годности микросхемы для требуемой вероятности безоткаэанной работы РТр и доверительной вероятности у по формуле (6) определяют количество испытаний п.

Устанавливают сопротивление резистора нагрузки минимальное для микросхем, признанных годными, равное

R Ккрит.м о, и повторяют контроль функционирования.

Если в п испытаниях микросхема ни разу не отказала, то ее считают надежной , в противном случае ее отбраковывают.

Применение способа обеспечивает существенное повышение надежности отобран- ной партии микросхем. Этим достигается высокая гарантированная надежность дорогостоящей аппаратуры, в состав которой входят КМОП микросхемы, а следовательно, и значительная экономия средств, обуслов-

ленная увеличением времени их безотказной эксплуатации.

Формула изобретения Способ отбраковки КМОП интегральных схем по уровням надежности по авт. св. № 1269061, отличающийся тем, что, с целью повышения достоверности отбраковки, задают доверительную вероятность и требуемую вероятность безотказной работы интегральной схемы в процессе испытаний, повторяют многократно испытания интегральной схемы при сопротивлении нет грузки, определяемом по формуле

R e Ккрит.м ОС, )

где Якрит.м - сопротивление, соответствующее максимуму распределения критических сопротивлений в ограниченной выборке микросхем;

а- среднеквадратичное отклонение, распределения критических сопротивлений,

причем число испытаний п определяют по формуле

П-Н1-У),

1П Ртр

где у-доверительная вероятность;

Ртц требуемая вероятность безотказной работы, и признают ненадежными интегральные схемы, отказавшие хотя бы один раз в процессе дополнительных испытаний.

| Способ отбраковки КМОП интегральных схем по уровням надежности | 1985 |

|

SU1269061A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-04-07—Публикация

1988-09-22—Подача