Изобретение относится к вычислительной технике и может быть применено для сопряжения каналов ввода-вывода ЭВМ с удаленными внешними абонентами через обычный или волоконно- оптический кабель

Целью изобретения является повышение быстродействия и сокращение аппаратурных затрат

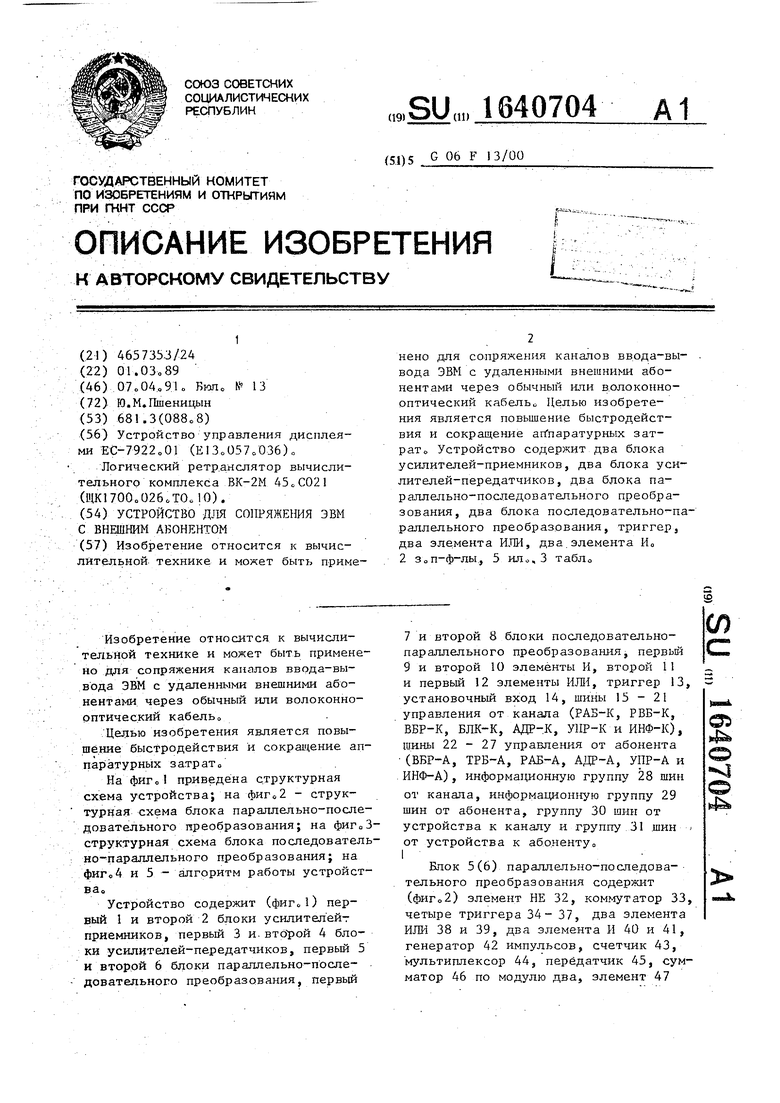

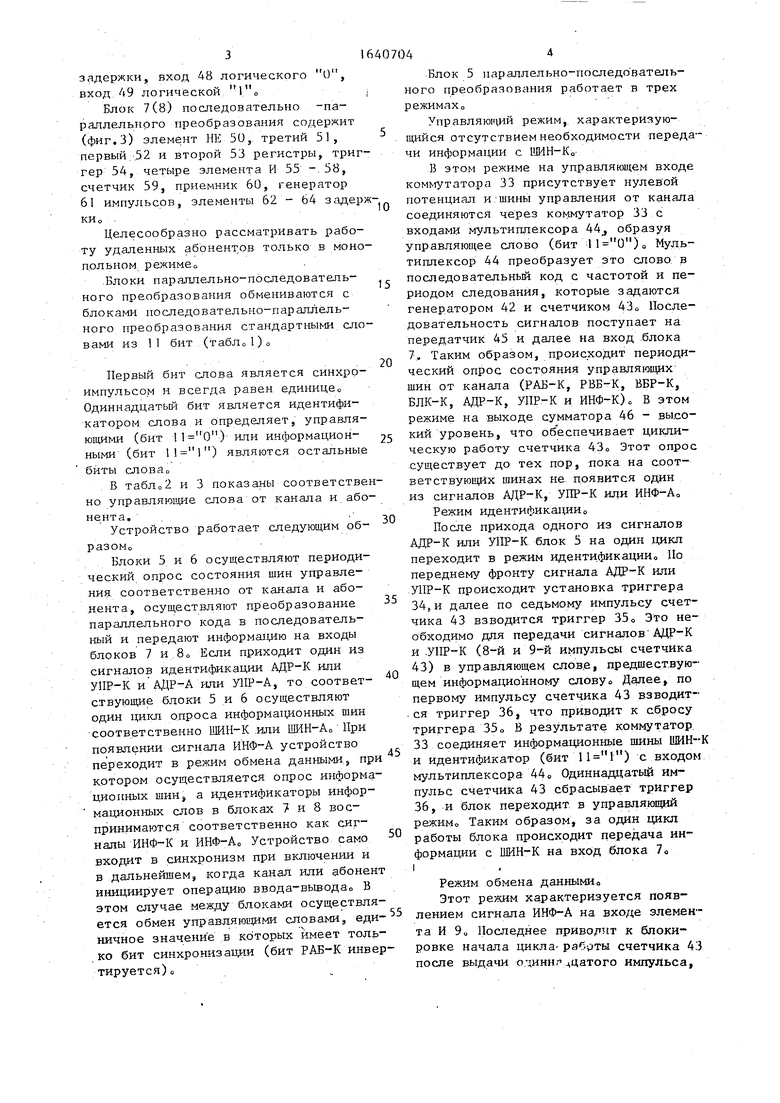

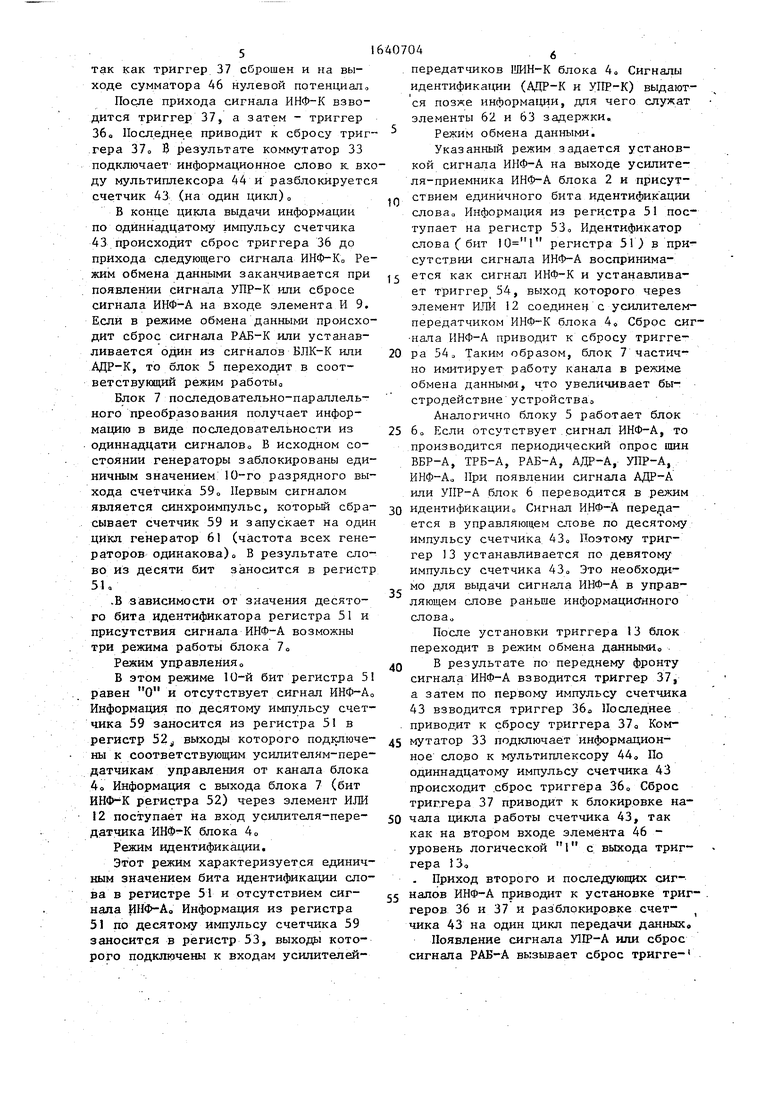

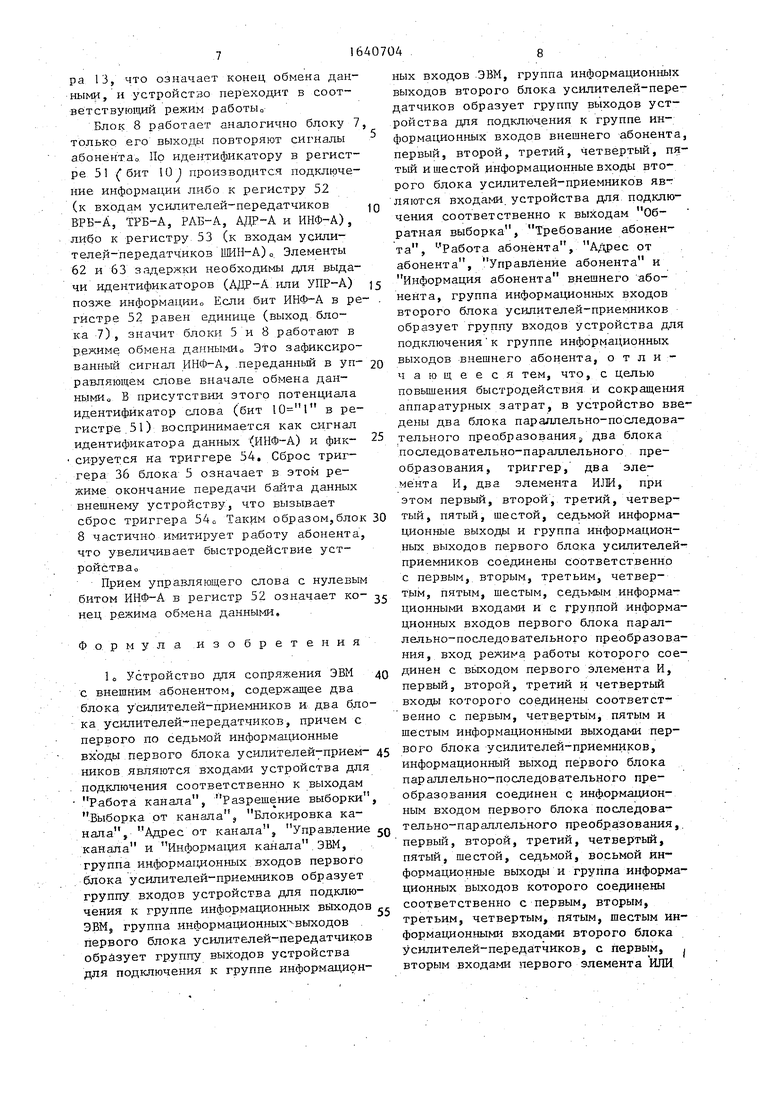

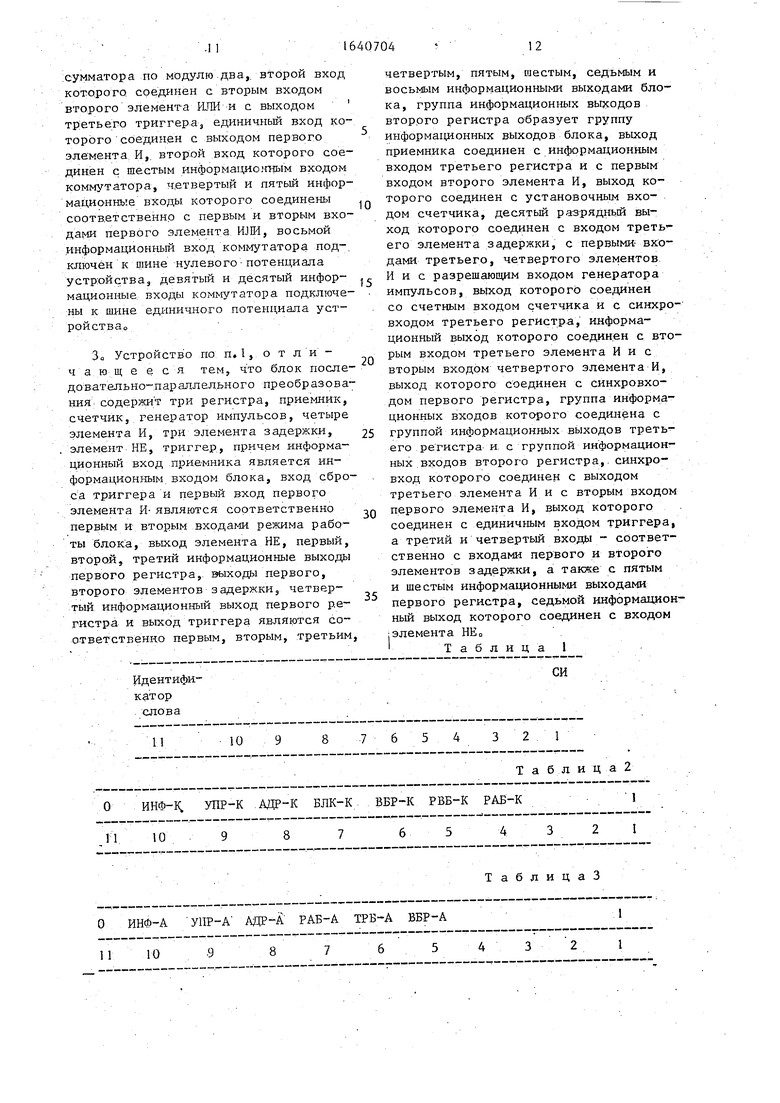

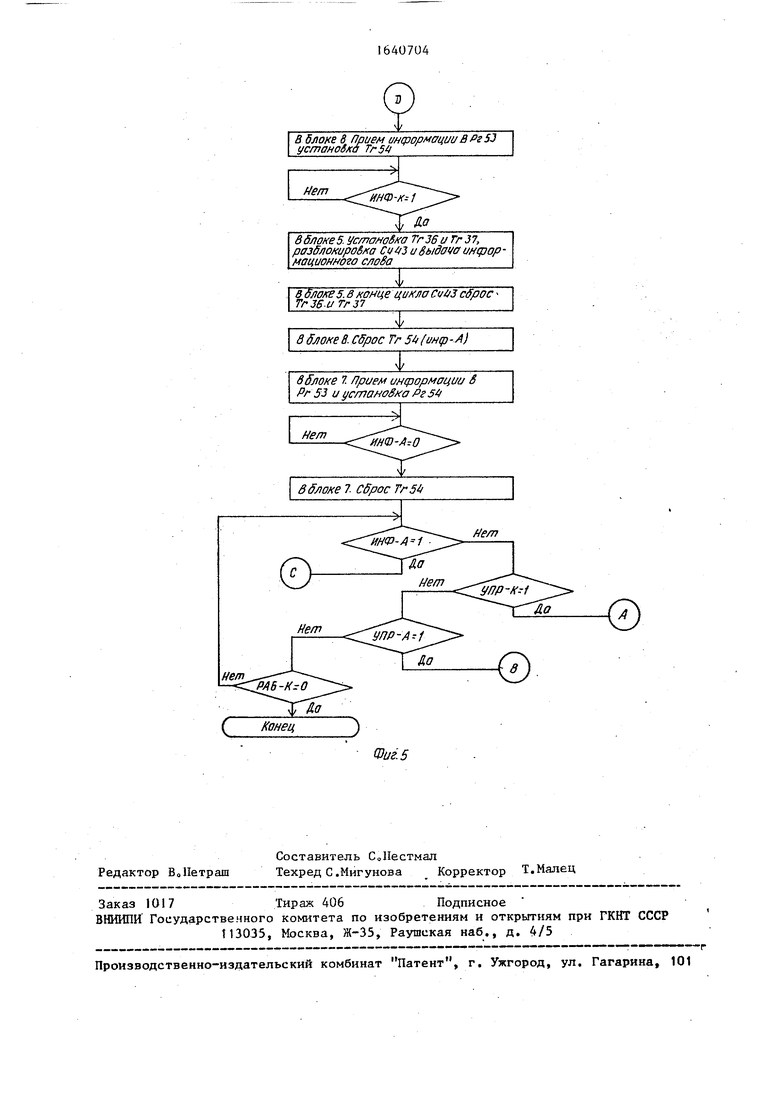

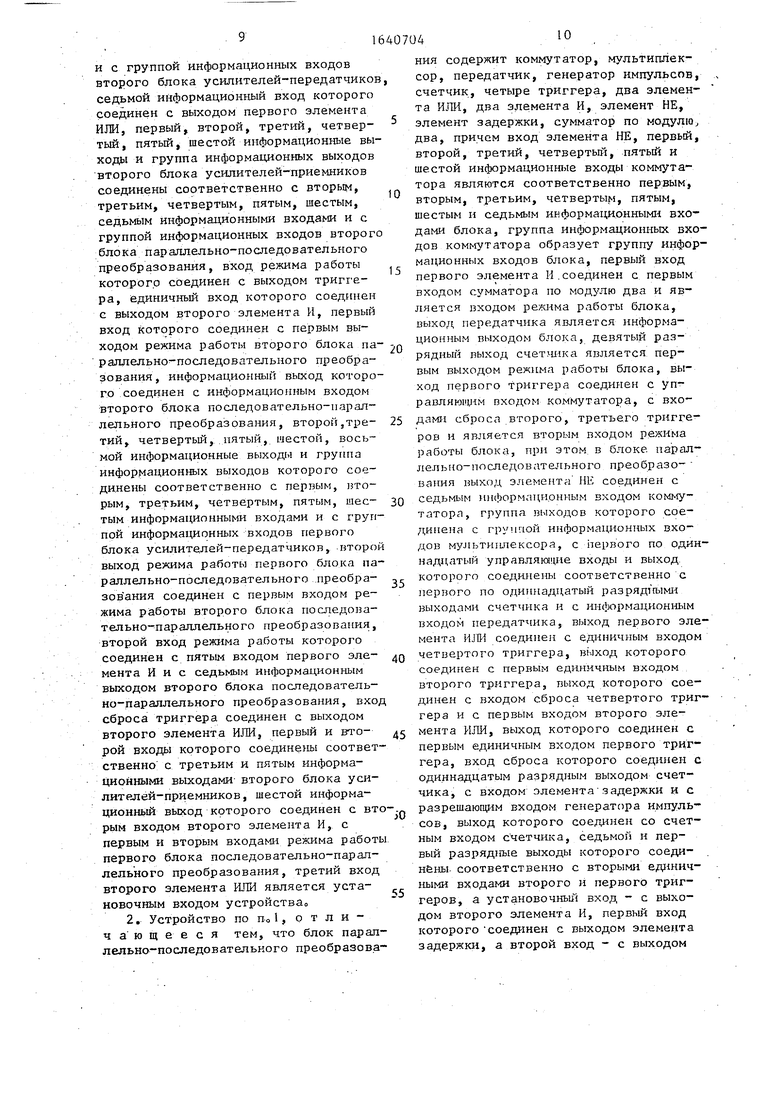

На фиг приведена структурная схема устройства; на - структурная схема блока параллельно-последовательного преобразования; на структурная схема блока последовательно-параллельного преобразования; на и 5 - алгоритм работы устройства,,

Устройство содержит () первый 1 и второй 2 блоки усилителей- приемников, первый 3 и второй 4 блоки усилителей-передатчиков, первый 5 и второй 6 блоки параллельно-последовательного преобразования, первый

7 и второй 8 блоки последовательно- параллельного преобразования, первый 9 и второй 10 элементы И, второй 11 и первый 12 элементы ИЛИ, триггер 13, установочный вход 14, шины 13-21 управления от канала (РАБ-К, РВБ-К, ВБР-К, БЛК-К, АДР-К, УПР-К и ИНФ-К), щины 22-27 управления от абонента (ВБР-А, ТРБ-А, РАБ-А, АДР-А, УПР-А и ИНФ-А), информационную группу 28 шин от канала, информационную группу 29 шин от абонента, группу 30 шин от устройства к каналу и группу 31 шин

от устройства к абоненту,, I

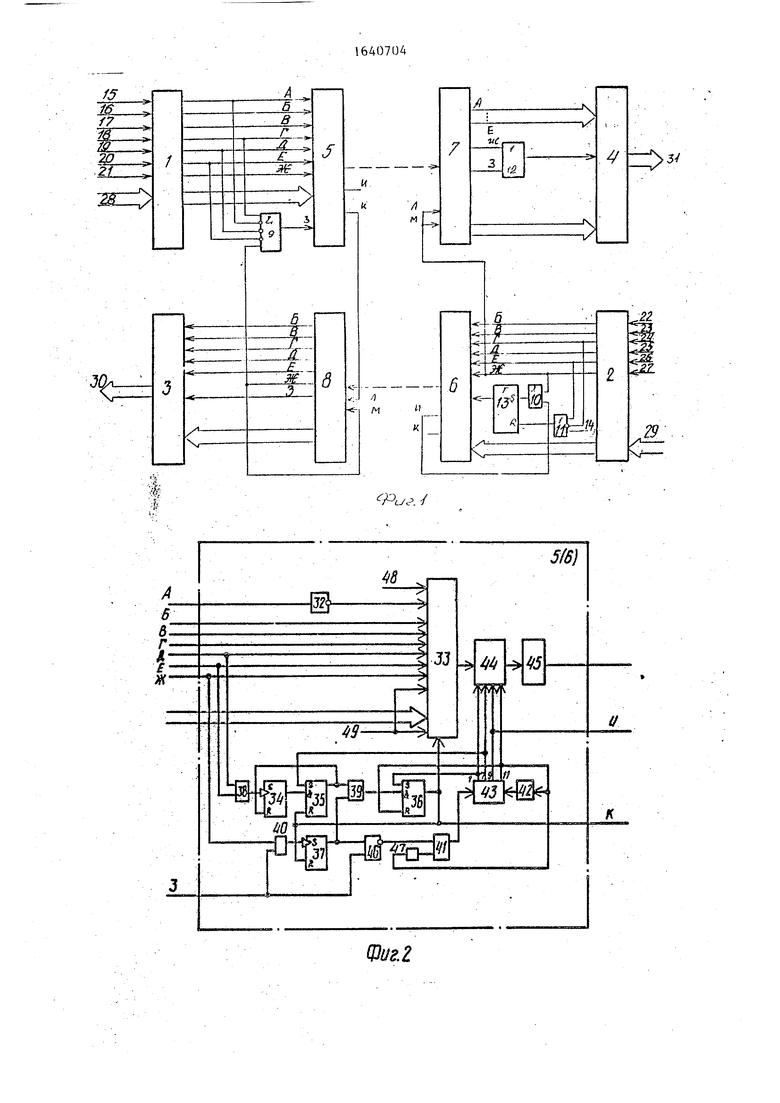

Блок 5(6) параллельно-последовательного преобразования содержит () элемент НЕ 32, коммутатор 33, четыре триггера 34- 37, два элемента ИЛИ 38 и 39, два элемента И 40 и 41, генератор 42 импульсов, счетчик 43, мультиплексор 44, передатчик 45, сумматор 46 по модулю два, элемент 47

(Л

с

о

Јь

о J

задержки, вход 48 логического О, вход 49 логической ,t

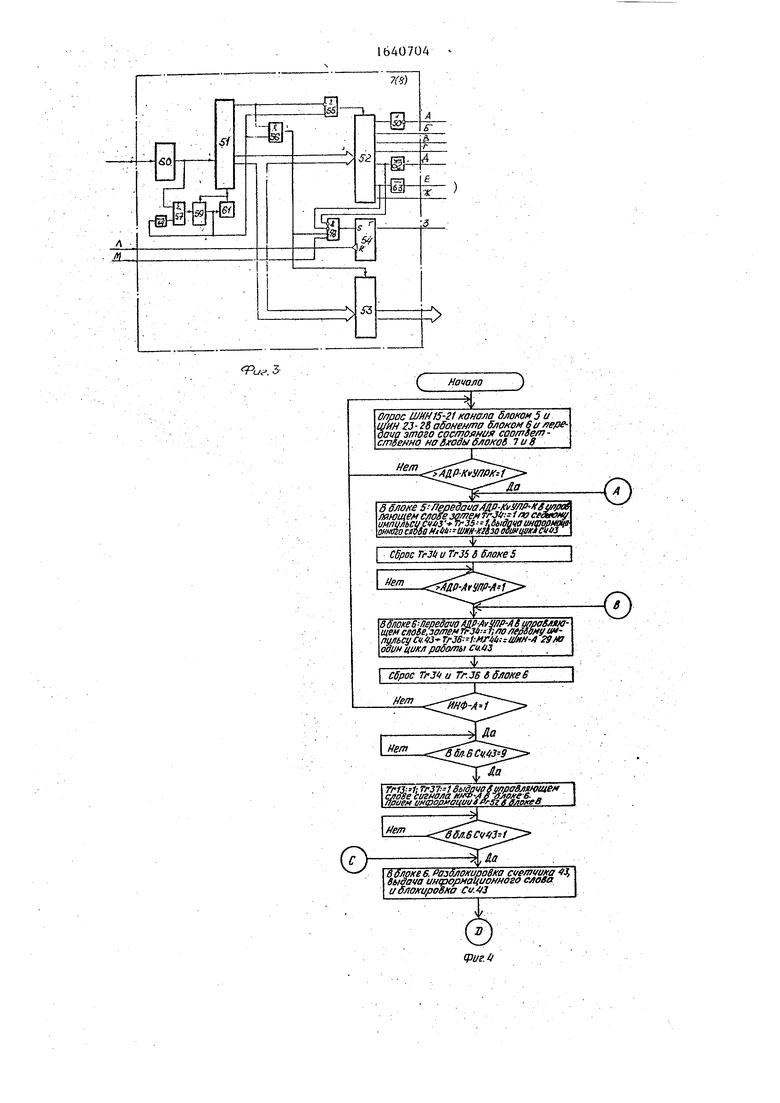

Блок 7(8) последовательно -параллельного преобразования содержит (фиг.З) элемент НЕ 50, третий 51, первый 52 и второй 53 регистры, триггер 54, четыре элемента И 55 - 58, счетчик 59, приемник 60, генератор 61 импульсов, элементы 62 - Ь4 задерж

,

КИо

Целесообразно рассматривать работу удаленных абонентов только в монопольном режиме0

Блоки параллельно-последовательного преобразования обмениваются с блоками последовательно-параллельного преобразования стандартными словами из 11 бит (табл01)о

- «

Первый бит слова является синхроимпульсом и всегда равен единице Одиннадцатый бит является идентификатором слова и определяет, управляющими (бит ) или информацией- ными (бит 11) являются остальные биты словао

В табл02 и 3 показаны соответственно управляющие слова от канала и абонента.

Устройство работает следующим об разом0

Блоки 5 и 6 осуществляют периодический опрос состояния шин управления соответственно от канала и абонента, осуществляют преобразование параллельного кода в последовательный и передают информацию на входы блоков 7 и 8о Если приходит один из сигналов идентификации АДР-К или УПР-К и АДР-А или УНР-А, то соответ ствующие блоки 5 и 6 осуществляют один цикл опроса информационных шин соответственно ШИН-К или ШИН-А0 При появлении сигнала ИНФ-А устройство переходит в режим обмена данными, при котором осуществляется опрос информационных шин, а идентификаторы информационных слов в блоках 7 и 8 воспринимаются соответственно как сигналы ИНФ-К и ИНФ-Ао Устройство само входит в синхронизм при включении и в дальнейшем, когда канал или абонент инициирует операцию ввода-вывода0 В этом случае между блоками осуществляется обмен управляющими словами,, единичное значение в которых имеет только бит синхронизации (бит РАБ-К инвертирует ся)0

п

- 10

15

30

20

25

355040

45

Блок 5 параллельно-последовательного преобразования работает в трех режимахо

Управляющий режим, характеризующийся отсутствием необходимости передачи информации с L MH-KQ

В этом режиме на управляющем входе ком гутатора 33 присутствует нулевой потенциал и шины управления от канала соединяются через коммутатор 33 с входами мультиплексора 44, образуя управляющее слово (бит )„ Мультиплексор 44 преобразует это слово в последовательный код с частотой и периодом следования, которые задаются генератором 42 и счетчиком 430 Последовательность сигналов поступает на передатчик 45 и далее на вход блока 7. Таким образом, происходит периодический опрос состояния управляющих шин от канала (РАБ-К, РВБ-К, ВБР-К, БЛК-К, АДР-К, УПР-К и ИНФ-К)о В этом режиме на выходе сумматора 46 - высокий уровень, что обеспечивает циклическую работу счетчика 430 Этот опрос существует до тех пор, пока на соответствующих шинах не появится один из сигналов АДР-К, УПР-К или ИНФ-А0

Режим идентификации;,

После прихода одного из сигналов АДР-К или УНР-К блок 5 на один цикл переходит в режим идентификации„ По переднему фронту сигнала АДР-К или УПР-К происходит установка триггера 34,и далее по седьмому импульсу счетчика 43 взводится триггер 350 Это необходимо для передачи сигналов АДР-К и УПР-К (8-й и 9-й импульсы счетчика 43) в управляющем слове, предшествующем информационному словуе Далее, по первому импульсу счетчика 43 взводится триггер 36, что приводит к сбросу триггера 350 В результате коммутатор 33 соединяет информационные шины ШИН-К и идентификатор (бит ) с входом мультиплексора 440 Одиннадцатый импульс счетчика 43 сбрасывает триггер 36, и блок переходит в управляющий режим Таким образом, за один цикл работы блока происходит передача информации с ШИН-К на вход блока 70 I

Режим обмена даннымиа

Этот режим характеризуется появлением сигнала ИНФ-А на входе элемента И 9о Последнее приводит к блокировке начала цикла- раОрты счетчика 43 после выдачи цатого импульса,

так как триггер 37 сброшен и на выходе сумматора 46 нулевой потенциал„

После прихода сигнала ИНФ-К взводится триггер 37, а затем - триггер 36о Последнее приводит к сбросу триггера 37о В результате коммутатор 33 подключает информационное слово к входу мультиплексора 44 и разблокируется счетчик 43 (на один цикл)„

В конце цикла выдачи информации по одиннадцатому импульсу счетчика 43 происходит сброс триггера 36 до прихода следующего сигнала ИНФ-К„ Режим обмена данными заканчивается при появлении сигнала УПР-К или сбросе сигнала ИНФ-А на входе элемента И 9. Если в режиме обмена данными происходит сброс сигнала РАБ-К или устанавливается один из сигналов БЛК-К или АДР-К, то блок 5 переходит в соответствующий режим работыо

Блок 7 последовательно-параллельного преобразования получает информацию в виде последовательности из одиннадцати сигналово В исходном состоянии генераторы заблокированы единичным значением 10-го разрядного выхода счетчика 59 Первым сигналом является синхроимпульс, которьй сбрасывает счетчик 59 и запускает на один цикл генератор 61 (частота всех генераторов одинакова) В результате слово из десяти бит заносится в регистр 51,

.В зависимости от значения десятого бита идентификатора регистра 51 и присутствия сигнала ИНФ-А возможны три режима работы блока 7„

Режим управленияо

В этом режиме 10-й бит регистра 51 равен О и отсутствует сигнал ИНФ-А„ Информация по десятому импульсу счетчика 59 заносится из регистра 51 в регистр 52 выходы которого подключены к соответствующим усилителям-передатчикам управления от канала блока 40 Информация с выхода блока 7 (бит ИНФ-К регистра 52) через элемент ИЛИ 12 поступает на вход усилителя-передатчика ИНФ-К блока 4 0

Режим идентификации.

Этот режим характеризуется единичным значением бита идентификации слова в регистре 51 и отсутствием сигнала ИНФ-Ао Информация из регистра 51 по десятому импульсу счетчика 59 заносится в регистр 53, выходы которого подключены к входам усшштелей0

5

0

5

передатчиков ШИН-К блока 4о Сигналы идентификации (АДР-К и УПР-К) выдаются позже информации, для чего служат элементы 62 и 63 задержки.

Режим обмена данными.

Указанный режим задается установкой сигнала ИНФ-А на выходе усилителя-приемника ИНФ-А блока 2 и присутствием единичного бита идентификации слова,, Информация из регистра 51 поступает на регистр 53„ Идентификатор слова С бит регистра 51) в присутствии сигнала ИНФ-А воспринимается как сигнал ИНФ-К и устанавливает триггер А, выход которого через элемент ИЛИ 12 соединен с усилителем- передатчиком ИНФ-К блока 4о Сброс сигнала ИНФ-А приводит к сбросу триггера 54 о Таким образом, блок 7 частично имитирует работу канала в режиме обмена данными, что увеличивает быстродействие устройства

Аналогично блоку 5 работает блок 6о Если отсутствует сигнал ИНФ-А, то производится периодический опрос шин ВБР-А, ТРБ-А, РАБ-А, АДР-А, УПР-А, ИНФ-Ао При появлении сигнала АДР-А или УПР-А блок 6 переводится в режим идентификации о Сигнал ИНФ-А передается в управляющем слове по десятому импульсу счетчика 43„ Поэтому триггер 13 устанавливается по девятому импульсу счетчика 430 Это необходимо для выдачи сигнала ИНФ-А в управляющем слове раньше информационного слова

После установки триггера 13 блок переходит в режим обмена данными0

В результате по переднему фронту сигнала ИНФ-А взводится триггер 37, а затем по первому импульсу счетчика 43 взводится триггер 360 Последнее приводит к сбросу триггера 37а Ком- 5 мутатор 33 подключает информационное слово к мультиплексору 440 По одиннадцатому импульсу счетчика 43 происходит сброс триггера 36 Сброс триггера 37 приводит к блокировке на- 0 чала цикла работы счетчика 43, так как на втором входе элемента 46 - уровень логической 1 с выхода триггера 130

Приход второго и последующих сиг- 5 налов ИНФ-А приводит к установке триггеров 36 и 37 и разблокировке счетчика 43 на один цикл передачи данных,,

Появление сигнала УПР-А или сброс сигнала РАБ-А вызывает сброс тригге-

0

5

0

pa 13, что означает конец обмена данными, и устройство переходит в соответствующий режим работыо

Блок 8 работает аналогично блоку 7, только его выходы повторяют сигналы - абонентао По идентификатору в регистре 51 ( бит 10 1 производится подключеие информации либо к регистру 52 (к входам усилителей-передатчикев ВРБ-А, ТРБ-А, РАБ-А, АДР-А и ИНФ-А), ибо к регистру 53 (к входам усилиелей-передатчиков ШИН-А)о Элементы 62 и 63 задержки необходимы для выдачи идентификаторов (АДР-А или УПР-А) $ позже информации,, Если бит ИНФ-А в регистре 52 равен единице (выход блока 7), значит блоки 5 и 8 работают в режиме обмена данными0 Это зафиксированный сигнал ИНФ-А, переданный в уп- 20 равляющем слове вначале обмена данными В присутствии этого потенциала идентификатор слова (бит в регистре 51) воспринимается как сигнал идентификатора данных (ИНФ-А) и фик- 25

сируется на триггере 54. Сброс триггера 36 блока 5 означает в этом режиме окончание передачи байта данных внешнему устройству, что вызывает сброс триггера 540 Таким образом,блок 30 8 частично имитирует работу абонента, что увеличивает быстродействие устройства.,

Прием управляющего слова с нулевым битом ИНФ-А в регистр 52 означает ко- 35 нец режима обмена данными.

Формула изобретения

1 о Устройство для сопряжения ЭВМ 40 с внешним абонентом, содержащее два блока усилителей-приемников и два блока усилителей-передатчиков, причем с первого по седьмой информационные входы первого блока усилителей-прием- 45 ников являются входами устройства для подключения соответственно к выходам

Работа канала, Разрешение выборки, Выборка от канала, Блокировка канала, Адрес от канала, Управление Q канала и Информация канала ЭВМ, группа информационных входов первого блока усилителей-приемников образует группу входов устройства для подключения к группе информационных выходов ЭВМ, группа информационныххвыходов первого блока усилителей-передатчиков образует группу выходов устройства

для подключения к группе информационных входов ЭВМ, группа информационных выходов второго блока усилителей-передатчиков образует группу выходов устройства для подключения к группе информационных входов внешнего абонента, первый, второй, третий, четвертый, пятый и шестой информационные входы второго блока усилителей-приемников являются входами устройства для подключения соответственно к выходам Обратная выборка, Требование абонени У

та, - Работа абонента , Адрес от абонента, Управление абонента и Информация абонента внешнего абонента, группа информационных входов второго блока усилителей-приемников образует группу входов устройства для подключения к группе информационных выходов внешнего абонента, отличающееся тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, в устройство введены два блока параллельно-последовательного преобразованияt два блока последовательно-параллельного преобразования, триггер, два элемента И, два элемента ИЛИ, при этом первый, второй, третий, четвертый, пятый, шестой, седьмой информационные выходы и группа информационных выходов первого блока усилителей- приемников соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым, седьмым информационными входами и с группой информационных входов первого блока параллельно-последовательного преобразования, вход режима работы которого соединен с выходом первого элемента И, первый, второй, третий и четвертый входы которого соединены соответственно с первым, четвертым, пятым и шестым информационными выходами первого блока усилителей-приемников, информационный выход первого блока параллельно-последовательного преобразования соединен с информационным входом первого блока последовательно-параллельного преобразования, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой информационные выходы и группа информационных выходов которого соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым Информационными входами второго блока усилителей-передатчиков, с первым, , вторым входами первого элемента ИЛИ

и с группой информационных входов второго блока усилителей-передатчиков седьмой информационный вход которого соединен с выходом первого элемента ИЛИ, первый, второй, третий, четвертый, пятый, шестой информационные выходы и группа информационных выходов второго блока усилителей-приемников соединены соответственно с вторым, третьим, четвертым, пятым, шестым, седьмым информационными входами и с группой информационных входов второго блока параллельно-последовательного преобразования, вход режима работы которого соединен с выходом триггера, единичный вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым выходом режима работы второго блока параллельно-последовательного преобразования , информационный выход которого соединен с информационным входом второго блока последовательно-параллельного преобразования, второй,третий, четвертый, пятый, шестой, восьмой информационные выходы и группа информационных выходов которого соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым информационными входами и с группой информационных входов первого блока усилителей-передатчиков, второй выход режима работы первого блока параллельно-последовательного преобра- зов ания соединен с первым входом режима работы второго блока последовательно-параллельного преобразования, второй вход режима работы которого соединен с пятым входом первого элемента И и с седьмым информационным выходом второго блока последовательно-параллельного преобразования, вход сброса триггера соединен с выходом второго элемента ИЛИ, первый и второй входы которого соединены соответственно с третьим и пятым информационными выходами второго блока усилителей-приемников, шестой информационный выход которого соединен с вторым входом второго элемента И, с первым и вторым входами режима работы первого блока последовательно-параллельного преобразования, третий вход второго элемента ИЛИ является установочным входом устройства

2. Устройство по По 1, о т л и - чающееся тем, что блок параллельно-последовательного преобразова0

5

0

5

0

5

0

5

O

5

ния содержит коммутатор, мультиплексор, передатчик, генератор импульсов, счетчик, четыре триггера, два элемента ИЛИ, два элемента И, элемент НЕ, элемент задержки, сумматор по модулю, два, причем вход элемента НЕ, первый, второй, третий, четвертый, пятый и шестой информационные входы коммутатора являются соответственно первым, вторым, третьим, четвертым, пятым, шестым и седьмым информационными входами блока, группа информационных входов коммутатора образует группу информационных входов блока, первый вход первого элемента И соединен с первым входом сумматора по модулю два и является входом режима работы блока, выход передатчика является информационным выходом блока, девятый разрядный выход счетчика является первым выходом режима работы блока, выход первого триггера соединен с уп- равлякнцим входом коммутатора, с входами сброса второго, третьего триггеров и является вторым входом режима работы блока, при этом в блоке параллельно-последовательного преобразо- вания выход элемента НЕ соединен с седьмым информационным входом коммутатора, группа выходов которого соединена с груччой информационных входов мультиплексора, с первого по одиннадцатый управляющие входы и выход которого соединены соответственно с первого по одиннадцатый разрядными выходами счетчика и с информационным входом передатчика, выход первого элемента ИЛИ соединен с единичным входом четвертого триггера, выход которого соединен с первым единичным входом второго триггера, выход которого соединен с входом сброса четвертого триг- гера и с первым входом второго элемента ИЛИ, выход которого соединен с первым единичным входом первого триггера, вход сброса которого соединен с одиннадцатым разрядным выходом счетчика, с входом элемента задержки и с разрешающим входом генератора импульсов, выход которого соединен со счетным входом счетчика, седьмой и первый разрядные выходы которого соединены соответственно с вторыми единичными входами второго и первого триггеров, а установочный вход - с выходом второго элемента И, первый вход которого соединен с выходом элемента задержки, а второй вход - с выходом

сумматора по модулю два, второй вход которого соединен с вторым входом второго элемента ИЛИ и с выходом третьего триггераэ единичный вход которого соединен с выходом первого элемента И, второй вход которого соединен с шестым информационным входом коммутатора, четвертый и пятый информационные входы которого соединены

соответственно с первым и вторым входами первого элемента ИЛИ, восьмой информационный вход коммутатора подключен к шине нулевого потенциала устройства., девятый и десятый инфор- ,- мационные входы коммутатора подключены к шине единичного потенциала устройства

Зо Устройство по п.1} отличающееся тем, что блок после довательно-параллельного преобразования содержит три регистра, приемник, счетчик, генератор импульсов, четыре элемента И, три элемента задержки, элемент НЕ, триггер, причем информационный вход приемника является информационным входом блока, вход сброса триггера и первый вход первого элемента И являются соответственно первым и вторым входами режима работы блока, выход элемента НЕ, первый, второй, третий информационные выходы первого регистра, выходы первого, второго элементов задержки, четвертый информационный выход первого регистра и выход триггера являются соответственно первым, вторым, третьим,

10

,-

20

25

30

35

четвертым, пятым, шестым, седьмым и восьмым информационными выходами блока, группа информационных выходов второго регистра образует группу информационных выходов блока, выход приемника соединен с информационным входом третьего регистра и с первым входом второго элемента И, выход которого соединен с установочным входом счетчика, десятый разрядный выход которого соединен с входом третьего элемента задержки, с первыми входами третьего, четвертого элементов И и с разрешающим входом генератора импульсов, выход которого соединен со счетным входом счетчика и с синхро- входом третьего регистра, информационный выход которого соединен с вторым входом третьего элемента И и с вторым входом четвертого элемента И, выход которого соединен с синхровхо- дом первого регистра, группа информационных входов которого соединена с группой информационных выходов третьего регистра и с группой информационных входов второго регистра, синхро- вход которого соединен с выходом третьего элемента И и с вторым входом первого элемента И, выход которого соединен с единичным входом триггера, а третий и четвертый входа - соответственно с входами первого и второго элементов задержки, а также с пятым и шестым информационными выходами первого регистра, седьмой информационный выход которого соединен с входом .элемента НЕ0 Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1615728A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Многоканальное устройство для сопряжения абонентов с каналами ввода-вывода ЭВМ | 1984 |

|

SU1275456A1 |

| Устройство для сопряжения | 1983 |

|

SU1176338A2 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ | 1990 |

|

RU2022346C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

Изобретение относится к вычислительной технике и может быть применено для сопряжения каналов ввода-вывода ЭВМ с удаленными внешними абонентами через обычный или волоконно- оптический кабель Целью изобретения является повышение быстродействия и сокращение аппаратурных затрат Устройство содержит два блока усилителей-приемников, два блока усилителей-передатчиков, два блока параллельно-последовательного преобразования, два блока последовательно-параллельного преобразования, триггер, два элемента ИПИ, два элемента И0 2 ЗоП-ф-лы, 5 ил«,3 табло

11

10

Таблица2 О ИНФ-К УПР-К АДР-К БЛК-К ВБР-К РВБ-К РАБ-К1

«ТТЛ -. . Г.- I-™ -Ц ™ .---- - - - 1111ГТ-И ЛГ.Ц|- ---В-Ц.--I TJИ 1 1- - ----- -J -.- -.-.-. - - - -.-..- .«-

И10987654321

О УПР-А АДР-А РАБ-А ТРБ-А ВБР-А

И10987654

1

ТаблицаЗ

Аус /

fe.Ј

Опрос ШИН 15-21 канала блоком 5 и шин 23- 28 абонента блоком 6а передача этого состояния саотвем- стбенно на бходы блокоб Т и 8

Сброс ГгЗЪ и TrJS д блоке 5

8$локеВ--ПередоиоАДР-АуУЛР-А1упра8ляа- щемсяо&е.зо/пентРЗЬ Ът/геавомуанПуЛЬСу СЧ «J Tr36 1:MrJtlt:;UUH-/l 29М

один цикл работы сиАЗ

Сброс и Тг.ЗБ бйяокеб

J

Тгзт.1 Выдача Sулравлйнхцем сигнала ИНФ-АВ уЯо#е Б- .. - информации iPrsz в елокев

В блоке 6. Разблокировка cvemvma выдача иноэормационного слова и блокировка Си.чз

В блоке 8 Прием информации В 0г 53 установка Тг54

Вдлокеб Усгланойка Тг36и Гг 37, разблокировка Cv43 и выдача информационного слова

в блоке 5. в конце цикла Си43 сброс Тг36иТг37

8 блоке В. Сброс Тг 5Ь (инф-А)

8Јлоке 7. Прием информации 8 Рг 53 и ycfnaHOSxa Рг54

Ла

L

| Папироса с самовоспламеняющейся головкой | 1926 |

|

SU7922A1 |

Авторы

Даты

1991-04-07—Публикация

1989-03-01—Подача