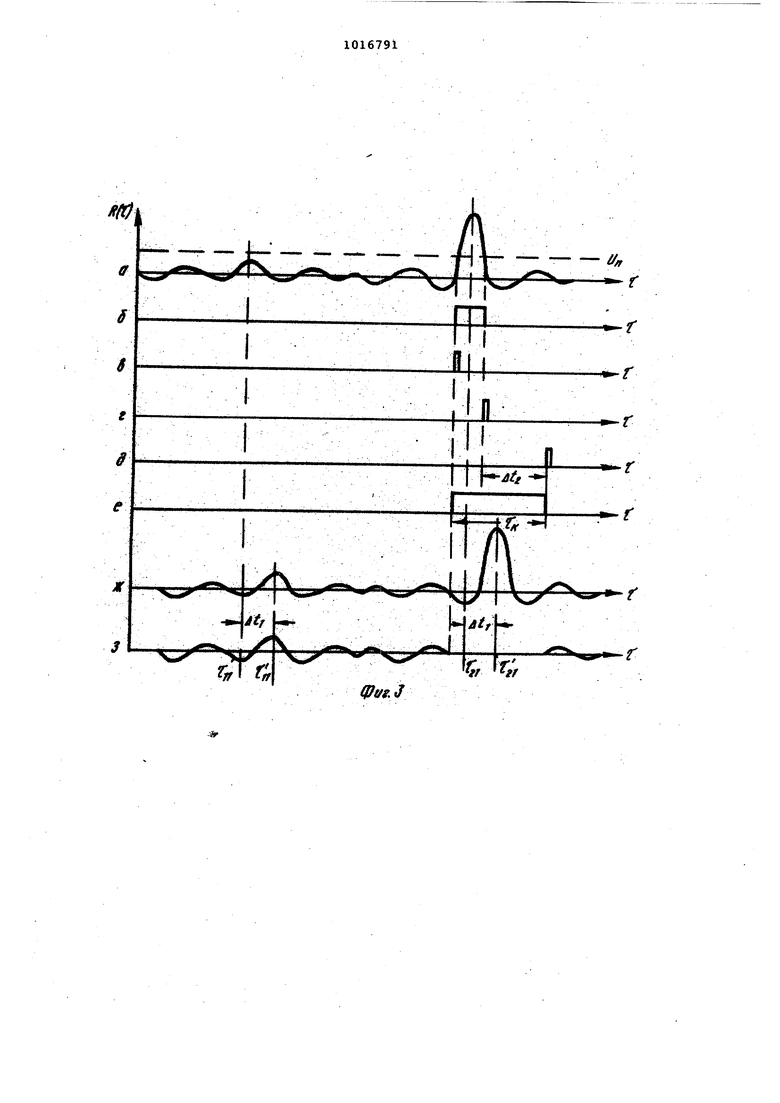

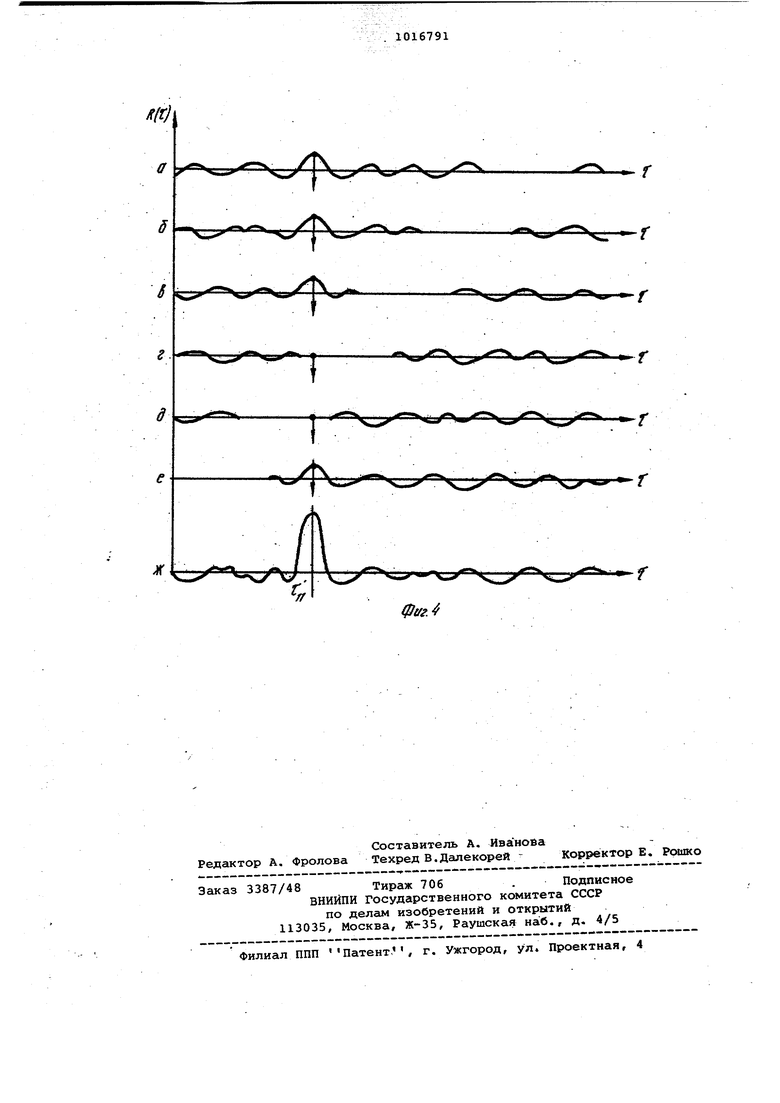

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения аргумента и значения функции взаимной корреляции между случайными процессами, подвергнутыми разным временным искажениям. Известно устройство для определе ния взаимной корреляционной функции между случайными процессами, подвер нутыми разным временным искажениям, в котором перед корреляционной обрабо кой один из исследуемых сигналов по вергается дискретизация с частотой, отличной от частоты дискретизации другого сигнала (1 3. Устройство обладает низким быстродействием, так как в нем осуществляется поиск частоты дискретизации Наиболее близким по технической сущности к предлагаемому является коррелометр, содержащий аналогоцифровые преобразователи, выч:ислите ный блок, два элемента ИЛИ, блок памяти, две группы элементов И, блоки усреднения, два генератора та товых импульсов, делитель частоты, триггер, три счетчика, постоянное запоминающее устройство .и дешифратор . Устройство параллельно создает различные варианты смещений отсчетов частных коррелограмм по оси вре мени, т.е..одновременно строит несколько моделей компенсации изменения задержки между входными Сигналами. Однако при анализе процессов, когда каждый из входных сигналов представляет собой сумму двух и более сигналов, подвергнутых разным временным искажениям, известные уст ройства обладают недостаточной точностью и разрешающей способностью. Особенно это проявляется при анализе процессов, когда из входящих в сумму сигналов один значительно пре восходит по мощности другие. Цель изобретения - увеличение разрешающей способности и точности при ана.Лизе процессов, представленных суммой сигйалов. Поставленная цель достигается те что в устройство для определения взаимных корреляционных функций, содержащее два аналого-цифровых пре образователя, информационные входы которых являются соответственно вхо дами устройства, а выходы соединены соответственно с информационными входами вычислительного блока, вход синхронизирующих импульсов которого соединен с первым входом первого элемента ИЛИ и входом записи блока памяти, выход которого соединен с информационными входами элементов И первой группы, выходы которых соеди нены с входами соответствующих блоков усреднения, выходы которых соед1гнены с информационными входами элементов И второй группы, выходы ко:Торых соединены соответственно с входами второго элемента ИЛИ, выход которого является выходом устройства, управляющие входы аналого-цифровых преобразователей вычислительного блока и вход делителя частоты объединены и соединены с входом первого генератора тактовых импульсов, выход делителя частоты соединен с входами начальной установки вычислительного блока, первого и второго счетчиков и с единичным входом первого триггера, выход которого соединен с информационным входом первого элемента И, управляющий вход которого соединен с выходом второго генератора тактовых импульсов, а выход соединен с вторым входом первого элемента ИЛИ, выход последнего соединен с информационным входом первого счетчика, выход старшего разряда которого соединен с информационным входом второго счетчика, выход старшего разряда которого соединен с информационным входом третьего счетчика и нулевым входом первого триггера, выхода разрядов первого и второго счетчиков соединены с соответствующими группами адресных входов блока постоянной памяти и дешифратора, а выходы разрядов третьего счетчика - с соответствующей группой адресных входов блока постоянной памяти, выходы дешифратора соединены с управляющими входами соответствующих эл,ментов И первой и второй групп, а выходы блока постоянной памяти - соответственно с адресными входами блока памяти, введены два элемента задержки, второй элемент И, компаратор, два формирователя импульсов, второй триггер, причем вход первого элемента задержки объединен с первым входом компаратора и соединен с информационным выходом вычислительного блока, а выход соединен с информационным входом второго элемента И, выход которого соединен с информационным входом блока памяти, второй вход компаратора соединен с источником порогового уровня, а выход - с входами формирователей импульсов, выходы первого из которых непосредственно, а второго через второй элемент задержки соединены соответственно с единичным и нулевым входами второго триггера, выход которого соединен с управляющим входом второго элемента И. На фиг. 1 пр:иведена функциональная схема устро;йства; на фиг. 2 функциональная Схема вычислительного блока; на фиг. 3 - временная диаграмма процесса обработки одной члстной коррелограммы, полученной ,

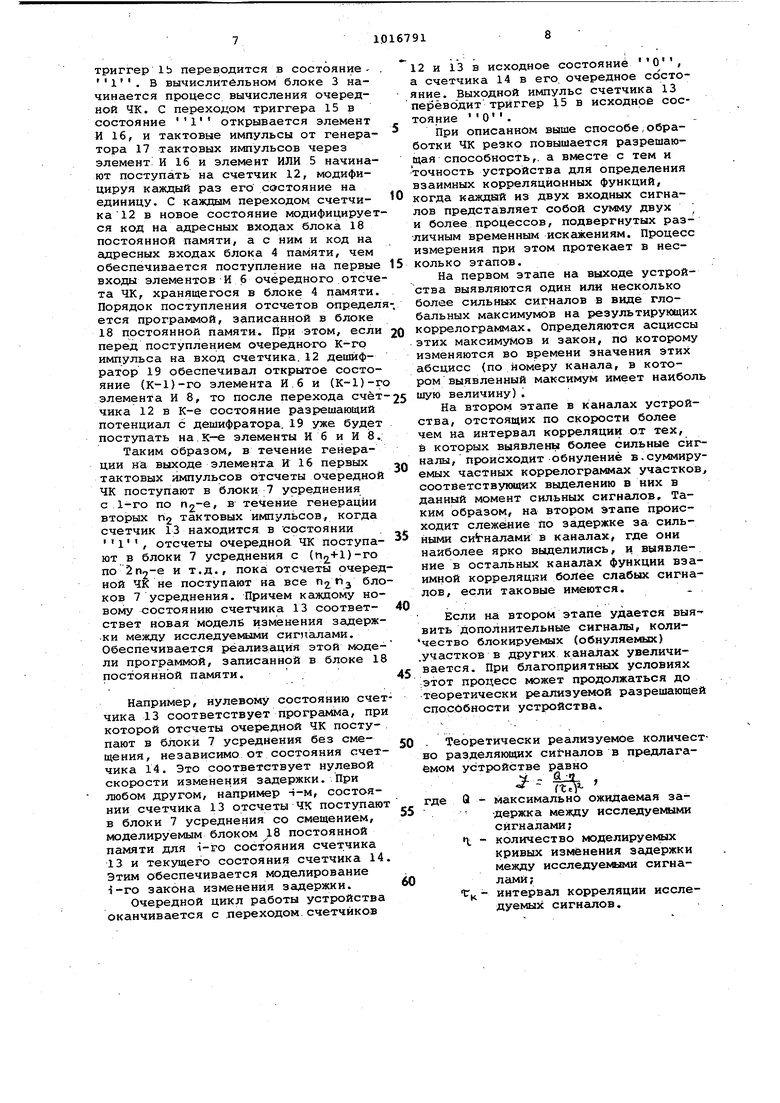

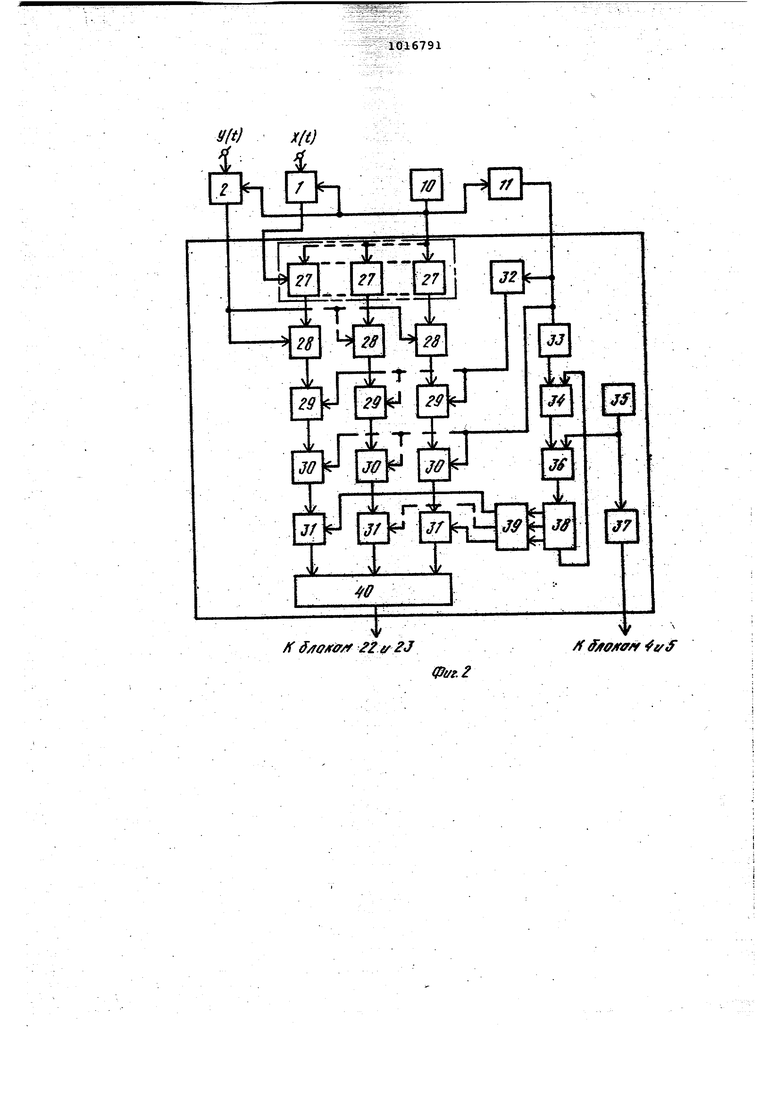

в результате корреляционного анализа двух сигналов X(-t) и У (t) , каждый из которых представлен суммой двух независимых случайных процессов (t) и ц (t) } на фиг, 4 - временная диаграмма процесса получения результирующей коррелограммы для канала, в котором выделяется взаимная корреляционная функция (ВКФ.) - R (Г) между сигналами (-t) и g (-t+t) .

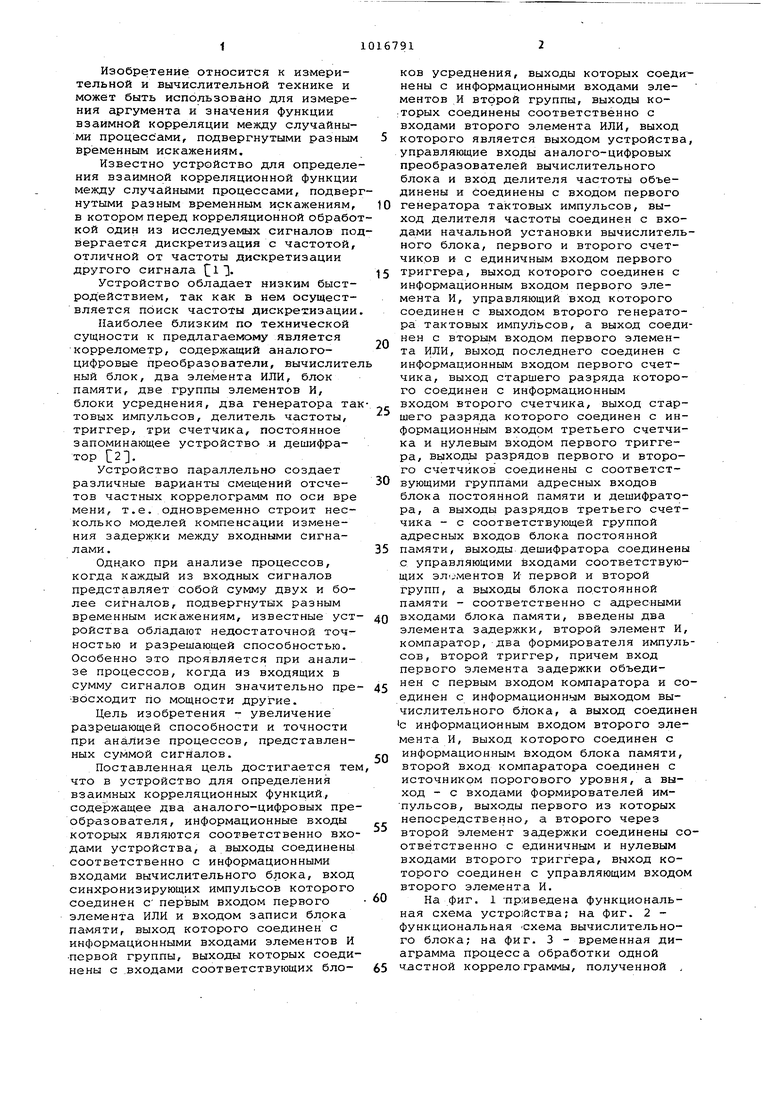

Устройство (фиг. I) содержит аналого-цифровые преобразователи 1 и 2, вычислительный блок 3, блок 4 памяти ; первый элемент ИЛИ 5, первую груп пу элементов И б, блоки 7 усреднения вторую группу элементов И 8, второй элемент ИЛИ 9, первый генератор 10 тактовых импульсов, делитель И частоты, первый счетчик 12, второй счетчик 13, третий счетчик 14, первый триггер 15, первый элемент И 16,. второй генератор 17 тактовых импульсов, блок 18 постоянной памяти, дешифратор 19, второй элемент И 20, второй триггер 21, элемент 22 задержки, компаратор 23, формирователи 24 и 25 импульсов, элемент 26 задержки.

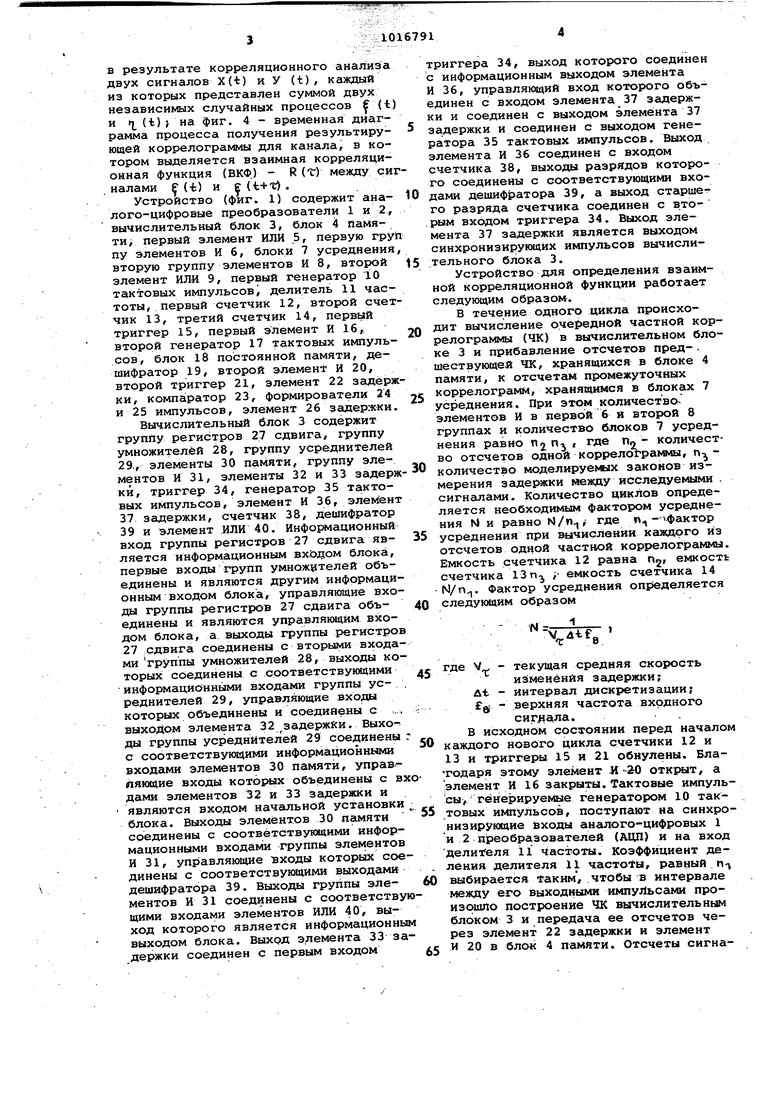

Вычислительный блок 3 содержит группу регистров 27 сдвига, группу умножителей 28, группу усреднителей 29., элементы 30 памяти, группу элементов И 31, элементы 32 и 33 задержкй, триггер 34, генератор 35 тактовых импульсов, элемент И 36, элемент 37 задержки, счетчик 38, дешифратор 39 и элемент ИЛИ 40. Информационный вход группы регистров 27 сдвига является информационным вхЗДом блока, первые входы групп умножителей объединены и являются другим информационным входом блока, управляющие входы группы регистров 27 сдвига объединены и являются управляющим входом блока, а выходы группы регистров 27 сдвига соединены с вторыми входами группы умножителей 28, выходы которых соединены с соотйетствующими информационными входами группы ус- . реднителей 29, управляющие входы которых объединены и соединены с .. выходом элемента 32 задержки. Выходы группы усреднителей 29 соединены г с соответствующими информационны входами элементов 30 памяти, управ-ляющие входы которых объединены с вхдами элементов 32 и 33 задержки и являются входом начальной установки блока. Выходы элементов 30 памяти соединены с соответствующими информационными входами группы элементов И 31, управляющие входы которых соединены с соответствукадими выходами дешифратора 39. Выходы группы элементов И 31 соединены с соответствующими входами элементов ИЛИ 40, выход которого является информационным выходом блока. Выход элемента 33 задержки соединен с первым входом

триггера 34, выход которого соединен с информационным выходом элемента И 36, управляющий вход которого объединен с входом элемента 37 задержки и соединен с выходом элемента 37 задержки и соединен с выходом генератора 35 тактовых импульсов. Выход элемента И 36 соединен с входом счетчика 38, выходе разрядов которого соединены с соответствующими входами дешифратора 39, а выход старшего разряда счетчика соединен с вторым входом триггера 34. Выход элемента 37 задержки является выходом синхронизирующих импульсов вычисли;тельного блока 3.

Устройство для определения взаимной корреляционной функции работает следующим образом.

В течение одного цикла происходит вычисление очередной частной коррелограммы (ЧК) в вычислительном блоке 3 и прибавление отсчетов пред- . шествующей} ЧК, хранящихся в блоке 4 памяти, к отсчетам промежуточных коррелограмм, хранящимся в блоках 7 усреднения. При этом количество элементов И в первой 6 я второй 8 группах и количество блоков 7 усреднения равно 2 п , где Пп - количество отсчетов одной коррелсйграгФШ, количество моделируемых законов измерения задержки между исследуемыми сигналами. Количество циклов определяется необходимым фактором усреднения N и равно где й --фактор усреднения при вычислении каждого из отсчетов одной частной коррелограммы Емкость счетчика 12 равна Oj, емкост счетчика 13 n-j ; емкость счетчика 14 N/n. Фактор усреднения определяется следующим образом

- (

где V - текущая средняя скорость изменения защержки;

д-t - Интервал дискретизации;

g - верхняя частота входного

.

В исходном состоянии перед начало каждого нового цикла счетчики 12 и 13 и триггеры 15 и 21 обнулены. Блатодар я этому элемент И -20 , а элемент И 16 закрыты. Тактовые импульсы, гёнерируеьше генератором 10 тактовых импульсов, поступают на синхро низирующие Ьходы анёшого-цифровых 1 и 2 преобразователей (АЦП) и на вход делигеля 11 частоты. Коэффициент деления делителя 11 частоты, рав1)ый nвыбирается «Таким, чтобы в интервале между его выходными импуЛьсами произошло построение ЧК вычислительным блоком 3 и передача ее отсчетов через элемент 22 задержки и элемент и 20 в блок 4 памяти. Отсчеты сигналов X (-t) и У (t) с выходов АЦП 1 и 2 поступают в вычислительный блок 3, в котором происходит вычисление отсчетов ЧК. Вычислительный блок 3 (фиг. 2) работает следующим образом. Сигнал X (t) поступает на вход аналого-цифрового преобразователя 1 и в момент поступления импульсов генератора 10 преобразуется в соответствующий m-разрядный двоичный код Этот код поступает на входы группы регистров 27 сдвига, выполняющих функцию цифровой линии задержки. Длина каждого из регистров 27 сдвиг определяется требуемой задержкой и количеством частных оценок: . гдet c,,. - требуемое время задержки 2 - количество частных оценок С появлением каждого нового сдвигающего импульса на выходе генерато ра 10 тактовых импульсов коды-отсче ты входного сигнала продвигаются вправо по группе регистров 27 сдвиг И:«тпульсы, представляюидие отсчет в двоичном коде, с выхода одноименных триггеров, например К, регистров 27 сдвига проходят на входы умножителей 28 того же номера К. На тот же умножитель 28 подаются отсчеты входного сигнала У (t) от аналого-цифрового преобразователя 2. На выходе К-того умножителя формируется код, равный элементарному произведению X (-t-K A-t (i). Код произведения- синхронно с тактовыми импульсами передается на К-й усреднитель 29. Накопление элементарных произведе ний в усреднителях 29 продолжается до возникновения сигнала на выходе делителя 11 частоты. Коэффициент деления делителя 11 частоты равен выбранному для частной оценки фактору усреднения N. Синхронно с выходным сигналом делителя 11 частоты результаты усреднения записываются в элементы 30 памяти, а через интервал времени, определяемый элементом 32 задержки, усреднители 29 обнуля-. ются и начинается новый процесс вычисления очередных частных оценок Через интервал времени t, определяемый элементом 33 задержки, триг гер 34 переходит в состояние I и разрешающий потенциал поступает на один из входов элемента 36 И, на второй вход которого поступают импульсы от генератора 35 тактовых импульсов, С выхода гене)атора 35 тактовые импульсы начинают поступать на вход счетчика 38, модифицируя каж дый раз его состояние на единицу. В соответствии с состояниями счетчика ,38 дешифратор 39 управляет элементами И 31 так, что на вход элемента 22 задержки и компаратора 23 синхронно со каждого состояния счетчика 38 через соответствующий элемент И 31 и элемент ИЛИ 40 поступают по порядку отсчеты ЧК (хранимые в элементах 30 памяти) с аргументами от Одо%- +2С. Лт Отсчеты ЧК через элемент 22 задержки и элемент И 20 поступают на вход блока 4 памяти. Передача каждого отсчета ЧК сопровождается синхронизирующим импульсом, который поступает на вход записи блока 4 памяти и через элемент ИЛИ 5/на вход счетчика 12, модифицируя каждый раз его состояние на единицу. Код состояния счетчика 12 через блок 18 постоянной памяти передается на адресные входы блока 4 памяти, чем обеспечивается запись каждого нового отсчета ЧК по новому адресу. Параллельно с этим отсчеты ЧК поступают на первый вход компаратора 23, к второму входу которого подключен источник Up, порогового уровня. Когда в момент времени -Ьр,(фиг. 3) величина очередного отсчета ЧК превысит пороговый уровень ип(фиг. За) , ;компаратор 23 открывается и генерируЬт импульс(фиг.Зб),который оканчивается в момент времени tj ,когда величина отсчетов ЧК вновь станет меньшей Up.Формирователь 24 импульсов вырабатывает импульс(фиг.Зв),который совпадает во времени с передним фронтом выходного импульса компаратора 23, а импульс на выходе формирователя 2f5 импульсов (фиг. Зг) совпадает с задним фронтом выходного импульса компаратора 23. Выходной импульс формирователя 24 импульсов устанавливает огриггер 21 в состояние i (фиг.Зе) , а йыходной импульс формирователя 25 импульсов задерживается элементом 24 задержки нал-Ь2(фиг. Зд) и устанавливает триггер 21 в исходное нулевое состояние (фиг. Зе). Время задержки выбирается таким, чтобы длительность импульса (фиг. Зе) на выходе триггера 21 была равна интервалу Т, корреляции процесса t Н) На это время элемент И 20 оказывается закрытым, и в блок 4 памяти поступают нулевые отсчеты. Отсчеты ЧК задерживаются элементом 22 задержки на интервал лt(фиг. 4ж), приблизительно равный гем обеспечивается замена нулевыми отсчетами тех участков ЧК (фиг. За), в которых наличие взаимной корреляции процесса t(-t) существенно влияет на выделение корреляционной функции процесса е(t) в i-м канале устройства. Синхронно с возникновением каждого очередного импульса на выходе деителя 11 частоты счетчики 12 и 13 и вычислительный блок 3 обнуляются, а

триггер 1Ь переводится в состояние . В вычислительном блоке 3 начинается процесс вычисления очередной ЧК. С переходом триггера 15 в состояние открывается элемент И 16, и тактовые импульсы от генератора 17 тактовых импульсов через элемент И 16 и элемент ИЛИ 5 начинают поступать на счетчик 12, модифицируя каждый раз его состояние на единицу. С каждым переходом счетчика12 в новое состояние модифицируется код на адресных входах блока 18 постоянной памяти, а с ним и код на адресных входах блока 4 памяти, чем обеспечивается поступление на первые входы элементов И б очередного отсчета ЧК, хранящегося в блоке 4 памяти. Порядок поступления отсч-етов определется программой, записанной в блоке 18 постоянной памяти. При этом, если перед поступлением очередного К-го импульса на вход счетчика.12 дешифратор 19 обеспечивал открытое состояние (K-l)-ro элемента И.б и (K-l)-r элемента И 8, то после перехода счёт чика 12 в К-е состояние разрешающий потенциал с дешифратора. 19 уже будет поступать на.К-е элементы И б и И iB..

Таким образом, в течение генерации на выходе элемента И 16 первых тактовых импульсов отсчеты очередной ЧК поступают в блоки 7 усреднения с 1-го по , в течение генерации вторых П2 тактовых импульсов, когда счетчик 13 находится в состоянии Ч , отсчеты очередной ЧК поступают в блоки 7 усреднения с (П2+1)-го по 2п2-е и т.д., пока отсчеты очередной ЧК не поступают на все . блоков 7 усреднения. Причем каждому новому состоянию счетчика 13 соответствет новая моделк изменения задержки между исследуемыми сигналами. Обеспечивается р ёали-з,ацйя этой модели программой, записанной в блоке 18 постоянной памяти.

Например, нулевому состоянию счетчика 13 соответствует програшла, при которой отсчеты очередной ЧК поступают в блоки 7 усреднения без смещения, независимо от состояния счетчика 14. Это соответствует нулевой скорости изменения задержки. При любом другом, например -i-м, состоянии счетчика 13 отсчеты ЧК поступают в блоки 7 усреднения со смещением, моделируемым блоком 18 постоянной памяти для i-ro состояния счетчика 13 и текущего состояния счетчика 14. Этим обеспечивается моделирование i-ro закона изменения задержки.

Очередной цикл работы устройства оканчивается с переходом счетчиков

12 и 13 в исходное состояние О, а счетчика 14 в его. очередное состояние. Выходной импульс счетчика 13 переводит триггер 15 в исходное состояние О .

При описанном выше способе,обработки ЧК резко повышается разрешающая способность ,, а вместе с тем и точность устройства для определения взаимных корреляционных функций, когда каждый из двух входных сигналов представляет собой сумму двух и более процессов, подвергнутых различным временным искажениям. Процесс измерения при этом протекает в несколько этапов.

На первом этапе на выходе устройства выявляются один или несколько более сильных сигналов в виде глобальных максимумов на результирующих коррелограммах. Определяются асциссы .этих максимумов и закон, по которому изменяются во времени значения этих абсцисс (по номеру канала, в котором выявленный максимум имеет наибол шук1 величину) .

На втором этапе в каналах устройства, отстоящих по скорости более чем на интервал корреляции от тех, в которых выявлены более сильные сигналы, происходит обнуление Б.суммируемых частных коррелограммах участков соответствукндях выделению в них в данный момент сильных сигналов. Таким образом, на втором этапе происходит слеже1ние по задержке за сильными сигналами в каналах, где они наиболее ярко выделились, и выявление в остальных каналах функции взаимной корреляции более слабых сигналов, если таковые имеются.

Если на втором этапе удается выявить дополнительные сигналы, количество блокируемых (обнуляемых) .участков в других каналах увеличивается. При благоприятных условиях этот процесс может продолжаться до теоретически реализуемой разрешающей способности устройства.

Теоретически реализуемое количество разделяющих сигналов в предлагаемом устройстве равно

где S - максимально ожидаемая задержка между исследуекыми сигналами;

t - количество моделируемых кривых изменения задержки между исследуемями сигналами ;

t - интервал корреляции исследуемых сигналов.

y(t)

xft)

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для определения взаимной корреляционной функции | 1989 |

|

SU1689968A1 |

| Устройство для определения взаимной корреляционной функции | 1984 |

|

SU1188752A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1727134A1 |

f( ff/fffjfiof/f 2ff2J

/ff ff/fff/V yS - w -гг tff. J i/я

f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-07—Публикация

1981-09-25—Подача