Изобретение относится к телевизионной технике и может быть использовано в телевизионных следящих системах.

Целью изобретения является сокращение времени стабилизации амплитуды видеосигнала.

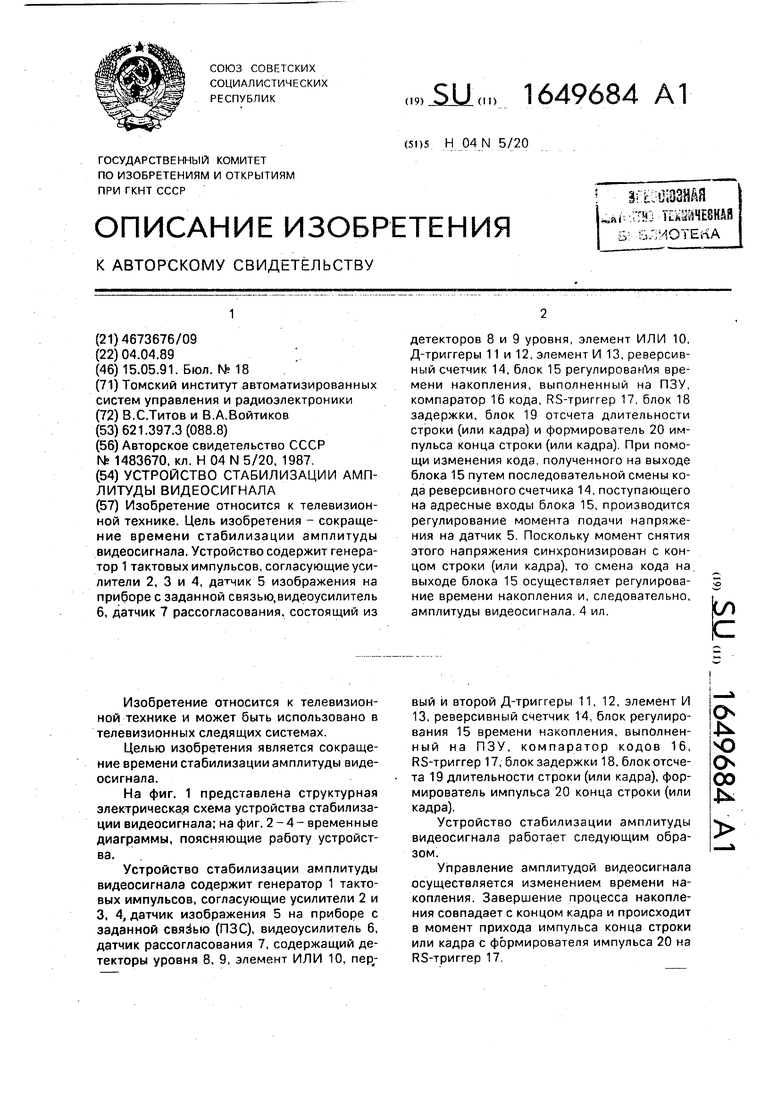

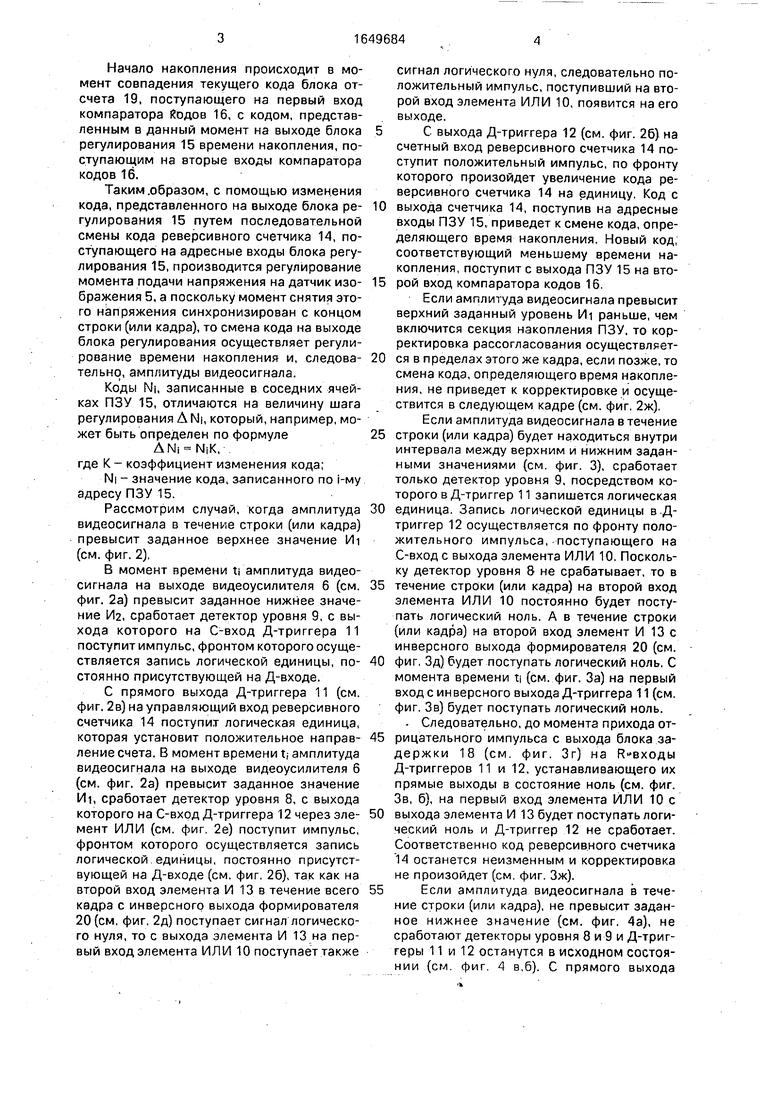

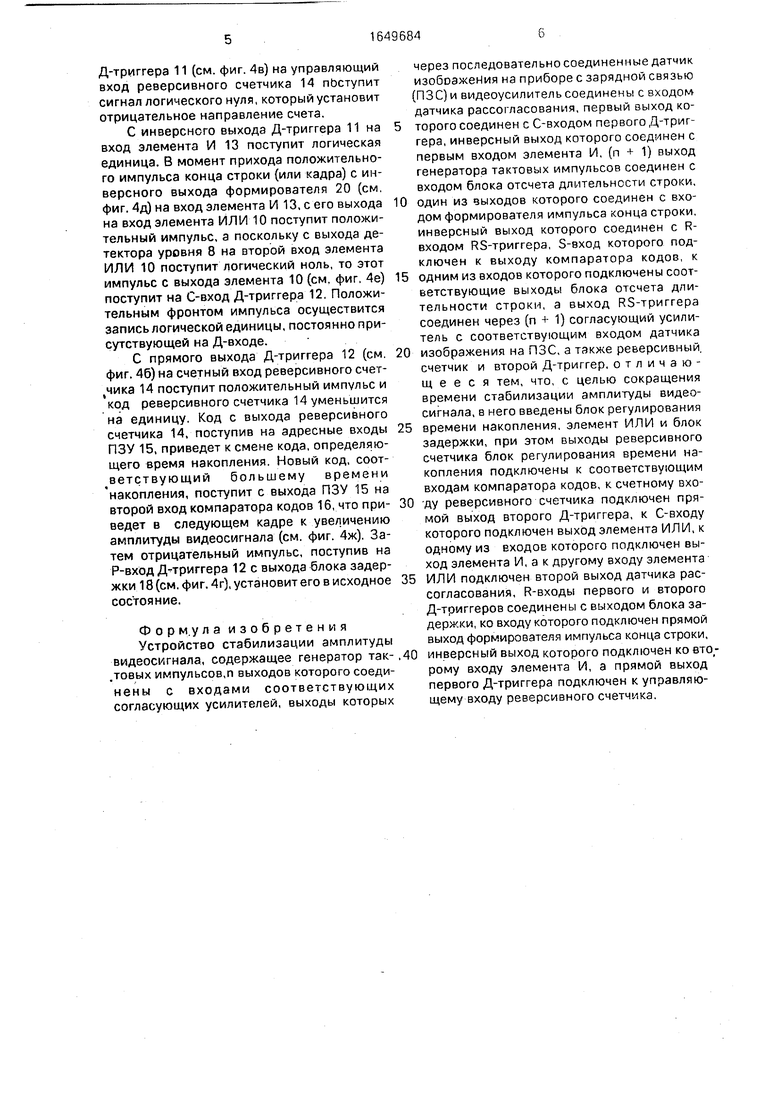

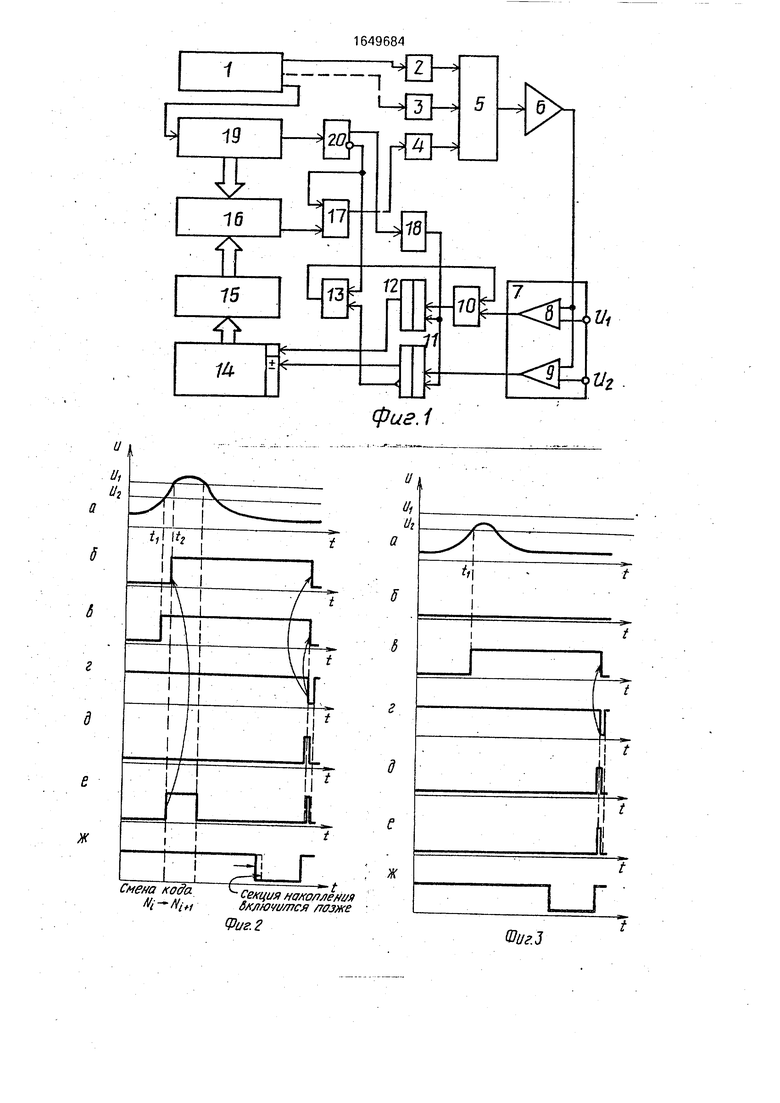

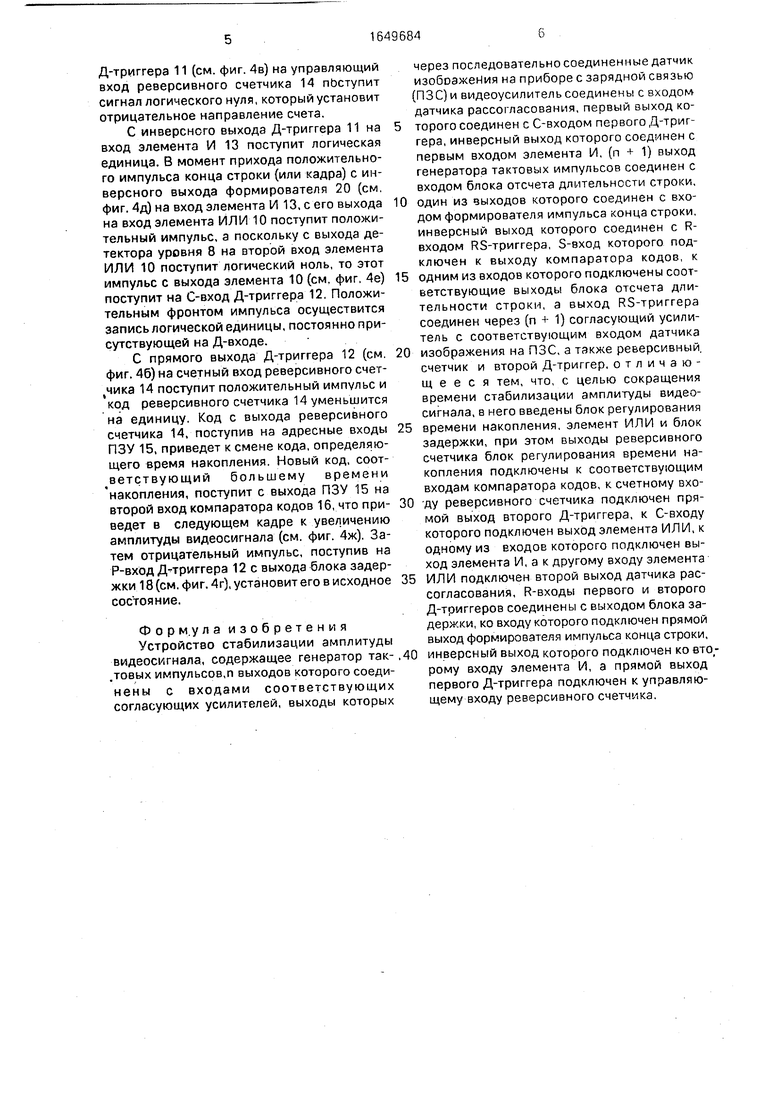

На фиг. 1 представлена структурная электрическая схема устройства стабилизации видеосигнала; на фиг. 2 - 4 - временные диаграммы, поясняющие работу устройства.

Устройство стабилизации амплитуды видеосигнала содержит генератор 1 тактовых импульсов, согласующие усилители 2 и 3, 4, датчик изображения 5 на приборе с заданной связью (ПЗС), видеоусилитель 6, датчик рассогласования 7, содержащий детекторы уровня 8, 9, элемент ИЛИ 10, первый и второй Д-триггеры 11, 12, элемент И 13, реверсивный счетчик 14 блок регулирования 15 времени накопления, выполненный на ПЗУ, компаратор кодов 16, RS-триггер 17, блок задержки 18, блок отсчета 19 длительности строки (или кадра), формирователь импульса 20 конца строки (или кадра).

Устройство стабилизации амплитуды видеосигнала работает следующим образом.

Управление амплитудой видеосигнала осуществляется изменением времени накопления Завершение процесса накопления совпадает с концом кадра и происходит в момент прихода импульса конца строки или кадра с формирователя импульса 20 на RS-триггер 17

О 4 Ю О 00 4

Начало накопления происходит в момент совпадения текущего кода блока отсчета 19, поступающего на первый вход компаратора Йодов 16, с кодом, представленным в данный момент на выходе блока регулирования 15 времени накопления, поступающим на вторые входы компаратора кодов 16.

Таким .образом, с помощью изменения кода, представленного на выходе блока регулирования 15 путем последовательной смены кода реверсивного счетчика 14, поступающего на адресные входы блока регулирования 15, производится регулирование момента подачи напряжения на датчик изображения 5, а поскольку момент снятия этого напряжения синхронизирован с концом строки (или кадра), то смена кода на выходе блока регулирования осуществляет регулирование времени накопления и, следовательно, амплитуды видеосигнала.

Коды NI, записанные в соседних ячейках ПЗУ 15, отличаются на величину шага регулирования Д NI, который, например, может быть определен по формуле

ЛМ| М|К, где К- коэффициент изменения кода;

NI - значение кода, записанного по i-му адресу ПЗУ 15.

Рассмотрим случай, когда амплитуда видеосигнала в течение строки (или кадра) превысит заданное верхнее значение Hi (см. фиг. 2),

В момент времени ti амплитуда видеосигнала на выходе видеоусилителя 6 (см. фиг. 2а) превысит заданное нижнее значение , сработает детектор уровня 9, с выхода которого на С-вход Д-триггера 11 поступит импульс, фронтом которого осуществляется запись логической единицы, постоянно присутствующей на Д-входе.

С прямого выхода Д-триггера 11 (см. фиг. 2в) на управляющий вход реверсивного счетчика 14 поступит логическая единица, которая установит положительное направление счета. В момент времени t,- амплитуда видеосигнала на выходе видеоусилителя 6 (см. фиг. 2а) превысит заданное значение Hi, сработает детектор уровня 8, с выхода которого на С-вход Д-триггера 12 через элемент ИЛИ (см. фиг. 2е) поступит импульс, фронтом которого осуществляется запись логической единицы, постоянно присутствующей на Д-входе (см. фиг, 26), так как на второй вход элемента И 13 в течение всего кадра с инверсного выхода формирователя 20 (см. фиг. 2д) поступает сигнал логического нуля, то с выхода элемента И 13 на первый вход элемента ИЛИ 10 поступает также

сигнал логического нуля, следовательно положительный импульс, поступивший на второй вход элемента ИЛИ 10. появится на его выходе.

С выхода Д-триггера 12 (см. фиг. 26) на

счетный вход реверсивного счетчика 14 поступит положительный импульс, по фронту которого произойдет увеличение кода реверсивного счетчика 14 на единицу. Код с

0 выхода счетчика 14, поступив на адресные входы ПЗУ 15, приведет к смене кода, определяющего время накопления. Новый код, соответствующий меньшему времени накопления, поступит с выхода ПЗУ 15 на вто5 рой вход компаратора кодов 16.

Если амплитуда видеосигнала превысит верхний заданный уровень Ич раньше, чем включится секция накопления ПЗУ, то корректировка рассогласования осуществляет0 ся в пределах этого же кадра, если позже, то смена кода, определяющего время накопления, не приведет к корректировке и осуществится в следующем кадре (см. фиг. 2ж), Если амплитуда видеосигнала в течение

5 строки (или кадра) будет находиться внутри интервала между верхним и нижним заданными значениями (см. фиг. 3), сработает только детектор уровня 9, посредством которого в Д-триггер 11 запишется логическая

0 единица. Запись логической единицы в Д- триггер 12 осуществляется по фронту положительного импульса, поступающего на С-вход с выхода элемента ИЛИ 10. Поскольку детектор уровня 8 не срабатывает, то в

5 течение строки (или кадра) на второй вход элемента ИЛИ 10 постоянно будет поступать логический ноль. А в течение строки (или кадра) на второй вход элемент И 13 с инверсного выхода формирователя 20 (см.

0 фиг, Зд) будет поступать логический ноль. С

момента времени ti (см. фиг. За) на первый

вход с ин версного выхода Д-триггера 11 (см,

фиг. Зв) будет поступать логический ноль.

- Следовательно, до момента прихода от5 рицательного импульса с выхода блока задержки 18 (см. фиг. Зг) на R-входы Д-триггеров 11 и 12, устанавливающего их прямые выходы в состояние ноль (см. фиг. Зв, б), на первый вход элемента ИЛИ 10 с

0 выхода элемента И 13 будет поступать логический ноль и Д-триггер 12 не сработает. Соответственно код реверсивного счетчика 14 останется неизменным и корректировка не произойдет (см. фиг. Зж).

5Если амплитуда видеосигнала в течение строки (или кадра), не превысит заданное нижнее значение (см. фиг. 4а), не сработают детекторы уровня 8 и 9 и Д-триг- геры 11 и 12 останутся в исходном состоянии (см. фиг. 4 в,б). С прямого выхода

Д-триггера 11 (см. фиг. 4в) на управляющий вход реверсивного счетчика 14 пЬступит сигнал логического нуля, который установит отрицательное направление счета.

С инверсного выхода Д-триггера 11 на вход элемента И 13 поступит логическая единица, В момент прихода положительного импульса конца строки (или кадра) с инверсного выхода формирователя 20 (см. фиг. 4д) на вход элемента И 13, с его выхода на вход элемента ИЛИ 10 поступит положительный импульс, а поскольку с выхода детектора уровня 8 на второй вход элемента ИЛИ 10 поступит логический ноль, то этот импульс с выхода элемента 10 (см. фиг. 4е) поступит на С-вход Д-триггера 12. Положительным фронтом импульса осуществится запись логической единицы, постоянно присутствующей на Д-входе.

С прямого выхода Д-триггера 12 (см. фиг. 46) на счетный вход реверсивного счет- 4чика 14 поступит положительный импульс и код реверсивного счетчика 14 уменьшится на единицу. Код с выхода реверсивного счетчика 14, поступив на адресные входы ПЗУ 15, приведет к смене кода, определяющего время накопления. Новый код, соответствующий большему времени накопления, поступит с выхода ПЗУ 15 на второй вход компаратора кодов 16, что приведет в следующем кадре к увеличению амплитуды видеосигнала (см. фиг. 4ж). Затем отрицательный импульс, поступив на Р-вход Д-триггера 12 с выхода блока задержки 18 (см. фиг. 4г), установит его в исходное состояние.

Формула изобретения Устройство стабилизации амплитуды видеосигнала, содержащее генератор так- .товых импульсов,п выходов которого соединены с входами соответствующих согласующих усилителей, выходы которых

через последовательно соединенные датчик изобоэжейия на приборе с зарядной связью (ПЗС) и видеоусилитель соединены с входом датчика рассогласования, первый выход ко5 торого соединен с С-входом первого Д-триггера, инверсный выход которого соединен с первым входом элемента И, (п + 1) выход генератора тактовых импульсов соединен с входом блока отсчета длительности строки,

0 один из выходов которого соединен с входом формирователя импульса конца строки, инверсный выход которого соединен с R- входом RS-триггера, S-вход которого подключен к выходу компаратора кодов, к

5 одним из входов которого подключены соответствующие выходы блока отсчета длительности строки, а выход RS-триггера соединен через (п + 1) согласующий усилитель с соответствующим входом датчика

0 изображения на ПЗС, а также реверсивный, счетчик и второй Д-триггер, отличающееся тем, что, с целью сокращения времени стабилизации амплитуды видеосигнала, в него введены блок регулирования

5 времени накопления, элемент ИЛИ и блок задержки, при этом выходы реверсивного счетчика блок регулирования времени накопления подключены к соответствующим входам компаратора кодов, к счетному вхо0 ду реверсивного счетчика подключен прямой выход второго Д-триггера, к С-входу которого подключен выход элемента ИЛИ, к одному из входов которого подключен выход элемента И, а к другому входу элемента

5 ИЛИ подключен второй выход датчика рассогласования, R-входы первого и второго Д-триггеров соединены с выходом блока задержки, ко входу которого подключен прямой выход формирователя импульса конца строки, 0 инверсный выход которого подключен ко рому входу элемента И, а прямой выход первого Д-триггера подключен к управляющему входу реверсивного счетчика.

1 гпф

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1996 |

|

RU2119725C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1998 |

|

RU2137318C1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1990 |

|

SU1757124A1 |

| Устройство автоматической регулировки амплитуды видеосигнала | 1987 |

|

SU1533014A1 |

| Устройство стабилизации амплитуды видеосигнала | 1985 |

|

SU1252973A2 |

| Устройство стабилизации амплитуды видеосигнала | 1984 |

|

SU1277426A1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1999 |

|

RU2150179C1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1985 |

|

SU1275788A1 |

| Устройство стабилизации амплитуды видеосигнала | 1985 |

|

SU1338112A1 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

Изобретение относится к телевизионной технике. Цель изобретения - сокращение времени стабилизации амплитуды видеосигнала. Устройство содержит генератор 1 тактовых импульсов, согласующие усилители 2, 3 и 4, датчик 5 изображения на приборе с заданной связью,видеоусилитель 6, датчик 7 рассогласования, состоящий из детекторов 8 и 9 уровня, элемент ИЛИ 10, Д-триггеры 11 и 12, элемент И 13, реверсивный счетчик 14, блок 15 регулирования времени накопления, выполненный на ПЗУ компаратор 16 кода, RS-триггер 17 блок 18 задержки, блок 19 отсчета длительности строки (или кадра) и формирователь 20 импульса конца строки (или кадра) При помощи изменения кода полученного на выходе блока 15 путем последовательной смены кода реверсивного счетчика 14, поступающего на адресные входы блока 15, производится регулирование момента подачи напряжения на датчик 5 Поскольку момент снятия этого напряжения синхронизирован с концом строки (или кадра), то смена кода на выходе блока 15 осуществляет регулирование времени накопления и, следовательно, амплитуды видеосигнала 4 ил сл

fr896Wl

и

ffl

Uz

и

А

i f

Смена кода t Ni .f

фиг. 4

| Устройство стабилизации амплитуды видеосигнала | 1987 |

|

SU1483670A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-15—Публикация

1989-04-04—Подача