I

(21)4489654/21

(22)05.10.88

(46) 30.05.91. Бкш. № 20 (72) В.Е.Тетерятников

(53)621.374 (088.8)

(56)Авторское свидетельство СССР 1206954 кл. Н 03 К 23/66, 04,07.84.

Авторское свидетельство СССР У 1298899, кн. . Н 03 К 23/00, Н 03 К 23/40, 08.10.85.

(54)ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

(57)Изобретение относится к импульсной технике и может использоваться в устройствах автоматики и вычислительной техники, в хронизаторах и цифровых синтезаторах частот. Цель изобретения - расширение функциональных возможностей путем обеспечения возможности регулирования длительности выходных импульсов при сохранении его начальной фазы. Это достигается введением инвертора 7, элементов И4, 5, 8 и 9, одновибра- торов 10 и 12, блока 14 сравнения и шины 16 опорного сигнала. Устройство также содержит счетчики 1 и 2 импульсов, триггер 11, дешифраторы 13 и 17, входную 6 кода коэффициента деления 3 и выходную 15 шины. Приведено выполнение блока 14 сравнения. 1 з.п. ф-лы, 2 ил.

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| Вычислительное устройство | 1981 |

|

SU985795A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 1987 |

|

SU1438439A1 |

| Устройство для измерения индикатрис рассеяния света | 1990 |

|

SU1723456A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, в хронизаторах и в цифровых синтезаторах частот.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности регулирования длительности выходного импульса при сохранении его начальной фазы.

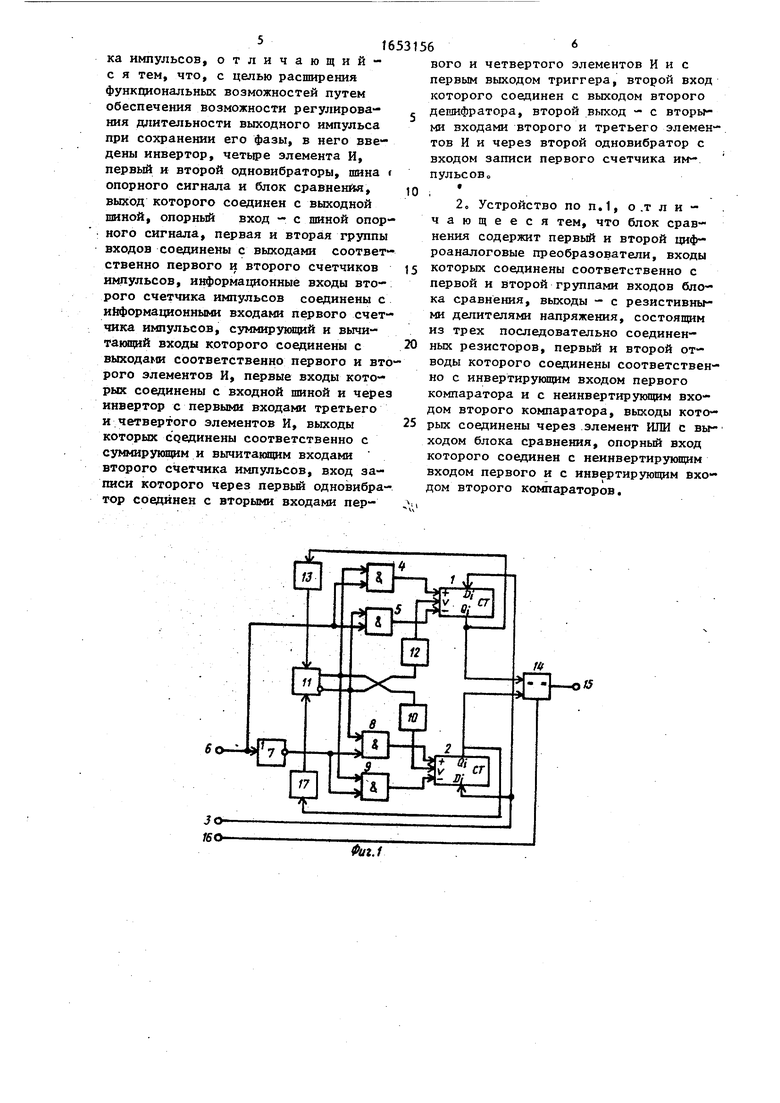

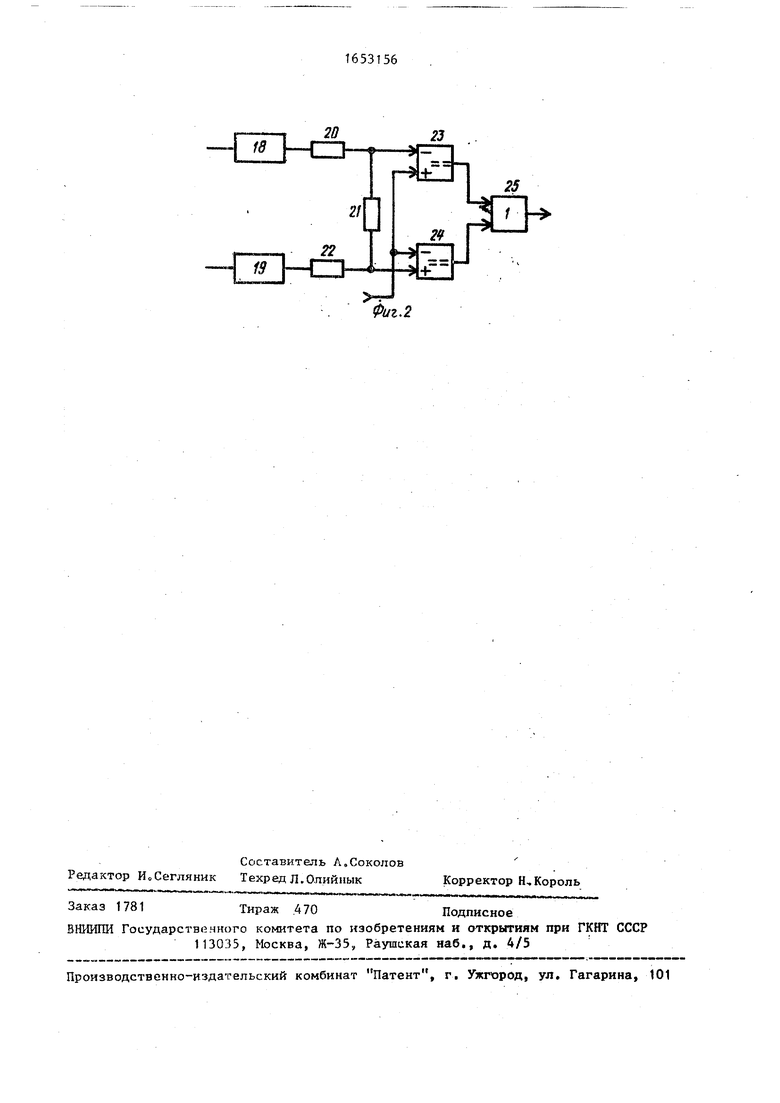

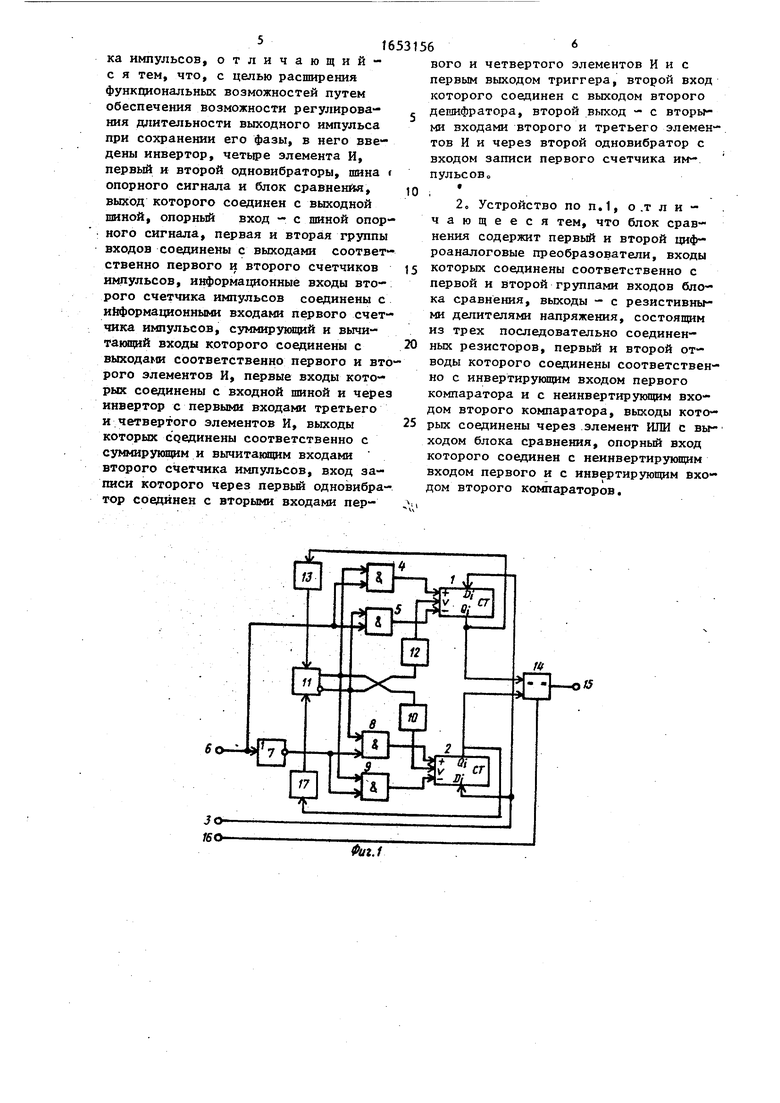

На фиг01 приведена электрическая структурная схема делителя частоты следования импульсов; на фиг.2 - электрическая структурная схема блока сравнения.

Делитель частоты следования импульсов содержит первый и второй счетчики 1 и 2 импульсов, информационные входы которых соединены с

шиной 3 кода коэффициента деления, суммирующий и вычитающий входы первого счетчика 1 импульсов соединены с выходами соответственно первого и второго элементов И 4 и 5, первые входы которых соединены с входной шиной 6 и через инвертор 7 и первыми входами третьего и четвертого элементов И 8 и 9, выходы которых соединены соответственно с суммирующим и даычмтающим входами второго счетчика 2 импульсов, вход записи которого через первый одновибратор 10 соединен со вторыми входами первого и четвертого элементов И 4 и 9 и с первым выходом триггера 11, второй вывод которого соединен со вторыми входами второго и третьего элементов И 5 и 8 и через второй одновибратор

&

СП

со

л

а

12 со входом записи первого счетчика

Iимпульсов, выходы которого через .первый дешифратор 13 соединены с первым входом триггера 11 и непосред- ственно с первой группой входов

блока 14 сравнения, выход которого соединен с выходной шиной 15, опорный вход - с шиной 16 опорного сигнала, вторая группа входов - с выхо- дами второго счетчика 2 импульсов и через второй дешифратор 17 со вто- рым входом триггера 11.

Блох 14 сравнения содержит первый и второй цифроаналоговые преобраэо- ват.ели 18 и 19, входы которых соединены соответственно с первой и со второй группами входов блока 14 сравнения, выходы - с резестивным делителем напряжения, состоящим из трех последовательно соединенных резисторов 20, 21 и 22, первый и второй отводы которого соединены соответственно с инвертирующим входом первого компаратора 23 и с неинвертнрующим входом второго компаратора 24, выходы которых через элемент ИЛИ 25 соединены с выходом блока 14 сравнения, опорный вход которого соединен с не- инвертирующих входом первого и с ин- вертирующим входом второго компараторов 23 и 24ь

Устройство работает следующим образом.

После включения устройства триггер

IIможет находиться в одном из двух состояний. При единичном состоянии триггера 7 счетчик 1 в режиме суммирования, а счетчик 2 - в режиме вычитания. При нулевом состоянии тригге- ра 11 режимы работы этих счетчиков противоположныо

При поступлении входного сигнала на шину 6 через открытые элементы 4,9 и 5,8 проходят импульсы, которые в одном счетчике суммируются в произвольным D нем числом, а в другом - вычитаются„ При установлении в процессе счета одного из счетчиков в нулевое состояние на выходе соответ- ствукяцего дешифратора 13, 17 сформируется импульс, который воздействует на триггер 11 и либо подтвердит прежнее его состояние, либо переключит его з противоположное состояние. При переключении триггера 11 на одном из его выходов сформируется фронт пере- пада напряжений, который запустит соответствующий одновибратор 10 или

,

5 0 5 о

5

д

з „

5

12, выходной импульс которого запишет в другой счетчик двоичное число, поступающее по шине 3.

Таким образом автоматически установится исходное состояние устройства, при котором в одном счетчике установится режим суммирования и нулевое состояние всех его разрядов,а в другом - режим вычитания и число, равное заданному с шины 3.

После этого начинается циклический процесс деления частоты, при котором в одном счетчике в режиме суммирования число монотонно увеличивается от нуля до значения кода на шине 3, а в другом счетчике в режиме вычитания число монотонно уменьшается от значения кода на шине 3 до нуля, и при переключении триггера 11 в противоположное состояние, режимы работы счетчиков меняются и процесс деления частоты возобновляется.

Параллельные двоичные коды с выходов разрядов счетчиков 1 и 2 поступают в блок 14, где преобразователями 18 и 19 преобразуются в напряжения. Эти напряжения через резистив- ный делитель, выполненный на резисто- pax 20, 21 и 22, поступают на входы компараторов 23 и 24, где сравниваются с напряжением, поступающим с шины 16. На выходе элемента 25 и на шине 15 формируется уровень логической единицы всякий раз, когда разность напряжений на первом и втором отводах резистивного делителя напряжения превышает значения напряжения, поступающего с шины 16.

Для необходимости организации серии вложенных друг в друга выходных импульсов в блок 14 сравнения необходимо ввести дополнительные компараторы и элемента ИЛИ, подключив их аналогично имеющимся, но со своими пинами опорных сигналов.

Формула изобретения1

ка импульсов, отличающий- с я тем, что, с целью расширения функциональных возможностей путем обеспечения возможности регулирования длительности выходного импульса при сохранении его фазы, в него введены инвертор, четыре элемента И, первый и второй одновибраторы, шина ( опорного сигнала и блок сравнения, выход которого соединен с выходной шиной, опорный вход - с шиной опорного сигнала, первая и вторая группы входов соединены с выходами соответственно первого и второго счетчиков импульсов, информационные входы второго счетчика импульсов соединены с информационными входами первого счетчика импульсов, суммирующий и вычитающий входы которого соединены с выходами соответственно первого и второго элементов И, первые входы которых соединены с входной шиной и через инвертор с первыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами второго счетчика импульсов, вход записи которого через первый одновибра- тор соединен с вторыми входами пер«О

вого и четвертого элементов И и с первым выходом триггера, второй вход которого соединен с выходом второго дешифратора, второй выход - с вторыми входами второго и третьего элементов И и через второй одновибратор с входом записи первого счетчика импульсов о

2, Устройство по п.1, о .т л и - чающееся тем, что блок сравнения содержит первый и второй циф- роаналоговые преобразователи, входы

которых соединены соответственно с первой и второй группами входов блока сравнения, выходы - с реэистивны- ми делителями напряжения, состоящим из трех последовательно соединенных резисторов, первый и второй отводы которого соединены соответственно с инвертирующим входом первого компаратора и с неинвертирующим входом второго компаратора, выходы которых соединены через элемент ИЛИ с выходом блока сравнения, опорный вход которого соединен с неинвертирующим входом первого и с инвертирующим входом второго компараторов.

Фиг.1

Авторы

Даты

1991-05-30—Публикация

1988-10-05—Подача