4

4 4

s|

со

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием в частоту импульсов.

Цель изобретения - повыгаение точности.

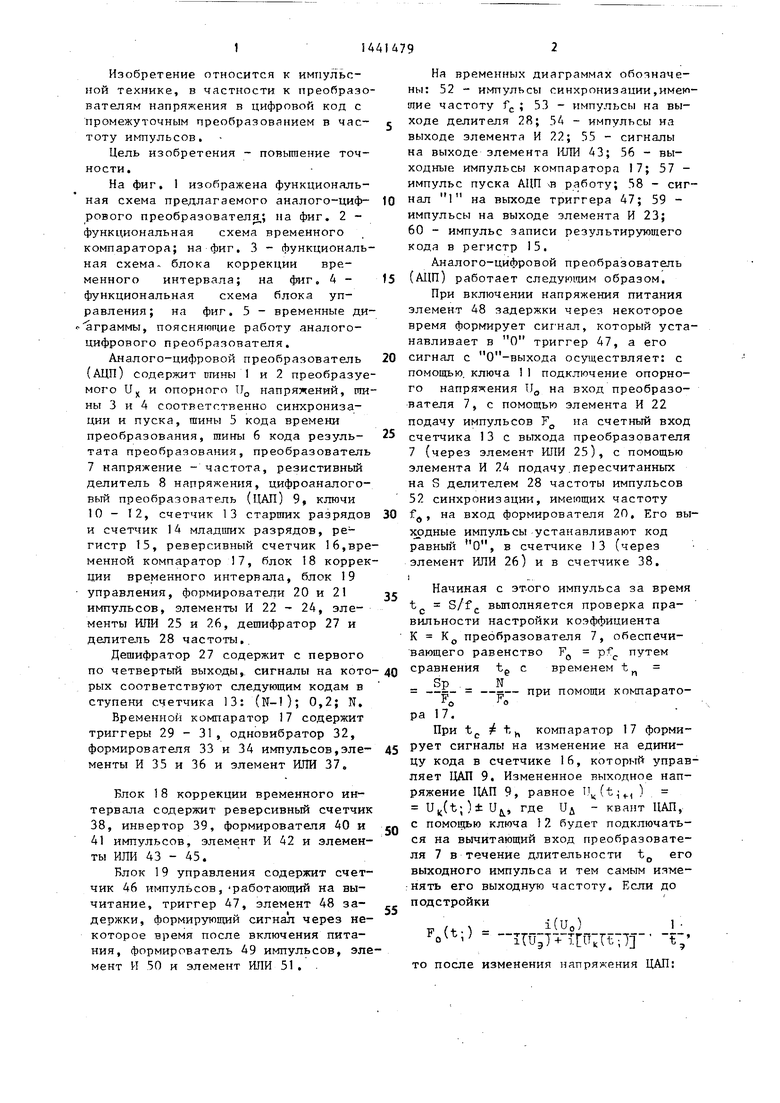

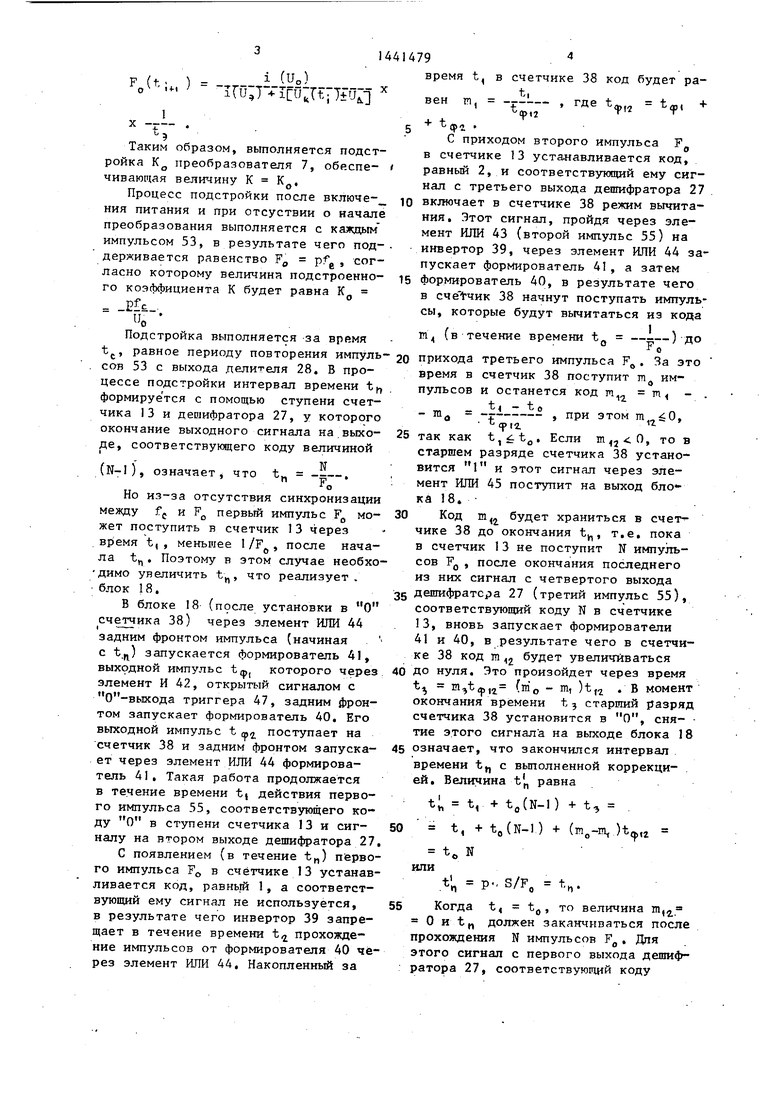

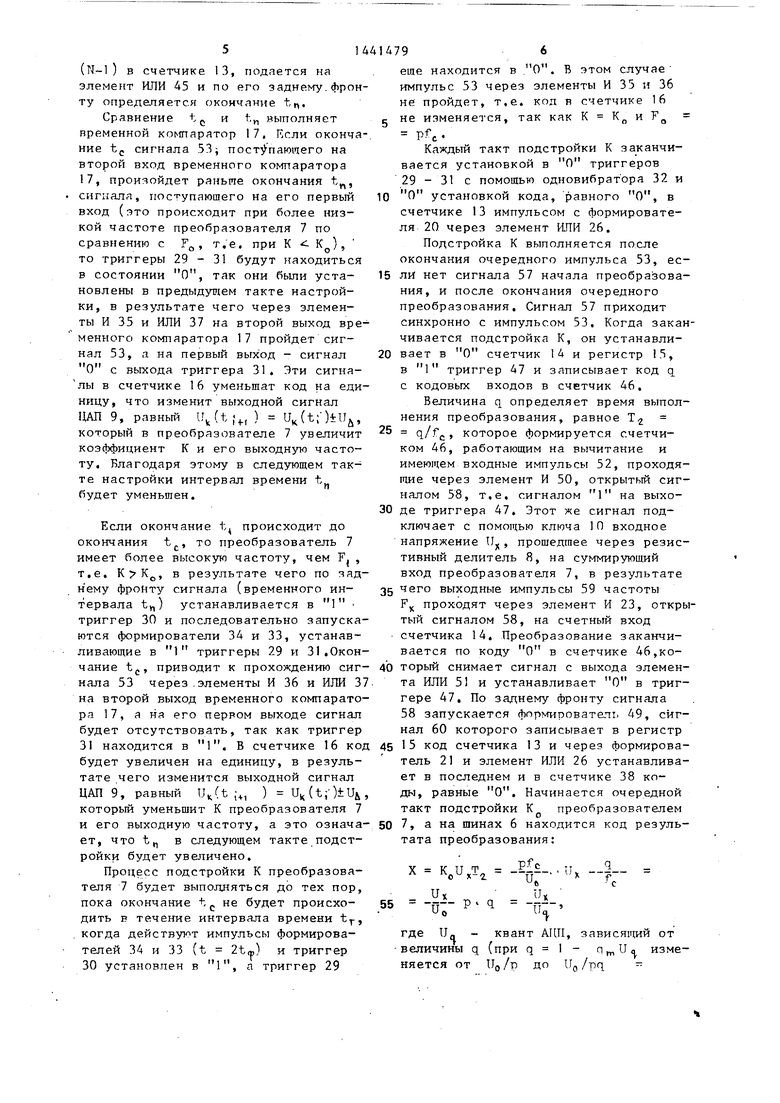

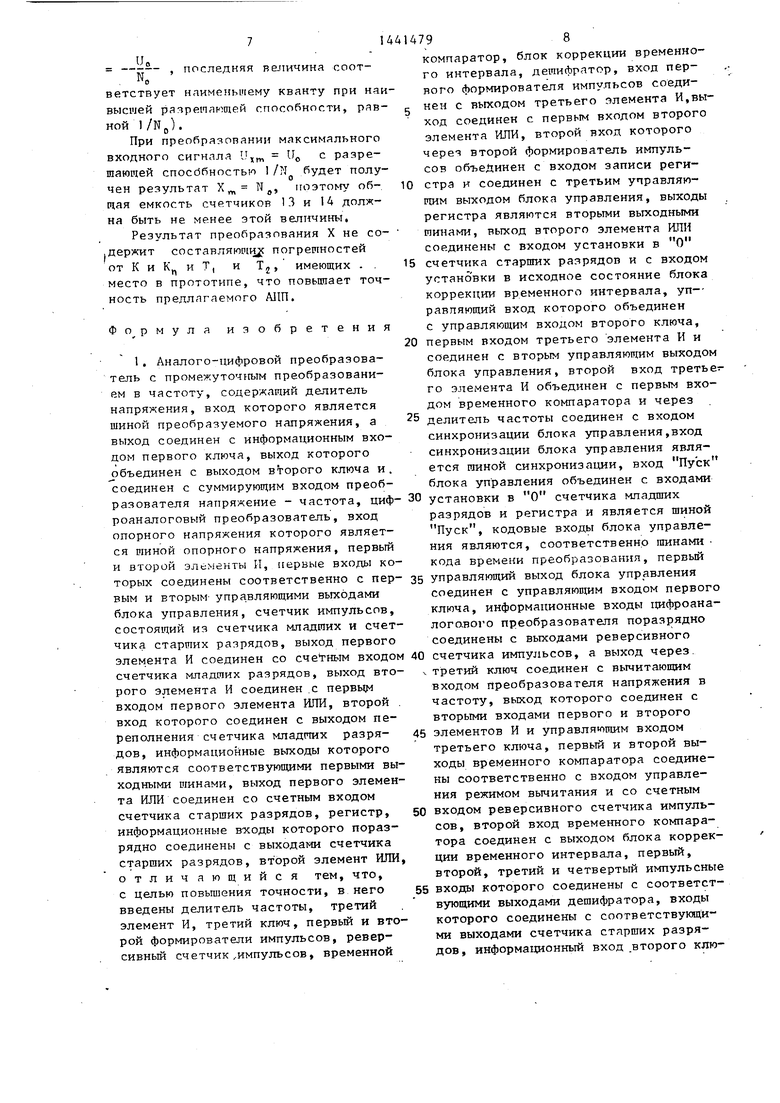

На фиг. 1 изображена функциональная схема предлагаемого аналого-цифрового преобразователя,; на фиг. 2 - функциональная схема временного компаратора; на фиг. 3 - функциональная схема- блока коррекции временного интервала; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - временные ди граммы, поясняющие работу аналого- цифрового преобразователя.

Аналого-цифровой преобразователь (АЦП) содержит пгины 1 и 2 преобразуемого и и опорного UQ напряжений, шины 3 и 4 соответственно синхронизации и пуска, шины 5 кода времени преобразования, шины 6 кода результата преобразования, преобразователь 7 напряжение - частота, резистивный делитель 8 напряжения, цифроаналого- вый преобразователь (ЦАП) 9, ключи 10 - 12, счетчик 13 старших разрядов и счетчик 14 младших разрядов, регистр 15, реверсивный счетчик 16,временной компаратор 17, блок 18 коррекции временного интервала, блок 19 управления, формирователи 20 и 21 импульсов, элементы И 22 - 24, элементы ИЛИ 25 и 26, дешифратор 27 и делитель 28 частоты.

Дешифратор 27 содержит с первого по четвертый выходы, сигналы на кото рык соответствуют следующим кодам в ступени счетчика 13: (N-l); 0,2; N,

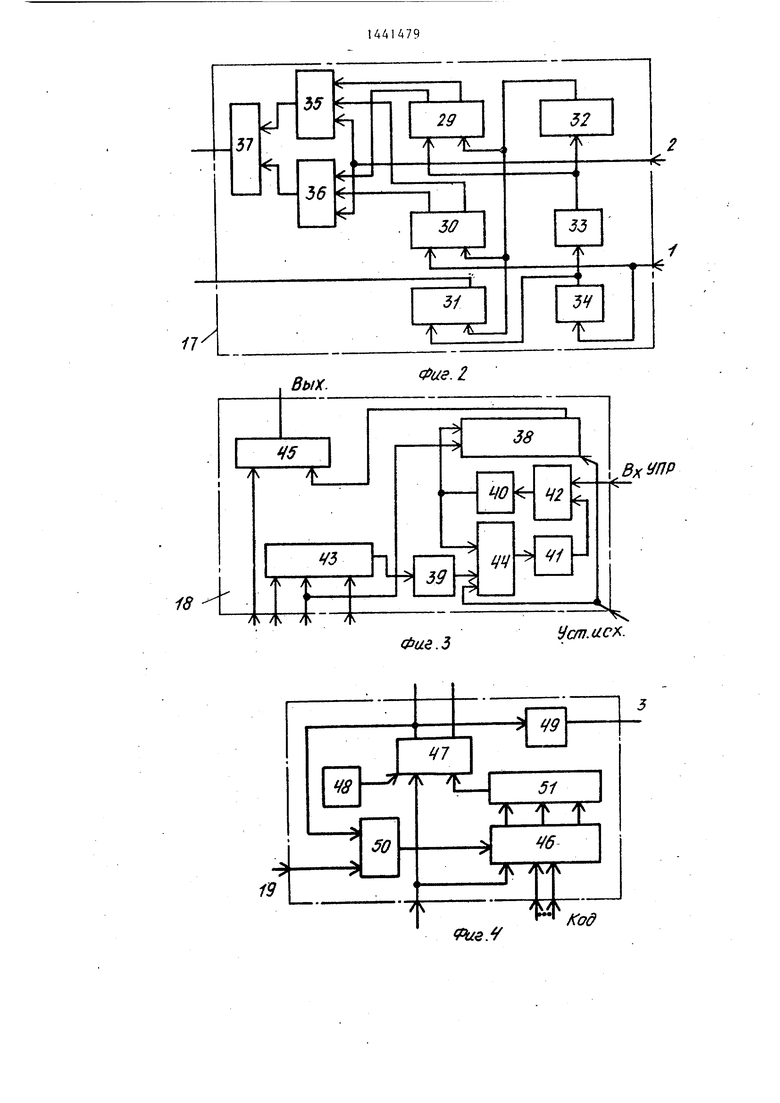

Временной компаратор 17 содержит триггеры 29-31, одновибратор 32, формирователя 33 и 34 импульсов,элементы И 35 и 36 и элемент ИЛИ 37,

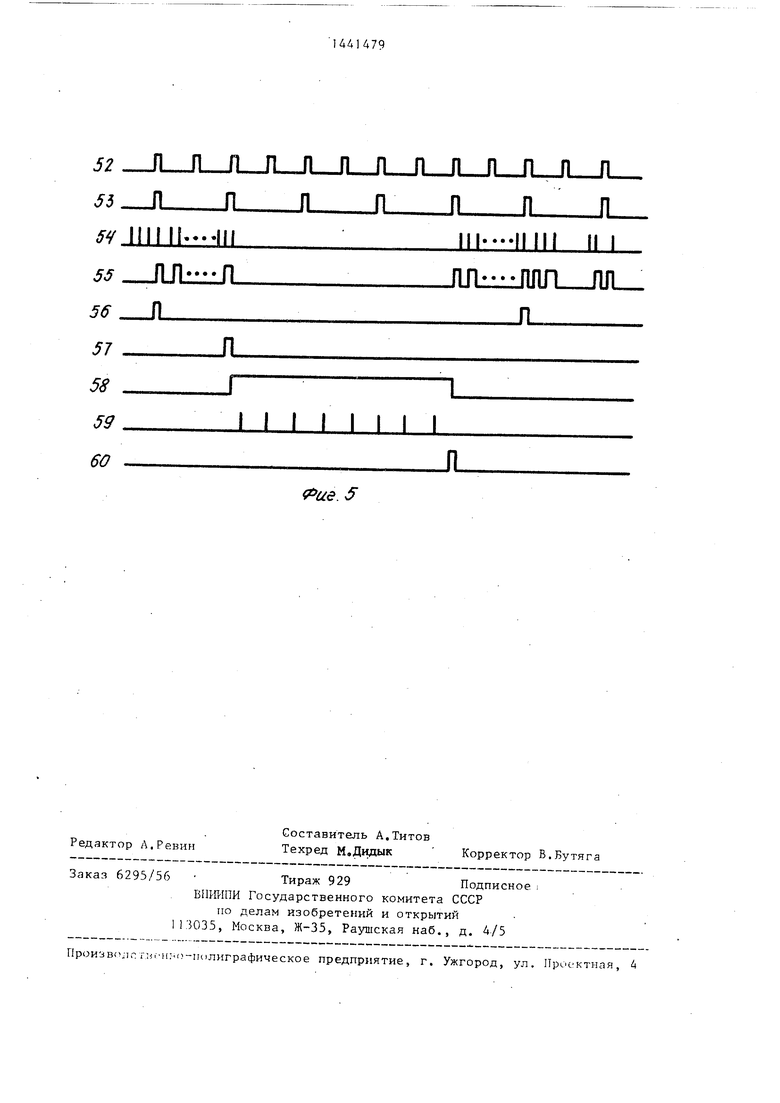

Блок 18 коррекции временного интервала содержит реверсивный счетчик 38, инвертор 39, формирователя 40 и 41 импульсов, элемент И 42 и элементы ИЛИ 43 - 45.

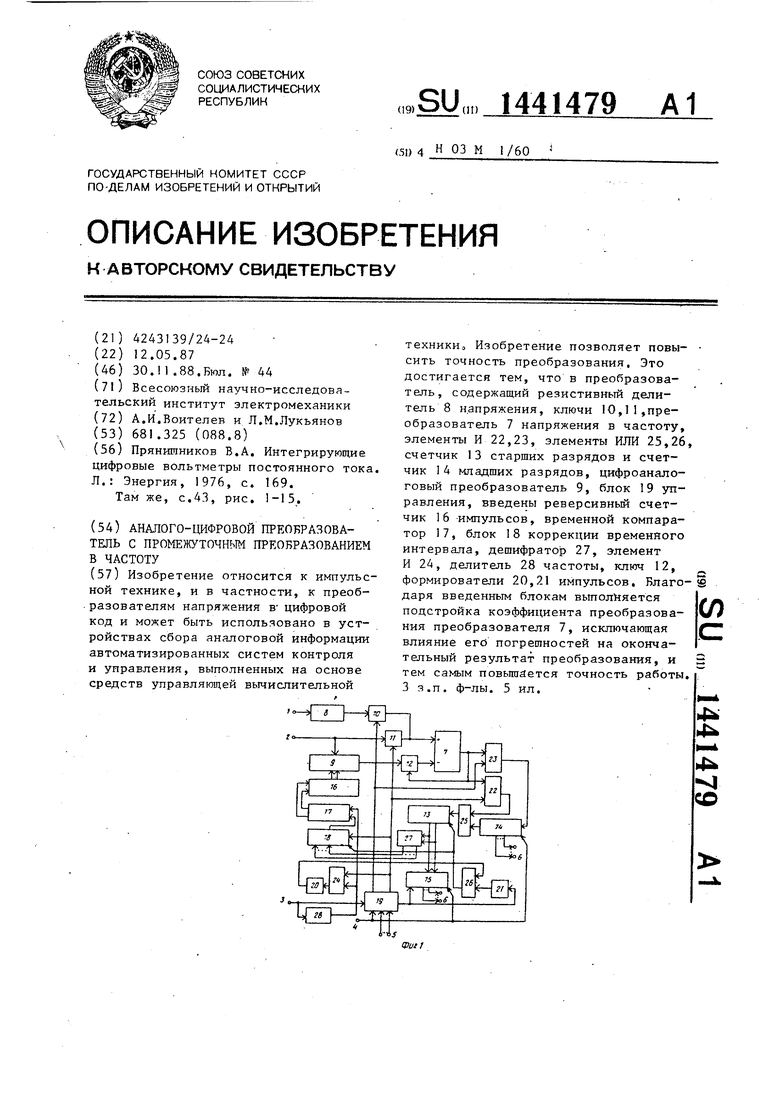

Влок 19 управления содержит счетчик 46 импульсов, работающий на вычитание, триггер 47, элемент 48 задержки, формирующий сигнал через некоторое время после включения питания, формирователь 49 импульсов, элемент И 50 и элемент ИЛИ 51.

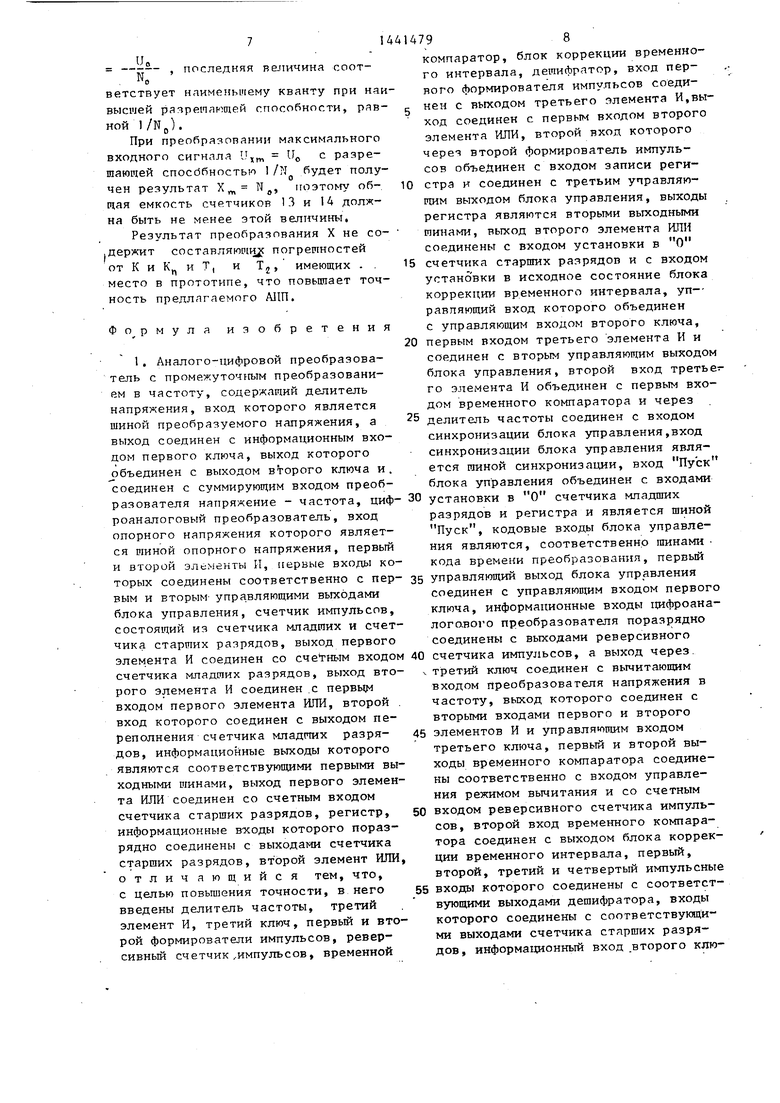

На временных диаграммах обозначены: 52 - импульсы синхронизации.имеющие частоту Tf. ; 53 - импульсы на выс ходе делителя 28; 54 - импульсы на выходе элемента И 22; 55 - сигналы на выходе элемента 1{ЯИ 43; 56 - выходные импульсы компаратора 17; 57 - импульс пуска АЦП -в работу; 58 - сиг10 нал 1 на выходе триггера 47; 59 - импульсы на выходе элемента И 23; 60 - импульс записи результирующего кода в регистр 15.

Аналого-цифровой преобразователь

15 (АЦП) работает следующим образом.

Цри включении напряжения питания элемент 48 задержки через некоторое время формирует сигнал, который устанавливает в О триггер 47, а его

20 сигнал с 0 -выхода осуществляет: с помощью, ключа 11 подключение опорного напряжения и, на вход преобразователя 7, с помощью элемента И 22 подачу импульсов F на счетный вход

25 счетчика 13 с выхода преобразователя 7 {через элемент ШШ 25), с помощью элемента И 24 подачу.пересчитанных на S делителем 28 частоты импульсов 52 синхронизации, имеющих частоту

30 f, на вход формирователя 20. Его выходные импульсы устанавливают код равньй о, в счетчике 13 (через элемент ИЛИ 26) и в счетчике 38. I

Начиная с эт-ого импульса за время

t. S/f, выполняется проверка праС

вильности настройки коэффициента К Кд преобразователя 7, обеспечивающего равенство F pf путем 40 сравнения tg с временем t

35

Sp .N

--- при помощи компарато- FOFO

ра 17.

При tp t компаратор 17 форми- д5 рует сигналы на изменение на единицу кода в счетчике 16, который управляет ЦАП 9. Измененное выходное нап

ряжение ЦАП 9, равное J(t U;(t;)±Uj, где ид - квант ЦАП, с помоцрью ключа 12 будет подключаться на вычитающий вход преобразователя 7 в течение длительности t его выходного импульса и тем са;мьгм изме- Нять его выходную частоту. Если до подстройки

F,(t;)

i(Uo)

тги;т 1ГГ1;п 7 1

то после изменения напряжения ЦАП:

Fc,(-i.

i (Uo)

-iru;7Vlcu;(

I

7

Таким образом, выполняется подстройка К преобразователя 7, обр.спе- чивающая величину К К.

Процесс подстройки после включе- ния питания и при отсуствии о начале преобразования выполняется с каяодым импульсом 53, в результате чего поддерживается равенство F pf. , согласно которому величина подстроенного коэффициента К будет равна К -

о Подстройка выполняется за время

t, равное периоду повторения импульсов 53 с выхода делителя 28, В процессе подстройки интервал времени t, формируемся с помощью ступени счетчика 13 и депшфратора 27, у которого окончание выходного сигнала на,выходе, соответствукщего коду величиной

(N-l), означает, что

t -

F;

Ho из-за отсутствия синхронизации между fp и Рд первый импульс F может поступить в счетчик 13 через время t, , меньшее 1/F, после начала t. Поэтому в этом случае необхо димо увеличить t, что реализует, блок 18,

В блоке 18 (после установки в О счетчика 38) через элемент ИЛИ 44 задним фронтом импульса (начиная с t.jj) запускается формирователь 41, выходной импульс t(p| которого через элемент И 42, открытый сигналом с 0 -выхода триггера 47, задним фронтом запускает формирователь 40, Его выходной импульс t 0,2, поступает на счетчик 38 и задним фронтом запускает через элемент ИЛИ 44 формирователь 41, Такая работа продолжается в течение времени t действия первого импульса 55, соответствующего коду О в ступени счетчика 13 и сигналу на втором выходе дешифратора 27

С появлением (в течение t) п ерво- го импульса F в счётчике 13 устанавливается код, равньй 1, а соответствующий ему сигнал не используется, в результате чего инвертор 39 запрещает в течение времени t прохождение импульсов от формирователя 40 через элемент ИЛИ 44, Накопленный за

время t, в счетчике 38 код будет рагде t(p,, t(p, +

вен

+ t

m, -г,

ерп

(f-i

, при этом m 60, ,, - о . Если m 2 : О, то в

С приходом второго импульса F в счетчике 13 устанавливается код, равный 2, и соответствующий ему сигнал с третьего выхода дешифратора 27

0 включает в счетчике 38 режим вычитания. Этот сигнал, пройдя через элемент ИЛИ 43 (второй импульс 55) на инвертор 39, через элемент ИЛИ 44 запускает формирователь 41, а затем

5 формирователь 40, в результате чего в c4e t4HK 38 начнут поступать импульсы, которые будут вычитаться из кода

и, (в течение времени t ---) до

- о

0 прихода третьего импульса F. За это время в счетчик 38 поступит т импульсов и останется код т, т - .

t4 - t о

Шд - -Г

(pli

5 так как t, t

старшем разряде счетчика 38 установится 1 и этот сигнал через элемент ИЛИ 45 поступит на выход бло ка 18.

0 Код т, будет храниться в счет чике 38 до окончания tj,, т,е, пока в счетчик 13 не поступит N импульсов FJJ , после окончания последнего из них сигнал с четвертого выхода

5 дешифратора 27 (третий импульс 55), соответствующий коду N в счетчике 13, вновь запускает формирователи 41 и 40, в результате чего в счетчике 38 код будет увеличиваться

0 до нуля. Это произойдет через время t m,t(j,, (m o - m, )t,2 . В момент окончания времени 13 старший разряд счетчика 38 установится в О, сня- - тие этого сигнала на выходе блока 18

5 означает, что закончился интервал времени t с выполненной коррекцией. Величина tj, равна

ti, t, + t(N-l) + t, . 0 t, + to (N-l) + (, )t(j,,2

t N

или

ч , t,.

55 Когда t, t, TO величина m 0 и t должен заканчиваться после прохождения N импульсов F, Для этого сигнал с первого выхода дешифратора 27, соответствующий коду

51441479

(N-1) в счетчике 13, подается на элемент ИЛИ 45 и по его заднему.фронту опредепяется окончание tf,.

ещ

им

н

Сравнение t

с

t« выполняет

временной компаратор 17. Если оконча ние tg сигнала 53 пост Упаюпего на второр вход временного компаратора 17, произойдет раньше окончания t, сигналя, поступающего на его первый вход (это происходит при более низкой частоте преобразователя 7 по сравнению с F , т.е. при К «с К), то триггеры 29-31 будут находиться в состоянии О, так они были установлены в предыдущем такте настройки, в результате чего через элементы И 35 и ИЛИ 37 на второй выход временного компаратора 17 пройдет сигнал 53, а на первый выхЪд - сигнал О с выхода триггера 31. Эти сигна- лы в счетчике 16 уменьшат код на единицу, что изменит выходной сигнал ЦАП 9, равный lJJt|., ) U(t; )tU;j, который в преобразователе 7 увеличит коэффициент К и его выходную частоту. Благодаря этому в следующем такте настройки интервал времени t будет уменьшен.

Если окончание t окончания t

происходит до J,, то преобразователь 7 имеет более высокую частоту, чем F , т.е. , в результате чего по заднему фронту сигнала (временного интервала t,) устанавливается в 1 триггер 30 и последовательно запускаются формирователи 34 и 33, устанавливающие в 1 триггеры 29 и 31.Окон

6

еще находится в 0. В этом случае

импульс 53 через элементы И 33 и 36

не пройдет, т.е. код в счетчике 16

не изменяется, так как К К„ и F

Pf с .

Каждый такт подстройки К заканчивается установкой в П триггеров 29-31 с помощью одновибратора 32 и

установкой кода, равного О, в счетчике 13 импульсом с формирователя 20 через элемент ИЛИ 26.

Подстройка К выполняется после окончания очередного импульса 53, если нет сигнала 57 начала преобра:зова- ния, и после окончания очередного преобразования. Сигнал 57 приходит синхронно с импульсом 53. Когда заканчивается подстройка К, он устанавливает в О счетчик 14 и регистр 15, в 1 триггер 47 и записывает код q с кодовых входов в счетчик 46.

Величина q определяет время выполнения преобразования, равное Т

q/fg, которое формируется счетчиком 46, работающим на вычитание и имеющем входные импульсы 52, проходящие через элемент И 50, открытый сигналом 58, т.е. сигналом 1 на выходе триггера 47. Этот же сигнал подключает с помощью ключа П входное напряжение Uj,, прошедшее через резис- тивный делитель 8, на суммирующий вход преобразователя 7, в результате

чего выходные импульсы 59 частоты

Р проходят через элемент И 23, открытый сигналом 58, на счетный вход счетчика 14. Преобразование заканчивается по коду О в счетчике 46,ко

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Устройство демодуляции телевизионного сигнала системы Секам | 1989 |

|

SU1688458A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1051703A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Адаптивный аналого-цифровой преобразователь | 1984 |

|

SU1226666A1 |

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Преобразователь временных интервалов | 1988 |

|

SU1525914A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

Изобретение относится к импульсной технике, и в частности, к преобразователям напряжения в цифровой код и может быть испольяовано в устройствах сбора аналоговой информации автоматизированных систем контроля и управления, выполненных на основе средств управляющей вычислительной техники. Изобретение позволяет повысить точность преобразования. Это достигается тем, что в преобразователь, содержащий резистивный делитель 8 напряжения, ключи 10,11,преобразователь 7 напряжения в частоту, элементы И 22,23, элементы ИЛИ 25,26 счетчик 13 старших разрядов и счетчик 14 младших разрядов, цифроанало- говый преобразователь 9, блок 19 управления, введены реверсивный счетчик 16 импульсов, временной компаратор 17, блок 18 коррекции временного интервала, дешифратор 27, элемент И 24, делитель 28 частоты, ключ 12, формирователи 20,21 импульсов. Благо даря введенным блокам вьтолКяется подстройка коэффициента преобразования преобразователя 7, исключающая влияние погрешностей на окончательный результат преобразования, и тем самым повьшйется точность работы 3 з.п. ф-лы. 5 ил. - SS сл

чание tg, приводит к прохождению сиг- 40 торый снимает сигнал с выхода элеменнала 53 через.элементы И 36 и ИЛИ 37 на второй выход временного компаратора 17, а на его первом выходе сигнал будет отсутствовать, так как триггер

та ИЛИ 51 и устанавливает О в триггере 47. По заднему фронту сигнала 58 запускается формирователь 49, сигнал 60 которого записывает в регистр

31 находится в 1. В счетчике 16 код 45 15 код счетчика 13 и через формирова- будет увеличен на единицу, в результате чего изменится выходной сигнал ЦАП 9, равный U,(t j, ) U(ti )±Ub, который уменьщит К преобразователя 7 и его выходную частоту, а это означа50

тель 21 и элемент ИЛИ 26 устанавливает в последнем и в счетчике 38 коды, равные О. Начинается очередной такт подстройки К преобразователем 7, а на шинах 6 находится код результата преобразования:

ет, что t в следующем такте подстройки будет увеличено.

Процесс подстройки К преобразователя 7 будет выполляться до тех пор, пока окончание t не будет происходить в течение интервала времени t,-, когда действуют импульсы формирователей 34 и 33 (t 2ta)) и триггер 30 установлен в 1, а триггер 29

торый снимает сигнал с выхода элемента ИЛИ 51 и устанавливает О в триггере 47. По заднему фронту сигнала 58 запускается формирователь 49, сигнал 60 которого записывает в регистр

45 15 код счетчика 13 и через формирова-

50

тель 21 и элемент ИЛИ 26 устанавливает в последнем и в счетчике 38 коды, равные О. Начинается очередной такт подстройки К преобразователем 7, а на шинах 6 находится код результата преобразования:

X К,и,Т

Ux р

iJx q ---,

V

где и„ - квант АЦП, зависящий от величины q (при q 1 - а няется от По/Р Д

mU-V

изме714414798

Uoкомпаратор, блок коррекции временно , последняя величина СООТ-isuMnnijai ,,кьNOго интервала, дешифратор, вход перветствует наименьшему кванту при наи- кого формирователя импульсов соеди- высшей разрешающей способности, ран- с ней с выходом третьего элемента И,вы- ной l/Ng). ход соединен с первым входом второго

При преобразовании максимального элемента ИЛИ, второй вход которого входного сигнала 1), U с разре- черея второй формирователь импуль- шающей способностью будет полу- сов объединен с входом записи реги- чен результат Х„ N, поэтому об- 10 стра и соединен с третьим управляющая емкость счетчиков 13 и 14 долж- щим выходом блока управления, выходы на быть не менее этой величины, регистра являются вторыми выходными

Результат преобразования X не со- тинами, выход второго элемента ИЛИ |Держит составляюо1и 5 погрешностей соединены с входом установки в О от К и К и Т, и Tj, имеющих . . 15 счетчика старптх разрядов и с входом место в прототипе, что повьшает точ- установки в исходное состояние блока ность предлагаемого А11П.коррекции временного интервала, уп-

равняющий вход которого объединен

Фо рмула изобретенияс управляющим входом второго ключа,

20 первым входом третьего элемента И и

ной компаратор выполнен на трех триггерах, одновибраторе, двух формирователях импульсов, двух элементах И, элементе ИЛИ, выход которого является вторым выходом временного компара- тора, первый и второй входы элемента ИЛИ соединены соответственно, с выхо дами первого и второго элементов И,- первые входы которых объединены и являются первым входом временного компаратора, вторые входы первого и второго элементов И соединены,соответственно, с прямым и инверсным выходами первого триггера, третьи входы первого и второго элементов И соединены соответственно с прямым и инверсным выходами второго триггера, входы установки в О первого,второго и третьего триггеров объединены и соединены с выходом одновибратора, вход которого объединен с входом установки в 1 первого тригге ра и через первый формирователь импульсов соединен с выходом второго формирователя импульсов и входом установки в 1 третьего триггера, прямой выход которого является первым выходом временного компаратора, вторым входом

которого является вход установки в второго триггера и вход второго

Ч

формирователя импульсов.

3, Преобразователь по п.1, о т - личающийся тем, что блок коррекции временного интервала выполнен на реверсивном счетчике импульсов, двух формирователях импульсов, инверторе, трех элементах ИЛИ, элементе И, первый вход которого является управляющим входом блока, выход и вход установки в исходное состояние которого являются, соответственно выходом первого элемента ИЛИ и входом установки в О реверсивного счетчика импульсов, объединенным с первым входом второго элемента ИЛИ, первый импульсный вход блока являет- ;-

5

ся первым входом первого элемента ИЛИ, второй, третий и четвертый импульсные входы блока являются соответственно первым, вторьм и третьим входами третьего элемента ИЛИ, второй вход которого объединен с входом управления режимом вычитания реверсивного счетчика импульсов, а выход через инвертор соединен с вторым входом второго элемента ИЛИ, третий вход которого объединен со счетным входом реверсивного счетчика импульсов и через первый формирователь импульсов соединен с выходом элемента И, второй вход которого через второй формирователь импульсов соединен с выходом второго элемента ИЛИ, выход старшего разряда реверсивного счетчика импульсов соединен с вторым входом первого элемента ИЛИ.

и счетчика импульсов, а выход - с

О

входом установки в О триггера,прямой выход которого является вторым управляющим выходом блока, первым управляющим выходом которого является реверсивный выход триггера, соёдиненный с первым входом элемента И и входом формирователя импульсов, выход которого является третьим управляю- щим выходом блока, кодовые входы которого являются соответствующими информационными входами счетчика импульсов, вход записи кода которого объединен с входом установки в 1 триггера и является входом Пуск блока, вход синхронизации которого

является вторым входом элемента И, выход которого соединен со счетным входом счетчика импульсов, вход установки в начальное состояние триггера соединен с выходом элемента задержки, вход которого является шиной питания.

Вых.

5

t

f/5

t i /y

V7

7

Фиг. 2

38

В)(УПР

4 59

Фае. 5

Уалмоа.

$.

5 n -JLJl Jl-Jl-Jl«Jl

ue. 5

| Прянишников В.А | |||

| Интегрирующие цифровые вольтметры постоянного тока | |||

| Л.: Энергия, 1976, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Там же, с.43, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-11-30—Публикация

1987-05-12—Подача