е&

2

00

Изобретение относится к вычислительной технике и радиолокации и предназначено для отождествления пеленгов (углов места и азимутов), полученных двумя пеленгаторами об одних и тех же объектах, и может быть использовано для отождествления пеленгов движущихся объектов в триангуляционных системах пассивной локации.

Цель изобретения - повышение быстродействия и достоверности отождествления набора данных за счет реализации инвариантно-группового алгоритма обработки информации.

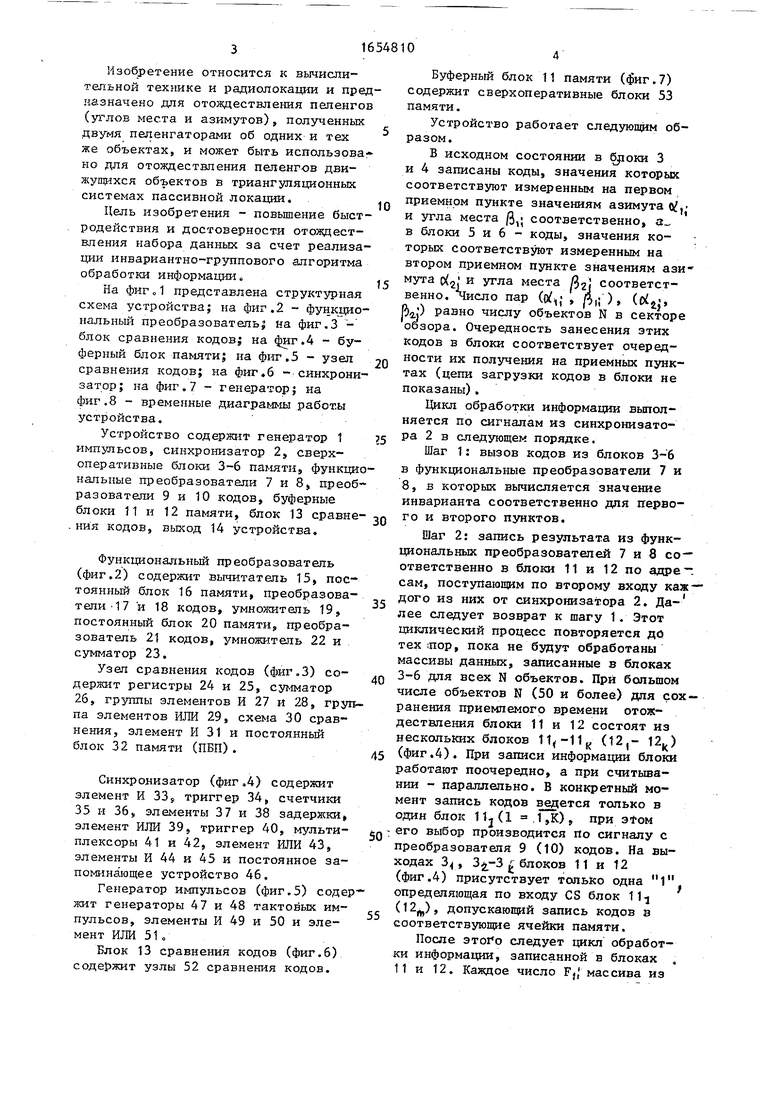

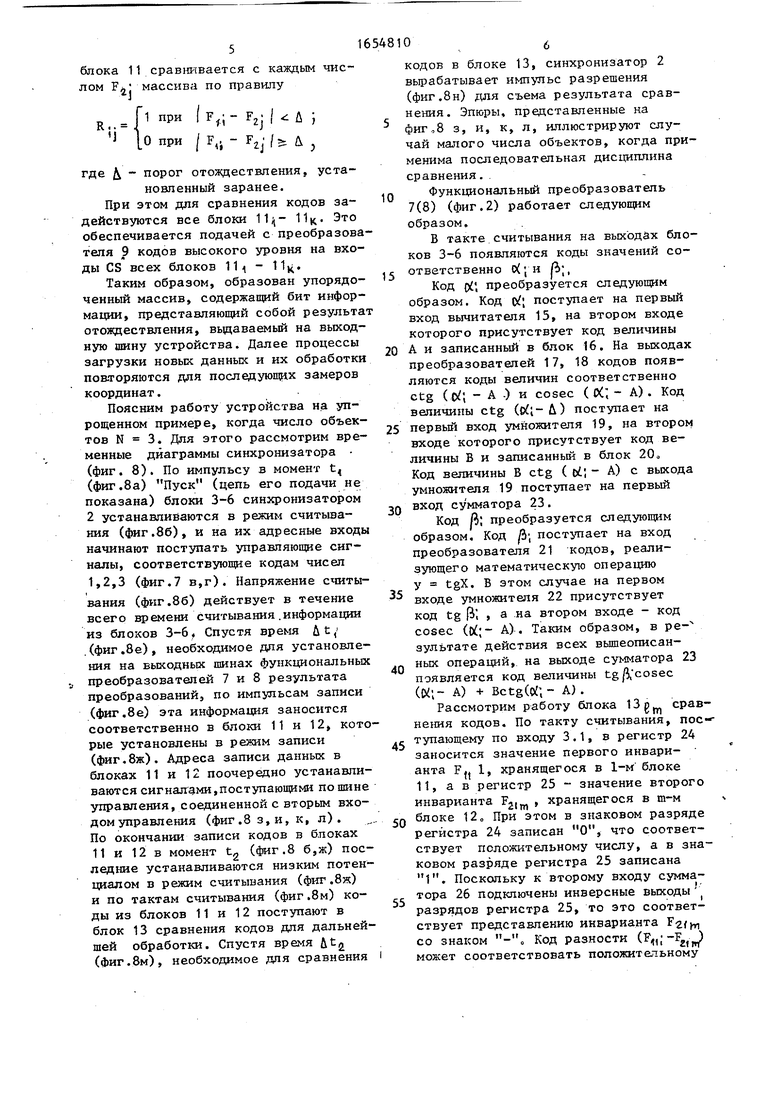

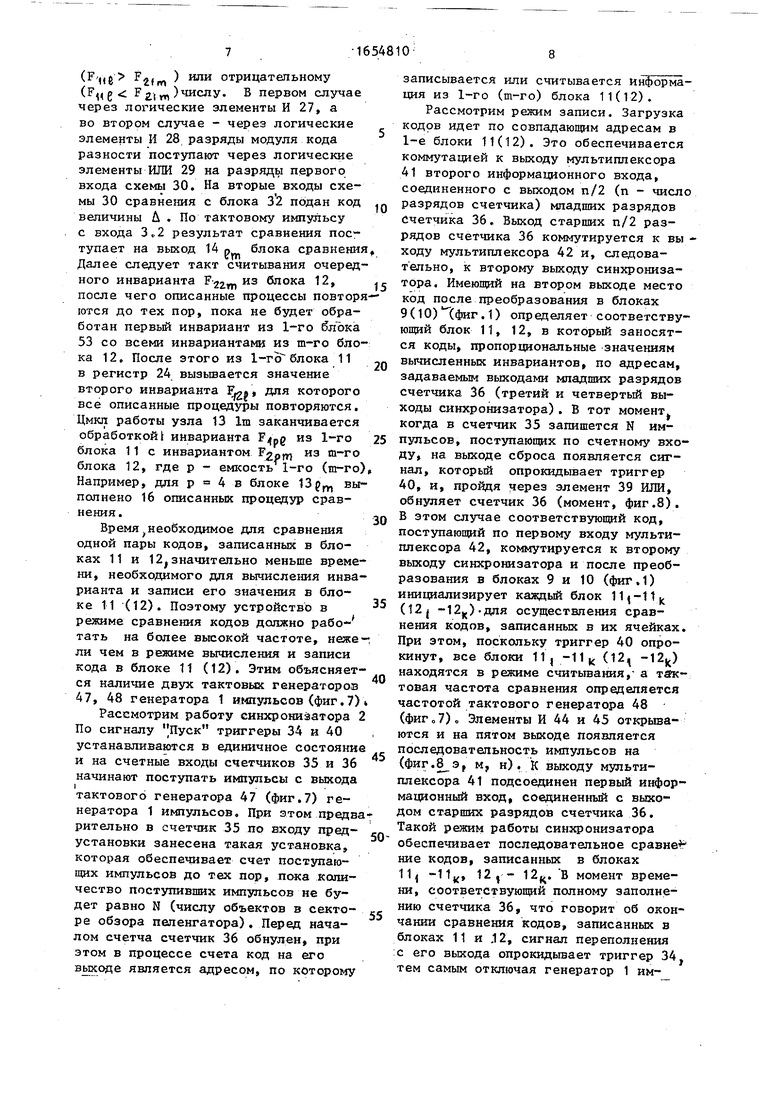

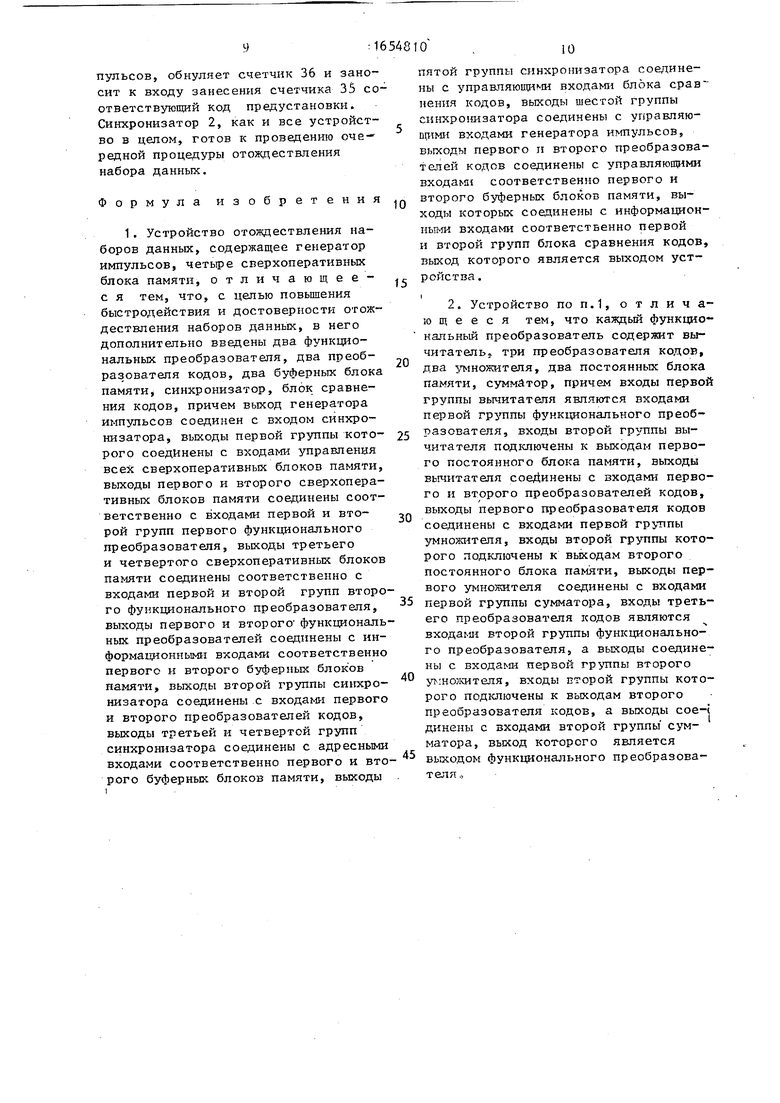

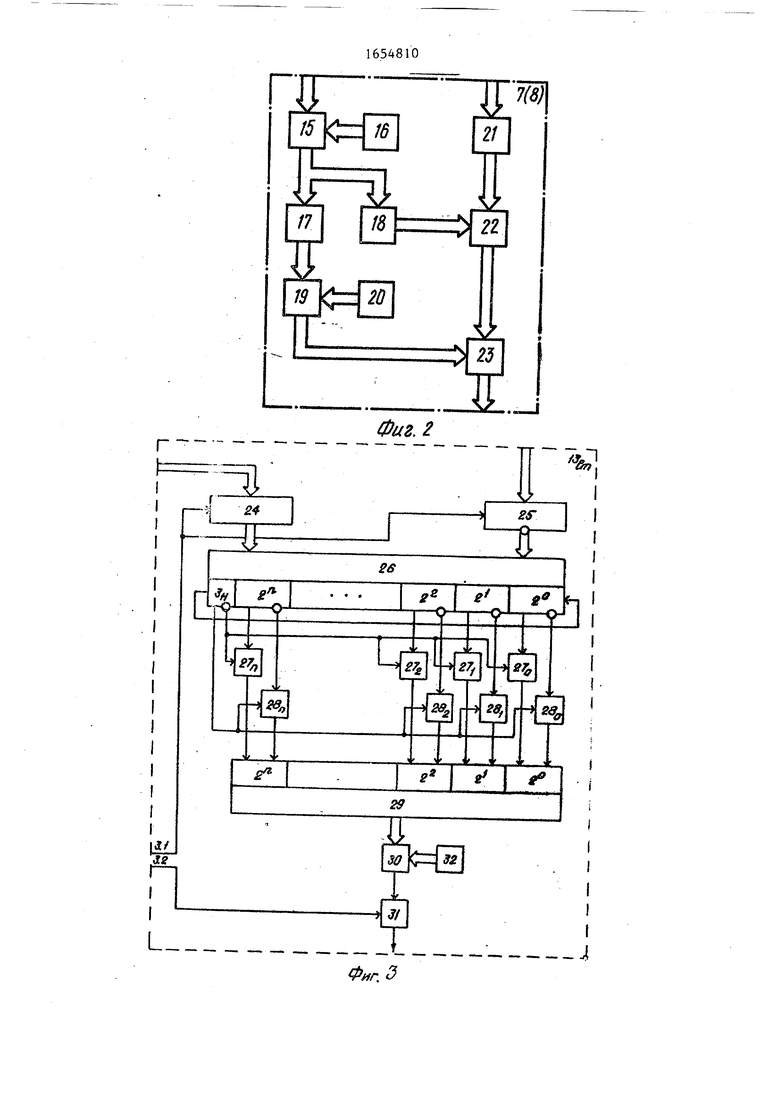

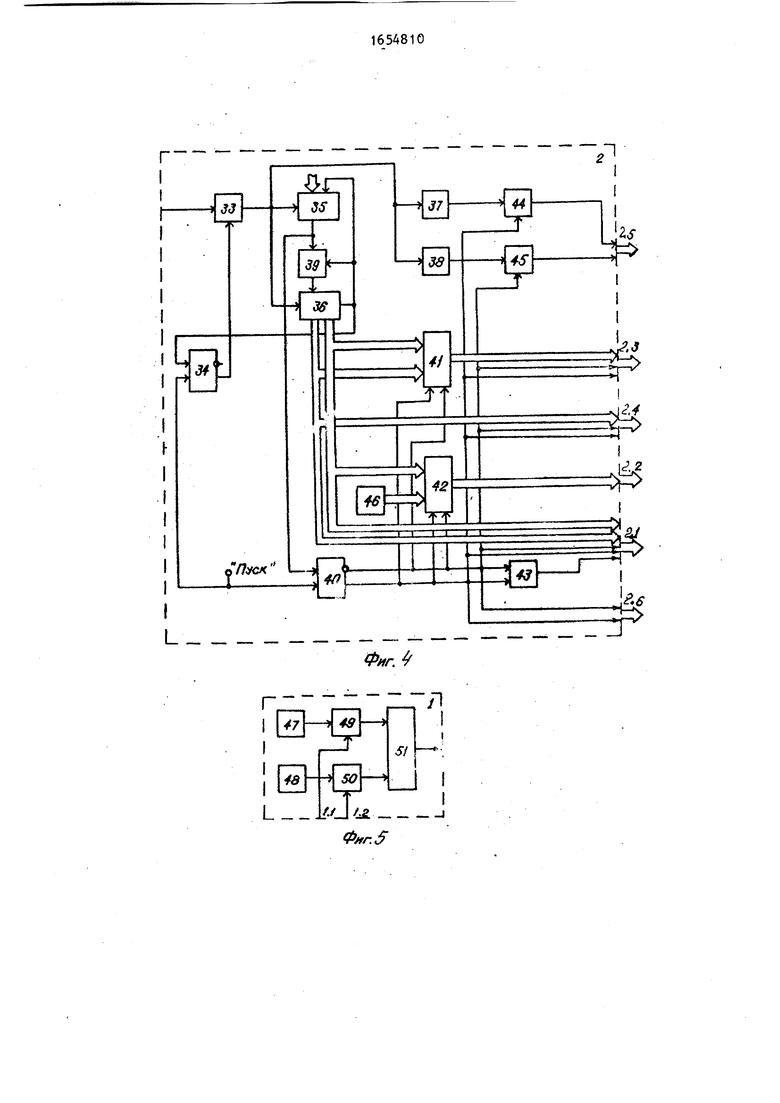

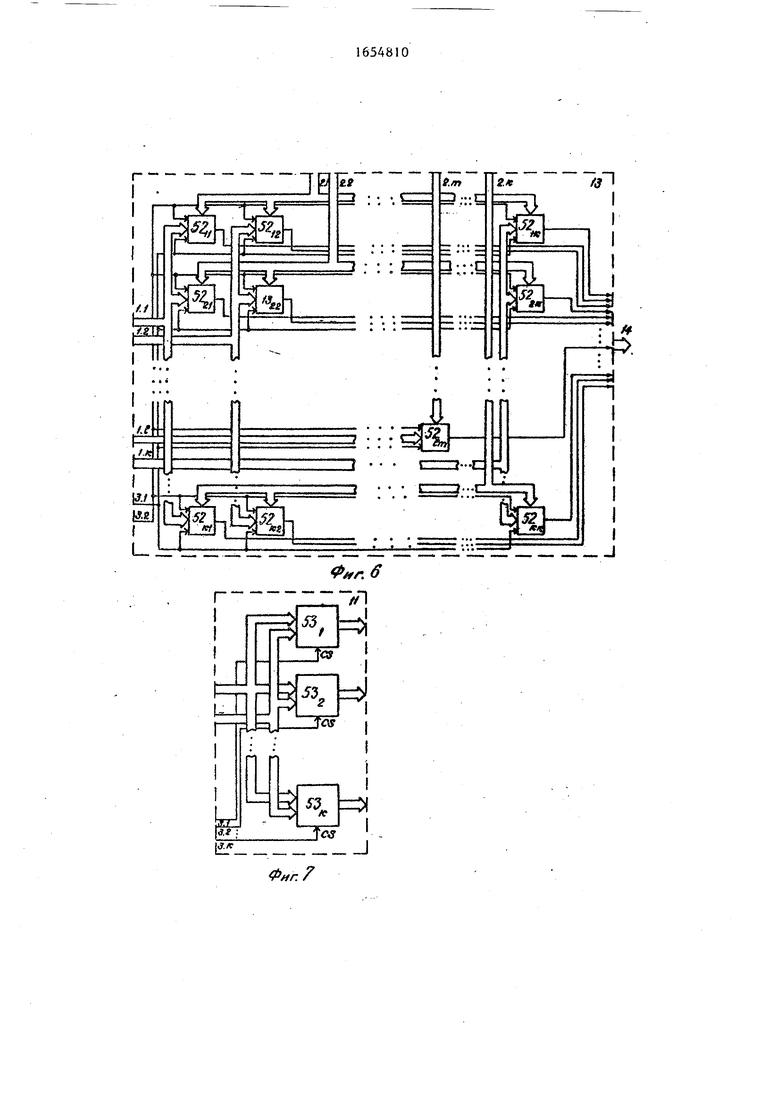

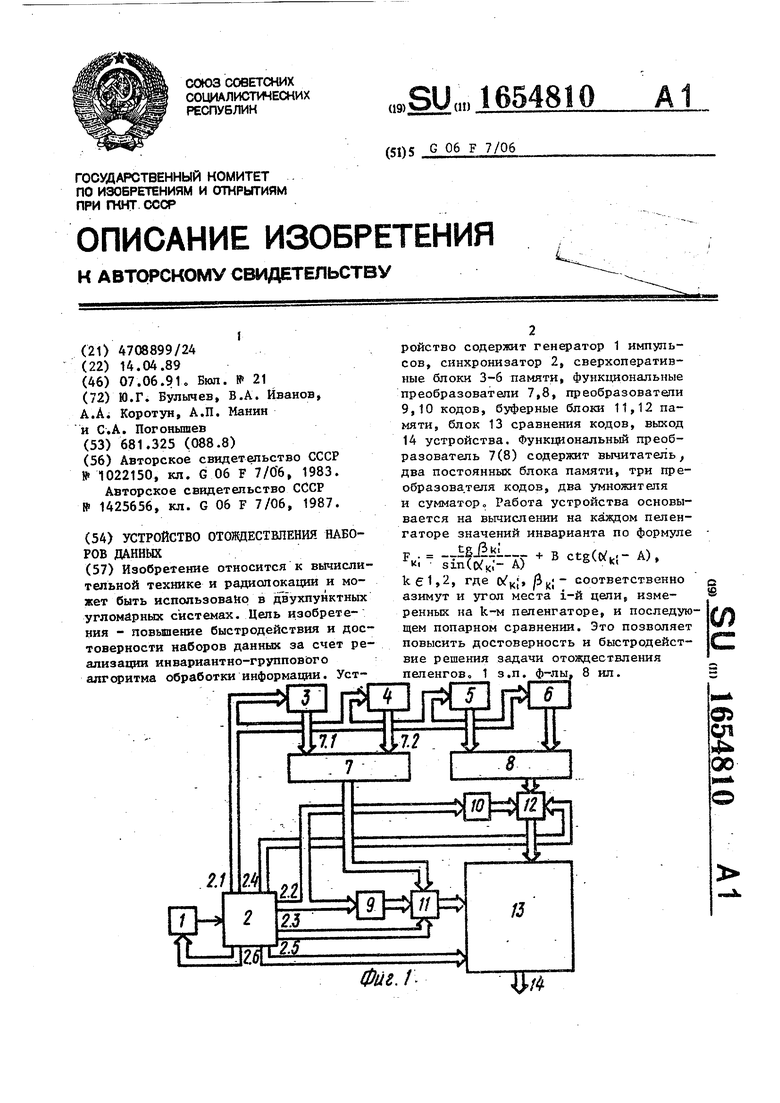

На фиг о 1 представлена структурная схема устройства; на фиг.2 - функциональный преобразователь на фиг.З - блок сравнения кодов; на .4 - буферный блок памяти; на фиг.З - узел сравнения кодов; на фиг.6 - синхронизатор; на фиг.7 - генератор; на фиг.8 - временные диаграммы работы устройства.

Устройство содержит генератор 1 импульсов, синхронизатор 2, сверхоперативные блоки 3-6 памяти, функциональные преобразователи 7 и 8, преобразователи 9 и 10 кодов, буферные блоки 11 и 12 памяти, блок 13 сравне- ния кодов, выход 14 устройства.

Функциональный преобразователь (фиг.2) содержит вычитатеяь 15, постоянный блок 16 памяти, преобразователи 17 и 18 кодов, умножитель 19, постоянный блок 20 памяти, преобразователь 21 кодов, умножитель 22 и сумматор 23.

Узел сравнения кодов (фиг.З) со- держит регистры 24 и 25, сумматор 26, группы элементов И 27 и 28, группа элементов ИЛИ 29, схема 30 сравнения, элемент И 31 и постоянный блок 32 памяти (ПБП).

Синхронизатор (фиг.4) содержит элемент И 339 триггер 34, счетчики 35 и 36, элементы 37 и 38 задержки, элемент ИЛИ 39, триггер 40, мульти- плексоры 41 и 42, элемент ИЛИ 43, элементы И 44 и 45 и постоянное запоминающее устройство 46.

Генератор импульсов (фиг.5) содержит генераторы 47 и 48 тактовых им- пульсов, элементы И 49 и 50 и элемент ИЛИ 51 о

Блок 13 сравнения кодов (фиг.6) содержит узлы 52 сравнения кодов.

n

5 п

-. 5

п

5

Буферный блок 11 памяти (ф иг. 7) содержит сверхоперативные блоки 53 памяти.

Устройство работает следующим образом.

В исходном состоянии в блоки 3 и 4 записаны коды, значения которых соответствуют измеренным на первом приемном пункте значениям азимута и угла места $,; соответственно, а в блоки 5 и 6 - коды, значения которых соответствуют измеренным на втором приемном пункте значениям ази мута р(г( и угла места А2| соответственно. Число пар ( , /$,;), (oi, 64j) равно числу объектов N в секторе обзора. Очередность занесения этих кодов в блоки соответствует очередности их получения на приемных пунктах (цепи загрузки кодов в блоки не показаны).

Цикл обработки информации выполняется по сигналам из синхронизатора 2 в следующем порядке.

Шаг 1: вызов кодов из блоков 3-6 в функциональные преобразователи 7 и 8, в которых вычисляется значение инварианта соответственно для первого и второго пунктов.

Шаг 2: запись результата из функциональных преобразователей 7 и 8 соответственно в блоки 11 и 12 по адре - сам, поступающим по второму входу каждого из них от синхронизатора 2. Да- лее следует возврат к шагу 1. Этот циклический процесс повторяется до тех пор, пока не будут обработаны массивы данных, записанные в блоках 3-6 для всех N объектов. При большом числе объектов N (50 и более) для сохранения приемлемого времени отождествления блоки 11 и 12 состоят из нескольких блоков (12,- 12) (фиг.4). При записи информации блоки работают поочередно, а при считывании - параллельно. В конкретный момент запись кодов ведется только в один блок 11-(1 1,К)t при этом - его выбор производится по сигналу с преобразователя 9 (10) кодов. На выходах 3+, Ј блоков 11 и 12 (фиг.4) присутствует только одна 1 определяющая по входу CS блок 11-j (12m), допускающий запись кодов в соответствующие ячейки памяти.

После следует цикл обработки информации, записанной в блоках . 11 и 12. Каждое число F,,1 массива из

516548

блока 11 сравнивается с каждым числом 7г массива по правилу

Г1 при IF,;- F,; | Д :

R.. Ч

2J

.° РИ FZJ/ & ,

где - порог отождествления, установленный заранее.

При этом для сравнения кодов за- действуются все блоки 11ц. Это обеспечивается подачей с преобразователя 9 кодов высокого уровня на входы CS всех блоков 111 - 11К.

Таким образом, образован упорядоченный массив, содержащий бит информации, представляющий собой результа отождествления, выдаваемый на выходную шину устройства. Далее процессы загрузки новых данных и их обработки поаторяются для последующих замеров координат.

Поясним работу устройства на упрощенном примере, когда число объектов N 3. Для этого рассмотрим временные диаграммы синхронизатора (фиг. 8). По импульсу в момент t (фиг.8а) Пуск (цепь его подачи не показана) блоки 3-6 синхронизатором 2 устанавливаются в режим считывания (фиг.86), и на их адресные входы начинают поступать управляющие сигналы, соответствующие кодам чисел 1,2,3 (фиг.7 в,г). Напряжение считывания (фиг.86) действует в течение всего времени считывания.информации из блоков 3-6« Спустя время ut,1 (фиг,8е), необходимое для установления на выходных шинах функциональных преобразователей 7 и 8 результата преобразований, по импульсам записи (фиг.8е) эта информация заносится соответственно в блоки 11 и 12, которые установлены в режим записи (фиг.8ж). Адреса записи данных в блоках 11 и 12 поочередно устанавливаются сигналами, поступающими по шине управления, соединенной с вторым входом управления (фиг.8 з,и, к, л). По окончании записи кодов в блоках 11 и 12 в момент tg (фиг.8 б,ж) последние устанавливаются низким потенциалом в режим считывания (фиг.8к) и по тактам считывания (фиг ,8м) коды из блоков 11 и 12 поступают в блок 13 сравнения кодов для дальнейшей обработки. Спустя время t (фиг.8м), необходимое для сравнения

5

0

5

0

5

0

5

0

5

1°6

кодов в блоке 13, синхронизатор 2 вырабатывает импульс разрешения (фиг.бн) для съема результата сравнения. Эпюры, представленные на фиг,8 з, и, к, л, илотюстрируют случай малого числа объектов, когда применима последовательная дисциплина сравнения.

Функциональный преобразователь 7(8) (фиг.2) работает следующим образом.

В такте считывания на выходах блоков 3-6 появляются коды значений соответственно (X; и ft;,

Код tf. преобразуется следующим образом. Код , поступает на первый вход вычитателя 15, на втором входе которого присутствует код величины А и записанный в блок 16. На выходах преобразователей 17, 18 кодов появляются коды величин соответственно ctg ( oi; - А -) и cosec ( ОС; - А) . Код величины ctg (#1-Д) поступает на первый вход умножителя 19, на втором входе которого присутствует код величины В и записанный в блок 20, Код величины В ctg ( Ы; А) с выхода умножителя 19 поступает на первый вход сумматора 23.

Код ft; преобразуется следующим образом. Код fi поступает на вход преобразователя 21 кодов, реализующего математическую операцию у tgX. В этом случае на первом входе умножителя 22 присутствует код tg $ , , а на втором входе - код cosec (0(; А). Таким образом, в ре-4 зультате действия всех вышеописанных операций, на выходе сумматора 23 появляется код величины tg cosec (К;- А) + Bctg(oT,- A).

Рассмотрим работу блока 13 рт сравнения кодов. По такту считывания, тупающему по входу 3.1, в регистр 24 заносится значение первого инварианта FJ. 1, хранящегося в 1-м блоке 11, а в регистр 25 - значение второго инварианта F2im хранящегося в т-м блоке 12„ При этом в знаковом разряде регистра 24 записан О, что соответствует положительному числу, а в знаковом разряде регистра 25 записана 1. Поскольку к второму входу сумматора 26 подключены инверсные выходы разрядов регистра 25, то это соответствует представлению инварианта со знаком -. Код разности (F,;-F21)J может соответствовать положительному

(F/,,g F2fm ) или отрицательному ( ( F г, m) числу. В первом случае через логические элементы И 27, а во втором случае - через логические элементы И 28 разряды модуля кода разности поступают через логические элементы ИЛИ 29 на разряды первого входа схемы 30. На вторые входы схемы 30 сравнения с блока подан код величины А . По тактовому импульсу с входа результат сравнения поступает на выход 14 « блока сравнения Далее следует такт считывания очередного инварианта F 22rn из блока 12, после чего описанные процессы повторяются до тех пор, пока не будет обработан первый инвариант из 1-го блЪка 53 со всеми инвариантами из m-го блока 12. После этого из 1-гсГ блока 11 в регистр 24 вызывается значение второго инварианта FU., для которого все описанные процедуры повторяются. Цмкл работы узла 13 1т заканчивается обработкой инварианта из 1-го блока 11 с инвариантом из блока 12, где р - емкость 1-го (т-го) Например, для р 4 в блоке 13рт выполнено 16 описанных процедур сравнения .

Время еобходимое для сравнения одной пары кодов, записанных в блоках 11 и 12,значительно меньше времени, необходимого для вычисления инварианта и записи его значения в блоке 11 (12). Поэтому устройство в режиме сравнения кодов должно рабо- тать на более высокой частоте, нежет ли чем в режиме вычисления и записи кода в блоке 11 (12). Этим объясняется наличие двух тактовых генераторов 47, 48 генератора 1 импульсов (фиг. 7)

Рассмотрим работу синхронизатора 2 По сигналу Пуск триггеры 34 и 40 устанавливаются в единичное состояние и на счетные входы счетчиков 35 и 36

начинают поступать импульсы с выхода

i

тактового генератора 47 (фиг.7) генератора 1 импульсов. При этом предварительно в счетчик 35 по входу пред- установки занесена такая установка, которая обеспечивает счет поступающих импульсов до тех пор, пока количество поступивших импульсов не будет равно N (числу объектов в секто- ре обзора пеленгатора). Перед началом счетча счетчик 36 обнулен, при этом в процессе счета код на его выходе является адресом, по которому

0

5 0

5

п -

0

5

записывается или считывается информация из 1-го (m-го) блока 11(12).

Рассмотрим режим записи. Загрузка кодов идет по совпадающим адресам в 1-е блоки 11(12). Это обеспечивается коммутацией к выходу мультиплексора 41 второго информационного входа, соединенного с выходом п/2 (п - число разрядов счетчика) младших разрядов счетчика 36. Выход старших п/2 разрядов счетчика 36 коммутируется к вы - ходу мультиплексора 42 и, следовательно, к второму выходу синхронизатора. Имеющий на втором выходе место код после преобразования в блоках 9(10)(фиг.1) определяет соответствующий блок 11, 12, в который заносятся коды, пропорциональные значениям вычисленных инвариантов, по адресам, задаваемым выходами младших разрядов счетчика 36 (третий и четвертый выходы синхронизатора). В тот момент когда в счетчик 35 запишется N импульсов, поступающих по счетному входу, на выходе сброса появляется сигнал, который опрокидывает триггер 40, и, пройдя через элемент 39 ИЛИ, обнуляет счетчик 36 (момент, фиг.8). В этом случае соответствующий код, поступающий по первому входу мультиплексора 42, коммутируется к второму выходу синхронизатора и после преобразования в блоках 9 и 10 (фиг.1) инициализирует каждый блок (12j -12к).для осуществления сравнения кодов, записанных в их ячейках. При этом, поскольку триггер 40 опрокинут, все блоки 11, -11 к (12 -12|) находятся в режиме считывания,- а тактовая частота сравнения определяется частотой тактового генератора 48 (фиг о 7)о Элементы И 44 и 45 открываются и на пятом выходе появляется последовательность импульсов на (фиг., м, н) . К выходу мультиплексора 41 подсоединен первый информационный вход, соединенный с выходом старших разрядов счетчика 36. Такой режим работы синхронизатора обеспечивает последовательное сравне ние кодов, записанных в блоках 11 -11 к 12, - 12ц. В момент времени, соответствующий полному заполнению счетчика 36, что говорит об окончании сравнения кодов, записанных в блоках 11 и .12, сигнал переполнения с его выхода опрокидывает триггер 34, тем самым отключая генератор 1 импульсов, обнуляет счетчик 36 и заносит к входу занесения счетчика 35 соответствующий код предустановки. Синхронизатор 2, как и все устройство в целом, готов к проведению очередной процедуры отождествления набора данных.

Формула изобретения

1. Устройство отождествления наборов данных, содержащее генератор импульсов, четыре сверхоперативных блока памяти, отличающее- с я тем, что, с целью повышения быстродействия и достоверности отождествления наборов данных, в него дополнительно введены два функциональных преобразователя, два преоб- разователя кодов, два буферных блока памяти, синхронизатор, блок сравнения кодов, причем выход генератора импульсов соединен с входом синхронизатора, выходы первой группы кото- рого соединены с входами управления всех сверхоперативных блоков памяти, выходы первого и второго сверхоперативных блоков памяти соединены соответственно с входами первой и вто- рой групп первого функционального преобразователя, выходы третьего и четвертого сверхоперативных блоков памяти соединены соответственно с входами первой и второй групп второго функционального преобразователя, выходы первого и второго функциональных преобразователей соединены с информационными входами соответственно первого и второго буферных блоков памяти, выходы второй группы синхронизатора соединены с входами первого и второго преобразователей кодов, выходы третьей и четвертой групп синхронизатора соединены с адресными входами соответственно первого и второго буферных блоков памяти, выходы

,. 5 0 5

0

пятой группы синхронизатора соединены с управляющими входами блока сравнения кодов, выходы шестой группы синхронизатора соединены с управляющими входами генератора импульсов, выходы первого и второго преобразователей кодов соединены с управляющими входами соответственно первого и второго буферных блоков памяти, выходы которых соединены с информационными входами соответственно первой и второй групп блока сравнения кодов, выход которого является выходом устройства .

2. Устройство поп.1, отлич а- ;о щ е е с я тем, что каждый функциональный преобразователь содержит вы- читатель, три преобразователя кодов, два умножителя, два постоянных блока памяти, сумматор, причем входы первой группы вычитателя являются входами первой группы функционального преобразователя, входы второй группы вычитателя подключены к выходам первого постоянного блока памяти, выходы вычитателя соединены с входами первого и второго преобразователей кодов, выходы первого преобразователя кодов соединены с входами первой группы умножителя, входы второй группы которого подключены к выходам второго постоянного блока памяти, выходы первого умножителя соединены с входами первой группы сумматора, входы третьего преобразователя кодов являются входами второй группы функционального преобразователя, а выходы соединены с входами первой группы второго умножителя, входы пторой группы которого подключены к выходам второго преобразователя кодов, а выходы coe-i динены с входами второй группы сумматора, выход которого является выходом функционального преобразователя ,

ТГЩ

16

21

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОТОЖДЕСТВЛЕНИЯ НАБОРОВ ДАННЫХ | 2010 |

|

RU2427884C1 |

| Подсистема определения дальности доплеровского радиопеленгатора | 1990 |

|

SU1797083A1 |

| Устройство для распознавания изображений объектов | 1988 |

|

SU1566385A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Аналого-цифровой фазовращатель | 1988 |

|

SU1584082A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

Изобретение относится к вычислительной технике и радиолокации и может быть использовано в двухпунктных угломарных системах. Цель изобретения - повышение быстродействия и достоверности наборов данных за счет реализации инвариантно-группового алгоритма обработки информации. Устройство содержит генератор 1 импульсов, синхронизатор 2, сверхоперативные блоки 3-6 памяти, функциональные преобразователи 7,8, преобразователи 9,10 кодов, буферные блоки 11,12 памяти, блок 13 сравнения кодов, выход 14 устройства. Функциональный преобразователь 7(8) содержит вычитатель, два постоянных блока памяти, три преобразователя кодов, два умножителя и сумматор о Работа устройства основывается на вычислении на каждом пеленгаторе значений инварианта по формуле + BctS(-A , где , соответственно азимут и угол места i-й цели, измеренных на k-м пеленгаторе, и последующем попарном сравнении. Это позволяет повысить достоверность и быстродействие решения задачи отождествления пеленгов, 1 з.п. ф-лы. 8 ил. i

IF

Г

L

i

I

s

Фиг. 2

&

2

и I 9-

5% r - «j г - за

j 4 I i

f1

г t e

.

ЯГ.

Фмг.7

-J U

t

м

S

U

I I

t I ill я n n n i

JL

| Устройство для сортировки чисел | 1982 |

|

SU1022150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1987 |

|

SU1425656A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1989-04-14—Подача