(Л

с:

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1984 |

|

SU1200278A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения арифметических устройств ЦВМ. Цель изобретения - расширение области применения за счет блокировки поступления на выход промежуточных результатов вычисления. Поставленная цель достигается тем, что ари1)метическое устройство, содер- жащее сумматоры-вычитатели 1,3, квадратор 2, коммутатор 4, сдвиговый регистр 5, злементыИЛИ 12, 19, 20, элементы И 13, 14, 15, элементы НЕ 17, 18 и триггер 21, содержит блок 6 элементов И и элемент И 16 с соответствующими связями . 1 ил.

ГС

ел

Од О1

О)

ю

и 22 ZJ

1

Изобретение относится к вычислительной технике и может быть использовано дпл построения арифметически устройств ЦВМ.

Цель изобретения - расширение области применения за счет блокиров1 и поступления на выход промежуточных результатов вычисления.

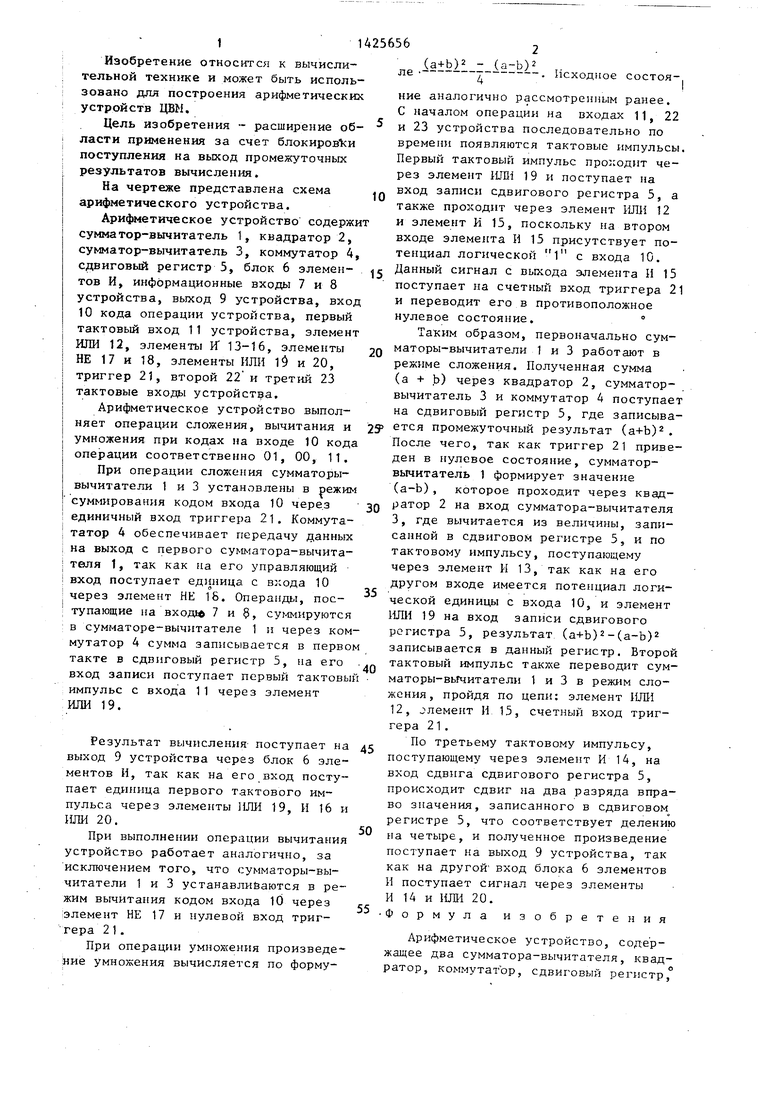

На чертеже представлена схема арифметического устройства.

Арифметическое устройство содерж сумматор-вычитатель 1, квадратор 2, сумматор-вычитатель 3, коммутатор 4 сдвиговый регистр 5, блок 6 элементов И, информационные входы 7 и 8 устройства, выход 9 устройства, вхо 10 кода операции устройства, первый тактовый вход 11 устройства, элемен ИЛИ 12, элементы И 13-16, элементы НЕ 17 и 18, элементы НЛИ 1$ и 20, триггер 21, второй 22 и третий 23 тактовые входы устройства.

Арифметическое устройство выполняет операции сложения, вычитания и умножения при кодах на входе 10 код операции соответственно 01, 00, 11,

При операции сложения сумматоры- вычитатели 1 и 3 установлены в режи сум№ рования кодом входа 10 через единичный вход триггера 21, Коммута- татор 4 обеспечивает передачу данных на выход с первого сумматора-вычита- теля 1, так как на его управляющий вход поступает единица с взсода 10 через элемент НК 18, Операнды, поступающие на ВХОД 7 и $, суммируются в сумматоре-вычитателе 1 и через коммутатор 4 сумма записывается в перво такте в сдвиговый регистр 5, на его вход записи поступает первый тактовы импульс с входа 11 через элемент ИЛИ 19,

Результат вычисления- поступает на выход 9 устройства через блок 6 элементов Н, так как на его вход поступает единица первого тактового импульса через элементы Ш11 19, И 16 и IfflH 20.

При выполнении операции вычитания устройство работает аналогично, за исключением того, что сумматоры-вы- читатели 1 и 3 устанавливаются в режим вычитания кодом входа lO через элемент НЕ 17 и нулевой вход триггера 21,

При операции умнохсения произведение умножения вычисляется по форму

ле

(а+Ь)2 - (а-Ь)2

Исходное Состоя-,

10

5

0

9

0

5

ние аналогично рассмотре1 иым ранее, С началом операции на входах 11, 22 и 23 устройства последовательно по времени появляются тактовые импульсы. Первый тактовый импульс проходит через элемент ИЛИ 19 и поступает на вход записи сдвигового регистра 5, а также проходит через элемент ИЛИ 12 и элемент И 15, поскольку на втором входе элемента И 15 присутствует потенциал логической 1 с входа 10, Данный сигнал с выхода элемента И 15 поступает на счетный вход триггера 21 и переводит его в противоположное нулевое состояние,°

Таким образом, первоначально сум- маторы-вычитатели 1 и 3 работают в режиме сложения. Полученная сумма (а + Ь) через квадратор 2, сумматор- вычитатель 3 и коммутатор А поступает на сдвиговый регистр 5, где записывается промежуточный результат (а+Ь), После чего, так как триггер 21 приведен в нулевое состояние, сумматор- вычитатель 1 формирует значение (а-Ь), которое проходит через квадратор 2 на вход сумматора-вычитателя 3, где вычитается из величины, записанной в сдвиговом регистре 5, и по тактовому импульсу, поступающему через элемент И 13, так как на его другом входе имеется потенциал логической единицы с входа 10, и элемент ИЛИ 19 на вход записи сдвигового регистра 5, результат (а+Ь)-(а-Ь) записывается в данный регистр. Второй тактовый импульс также переводит сум- маторы-вьГчитатели 1 и 3 в режим сложения, пройдя по цепи: элемент ИЛИ

12, элемент И.15, счетный вход триггера 21 .

По третьему тактовому импульсу, поступающему через элемент И 14, на вход сдвига сдвигового регистра 5, происходит сдвиг па два разряда вправо значения, записанного в сдвиговом регистре 5, что соответствует делению четыре, и полученное произведение поступает на выход 9 устройства, так как на другой вход блока 6 элементов И поступает сигнал через элементы И 14 и ИЛИ 20, Формула изобретения

Арифметическое устройство, содержащее два сумматора-вычитателя, квадратор, коммутатор, сдвиговый регистр,

триггер, два элемента НЕ, три элемента И и три элемента ItTDi, причем первый и второй информационные входы устройства соединены с соответствующими информационными входами первого сумматора-вычитателя, выход которого соединен с первым информационным входом коммутатора и входом квадратора, выход второго сумматора-вычитателя соединен с вторым информационным входом коммутатора, выход которого соединен с информационным входом сдвигового регистра, выход которого соединен с первым информационным входом- сумматора-вычитателя, второй информационный вход которого с выходом квадратора, первый тактовый вход устройства соединен с первыми входами первого и второго элементов ИЛИ, второй тактовый вход устройства соединен с вторым входом первого элемента ИЛИ и первым входом первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом раэ- решения записи сдвигового регистра, третий тактовый вход устройства соединен с первым входом второго элемента И, выход которого соединен с входом разрешения сдвига сдвигового регистра, вход первого разряда входа кода операции устройства соединен с вторыми входами первого и второ го элементов И и с первым входом третье

го элемента И, выход которого соеди- нет со счетным входом триггера, выход которого соединен с управляющими входами первого и второго суммато- ров-вычитателей, вход второго разряда входа кода операции устройства соединен через первый элемент НЕ с входом установки в О триггера, вход первого разряда входа кода операции устройства соединен через во- . рой элемент НЕ с управляющим входом коммутатора, отличающееся тем, что, с целью расширения области пpимJeнeния за счет блокировки поступления на выход промежуточных результатов вычисления, оно содержит блок элементов И и четвертый элемент И, причем вход первого элемента НЕ соединен с входом установки в 1 триггера, выход первого элемента ИЛИ соединен с вторым входом третьего элемента И, выход второго элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым входом блока элементов И, второй вход и выход которого соединены соответственно с выходом сдвигового регистра и выходом устройства, выходы второго элемента ИЛИ и второго элемента НЕ соединены соответственно с первым и вторым входами четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ.

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ I | 0 |

|

SU378845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1984 |

|

SU1200278A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-31—Подача