Изобретение относится к преобразовательной технике, а именно к классу преобразователей постоянного напряжения в переменное N-ступенчатой формы.

Цель изобретения - повышение надежности преобразователя при формировании переменного напряжения с N }10.

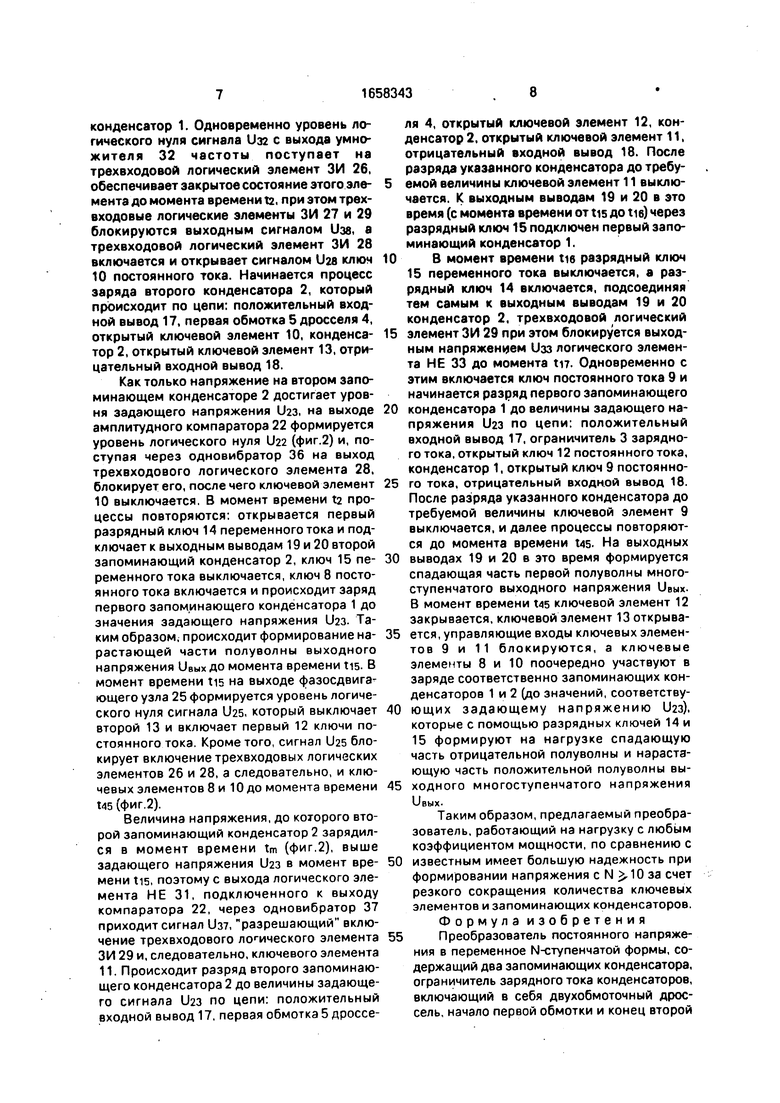

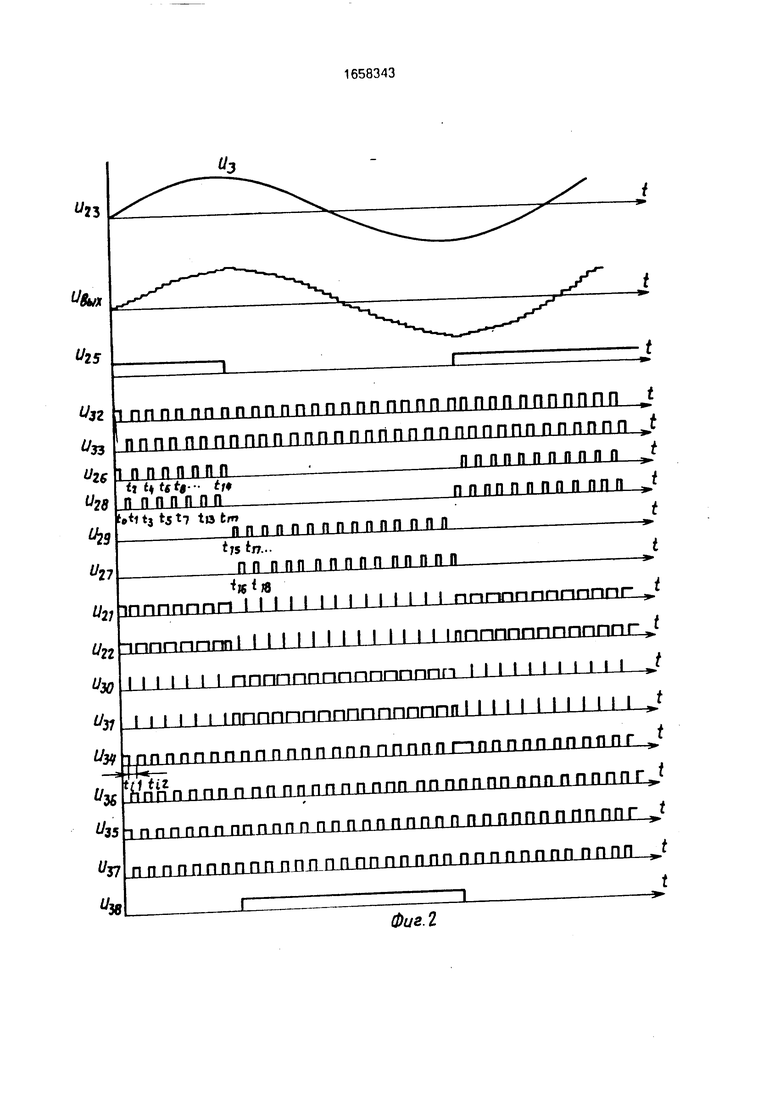

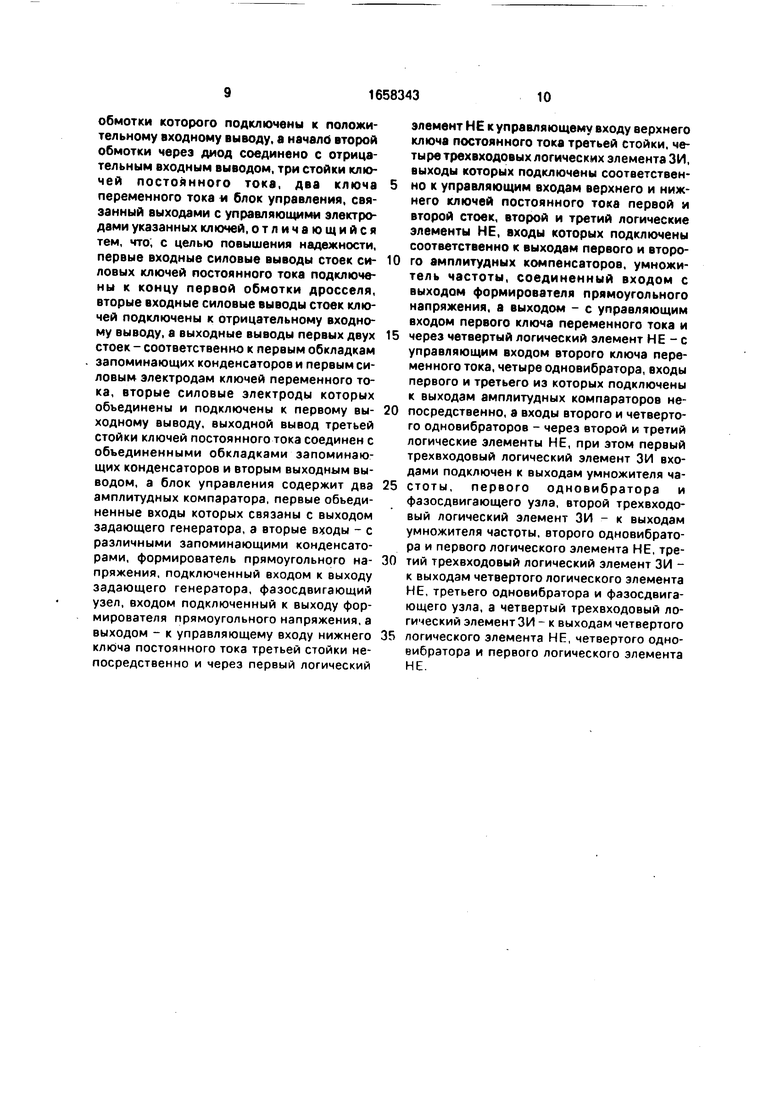

На фиг.1 представлены силовая схема преобразователя и блок управления; на фиг.2 - 3 - диаграммы напряжений на отдельных элементах схемы.

Силовая схема преобразователя содержит два запоминающих конденсатора 1 и 2, ограничитель 3 зарядного тока конденсатора, включающий в себя дроссель 4 с двумя обмотками 5 и б и диод 7(три стойки ключей 8-13 постоянного тока, два ключа 14 и 15 переменного тока и блок 16 управления, при этом первые входные силовые выводы стоек силовых ключей 8-13 постоянного тока подключены к концу первой обмотки 5 дросселя 4 /начало которой соединено с концом второй обмотки 6 и подключено к входному выводу 17, кроме того, начало второй обмотки 6 дросселя 4 соединено с катодом диода 7, анод которого связан с входным выводом 18 и с вторыми входными силовыми выводами стоек силовых ключей постоянного тока.

Выводы первых двух стоек подключены соответственно к первым обкладкам запоминающих конденсаторов 1 и 2 и первым силовым электродам ключей 15 и 14 переменного тока, вторые силовые электроды которых объединены и подключены к выходному выводу 19. Выходной вывод третьей стойки силовых ключей постоянного тока соединен с объединенными обкладками запоминающих конденсаторов 1 и 2 и вторым выходным выводом 20. Блок 16 управления включает в себя два амплитудных компаратора 21 и 22, первые объединенные входы которых соединены с выходом задающего генератора 23, а вторые входы - с различными запоминающими конденсаторами 1 и 2, формирователь 24 прямоугольного напряжения, подключенный входом к рыходу задающего генератора 23, а выходом - к входу фазосдвигающего узла 25, четыре трехвхо- довых логических элемента ЗИ 26-29, два логических элемента НЕ 30 и 31, входы которых подключены соответственно к выходам первого 21 и второго 22 амплитудных компараторов, умножитель 32 частоты, вход которого соединен с выходом формирователя 24 прямоугольного напряжения, а выход - с управляющим входом первого ключа 14 переменного тока и через логический элемент НЕ 33 с управляющим входом второго ключа 15 переменного тока, четыре одновибратора 34-37, входы первого 34 и третьего 36 из которых подключены к выходам амплитудных компараторов 21 и 22 непосредственно, а входы второго 35 и четвертого

37 одновибраторов - через логические элементы НЕ 30 и 31. При этом первый трехвхо- довой логический элемент ЗИ 26 своим входом подключен к выходу умножителя 32 частоты, выходу первого одновибратора 34

0 и выходу фазосдвигающего узла 25, который соединен с управляющим входом второго ключа 13 постоянного тока и через четвертый логический элемент НЕ 38 - с управляющим входом ключа 12 постоянного тока.

5Второй трехвходовой логический элемент И 27 своими входами подключен к выходу умножителя 32 частоты, выходу второго одновибратора 35 и выходу четвертого логического элемента НЕ 38. Входы

0 третьего трехвходового логического элемента ЗИ 28 соединены с выходом третьего логического элемента НЕ 33, с выходом третьего одновибратора 36 и выходом фазосдвигающего узла 25, а входы четвертого

5 трехвходового логического элемента ЗИ 29 соединены с выходом третьего логического элемента НЕ 33, с выходом четвертого одно- вибратора 37 и выходом четвертого логического элемента Н Е 38, выходы трехвходовых

0 логических элементов ЗИ 26-29 подключены к управляющим входам ключей 8-11 постоянного тока соответственно.

На фиг.2 представлены: напряжение U23. формируемое на выходе задающего ге5 нератора 23, выходное напряжение Увых преобразователя, напряжение Das - на выходе фазосдвигающего узла 25. напряжения U32 и 1)зз - на выходах умножителя 32 частоты и логического элемента НЕ 33, напряже0 ния 1)26. U28. U29 и U27 - на выходах первого 26, третьего 28, четвертого 29 и второго 27 трехвходовых логических элементов ЗИ. выходные напряжения U21, U22 амплитудных компараторов 21 и 22, напряжения изо и

5 U31. получаемые на выходах логических элементов НЕ 30 и 31, выходные напряжения 1)34, Use. U35 и Уз соответственно одновибраторов 34, 36,35 и 37 и выходное напряжение U за логического элемента НЕ 38.

0 Преобразователь частоты работает следующим образом.

Задающий синусоидальный (в общем случае любой формы) сигнал U23 (фиг.2) поступает с выхода задающего генератора 23

5 на объединенные неинвертирующие входы амплитудных компараторов 21 и 22, на инвертирующие входы которых подается сигнал с запоминающих конденсаторов 1 и 2. В качестве задающего генератора может выступать и цифроаналоговый преобразователь (ЦАП), на вход которого поступает задающий сигнал в цифровой форме. Результаты сравнения этих сигналов в виде напряжений U21, U22, изо и 11з1 с выходов компараторов 21 и 22 поступают соответст- венно на входы одновибраторов 34 и 36 и через логический элемент НЕ 30 и 31 на входы одновибраторов 35 и 37.

Применение одновибраторов 34-37 в блоке 16 управления необходимо для созда- ния зоны нечувствительности величиной в управляющих сигналах U26-U29, исключающей повторные ложные включения ключевых элементов 8-11, что без применения одновибраторов в условиях действия помех сделать невозможно. Величина tn-ti2 выбирается примерно равной величине tcrti (tcr ti, - длительность полупериода умножителя частоты, определяющая частоту переключения разрядных ключей 14 и 15). Кроме того, задающий синусоидальный сигнал U23 поступает на вход формирователя 24 прямоугольного напряжения, на выходе которого формируется сигнал прямоугольной формы, по частоте и фазе совпадающей с задающим напряжением Uz3. Далее этот сигнал поступает на фазосдвигающий узел 25, где он сдвигается по фазе относительно исходного на 90° и поступает а виде управляющего сигнала U25 на управляющий вход ключа 13 постоянного тока и через логический элемент НЕ 38 на управляющий вход ключа 12 постоянного тока. Управляющие сигналы 11з2 и Узз на ключи 14 и 15 переменного тока поступают соответственно с выхо- да умножителя 32 частоты, вход которого соединен с выходом формирователя 24 прямоугольного напряжения, и с выхода логического элемента НЕ 33, соединенного входом с выходом умножителя 32 частоты.

Частота управляющих импульсов U32 и изз должна быть в 2п раз выше частоты задающего сигнала U23, а величина п определяет количество ступеней в выходном напряжении 1)вых. С выходов одновибраторов 34-37 напряжения поступают на первые входы трехвходовых логических элементов ЗИ 26-29, вторые и третьи входы трехвходового логического элемента 1)26 подключены к выходу умножителя 32 часто- ты и выходу фазосдвигающего устройства 25, трехвходового логического элемента ЗИ 27 - к выходу умножителя 32 частоты и выходу логического элемента НЕ 38, трехвходового логического элемента ЗИ 28 - к выходу логического элемента НЕ 33 и выходу фазосдвигающего устройства 25, а трехвходового логического элемента ЗИ 29 - к выходу логического элемента НЕ 33 и выходу логического элемента НЕ 38. Выходы

трехвходовых логических элементов И 26- 29 соединены с управляющими входами ключей 8-11 постоянного тока.

Формирование импульсов управления для ключевых элементов происходит следующим образом.

В момент времени to первый запоминающий конденсатор 1 заряжен до отрицательного напряжения, величина которого равна первой ступени выходного напряжения Квых, а задающее напряжение больше нуля, следовательно, на выходе амплитудного компаратора 21 формируется сигнал логической единицы Uzi (фиг.2). Этот сигнал U21 через одновибратор поступает на первый вход трехвходового логического элемента ЗИ 26, на второй и третий входы которого поступают разрешающие сигналы Уз2 и U25 с выхода умножителя 32 частоты и выхода фазосдвигающего устройства 25. На выходе первого трехвходового логического элемента ЗИ 26 формируется сигнал логической единицы LJ26, который далее поступает на управляющий вход ключа 8 постоянного тока и открывает его. Постоянное напряжение через ограничитель зарядного тока запоминающих конденсаторов 3 и открытый ключ 8 постоянного тока поступает на вторую обкладку первого конденсатора 1, и конденсатор 1 заряжается по цепи: положительный входной вывод 17, первая обмотка 5 дросселя 4, открытый ключевой элемент 8, конденсатор 1, открытый ключевой элемент 13, отрицательный входной вывод 18. Когда напряжение на конденсаторе 1 достигает величина задающего напряжения U23. на выходе амплитудного компаратора 21 формируется сигнал LJ21 логического нуля (фиг.2), который блокирует трехвходо- вой логический элемент ЗИ 26 и тем самым обеспечивает выключение ключевого элемента 8. Начиная с момента времени t0, трехвходовые логические элементы 28, 27 и 29 блокированы сигналами 11зз и 1)за соответственно с выхода логического элемента НЕ 33 и выхода логического элемента НЕ 38.

При отключении цепи заряда конденсаторов 1 и 2 (в интервале времени, когда транзисторы 8-11 выключены) происходит сброс энергии дросселя 4, входящего в состав ограничителя 3 зарядного тока, в конденсатор входного фильтра по цепи: конец второй обмотки 6 дросселя 4, входная клемма 17, входной фильтр, входная клемма 18, диод 7 и начало обмотки 6 дросселя 4.

В момент времени to происходит переключение разрядных ключей 14 и 15 переменного тока: первый ключ 14 выключается. а второй ключ 15 включается, подключая к выходным выводам 19 и 20 запоминающий

конденсатор 1. Одновременно уровень логического нуля сигнала Uaa с выхода умножителя 32 частоты поступает на трехвходовой логический элемент ЗИ 26, обеспечивает закрытое состояние этого элемента до момента времени tz, при этом трех- входовые логические элементы ЗИ 27 и 29 блокируются выходным сигналом Uae. a трехвходовой логический элемент ЗИ 28 включается и открывает сигналом Uae ключ 10 постоянного тока. Начинается процесс заряда второго конденсатора 2, который происходит по цепи: положительный входной вывод 17, первая обмотка 5 дросселя 4, открытый ключевой элемент 10, конденсатор 2, открытый ключевой элемент 13, отрицательный входной вывод 18,

Как только напряжение на втором запоминающем конденсаторе 2 достигает уровня задающего напряжения LJ23, на выходе амплитудного компаратора 22 формируется уровень логического нуля U22 (фиг.2) и, поступая через одновибратор 36 на выход трехвходового логического элемента 28, блокирует его, после чего ключевой элемент 10 выключается. В момент времени t2 процессы повторяются: открывается первый разрядный ключ 14 переменного тока и подключает к выходным выводам 19 и 20 второй запоминающий конденсатор 2, ключ 15 переменного тока выключается, ключ 8 постоянного тока включается и происходит заряд первого запоминающего конденсатора 1 до значения задающего напряжения U23. Таким образом, происходит формирование нарастающей части полуволны выходного напряжения Увых до момента времени tis. В момент времени ti5 на выходе фазосдвига- ющего узла 25 формируется уровень логического нуля сигнала U25, который выключает второй 13 и включает первый 12 ключи постоянного тока. Кроме того, сигнал U25 блокирует включение трехвходовых логических элементов 26 и 28, а следовательно, и ключевых элементов 8 и 10 до момента времени

t45 (фИГ.2).

Величина напряжения, до которого второй запоминающий конденсатор 2 зарядился в момент времени tm (фиг.2), выше задающего напряжения IJ23 в момент времени tis, поэтому с выхода логического элемента НЕ 31, подключенного к выходу компаратора 22, через одновибратор 37 приходит сигнал Уз, разрешающий включение трехвходового логического элемента ЗИ 29 и, следовательно, ключевого элемента 11. Происходит разряд второго запоминающего конденсатора 2 до величины задающего сигнала U23 по цепи: положительный входной вывод 17, первая обмотка 5 дросселя 4, открытый ключевой элемент 12, конденсатор 2, открытый ключевой элемент 11, отрицательный входной вывод 18. После разряда указанного конденсатора до требуемой величины ключевой элемент 11 выключается. К выходным выводам 19 и 20 в это время (с момента времени от tis до не) через разрядный ключ 15 подключен первый запоминающий конденсатор 1.

0 В момент времени tie разрядный ключ 15 переменного тока выключается, а разрядный ключ 14 включается, подсоединяя тем самым к выходным выводам 19 и 20 конденсатор 2, трехвходовой логический

5 элемент ЗИ 29 при этом блокируется выходным напряжением Узз логического элемента НЕ 33 до момента т. Одновременно с этим включается ключ постоянного тока 9 и начинается разряд первого запоминающего

0 конденсатора 1 до величины задающего напряжения 1)23 по цепи: положительный входной вывод 17, ограничитель 3 зарядного тока, открытый ключ 12 постоянного тока, конденсатор 1, открытый ключ 9 постоянно5 го тока, отрицательный входной вывод 18. После разряда указанного конденсатора до требуемой величины ключевой элемент 9 выключается, и далее процессы повторяются до момента времени . На выходных

0 выводах 19 и 20 в это время формируется спадающая часть первой полуволны многоступенчатого выходного напряжения 1)Вых. В момент времени Мб ключевой элемент 12 закрывается, ключевой элемент 13 открыва5 ется, управляющие входы ключевых элементов 9 и 11 блокируются, а ключевые элементы 8 и 10 поочередно участвуют в заряде соответственно запоминающих конденсаторов 1 и 2 (до значений, соответству0 ющих задающему напряжению U23), которые с помощью разрядных ключей 14 и 15 формируют на нагрузке спадающую часть отрицательной полуволны и нарастающую часть положительной полуволны вы5 ходного многоступенчатого напряжения

UBWX.

Таким образом, предлагаемый преобразователь, работающий на нагрузку с любым коэффициентом мощности, по сравнению с

0 известным имеет большую надежность при

формировании напряжения с N Ј. 10 за счет

резкого сокращения количества ключевых

элементов и запоминающих конденсаторов.

Формула изобретения

5Преобразователь постоянного напряжения в переменное N-ступенчатой формы, содержащий два запоминающих конденсатора, ограничитель зарядного тока конденсаторов, включающий в себя двухобмоточный дроссель, начало первой обмотки и конец второй

обмотки которого подключены к положительному входному выводу, а начали второй обмотки через диод соединено с отрицательным входным выводом, три стойки ключей постоянного тока, два ключа переменного тока и блок управления, связанный выходами с управляющими электродами указанных ключей, отличающийся тем, что, с целью повышения надежности, первые входные силовые выводы стоек силовых ключей постоянного тока подключены к концу первой обмотки дросселя, вторые входные силовые выводы стоек ключей подключены к отрицательному входному выводу, а выходные выводы первых двух стоек - соответственно к первым обкладкам запоминающих конденсаторов и первым силовым электродам ключей переменного тока, вторые силовые электроды которых объединены и подключены к первому выходному выводу, выходной вывод третьей стойки ключей постоянного тока соединен с объединенными обкладками запоминающих конденсаторов и вторым выходным выводом, а блок управления содержит два амплитудных компаратора, первые объединенные входы которых связаны с выходом задающего генератора, а вторые входы - с различными запоминающими конденсаторами, формирователь прямоугольного напряжения, подключенный входом к выходу задающего генератора, фазосдвигающий узел, входом подключенный к выходу формирователя прямоугольного напряжения, а выходом - к управляющему входу нижнего ключа постоянного тока третьей стойки непосредственно и через первый логический

элемент НЕ к управляющему входу верхнего ключа постоянного тока третьей стойки, четыре трехвходовых логических элемента ЗИ, выходы которых подключены соответственно к управляющим входам верхнего и нижнего ключей постоянного тока первой и второй стоек, второй и третий логические элементы НЕ, входы которых подключены соответственно к выходам первого и второго амплитудных компенсаторов, умножитель частоты, соединенный входом с выходом формирователя прямоугольного напряжения, а выходом - с управляющим входом первого ключа переменного тока и

через четвертый логический элемент НЕ - с управляющим входом второго ключа переменного тока, четыре одновибратора, входы первого и третьего из которых подключены к выходам амплитудных компараторов непосредственно, а входы второго и четвертого одновибраторов - через второй и третий логические элементы НЕ, при этом первый трехвходовый логический элемент ЗИ входами подключен к выходам умножителя частоты, первого одновибратора и фазосдвигающего узла, второй трехвходовый логический элемент ЗИ - к выходам умножителя частоты, второго одновибратора и первого логического элемента НЕ, третий трехвходовый логический элемент ЗИ - к выходам четвертого логического элемента НЕ, третьего одновибратора и фазосдвигающего узла, а четвертый трехвходовый логический элемент ЗИ - к выходам четвертого

логического элемента НЕ, четвертого одно- вибратора и первого логического элемента НЕ.

UH

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты | 1984 |

|

SU1205240A1 |

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| Преобразователь частоты | 1986 |

|

SU1403287A2 |

| Однофазный преобразователь частоты | 1987 |

|

SU1800569A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

| Устройство для контроля качества электрической изоляции | 1990 |

|

SU1749845A1 |

| Устройство пуска и управления трансформаторно-ключевого преобразователя | 1991 |

|

SU1775821A1 |

| Импульсный стабилизатор переменного напряжения | 1987 |

|

SU1511739A1 |

| Однофазный преобразователь частоты | 1985 |

|

SU1422329A1 |

| Преобразователь переменного напряжения в постоянное | 1985 |

|

SU1270849A1 |

Изобретение относится к преобразовательной технике. Его целью является повышение надежности преобразования при формировании N-ступенчатого напряжения с N , 10. Преобразователь содержит три стойки ключей 8-13 постоянного тока, запоминающие конденсаторы 1 и 2, ключи 14 и 15 переменного тока и блок 16 управления. Формирование ступеней выходного напряжения осуществляют благодаря предварительному заряду конденсаторов до соответствующего напряжения, а приближение формы выходного напряжения к синусоидальной благодаря использованию принципа слежения за задающим синусоидальным сигналом. 3 ил. ё Os сл 00 CJ Јь 00

Л/д

25

Чп и

1ППППППППППППППППППППППППППППППППП t

ПППППППППППППППППППППППППППППППППП J

foyhnnnnnnn

.. , i U28 П П П П П П П

t517 to tm

nnnnnnnnnnnnnnn

in tn... ПП ППП ППППП RILD П П

и

w

1ППППППП I I I I I I I I I I I I I I ПППППППППППГ t

1ППППППП1 I I I I I I I i I I I I I 1ППППППППППППГ

%

37

%

I I I I I 1 I nnnnnnnnnnnnnnn 1 I I I I I I I I i I J

i I I I I t 1ПППППППППППППППП 1 I i I I 1 1 I I I I I

№

ПППППППППППП ПППППППППППППППППЛПГ

t

и3Ј35

37

зв

Ьпп n ппп п ппп пппппппп пппппппппппппппг

Т ПППППППППППППППППППППП ПППППППППППГ

пппппппппппппппппппппппппппппп пппп жЈ

,t

X

S s

ППППППППППП

t

ПППППППППППП J

t

t

t

Фиг. 2

.;

Фиг.З

| Инвертор | 1977 |

|

SU653705A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Инвертор с -ступенчатым выводным напряжением | 1978 |

|

SU748744A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Статический преобразователь с @ -ступенчатой формой выходного напряжения (его варианты) | 1983 |

|

SU1171940A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-06-23—Публикация

1988-01-07—Подача