Изобретение относится к электротех нике, в частности к статическим преобразователям переменного напряжения одной частоты в переменное напряжение другой частоты.

Целью изобретения является повышение надежности и улучшение массогаба- ритных показателей путем упрощения силовой части, уменьшения количества запоминающих конденсаторов и уменьшения искажения формы выходного напряжения,

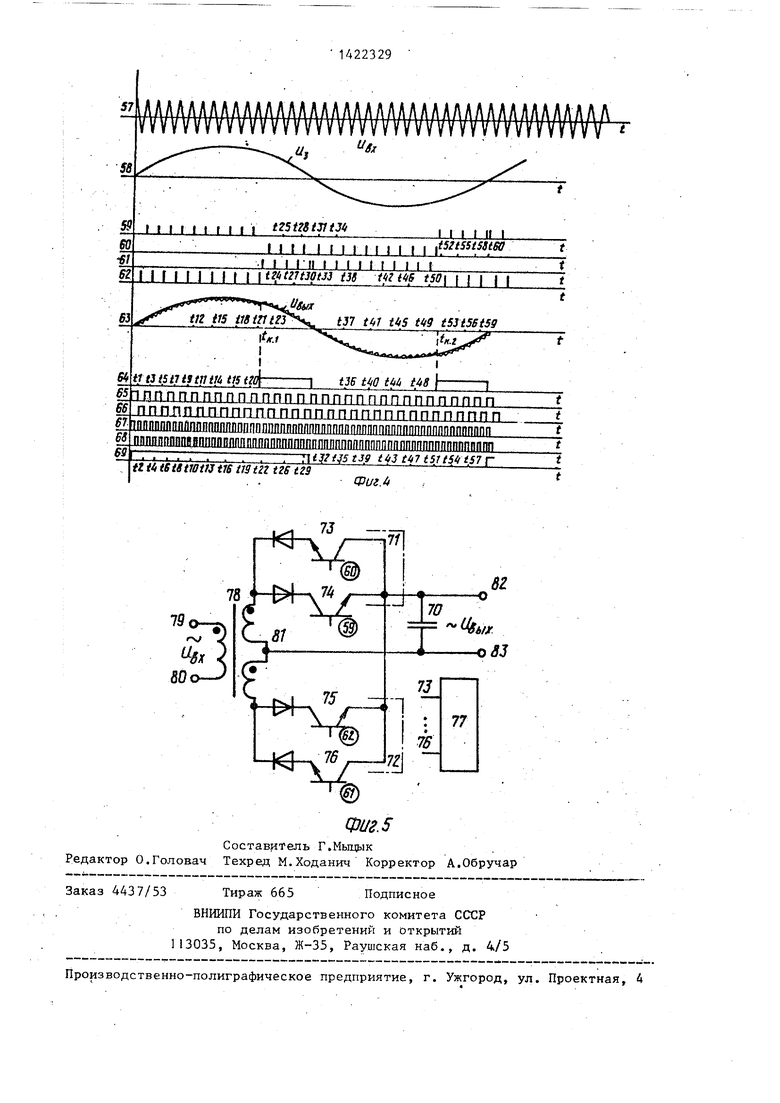

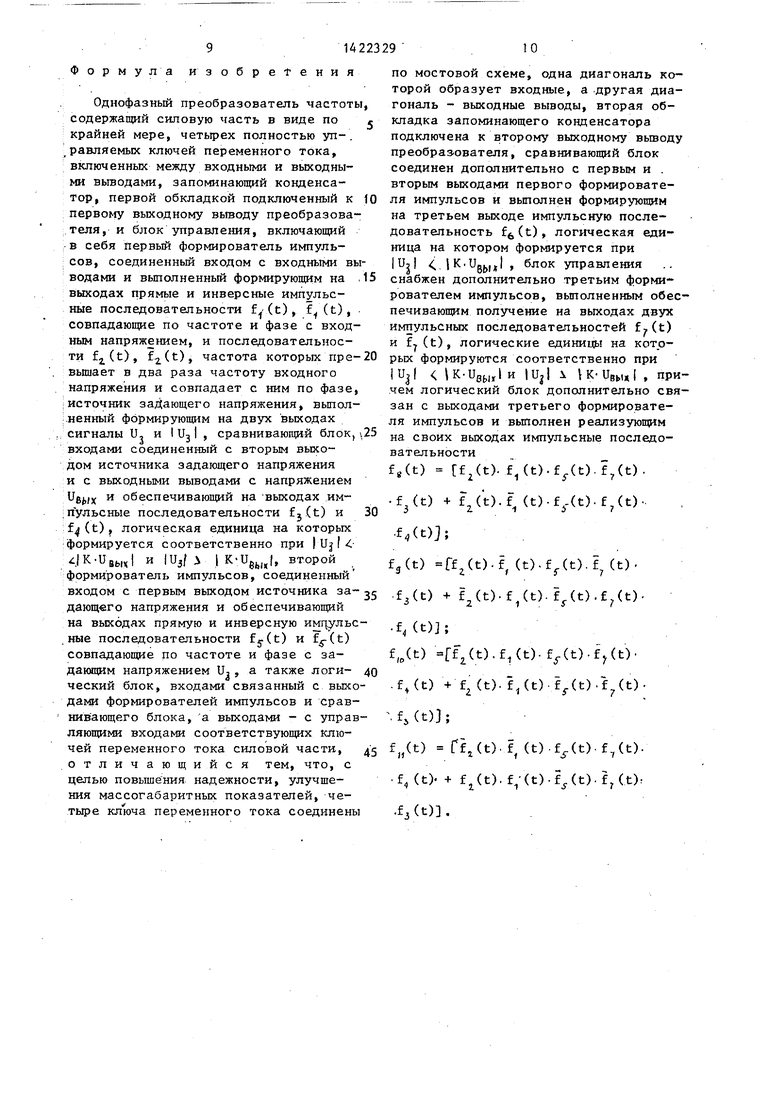

На фиг. 1 представлена мостовая схема преобразователя частоты на фиг. 2 - блок упра.вления; на фиг. 3 - схема сравнивающего устройства; на фиг. 4 - диаграммы напряжений на от- дел-ьных элементах схемы, на фиг. 5 - нулевая схема преобразователя часто-

:ТЫ..

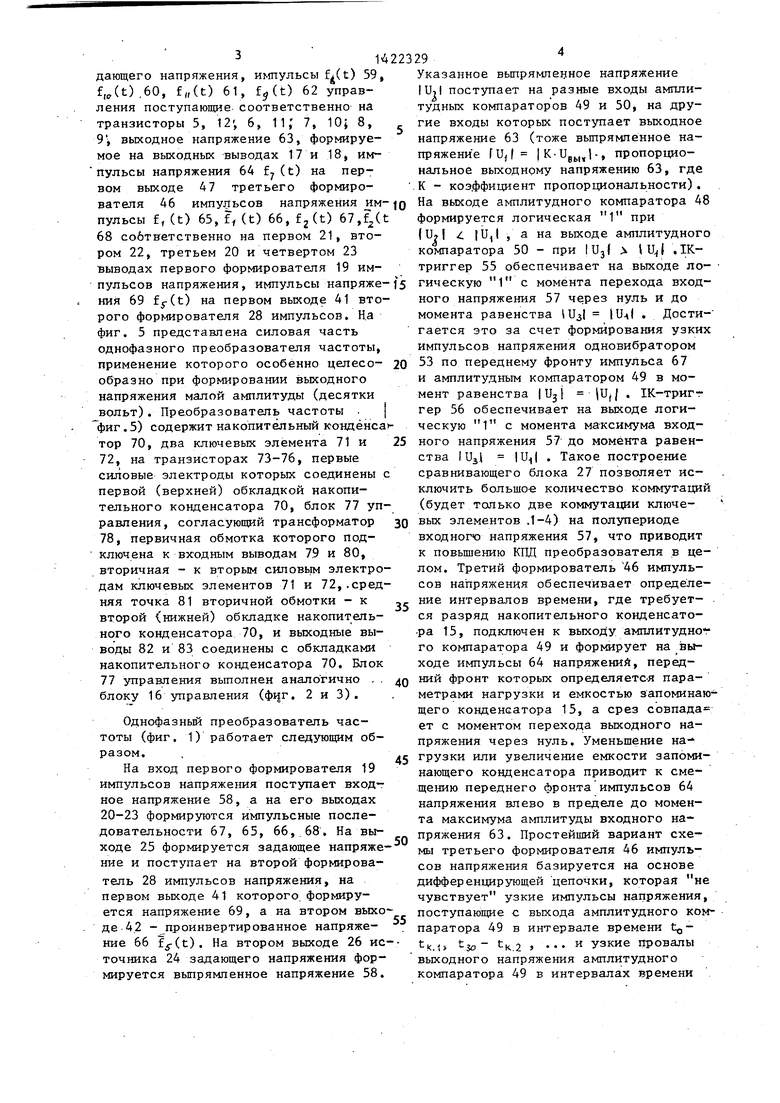

Однофазный преобразователь частоты содержит, силовую.часть, выполненную по мостовой схеме на ключах 1-4 переменного тока, на основе транзисторов 5-12, которые соединены с входными выводами 13 и 14, запо минающий конденсатор 15 на выходе, блок 16 управления и выходные выводы 17 и 18. Блок управления (фиг. 2) включает в себя первый 19 формирователь импульсов с выходами 20-23, соединенный входом с входными вьгеодами 13 и 14, источник 24 задающего напряжения, на двух выходных выводах 25 и 26 кото- рого формируются сигналы U, и (U 1 сравнивающий блок 27, соединенный входами с вторым вьшодом 26 источника 24 задающего напряжения, выходными вьшодами 17 и 18 с напряжением Uftwx второй формирователь 28 им- .пульсов, соединенный входом с первым выходом 25 источника 24 задающего напряжения, и логический блок, включающий в себя четыре двухвходовых ло- гических элемента ИЛИ 29-32 я восемь пятивходовых логических элементов И 33-40, и входами связанный с выхода-: ми 20-23 и 41-44 формирователей импульсов и сравнивающего блока, а вы- ходами - с управляющими входами соответствующих ключей переменного тока силовой части, причем сравнивающий блок 27 соединен дополнительно с первым 21 и вторым 22 выходами первого формирователя и имеет дополнительньш выход 45,

Блок управления снабжен дополнительно третьим формирователем 46 импульсов с выходами 47 и 48, которые соединены с входами- логического блока (пятивходовыми; логическими элементами И 33-40).

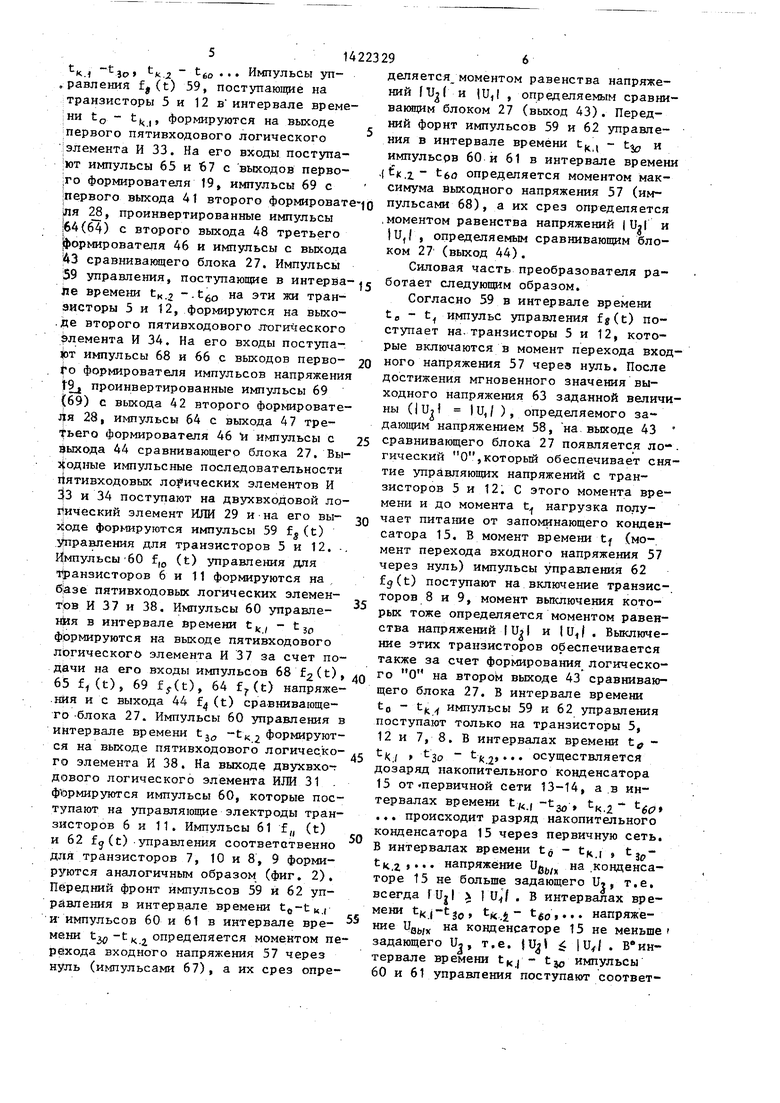

Сравнивающий (фиг. 3) содержит амплитудные компараторы 49 и 50, входы которых связаны с источником 24 задающего напряжения и выходными вьгаодами 17 и 18 ч ерез выпрямит тель 51 и согласующий трансформатор 52, одновибраторы 53 и 54, входы которых соединены с первыми 21 и вторым 22 выходами первого формирователя 19 импульсов напряжения, два IK- триггера. 55 и 56, входы С которых соединены с положительной клеммой питания, входы 1-е выходами одновиб- раторов 53 и 54, входы К - с выходами амплитудных компараторов 49 и 50, а их выходы являются выходными клеммами 43-45 сравнивающего блока, на которых формируются импульсные последовательности Гз(ь), f(t), 5(1)

Функциональная характеристика логического блока, а также внутренние его связи между логическими элементами (внешние - с узлами блока управления) определяются следующими логическими выражениями:

f,(t) rf2(t).f/(t).f(t).f,(t). -fj(t) + f(t)-f (t).f(t).f, (t).

f(t) rfi(t).f(t).f.(t).f7(t).

.f(t) + f2(t).f (t):f(t). f(t).

€4 (t)J ;

f,o(t) rf2(t),f(t). f(t). f(t).

.f(t) + f2(t).f(t).f(t).f(t).

f3(t)J;

f,(t) f(t).f(t). f,,(t).f(t).

.(0 + f(t).f(t).f(t).f(t).

.

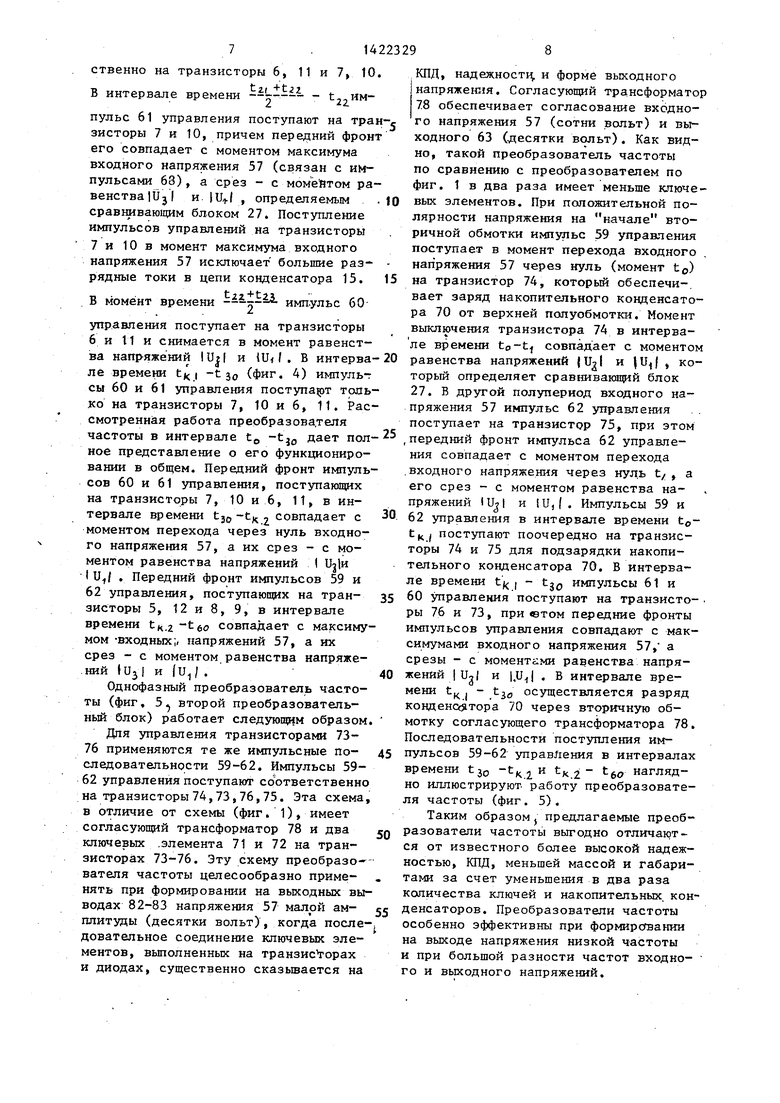

Ha фиг. 4 представлено входное напряжение 57, подаваемое на входные выводы 13 и 14, задакяцее напряжение и 58 на выходе 25 источника 24 задающего напряжения, иьтульсы f(t) 59, Указанное выпрямленное напряжение f,,(t),60, f,,(t) 61, f(t) 62 управIU, I поступает на разные входы ампл тудных компараторов 49 и 50, на др гие входы которых поступает выходн напряжение 63 (тоже вьшрямпенное н пр яжени е fU, ( |K-Uj,l-, пропорцио нальное выходному напряжению 63, г .К - коэффициент пропорциональности На выходе a fflлитyднoгo компаратора формируется логическая 1 при I и. I |U,I , а на выходе амплитудн компаратора 50 - при lUjf .I триггер 55 обеспечивает на выходе

ления поступающие соответственно на транзисторы 5, 12; 6, 11, 7, 10} 8, 9 j выходное напряжение 63, формируемое на выходных выводах 17 и 18, импульсы напряжения 64 fy(t) на первом выходе 47 третьего формирователя 46 импульсов напряжения импульсы f, (t) 65,f|(t) 66,f2(t) 67,f.,(t 68 собтнетственно на первом 21, втором 22, третьем 20 и четвертом 23 выводах первого формирователя 19 им Указанное выпрямленное напряжение

IU, I поступает на разные входы амплитудных компараторов 49 и 50, на другие входы которых поступает выходное напряжение 63 (тоже вьшрямпенное напр яжени е fU, ( |K-Uj,l-, пропорциональное выходному напряжению 63, где .К - коэффициент пропорциональности). На выходе a fflлитyднoгo компаратора 48 формируется логическая 1 при I и. I |U,I , а на выходе амплитудного компаратора 50 - при lUjf .IK- триггер 55 обеспечивает на выходе ло

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты | 1984 |

|

SU1205240A1 |

| Преобразователь частоты | 1986 |

|

SU1403287A2 |

| Однофазный преобразователь частоты | 1987 |

|

SU1800569A1 |

| Способ измерения амплитудных значений электрических сигналов | 1986 |

|

SU1509751A1 |

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| ДИСКРИМИНАТОР ФОРМЫ ИМПУЛЬСОВ ОРГАНИЧЕСКОГО СЦИНТИЛЛЯЦИОННОГО ДЕТЕКТОРА | 1991 |

|

SU1829650A1 |

| Преобразователь частоты | 1982 |

|

SU1092680A1 |

| Преобразователь переменного напряжения в постоянное | 1982 |

|

SU1171932A1 |

| Устройство для измерения временных интервалов | 1985 |

|

SU1293692A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

Изобретение относится к преобразовательной технике. Целью является повышение надежности и улучшение мас- согабаритных показателей. Устр-во содержит мост на ключах 1-4 переменного тока, выполненный на транзисторах 5- 12. На выходе включен запоминающий . конденсатор 1.5. Для управления транзисторами 5-12 используются импульсные последовательности, формируемые .. блоком управления 16 в соответствии с определенными логическими вьфажения- ми. 5 ил. (Л

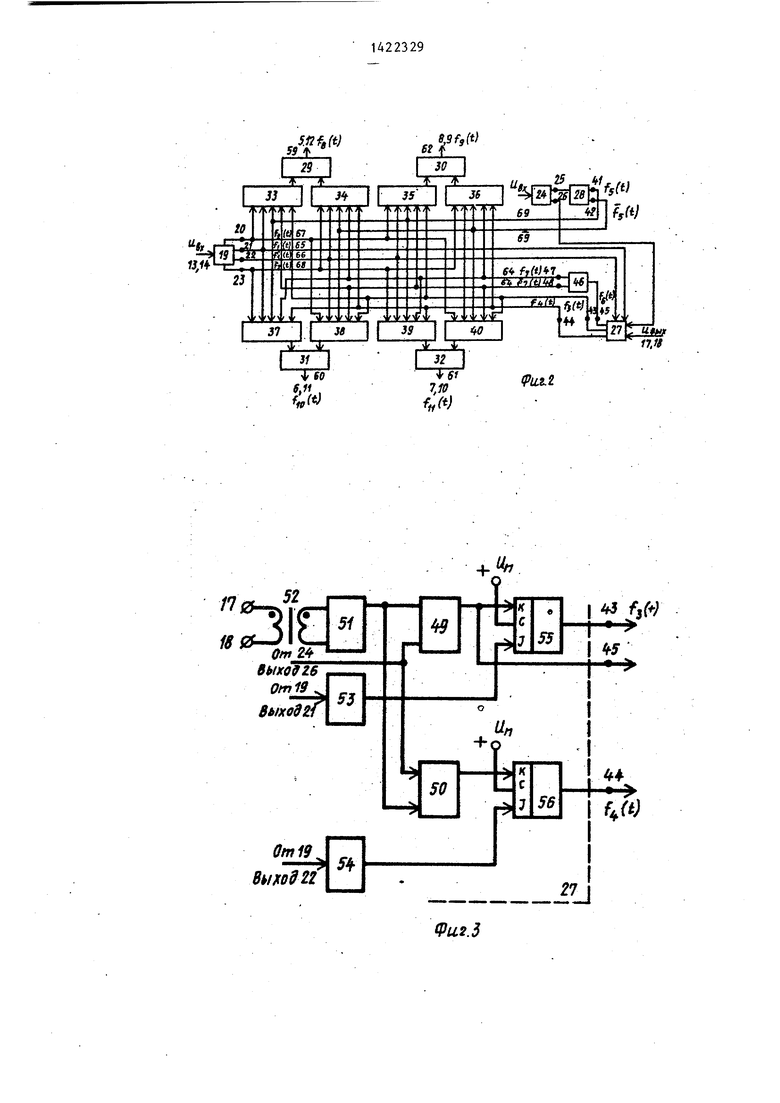

пульсов напряжения, импульсы напряже-{5 гическую 1 с момента перехода вход- ния 69 ) на первом вькоде 41 второго формирователя 28 импульсов. Н.а фиг. 5 представлена силовая часть однофазного преобразователя частоты, применение которого особенно целесо- 20 образно при формировании выходного напряжения малой амплитуды (десятки вольт). Преобразователь частоты . | фиг,5) содержит накопительный конденсат- тор 70, два ключевых элемента 71 и 25 72, на транзисторах 73-76, первые силовые электроды которых соединены с первой (верхней) обкладкой накопительного конденсатора 70, блок 77 управления, согласующий трансформатор ЗО 78, первичная обмотка которого подключена к входным выводам 79 и 80, вторичная - к вторым силовьм электродам ключевых элементов 71 и 72,.средняя точка 81 вторичной обмотки - к , второй (нижней) обкладке накопительного конденсатора 70, и выходные выводы 82 и 83 соединены с обкладками накопительного конденсатора 70. Блок 77 управления выполнен аналогично . . Q блоку 16 управления (фиг. 2 и 3).

ного напряжения 57 через нуль и до момента равенства . Дости- гается это за счет формирования узких импульсов напряжения одновибратором 53 по переднему фронту импульса 67 и амплитудным компаратором 49 в момент равенства |U ( ( . IK-тригг rep 56 обеспечивает на выходе логическую 1 с момента максимума входного напряжения 57 до момента равенства . Такое построение сравнивающего блока 27 позволяет исключить большо-е количество коммутаций (будет только две коммутации ключевых элементов .1-4) на полупериоде входного напряжения 57, что приводит к повышению КПД преобразователя в целом. Третий формирователь 46 импульсов напряжения обеспечивает определение интервалов времени, где требует- ся разряд накопительного конденсато- ра 15, подключен к выходу амплитудно го компаратора 49 и формирует на выходе импульсы 64 напряжений, передний фронт которых определяется параметрами нагрузки и емкостью запоминающего конденсатора 15, а срез совпада ет с моментом перехода выходного напряжения через нуль. Уменьщение на- грузки или увеличение емкости запоминающего конденсатора приводит к смещению переднего фронта импульсов 64 напряжения влево в пределе до момента максимума амплитуды входного напряжения 63. Простейший вариант схеОднофазньй преобразователь частоты (фиг. 1) работает следующим образом.

На вход первого формирователя 19 импульсов напряже1шя поступает входное напряжение 58, а на его выходах 20-23 формируются импульсные последовательности 67, 65, 66,,68. На вы45

ного напряжения 57 через нуль и до момента равенства . Дости гается это за счет формирования узки импульсов напряжения одновибратором 53 по переднему фронту импульса 67 и амплитудным компаратором 49 в момент равенства |U ( ( . IK-тригг rep 56 обеспечивает на выходе логическую 1 с момента максимума входного напряжения 57 до момента равенства . Такое построение сравнивающего блока 27 позволяет исключить большо-е количество коммутаци (будет только две коммутации ключевых элементов .1-4) на полупериоде входного напряжения 57, что приводит к повышению КПД преобразователя в це лом. Третий формирователь 46 импульсов напряжения обеспечивает определе ние интервалов времени, где требует- ся разряд накопительного конденсато- ра 15, подключен к выходу амплитудно го компаратора 49 и формирует на выходе импульсы 64 напряжений, передний фронт которых определяется параметрами нагрузки и емкостью запомина щего конденсатора 15, а срез совпада ет с моментом перехода выходного напряжения через нуль. Уменьщение на- грузки или увеличение емкости запоми нающего конденсатора приводит к смещению переднего фронта импульсов 64 напряжения влево в пределе до момента максимума амплитуды входного напряжения 63. Простейший вариант схе д-л Х1рЛЛЧЧ:;пг1Л U-J. ilpui- 1 CiHUUlJKl ± cll nclt1i WA.C -

ходе 25 формируется задающее напряже- „ь третьего формирователя 46 импульние и поступает на второй формирователь 28 импульсов напряжения, на первом выходе 41 которого формируется напряжение 69, а на втором выхо де 4.2 - проинвертированное напряжение 66 f(t). На втором выходе 26 ис-- точника 24 задающего напряжения формируется выпрямпенное напряжение 58.

сов напряжения базируется на основе дифференцирующей цепочки, которая не чувствует узкие импульсы напряжения поступающие с выхода амплитудного ком паратора 49 в интервале времени t,-

30

- t

к.2

и узкие провалы

выходного напряжения амплитудного компаратора 49 в интервалах времени

гическую 1 с момента перехода вход-

ного напряжения 57 через нуль и до момента равенства . Дости- гается это за счет формирования узких импульсов напряжения одновибратором 53 по переднему фронту импульса 67 и амплитудным компаратором 49 в момент равенства |U ( ( . IK-тригг rep 56 обеспечивает на выходе логическую 1 с момента максимума входного напряжения 57 до момента равенства . Такое построение сравнивающего блока 27 позволяет исключить большо-е количество коммутаций (будет только две коммутации ключевых элементов .1-4) на полупериоде входного напряжения 57, что приводит к повышению КПД преобразователя в целом. Третий формирователь 46 импульсов напряжения обеспечивает определение интервалов времени, где требует- ся разряд накопительного конденсато- ра 15, подключен к выходу амплитудно го компаратора 49 и формирует на выходе импульсы 64 напряжений, передний фронт которых определяется параметрами нагрузки и емкостью запоминающего конденсатора 15, а срез совпада ет с моментом перехода выходного напряжения через нуль. Уменьщение на- грузки или увеличение емкости запоминающего конденсатора приводит к смещению переднего фронта импульсов 64 напряжения влево в пределе до момента максимума амплитуды входного напряжения 63. Простейший вариант схеХ1рЛЛЧЧ:;пг1Л U-J. ilpui- 1 CiHUUlJKl ± cll nclt1i WA.C -

„ь третьего формирователя 46 импульсов напряжения базируется на основе дифференцирующей цепочки, которая не чувствует узкие импульсы напряжения, поступающие с выхода амплитудного компаратора 49 в интервале времени t,-

30

- t

к.2

и узкие провалы

выходного напряжения амплитудного компаратора 49 в интервалах времени

514223296

-к. -}о к.2 60 Импульсы уп-деляется моментом равенства напряже, равления f (t) 59, поступающие наний (11}( и |U,| , определяемым сравнитранзисторы 5 и 12 в интервале време- вакицим блоком 27 (выход 43). Перед:НИ to - tj,, формируются на выходе

первого пятивходового логического

(элемента И 33. На его входы поступа|ют импульсы 65 и 67 с выходов первоний форнт импульсов 59 и 62 управле;го формирователя 19, импульсы 69 с

ния в интервале времени t , - tj и импульсов 60 и 61 в интервале времени («.2. 60 определяется моментом максимума выходного напряжения 57 (им- jnepBoro выхода 41 второго формировате- о пульсами 68), а их срез определяется 1пя 28, проинвертированные импульсы.моментом равенства напряжений 11Ь1 и

|64(64) с второго выхода 48 третьегоtU,l , определяемым сравнивающим бло|формирователя 46 и импульсы с выходаком 27 (выход 44).

143 сравнивающего блока 27. ИмпульсыСиловая часть преобразователя ра59 управления, поступающие в интерва- с ботает следующим образом. йе времени t. f тран-Согласно 59 в интервале времени

эисторы 5 и 12, формируются на выхо-te - t импульс управления fj(t) по.де второго пятивходового л-огическогоступает на. транзисторы 5 и 12, кото лемента И 34. На его входы поступа-рые включаются в момент перехода входит импульсы 68 и 66 с выходов перво- 20 ного напряжения 57 черев нуль. После to формирователя импульсов напряжения достижения мгновенного значения вы- t9j проинвертированные импульсы 69ходного напряжения 63 заданной величи 69) с выхода 42 второго формировате- ны ( IU, / ), определяемого за- 4я 28, и fflyльcы 64 с выхода 47 тре-дающим напряжением 58, на. выходе 43

Тьего формирователя 46 in импульсы с 25 сравнивающего блока 27 появляется ло-. дыхода 44 сравнивающего блока 27. Вы- гический О,который обеспечивает сня- з одные импульсные последовательноститие управляющих напряжений с транпятивходовых логических элементов Изисторов 5 и 12. С этого момента вре33 и 34 поступают на двухвходовой ло- мени и до момента t нагрузка полу- Гический элемент ИЛИ 29 и-на его вы- о чает питание от запоминающего конден- 4оде формируются импульсы 59 fj (t)сатора 15. В момент времени tf (мо-.

5 |правления для транзисторов 5 и 12. . Импульсы 60 ,0 (t) управления для тфанзисторов 6 и 11 формируются на б1азе пятивходовых логических элемен- тЬв И 37 и 38. Импульсы 60 управле- Шя в интервале времени t, - tj формируются на выходе пятивходового логическогб элемента И 37 за счет подачи на его входы импульсов 68 f2(t), л 65 f(t), 69 fj-(t), 64 fj(t ) напряже- .нИя и с выхода 44 f (t) сравнивающего -блока 27. Импульсы 60 управления в интервале времени tj -t 2 ся на выходе пятивходового логичес.ко- , го элемента И 38. На выходе двухвхо-г дового логического элемента ИЛИ 31 . формируются импульсы 60, которые поступают на управляющие электроды транзисторов 6 и 11. Импульсы 61 „ (t)

35

мент перехода входного напряжения 57 через нуль) импульсы управления 62 fg(t) поступают на включение транзис-. торов 8 и 9, момент выключения которых тоже определяется моментом равенства напряжений I U} I и . Выключение этих транзисторов обеспечивается также за счет формирования логического О на втором выходе 43 сравнивающего блока 27. В интервале времени to - tjj; импульсы 59 и 62 управления поступают только на транзисторы 5, 12 и 7, 8. В интервалах времени t .l 30

- t

К.2

осуществляется

и 62 f(t) управления соответственно для транзисторов 7, 10 и 8, 9 формируются аналогичным образом (фиг, 2). Передний фронт импульсов 59 и 62 управления в интервале времени t,-tK.(

50

дозаряд накопительного конденсатора 15 от«первичной сети 13-14, а .в интервалах времени tgjj , n.Z 6ff ,.. происходит разряд накопительного конденсатора 15 через первичную сеть. В интервалах времени t - t , , зо к.,г напряжение Ugj на .конденсаторе 15 не больше задающего U, т.е. всегда , В интервалах времени t«(-t3(,, t j - ,... напряже -- - - -«.---,-ы- .1

и-импульсов 60 и 61 в интервале вре- ние Ug на конденсаторе 15 не меньше

мени определяется моментом пе-задающего U,, т.е. jUjt . В инрехода входного напряжения 57 черезтервале времени - tj, импульсы

нуль (импульсами 67), а их срез опре-60 и 61 управления поступают соответний форнт импульсов 59 и 62 управлемени и до момента t нагрузка полу- чает питание от запоминающего конден- сатора 15. В момент времени tf (мо-.

мент перехода входного напряжения 57 через нуль) импульсы управления 62 fg(t) поступают на включение транзис-. торов 8 и 9, момент выключения которых тоже определяется моментом равенства напряжений I U} I и . Выключение этих транзисторов обеспечивается также за счет формирования логического О на втором выходе 43 сравнивающего блока 27. В интервале времени to - tjj; импульсы 59 и 62 управления поступают только на транзисторы 5, 12 и 7, 8. В интервалах времени t

K.l 30

- t

К.2

осуществляется

дозаряд накопительного конденсатора 15 от«первичной сети 13-14, а .в интервалах времени tgjj , n.Z 6ff ,.. происходит разряд накопительного конденсатора 15 через первичную сеть. В интервалах времени t - t , , зо к.,г напряжение Ugj на .конденсаторе 15 не больше задающего U, т.е. всегда , В интервалах времени t«(-t3(,, t j - ,... напряже

ние Ug на конденсаторе 15 не меньше

ственно на транзисторы 6, 11 и 7, 10.

ti, +tiz

2

В интервале времени

- t HMпульс 61 управления поступают на тран-с зисторы 7 и 10, причем фронт его совпадает с моментом максимума входного напряжения 57 (связан с импульсами 63), а срез - с момейтом равенства |Ujl и. |Ut( , определяемым . Ю сравшвающим блоком 27. Поступление импульсов управлений на транзисторы 7 и 10 в момент максимума входного напряжения 57 исключает большие раз- - рядные токи в цепи конденсатора 15. 15

В момент времени

ti2.it2i

импульс 60упр.авления поступает на транзисторы 6 и 11 и снимается в момент равенства напр яжёний lUjI и iU I . В интервага,

ле времени -t30 (Фиг. 4) импульт сы 60 и 61 управления поступает только на транзисторы 7, 10 и 6, 11. Рассмотренная работа преобразователя частоты в интервале tj, -tj дает полное представление о его функционировании в общем. Передний фронт импульсов 60 и 61 управления, поступающих на транзисторы 7, 10 и 6, 11, в интервале времени tjj,-t , совпадает с моментом перехода через нуль входного напряжения 57, а их срез - с моментом равенства напряжений I I . Передний фронт импульсов 59 и 62 управления, поступающих на тран- зисторы 5, 12и8, 9, в интервале времени tK.z бо совпадает с максимумом -входных;, напряжений 57, а их срез - с моментом равенства напряже- .ний и (.

Однофазный преобразователь частоты (фиг, 5 второй преобразователь- ньй блок) работает следующим образом.

Для управления транзисторами 73- 76 применяются те же импульсные по- следовательности 59-62. Импульсы 59- 62 управления поступают соЪтветственно на транзисторы 74, 73, 76, 75. Эта схема, в отличие от схемы (фиг. 1), имеет согласующий трансформатор 78 и два ключевых .элемента 71 и 72 на транзисторах 73-76. Эту схему преобразователя частоты целесообразно применять при формировании на выходных выводах 82-83 напряжения 57 малой ам- штитуды (десятки вольт), когда последовательное соединение ключевых зле- ментов, выполненных на транзисторах и диодах, существенно сказьшается на

КПД, надежностц. и форме выходного напряжеш1я. Согласующий трансформато 78 обеспечивает согласование входного напряжения 57 (сотни вольт) и ходного 63 (десятки вольт). Как видно, такой преобразователь частоты по сравнению с преобразователем по фиг. 1 в два раза имеет меньше ключевых элементов. При положительной полярности напряжения на начале вторичной обмотки импульс 59 управления поступает в момент перехода входного напряжения 57 через нуль (момент tjj) на транзистор 74, который обеспечи-. вает заряд накопительного конденсатора 70 от верхней полуобмоткн. Момент выключения транзистора 74 в интерва- ле времени to-t совпадает с моментом равенства напряжений и |U( , который определяет сравнивакщнй блок 27. В другой полупериод входного напряжения 57 импульс 62 управления . поступает на транзистор 75, при этом ,передний фронт импульса 62 управления совпадает с моментом перехода .входного напряжения через нуль t/, а его срез - с моментом равенства напряжений lUjI и iU, ( . Импульсы 59 и 62 управления в интервале времени to- поступают поочередно на транзисторы 74 и 75 для подзарядки накопительного конденсатора 70. В интервале времени tj | - tj импульсы 61 и 60 управления поступают на транзисторы 76 и 73, при «том передние фронты импульсов управления совпадают с максимумами входного напряжения 57, а срезы - с моментами равенства напряжений I U-jl и I.U.,1 . В интервале времени tj . - осуществляется разряд конденсатора 70 через вторичную обмотку согласующего трансформатора 78. Последовательности поступления импульсов 59-62 управления в интервалах времени tj . бо наглядно иллюстрируют, работу преобразователя частоты (фиг. 5).

Таким образомJ предлагаемые преобразователи частоты выгодно отличаются от известного более высокой надежностью, КПД, меньшей массой и габаритами за счет уменьшения в два раза количества ключей и накопительных, конденсаторов. Преобразователи частоты особенно эффективны при формирсгвании на выходе напряжения низкой частоты и при большой разности частот входно- го и выходного напряжений.

Формула изобретения

Однофазный преобразователь частоты, содержащий силовую часть в виде по , крайней мере, четырех полностью уп-. равляемых ключей переменного тока, включенных между входными и выходными вьгаодами, запоминающий конденсатор, первой обкладкой подключенный к Ю первому выходному вьшоду преобразователя, и блок управления, включающий в себя первый формирователь импульсов, соединенный входом с входными выводами и выполненный формирующим на .15 выходах прямые и инверсные импульсные последовательности f(t), f|(t), совпадающие по частоте и фазе с входным напряжением, и последовательности

), ), частота которых пр е-20

вьпиает в два раза частоту входного напряжения и совпадает с ним по фазе, источник задающего напряжения, вьшол- .ненный формирующим на двух выходах сигналы Uj и I Uj I , сравнивающий блок, 25 входами соединенный с вторым выходом источника задающего напряжения и с выходными выводами с напряжением UBMX обеспечивающий на -выходах импульсные последовательности г,() и 30 f(t), логическая единица на которых формируется соответственно при UjI4 JK-UBb,, и Шз/ i I K-Ug,J, второй формирователь импульсов, соединенный входом с первым выходом источника за- дающего напряжения и обеспечивающий на выходах прямую и инверсную имг ульс- ные последовательности fyCt) и f(t) совпадающие по частоте и фазе с за- даннцим напряжением U, , а также логи- 40 ческий блок, входами связанный с выходами формирователей импульсов и сравнивающего блока, а выходами - с управляющими входами соответствующих ключей переменного тока силовой части, д д отличающийся тем, что, с целью повьппения надежности, улучшения массогабаритных показателей, четыре ключа переменного тока соединены

по мостовой схеме, одна диагональ которой образует входные, а другая диагональ - выходные выводы, вторая обкладка запоминающего конденсатора подключена к второму выходному вьшоду преобраз.ователя, сравнивающий блок соединен дополнительно с первым и . вторым выходами первого формирователя импульсов и выполнен формирующим на третьем выходе импульсную последовательность f(t), логическая единица на котором формируется при I Uj I I К. Ugu,,I , блок управления снабжен дополнительно третьим формирователем импульсов, выполненным обес печиваю1Щ1м получение на выходах двух импульсных последовательностей f(t) и f(t), логические единицы на которых формируются соответственно при lUjI К.и0(,„|и lUgl i IK-UBM«| , при .чем логический блок дополнительно связан с выходами третьего формирователя импульсов и вьтолнен реализующим на своих выходах импульсные последовательности

fg(t) rf(t). i(t).f(t).f(t).

.f(t) f(t).f, (t).f.(t).f,(t)..

fg(t) ffjt).f (t).fj.(t).f(t).

.f(t) -t- f(t).f(t).f(t).f(t). );

f(t) .rfi(t).fi(t). .(t).f(t).

.f,(t) + f(t). f,(t).f(t).f.,(t).

);

f,/t) rf,(t).f (t).f(t).f(t).

.f, (t). + f(t).f/(t).f(t).f,(t)r

fjCt).

CltD

. ,

fcj И/

-дг- -If

Ljp

Ф w

t f.

.

25 „4/

IpLLii

n.tg

| Современные задачи преобразова- тельной техники | |||

| - Ч | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топочная решетка для многозольного топлива | 1923 |

|

SU133A1 |

| Преобразователь частоты | 1982 |

|

SU1092680A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь частоты | 1984 |

|

SU1205240A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-09-07—Публикация

1985-07-01—Подача