Изобретение относится к элект- ротехнике, в частности к бестрансформаторным статическим преобразова телям переменного напряжения одной частоты в переменное напряжение другой частоты.

Целью изобретения является повышение надежности и КПД путем уменьшения количества управляемых ключевых элементов.

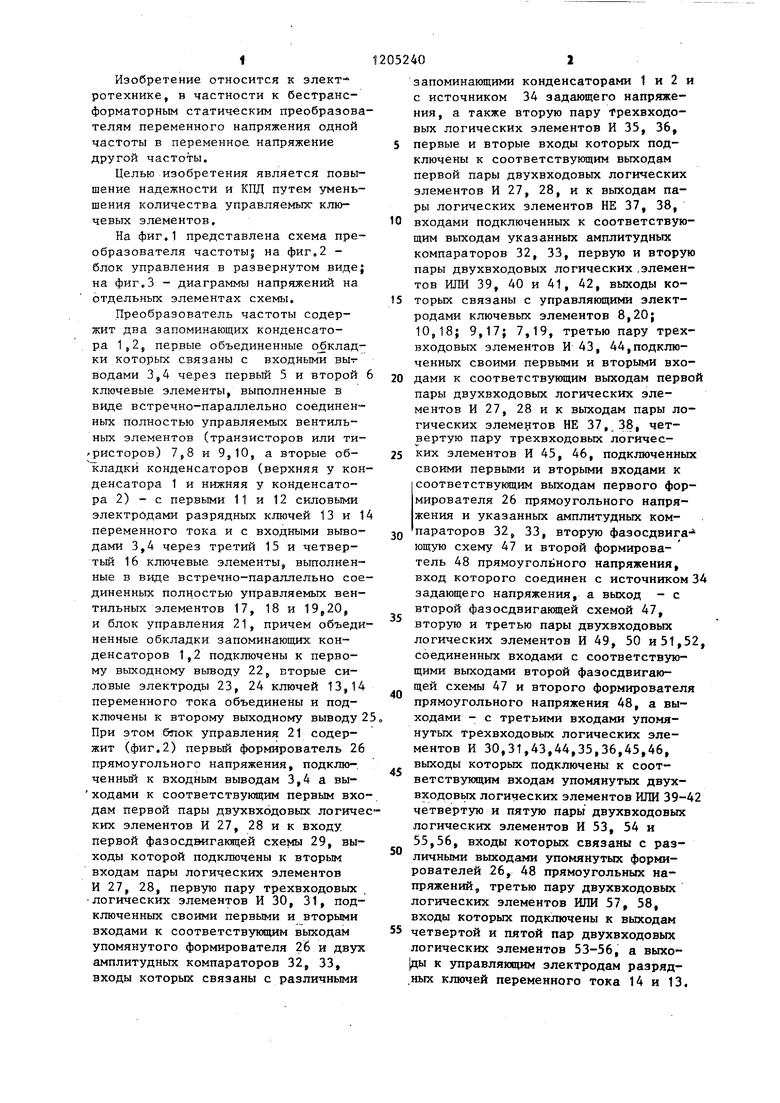

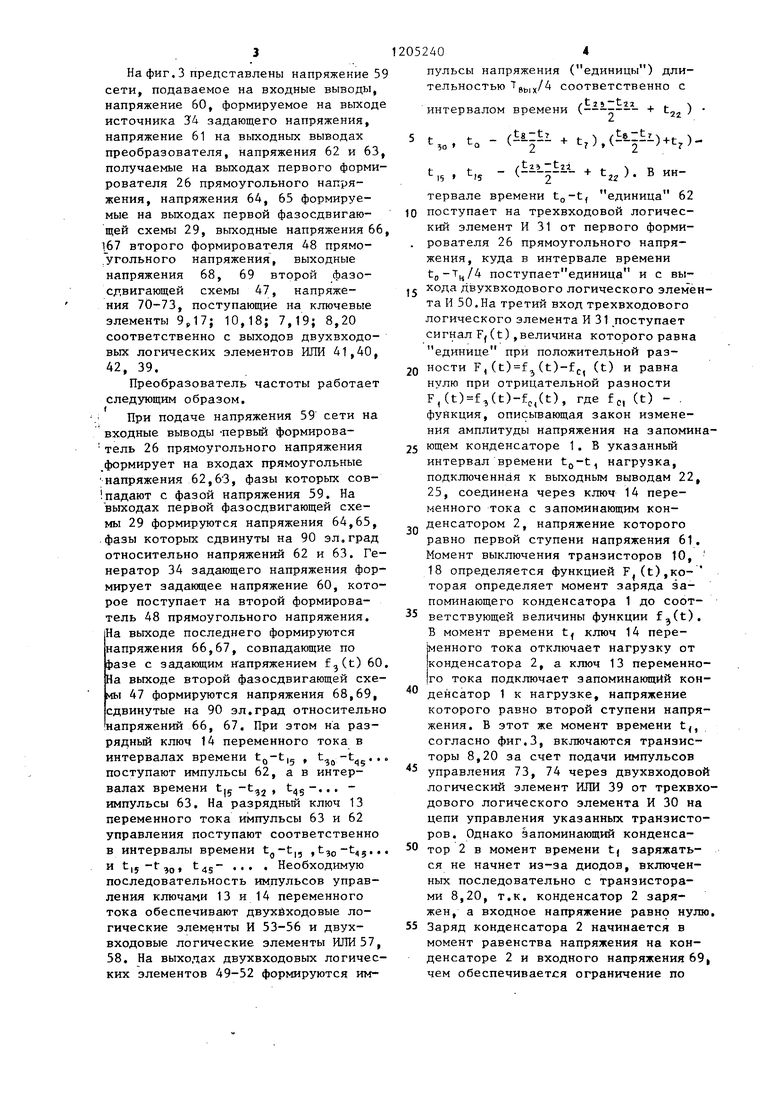

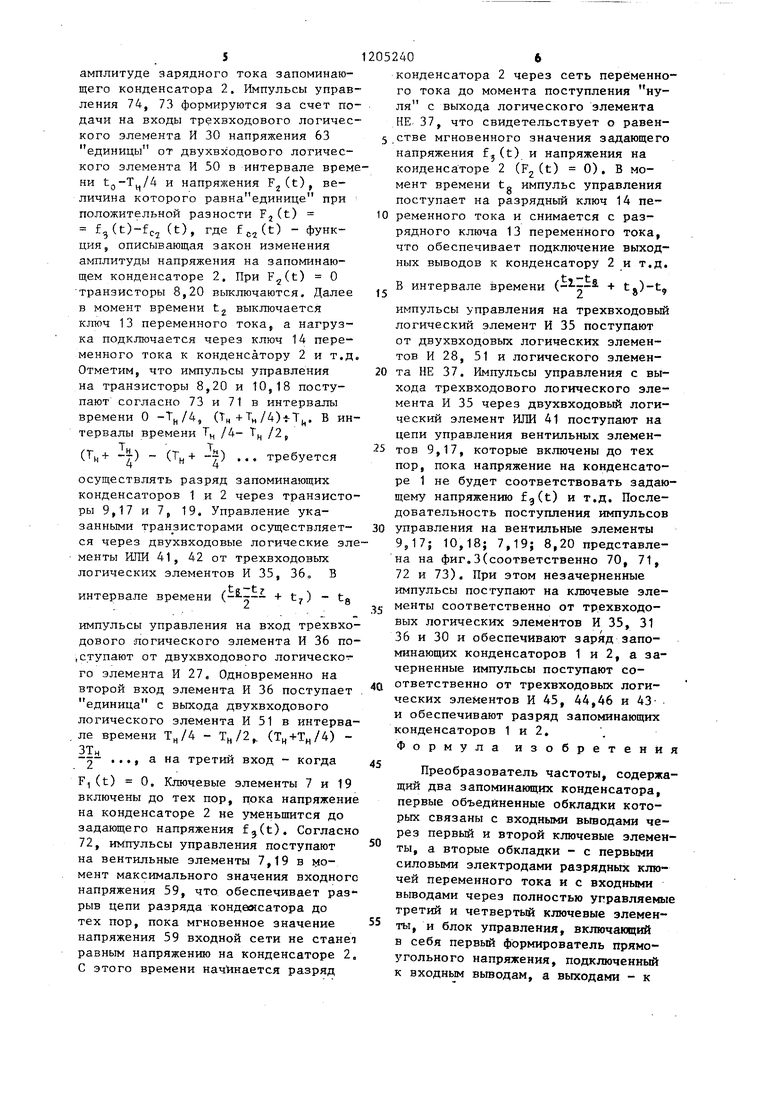

На фиг.1 представлена схема преобразователя частоты; на фиг,2 - блок управления в развернутом виде; на фиг.З - диаграммы напряжений на отдельных элементах схемы.

Преобразователь частоты содержит два запоминающих конденсатора 1(2j первые объединенные о бклад- ки которых связаны с входными выт водами 3j4 через первый 5 и второй 6 ключевые элементы, выполненные в виде встречно-параллельно соединенных полностью управляемых вентильных элементов (транзисторов или ти- ристоров) 7,8 и 9j10j а вторые об- 1 :ладкй конденсаторов (верхняя у конденсатора 1 и нижняя у конденсатора 2) - с первыми 11 и 12 силовыми электродами разрядных ключей 13 и 14 переменного тока и с входными выводами 3,4 через третий 15 и четвер- тьй 16 ключевые элементы, выполненные в виде встречно-параллельно соединенных полностью управляемых вентильных элементов 17, 18 и 19(20, и блок управления 21, причем объединенные обкладки запоминающих конденсаторов 1,2 подключены к первому выходному выводу 22, вторые силовые электроды 23, 24 ключей 13,14 переменного тока объединены и подключены к второму выходному выводу 2 При этом блок управления 21 содержит (фиг.2) первый формирователь 26 прямоугольного напряжения, подклю-. ченньй к входным выводам 3,4 а вы- ходами к соответствующим первым входам первой пары двухвходовых логических элементов И 27, 28 и к входу первой фазосдвигакщей схемы 29, выходы которой подключены к вторым входам пары логических элементов И 27, 28, первую пару трехвходовых -логических элементов И 30, 31, подключенных своими первыми и вторыми входами к соответствуюпщм выходам упомянутого формирователя 26 и двух амплитудньпс компараторов 32, 33, входы которых связаны с различными

12052402

запоминающими конденсаторами 1 и 2 и с источником 34 задающего напряже

5

0

5

0

5

0

ния, а также вторую пару трехвходовых логических элементов И 35, 36, первые и вторые входы которых подключены к соответствующим выходам первой пары двухвходовых логических элементов И 27, 28, и к выходам пары логических элементов НЕ 37, 38, входами подключенных к соответствующим выходам указанных амплитудных компараторов 32, 33, первую и вторую пары двухвходовых логических .элементов ИЛИ 39, 40 и 41, 42, выходы которых связаны с управляющи1«ш электродами ключевых элементов 8,20; 10,18; 9,17; 7,19, третью пару трехвходовых элементов И 43, 44,подключенных своими первыми и вторыми вхо0 дами к соответствующим выходам первой пары двухвходовых логических элементов И 27, 28 и к выходам пары логических элементов НЕ 37, 38, четвертую пару трехвходовых логичес5 ких элементов И 45, 46, подключенных своими первыми и вторыми входами к соответствующим выходам первого формирователя 26 прямоугольного напряжения и указанных амплитудных компараторов 32, 33, вторую фазосдвига- ющую схеьгу 47 и второй формирова- тель 48 прямоугольного напряжения, вход которого соединен с источником 34 задающего напряжения, а выход - с второй фазосдвигающей схемой 47, вторую и третью пары двухвходовых логических элементов И 49, 50 и 51,52, соединенных входами с соответствзгю- щими выходами второй фазосдвигаю- щей схемы 47 и второго формирователя прямоугольного напряжения 48, а выходами - с третьими входами упомянутых трехвходовых логических элементов И 30,31,43,44,35,36,45,46, выходы которых подключены к соответствующим входам упомянутых двух- входовьпс логических элементов ИЛИ 39-42 четвертую и пятую пары двухвходовых логических элементов И 53, 54 и 55,56, входы которых связаны с различными выходами упомянутых формирователей 26, 48 прямоугольных напряжений, третью пару двухвходовых логических элементов ИЛИ 57, 58, входы которых подключены к выходам

5 четвертой и пятой пар двухвходовых логических элементов 53-56, а выхо- |ды к управляющим электродам разряд- .ных ключей переменного тока 14 и 13.

На фиг. 3 представлены напряжение 59 сети, подаваемое на входные выводы, напряжение 60, формируемое на выходе источника 54 задающего напряжения, напряжение 61 на выходных выводах преобразователя, напряжения 62 и 63, получаемые на выходах первого формирователя 26 прямоугольного напряжения, напряжения 64, 65 формируемые на выходах первой фазосдвигаю- щей схемы 29, выходные напряжения 66, .67 второго формирователя 48 прямоугольного напряжения, выходные напряжения 68, 69 второй фазо- сдвигающей схемы 47, напряжения 70-73, поступающие на ключевые элементы 9J7; 10,18; 7,19; 8,20 соответственно с выходов двухвходо- вых логических элементов ИЛИ 41,40, 42, 39.

Преобразователь частоты работает следующим образом,

При подаче напряжения 59 сети на входные выводы -первьй формирова- тель 26 прямоугольного напряжения формирует на входах прямоугольные напряжения 62,63, фазы которых сов- падают с фазой напряжения 59. На выходах первой фазосдвигающей схемы 29 формируются напряжения 64,65, фазы которых сдвинуты на 90 эл.град относительно напряжений 62 и 63. Генератор 34 задающего напряжения формирует задающее напряжение 60, которое поступает на второй формирователь 48 прямоугольного напряжения. Па выходе последнего формируются напряжения 66,67, совпадающие по фазе с задающим напряжением f(t) 60. На выходе второй фазосдвигающей схе- У1Ы 47 формируются напряжения 68,69, сдвинутые на 90 эл.град относительно напряжений 66, 67. При этом на разрядный ключ 14 переменного тока в интервалах времени , .., поступают импульсы 62, а в интервалах времени tjj -t,jj , Цд-... - импульсы 63. На разрядный ключ 13 переменного тока импульсы 63 и 62 управления поступают соответственно в интервалы времени ,, ,,-t.., и t|5-t,(,, ... . Необходимую последовательность импульсов управления ключами 13 и 14 переменного тока обеспечивают двухйходовые логические элементы И 53-56 и двух- входовые логические элементы ИЛИ 57, 58. На выходах двухвходовых логических элементов 49-52 формируются им2052404

пульсы напряжения (единицы) длительностью Tgbix соответственно с

t 2 -tiz

интервалом времени ( + t )

5 г t - r-S-I-I + f ..,- ч д , to I. 2 + ty;, V 2 ;+Lj.;- ( + t,,). В ин15

-15

тервале времени to-t, единица 62

поступает на трехвходовой логический элемент И 31 от первого формирователя 26 прямоугольного напряжения, куда в интервале времени поступает единица и с выхода Д1зухвходового логического элемента И 50.На третий вход трехвходового огического элемента И 31 поступает сигнал ГД t),величина которого равна

0

единице при положительной разности F,(t)f (t)-ff (t) и равна

0

54-/ -с,

нулю при отрицательной разности F,(t)f,(t)-f,,(t), где fc, (t) - . функция, описьгеающая закон изменения амплитуды напряжения на запомина5 ющем конденсаторе 1. В указанньм интервал времени , нагрузка, подключенная к выходным выводам 22, 25, соединена через ключ 14 переменного тока с запоминающим конденсатором 2, напряжение которого равно первой ступени напряжения 61. Момент выключения транзисторов 10, 18 определяется функцией F(t),KO- торая определяет момент заряда запоминающего конденсатора 1 до соот5 ветствующей величины функции fj(t). В момент времени t ключ 14 переменного тока отключает нагрузку от конденсатора 2, а ключ 13 переменного тока подключает запоминающий конденсатор 1 к нагрузке, напряжение которого равно второй ступени напряжения. В этот же момент времени t,, согласно фиг.З, включаются транзисторы 8,20 за счет подачи импульсов

управления 73, 74 через двухвходовой логический элемент ИЛИ 39 от трехвхо- дового логического элемента И 30 на цепи управления указанных транзисторов. Однако запоминающий конденсатор 2 в момент времени t( заряжаться не начнет из-за диодов, включенных последовательно с транзисторами 8,20, т.к. конденсатор 2 заряжен, а входное напряжение равно нулю.

5 Заряд конденсатора 2 начинается в момент равенства напряжения на конденсаторе 2 и входного напряжения 691 чем обеспечивается ограничение по

0

0

5

амплитуде зарядного тока запоминающего конденсатора 2. Импульсы управления 74, 73 формируются за счет подачи на входы трехвходового логического элемента И 30 напряжения 63 единицы от двухвходового логического элемента И 50 в интервале времни t,, и напряжения ), величина которого равна единице при положительной разности F(t) fg(t)-fc2 (t), где ) - функция, описывающая закон изменения амплитуды напряжения на запоминающем конденсаторе 2. При ) О транзисторы 8,20 выключаются. Далее в момент времени t выключается ключ 13 переменного тока, а нагрузка подключается через ключ 14 переменного тока к конденсатору 2 и т.д Отметим, что импульсы управления на транзисторы 8,20 и 10,18 поступают согласно 73 и 71 в интервалы времени О , (Тц+Т„/4)T, В интервалы времени Т /4- Т /2,

( -) - (TH+ -) « требуется

осуществлять разряд запоминающих конденсаторов 1 и 2 через транзисторы 9,17 и 7, 19, Управление указанными транзисторами осуществляется через двухвходовые логические элменты ИЛИ 41, 42 от трехвходовьгх логических элементов И 35, 36,, В

1 - t

интервале времени ( + t,) - t

8

импульсы управления на вход трехвходового логического элемента И 36 по- ступают от двухвходового логическо го элемента И 27, Одновременно на второй вход элемента И 36 поступает . единица с выхода двухвходового логического элемента И 51 в интерва- ле времени Т„/4 - Тц/2,. () ЗТ

-2 о, а на третий вход - когда

F,(t) О, Ключевые элементы 7 и 19 включены до тех пор, пока напряжение на конденсаторе 2 не уменьшится до задающего напряжения fj(t). Согласно 72, импульсы управления поступают на вентильные элементы 7,19 в момент максимального значения входного напряжения 59, что обеспечивает разрыв цепи разряда кондемсатора до тех пор, пока мгновенное значение напряжения 59 входной сети не станет равным напряжению на конденсаторе 2. С этого времени начинается разряд

.

2052406

конденсатора 2 через сеть переменного тока до момента поступления нуля с выхода логического элемента НЕ- 37, что свидетельствует о равен- 5,стве мгновенного значения задающего напряжения f (t) и напряжения на конденсаторе 2 (F(t) 0), В момент времени tg импульс управления поступает на разрядный ключ 14 пе- 10 ременного тока и снимается с разрядного ключа 13 переменного тока, что обеспечивает подключение выходных выводов к конденсатору 2 и т.д.

В интервале времени ( + tg)-t,

импульсы управления на трехвходовый логический элемент И 35 поступают от двухБходовых логических элементов И 28, 51 и логического элемен20 та НЕ 37. Импульсы управления с выхода трехвходового логического элемента И 35 через двухвходовый логический элемент ИЛИ 41 поступают на цепи управления вентильных элемен25 тов 9,17, которые включены до тех пор, пока напряжение на конденсаторе 1 не будет соответствовать задающему напряжению fg(t) и т.д. Последовательность поступления импульсов

30 управления на вентильные элементы 9,17; 10,18; 7,19; 8,20 представлена на фиг.3(соответственно 70, 71, 72 и 73), При этом незачерненные импульсы поступают на ключевые эле менты соответственно от трехвходо- вых логических элементов И 35, 31 36 и 30 и обеспечивают заряд запоминающих конденсаторов 1 и 2, а зачерненные импульсы поступают со40 ответственно от трехвходовых логических элементов И 45, 44,46 и 43- и обеспечивают разряд запоминающих конденсаторов 1 и 2, Формула изобретения

Преобразователь частоты, содержащий два запоминающих конденсатора, первые объединенные обкладки которых связаны с входными вьшодами через первый и второй ключевые элементы, а вторые обкладки - с первыми силовыми электродами разрядных ключей переменного тока и с входными выводами через полностью управляемые третий и четвертый ключевые элемен- 55 ты, и блок управления, включающий в себя первый формирователь прямоугольного напряжения, подключенный к входным вьгаодам, а выходами - к

50

соответствующим первым входам первой пары двухвходовых логических элементов Инк входу первой фазосдвигз ющей схемы, выходы которой подключены к вторым входам указанной пары логических элементов И, первую пару трехвходовьгх логических элементов И, подключенных своими первыми и вторыми входами к соответствующим выходам упомянутого формирователя и двух амплитудных компараторов, входы которых связаны с различными запоминающими конденсаторами и источником задающего напряжения, а также вторую пару трехвходовых . .логических элементов И, первые и вторые входы которых подключены к соответствую- щим выходам первой пары двухвходовых логических элементов И и к выходам пары логических элементов НЕ, входами подключенных к соответствующим выходам указанных амплитудных компараторов, отличающий- с я тем, что, с целью повьппения надежности и КПД, первые и вторые ключевые элементы выполнены на полностью управляемых вентилях, а выходные вьгооды подключены соответственно к объединенным обкладкам запоминающих конденсаторов и объединенным вторым силовым электродам разрядных ключей переменного тока, при этом блок управления дополнительно снабжен первой и второй парами двухвходовых логических элементов ИЛИ, выходы которых связаны с управляющими электродами четырех ключевых элементов, третьей парой трехвходовых логических элементов И, подключенных

2052408

своими первыми и вторыми выходами к соответствующим выходам первой пары двухвходовых логических элементов Ник вькодам пары логических 5 элементов НЕ, четвертой парой трехвходовых логических элементов И, ,подключенных своими первыми и вторыми входами к соответствующим выходам первого формирователя пря10 моугольного напряжения и указанных амплитудных компараторов, второй фазосдвигающей схемой и вторым формирователем прямоугольного напряжения, вход которого соединен с ис15 точником задающего напряжения, а выход - с второй фазосдвигающей схемой, второй и третьей парами двухвходовых логических элементов И, соединенных входами с срответствую20 щими выходами второй фазосдвигающей схемы и второго формирователя прямоугольного напряжения, а выхо- .дами - с третьими входами упомянутых трехвходовых логических эле25 ментов И, выходы которых подключены к соответствующим входам двухвходовых логических элементов ИЛИ, четвертой и пятой парами двухвходовых логических элементов И, вхо30 ды которых связаны с различными

выходами формирователей прямоугольных напряжений, третьей парой двухвходовых логических элементов ИЛИ, входы которых подключены к выходам , четвертой и пятой пар двухвходовых логических элементов И, а выходы - к управляющим электро- дам разрядных ключей переменного тока.

lem

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| Преобразователь частоты | 1986 |

|

SU1403287A2 |

| Однофазный преобразователь частоты | 1987 |

|

SU1800569A1 |

| Преобразователь постоянного напряжения в переменное N-ступенчатой формы | 1988 |

|

SU1658343A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

| Устройство для импульсно-фазового управления @ -фазным преобразователем | 1987 |

|

SU1610566A1 |

| Устройство для автоматической настройки дугогасящего реактора | 1984 |

|

SU1228182A1 |

| Однофазный преобразователь частоты | 1985 |

|

SU1422329A1 |

| Преобразователь переменного напряжения в постоянное | 1982 |

|

SU1171932A1 |

| Устройство для одноканального синхронного фазового управления вентильным трехфазным преобразователем | 1982 |

|

SU1086543A1 |

Изобретение позволяет повысить надежность КПД преобразователя частоты путем уменьшения количества управляемых ключевых элементов 5, 6 и 15, 16, выполненных на полностью управляемых вентилях 7, 8, 9, 10 и 17, 18, 19, 20, Выходные выводы вентилей подключены соответственно к обкладкам конденсаторов 1, 2 и силовым электродам разрядных ключей 13, 14 переменного тока, Импульсы управления с выхода блока управления 21 поступают на цепи уп равления управляемых вентилей 9,17, которые будут включены до тех пор, пока напряжение на конденсаторе 1 не будет соответствовать задающему напряжению. Последовательность поступления импульсов управления на управляющие вентили 9, 17; 10, 18; 7, 19 и 8, 20 от блока управления 21 .обеспечивает заряд запоминающих конденсаторов 1,2. 3 ил. § (Л Л

ff ППППППППППДМ1ШППППППППШШЖ1ПППППП1 .

w

ппппппппппппппппппппппппппппппппппп ;

ППППППППППППППППППППППППППППППППППП .t

tyf

М1 Ш.11111.

liiii Jl 5j lJ±filli

1

. in8fliai

и

(ff tr4 tffte

.OJJJ.

ВНИИПИ Заказ 8537/56 Тираж 645 Подписное Филиал ППП Патент, г.Ужгород, ул.Проектная, А

t% « B t«

r .j

3

JfaJJt,

JigJilL.

HO «.га

Фи$.3

| Проблемы преобразовательной техники | |||

| Киев: Изд-во АН УССР, 1979, с.39-41 | |||

| Электронная техника в автоматике, вып | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| М.: Сов | |||

| радио, 1980, с.233-240 | |||

| Преобразователь частоты | 1982 |

|

SU1092680A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-01-15—Публикация

1984-06-25—Подача