Изобретение относится к электросвязи и может использоваться для оценки качества передачи сложных сигналов.

Цель изобретения - расширение функциональных возможностей за счет локализации отклонений параметров выходного сигнала радиостанции.

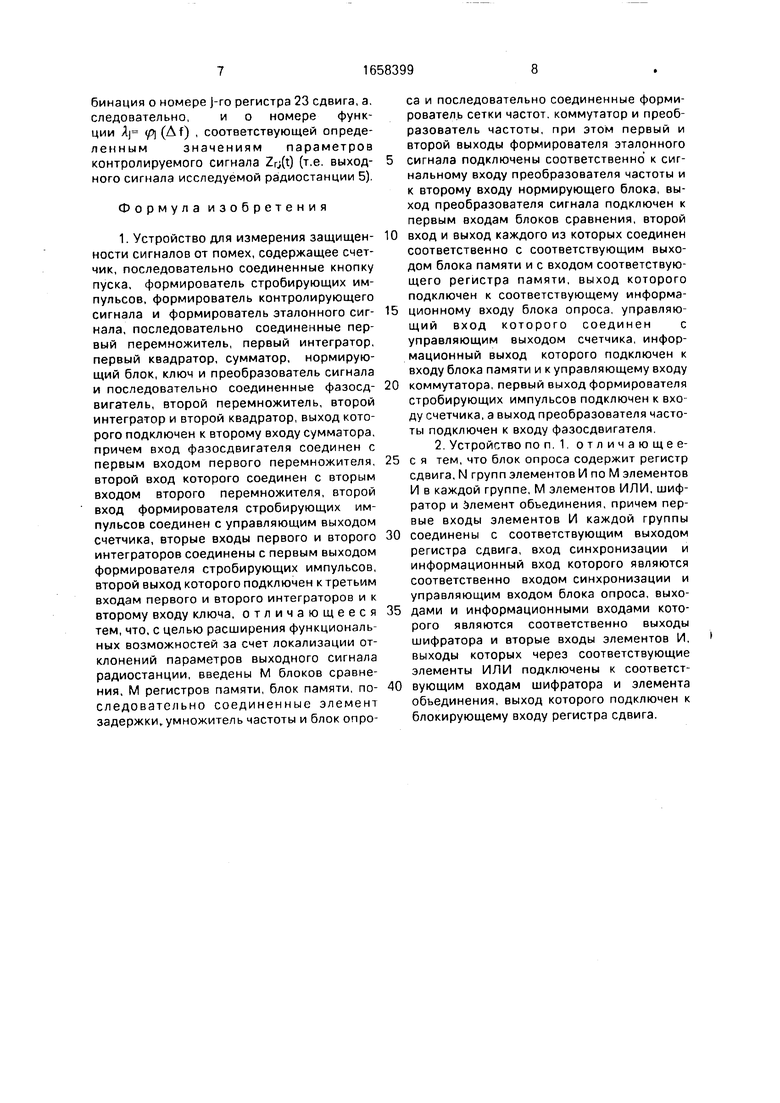

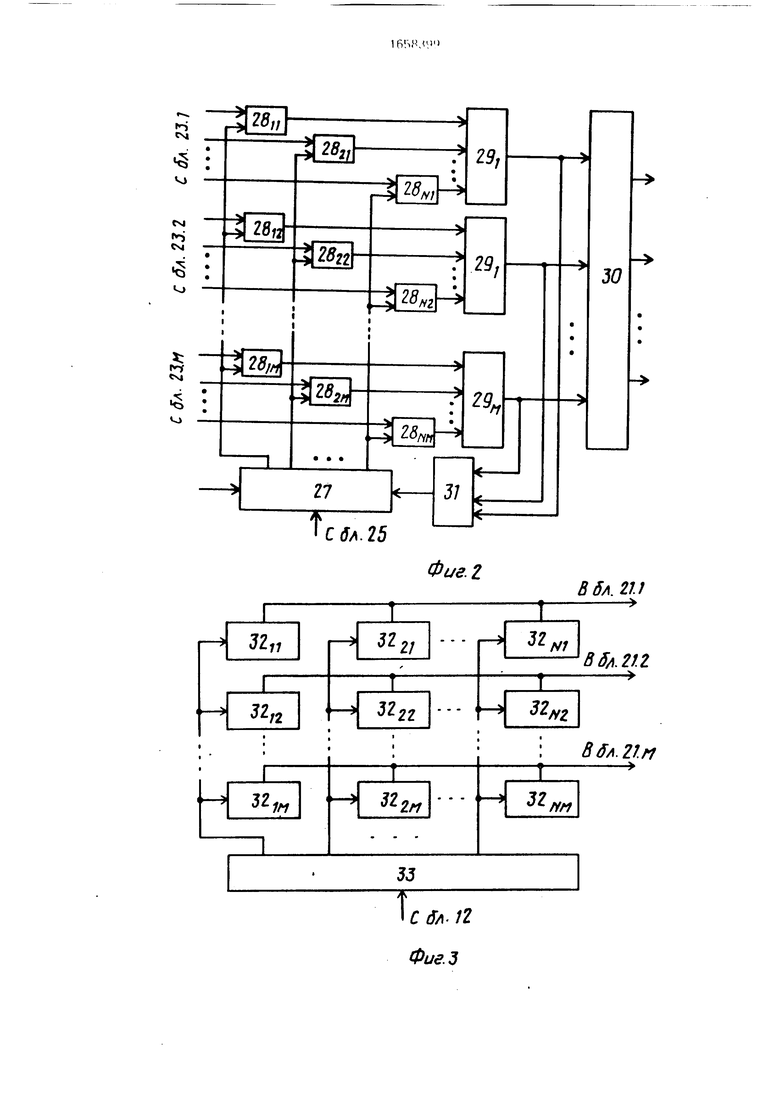

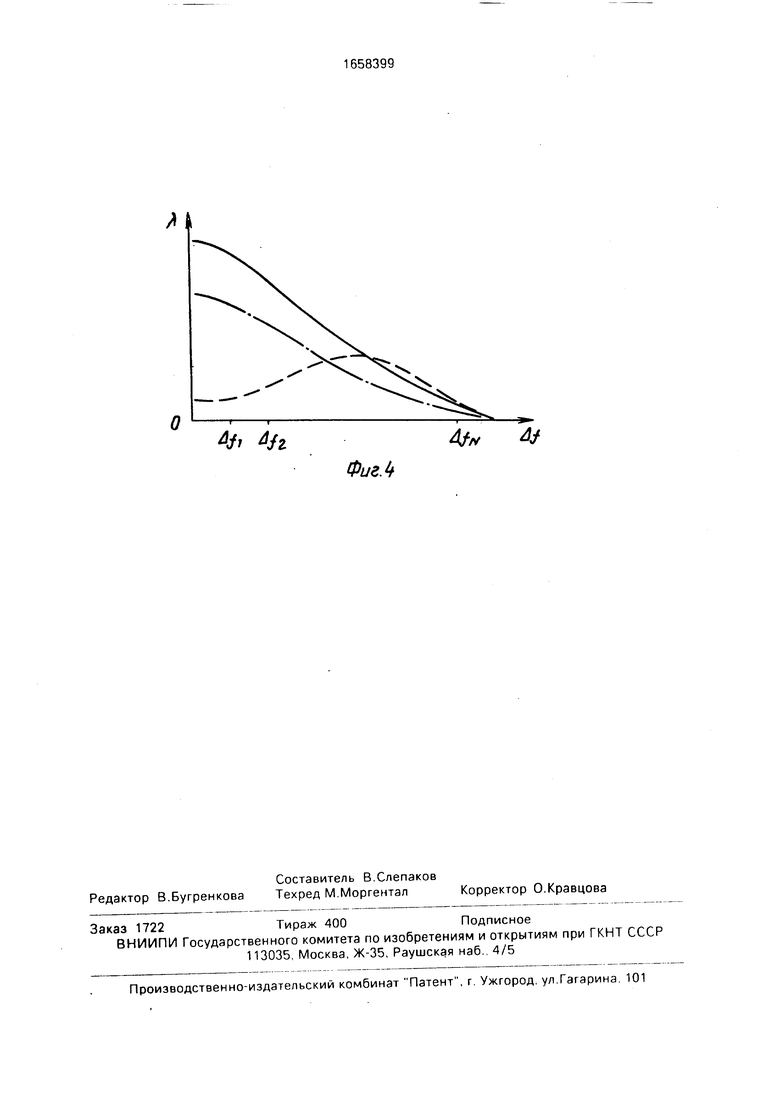

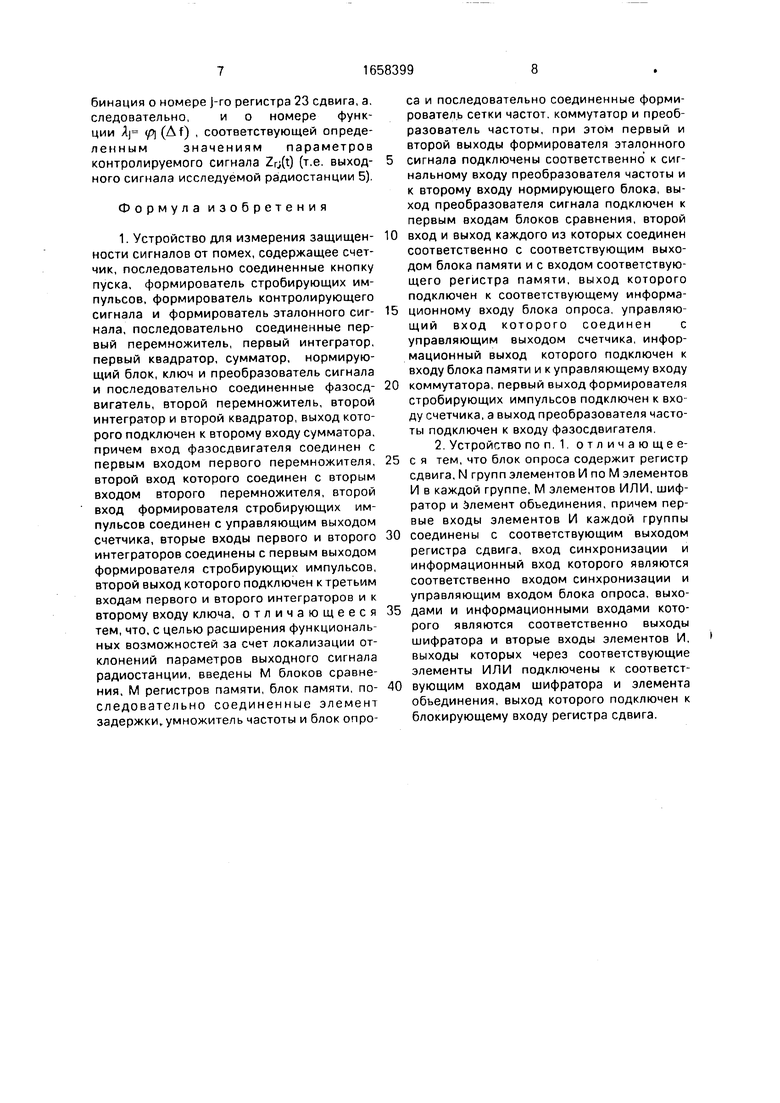

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема блока опроса; на фиг. 3 - структурная электрическая схема блока памяти: на фиг. 4 - графики зависимостей коэффициента взаимного различия от величины расстройки между несущими частотами контролируемого и эталонного сигналов для различных значений параметров выходного сигнала исследуемой радиостанции.

Устройство для контроля сигналов содержит кнопку 1 пуска, формирователь 2 стробирующих импульсов, формирователь 3 контролирующего сигнала, формирователь 4 эталонного сигнала, исследуемую радиостанцию 5, первый перемножитель 6, второй перемножитель 7, преобразователь 8 частоты, фазосдвигательЭ, коммутатор 10, формирователь 1. сетки частот, счетчик 12, первый интегратор 13, второй интегратор 14, первый квадратор 15, второй квадратор 16, сумматор 17, нормирующий блок 18, ключ 19, преобразователь 20 сигнала, блоки 21.1-21.М сравнения, блок 22 памяти, регистры 23.1-23.М памяти, блок 24 опроса, умножитель 25 частоты импульсов и элемент 26 задержки, причем блок 24 опроса содержит регистр 27 сдвига, элементы И 28ц - 28мм, элементы ИЛИ 29ч - 29м, дешифратор 30 и элемент объединения 31, а блок 22 памяти содержит ячейки 32ц - 32м памяти и дешифратор 33.

Устройство работает следующим образом.

Перед началом работы формирователь 2 стробирующих импульсов, формирователь 3 контролирующего сигнала и формирователь 4 эталонного сигнала находятся в исходном (выключенном) состоянии. Счетчик 12 и М регистров 23 памяти обнулены. В ячейках 32 блока 22 памяти записана информация о значениях коэффициента взаимного различия для N частотных сдвигов {Afi} I 1, 2,...N между контролируемым и эталонным сигналом и М значений параметров контролируемого сигнала. Выходы ячеек памяти, соответствующие контролируемому сигналу 2,ь (j - 1, 2...М) с определенными значениями паря- мгмров, объединены и подключены к чтороМу ХОДУ ГПГН ВРТСТруЮЩРГГ) Плпьл 1

сраччрния

При нажатии кнопки 1 напряжение подается на вход формирователя 2 стробирующих импульсов, запуская его генератор тактовых импульсов (не показан).

По команде с первого выхода формирователя 2 стробирующих импульсов формирователь 3 контролирующего сигнала вырабатывает управляющий низкочастотный сигнал (для дискретной двоичной сис0 темы передачи информации это может быть телеграфная посылка О либо 1), поступивший одновременно на входы формирователя 4 эталонного сигнала и исследуемой радиостанции 5. Контролируемый сигнал

5 Zrk(t). прошедший через все тракты исследуемой радиостанции 5, поступает на первые входы перемножителей 6 и 7. С выхода формирователя 4 эталонного сигнала (в простейшем случае это может быть радио0 станция, однотипная с исследуемой, но параметры которой имеют номинальные значения) эталонный сигнал Zr{t) идеальный, т.е. без искажений, обусловленных отклонениями параметров реальных радиостан5 ций от номинальных значений) мощностью Ргэ через преобразователь 8 частоты поступает на второй вход первого перемножителя 6 непосредственно, а на второй вход второго перемножителя 7 - че0 рез фазосдвигатель 9, который осуществляет формирование сигнала Zr3t), сопряженного по Гильберту с эталонным сигналом Zr3(t).

На второй вход преобразователя 8 час5 тоты через электронный коммутатор 10 с выхода формирователя 11 сетки частот подается сигнал одной из гетеродинных частот fi(rfle i 1,2...N; N -число гетеродинных частот на выходе формирователя 11). Выбор

0 необходимой гетеродинной частоты осуществляется при подаче на управляющий вход коммутатора 10 соответствующей кодовой комбинации с информационного выхода счетчика 12, вход которого подклю5 чен к первому выходу формирователя 2 стробирующих импульсов.

Сигйалы, полученные в результате перемножения с выходов перемножителей 6 и 7, поступают на первые входы интеграторов

0 13 и 14. предварительно установленных в начальное состояние импульсом с первого выхода формирователя 2. После интегрирования в течение времени, равного длительности элемента сигнала tf О, Т. сигналы с

5 выходов интеграторов 13 и 14 поступают через квадраторы 15 и 16 на соответствующие входы сумматора 17. С выхода сумматора 17 сигнал поступает на первый вход нормирующего блока 18, второй вход которого соединен с вторым выходом форми

роеателя 4 эталонного сигнала. С нормирующего блока 18 сигнал поступает на информационный вход ключа 19, в котором при поступлении на его управляющий вход стробирующего импульса с второго выхода формирователя 2 осуществляется отсчет результата измерения коэффициента взаимного различия контролируемого и эталонного сигналов, описываемого следующим выражением:

,K(t)Ј9(t)dti2+

гэ 11 оJ

+ t/zrK(t)Zr3(t)dtl}2

Стробирующий импульс с второго выхода формирователя 2 поступает также на третьи входы интеграторов 13 и 14 для сброса накопленной в них энергии.

Напряжение с выхода ключа 19, подаваемое на информационный вход преобразователя 20 сигнала, в зависимости от измеренного значения k, преобразуется в соответствующий двоичный код, поступающий на первые входы блоков 21.2 - 21.М сравнения.

К вторым входам блоков 21.1-21.М сравнения подключены соответствующие выходы блока 22 памяти. При поступлении с информационного выхода счетчика 12 на вход блока 22 памяти кодовой комбинации, соответствующей номеру 1-й гетеродинной частоты на выходе преобразователя 8, к выходам блока 22 будут подключены ячейки памяти, в которых записана информация об уровнях коэффициента взаимного различия, соответствующих различным значениям параметров контролируемого сигнала и определенной частотной расстройке Afi между эталонным и контролируемым сигналами.

На фиг. 4 в качестве примера рассмотрен сложный сигнал последовательной структуры, фазокодированный последовательностью Баркера: {drk } 1111100110101. Графики приведены для следующих значений параметров контролируемого сигнала (выходного сигнала исследуемой радиостанции): сплошная линия - все параметры контролируемого сигнала имеют номинальные значения; штриховая линия - относительная нестабильность длительности субэлемента контролируемого сигнала Д г/Го 0,08: штрих-пунктирная линия - искажение начальной фазы одного из субэлементов контролируемого сигнала Д V П .

Точки на оси абсцисс { Д fi} I - 1,2... N соответствуют значениям частотных расстроек между контролируемым и эталонным сигналами, при которых измеряется коэффициент

взаимного различия.

Если результат измерения коэффициента AJ с выхода преобразователя 20 равен уровню коэффициента взаимного различия, записанного в одной или нескольких ячейках 32 памяти блока 22, то на выходе соответствующих блоков 21 сравнения появляется сигнал логической единицы, который поступает в соответствующие регистры 23 памяти.

После проведения N измерений коэффициента взаимного различия с управляющего выхода счетчика 12 поступает импульс на второй вход формирователя 2 стробиру- ющих импульсов (для отключения входящего в его состав генератора тактовых импульсов) и на управляющий вход блока 24 опроса (в регистр 27 сдвига). На вход синхронизации регистра 27 сдвига поступают импульсы с умножителя 25 частоты импульсов, подключенного через элемент 26 задержки, к первому выходу формирователя 2 стробирующих импульсов. Время задержки определяется длительностью процессов в устройстве для контроля сигналов от момента формирования импульса блоком 2 до окончания записи логической единицы в соответствующий регистр 23 памяти.

Каждый элемент И 28i) подключен информационным входом к 1-му выходу (соответствующего i-му разряду) J-ro регистра 23 памяти, а управляющим входом к i-му выходу регистра 27 сдвига. При продвижении логической единицы по регистру 27 в первую очередь открываются элементы И

28m - 28NM а, следовательно, к выходам шифратора 30 через соответствующие элементы ИЛИ 29 подключаются высшие разряды памяти всех М регистров 23.

Если, например, в j-м регистре 23 памяти записано максимально возможное число единиц, что соответствует случаю совпадения измеренных значений коэффициента взаимного различия при всех N частотных расстройках между контролируемым и эталонным сигналами со значениями функции Aj pj/Af (фиг. 4), записанными в ячейки 32ij - 32Nj, то через открытый элемент И 28Nj и соответствующий элемент ИЛИ 29J на j-й вход шифратора 30 поступает импульс. Этот же импульс через элемент 31 объединения поступает на блокирующий вход регистра 27 сдвига для его остановки. С выхода шифратора 30 на выход устройства поступает кодовая комбинация о номере j-ro регистра 23 сдвига, а, следовательно, и о номере функции Aj p (Af) , соответствующей определенным значениям параметров контролируемого сигнала Zrj(t) (т.е. выходного сигнала исследуемой радиостанции 5).

Формула изобретения

1. Устройство для измерения защищенности сигналов от помех, содержащее счетчик, последовательно соединенные кнопку пуска, формирователь стробирующих импульсов, формирователь контролирующего сигнала и формирователь эталонного сигнала, последовательно соединенные первый перемножитель, первый интегратор, первый квадратор, сумматор, нормирующий блок, ключ и преобразователь сигнала и последовательно соединенные фазосд- вигатель, второй перемножитель, второй интегратор и второй квадратор, выход которого подключен к второму входу сумматора, причем вход фазосдвигателя соединен с первым входом первого перемножителя, второй вход которого соединен с вторым входом второго перемножителя, второй вход формирователя стробирующих импульсов соединен с управляющим выходом счетчика, вторые входы первого и второго интеграторов соединены с первым выходом формирователя стробирующих импульсов, второй выход которого подключен к третьим входам первого и второго интеграторов и к второму входу ключа, отличающееся тем, что, с целью расширения функциональных возможностей за счет локализации отклонений параметров выходного сигнала радиостанции, введены М блоков сравнения, М регистров памяти, блок памяти, последовательно соединенные элемент задержки,, умножитель частоты и блок опроса и последовательно соединенные формирователь сетки частот, коммутатор и преобразователь частоты, при этом первый и второй выходы формирователя эталонного

сигнала подключены соответственно к сигнальному входу преобразователя частоты и к второму входу нормирующего блока, выход преобразователя сигнала подключен к первым входам блоков сравнения, второй

вход и выход каждого из которых соединен соответственно с соответствующим выходом блока памяти и с входом соответствующего регистра памяти, выход которого подключен к соответствующему информационному входу блока опроса, управляющий вход которого соединен с управляющим выходом счетчика, информационный выход которого подключен к входу блока памяти и к управляющему входу

коммутатора, первый выход формирователя стробирующих импульсов подключен к входу счетчика, а выход преобразователя частоты подключен к входу фазосдвигателя.

2. Устройство поп.1, отличающеес я тем, что блок опроса содержит регистр сдвига, N групп элементов И по М элементов И в каждой группе, М элементов ИЛИ, шифратор и элемент объединения, причем первые входы элементов И каждой группы

соединены с соответствующим выходом регистра сдвига, вход синхронизации и информационный вход которого являются соответственно входом синхронизации и управляющим входом блока опроса, выходами и информационными входами которого являются соответственно выходы шифратора и вторые входы элементов И, выходы которых через соответствующие элементы ИЛИ подключены к соответствующим входам шифратора и элемента обьединения, выход которого подключен к блокирующему входу регистра сдвига.

О

Aj 4/г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения защищенности сигнала от помех | 1988 |

|

SU1570006A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЗАЩИЩЕННОСТИ СИГНАЛА ОТ ПОМЕХ | 2013 |

|

RU2542352C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГОВЫХ ОБЪЕКТОВ | 2004 |

|

RU2262128C1 |

| Устройство для контроля параметров | 1988 |

|

SU1665390A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Устройство для оценки сигналов | 1989 |

|

SU1598189A2 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СИГНАЛОВ | 2007 |

|

RU2354055C1 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1989 |

|

SU1608591A1 |

Изобретение относится к электросвязи. Цель изобретения - расширение функциональных возможностей за счет локализации отклонений параметров выходного сигнала радиостанции. Устройство содержит кнопку 1 пуска, формирователи 2-4 соответственГО К.Л ппч Пуск но стробирующих импульсов, контролирующего и эталонного сигналов, перемножители 6 и 7, преобразователь 8 частоты, фазосдвигатель 9, коммутатор 10, формирователь 11 сетки частот, счетчик 12, интеграторы 13 и 14, квадраторы 15 и 16, сумматор 17 нормирующий блок 18, ключ 19, преобразователь 20 сигнала. М блоков 21 сравнения, блок 22 памяти, М регистров 23 памяти, блок 24 опроса, умножитель 25 частоты импульсов и элемент задержки 26 Устройство позволяет не только измерить комплексный показатель качества сигнала в виде коэффициента взаимного различия, но и определить параметры выходного сигнала объекта контроля (радиостанция 5), отклонение которых от номинальных значений приводит к искажению сигнала. 1 з.п. ф-лы, 4 ил Ё О ел 00 СА) Ю ю Фие.1

Фиг4

| Устройство для измерения защищенности сигнала от помех | 1988 |

|

SU1570006A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-23—Публикация

1989-07-03—Подача