Изобретение относится к области измерения аналоговых параметров и может быть использовано в системах автоматического контроля параметров.tИзвестно устройство ускоренного технологического контроля параметров, содер- жащее объект контроля, блок управления, измеритель коэффициента взаимного раз личия, состоящий из фазовращателя, двух перемножителей, двух интеграторов, двух квадраторов, сумматора, стрббирующего устройства, нормирующего узла и аналого- цифрового преобразователя, генератор эталонных сигналов, синтезатор частот, блок низких частот, блок высоких частот эквивалент антенны и устройство ввода-вывода.

Но известное устройство измеряет комплексный показатель качества в виде коэффициента взаимного различия эталонного и контролируемого сигналов, по значению которого невозможно определить значение параметров объекта контроля

Наиболее близким по своей технической сущности к изобретению является устройство для контроля аналоговых параметров, содержащее коммутатор, три блока вычитания, блок эталонных сигналов, блок сложения, сумматор, преобразователь аналог-код, блоки сравнения, вывода, памяти, и управления.

Однако данное устройство измеряет только комплексную функцию параметров.

Недостатком этих устройств является низкая эффективность контроля, так как они не позволяют определить вследствие изменения каких параметров объекта контроля изменилось значение комплексной функции параметров (комплексного показателя качества объекта контроля).

SI

со

00

ю

Цель изобретения - повышение эффективности контроля объекта за счет выделения параметров, вызывающих уход комплексной функции параметров за пределы допуска.

В качестве комплексной функции параметров контролируемого радиосредства ис- пользуется коэффициент взаимного различия эталонного и контролируемого сигналов, описываемый следующим выражением:

/ Zrk(t)Zra(t)dtf+

+ j / ZrkWZraWatft0)

1 о

где. Zrk(t) и Zra(t) - функции времени, определяющие структуры r-го варианта, соответственно кбнтролируемого и эталонного сигналов;

Zre(t) - функция времени, сопряженная по Гильберту с Zra(t);

Ргэ - мощность эталонного сигнала:

Т - длительность элемента сигнала.

Математическая связь между коэффициентом взаимного различия g и парамет- рами в будет различной для различных видов контролируемых изделий. Так, например, если в качестве контролируемого изделия использовать радиостанцию, работающую сложными параллельными сигналами, то контролируемый сигнал можно передать в следующем аналитическом виде:, .

. . N

Zrk(t) 2 Alk COS (I «Jbt 4V ).

, t.e o.Tj,№

где I - целые числа; Ац. - амплитуда I -и гармонической составляющей контролируемого сигнала; V начальная фаза 1-й составляющей контролируемого сигнала; ofe 2 л/Т; Т - длительность сложного сигнала; N IN - И1 +1 - число.гармоничееких состав- - ляющих сложного сигнала.

По аналогии с (2) эталонный сигнал представляем в форме:

N Zrs(t) 2 А% COs(ftfet+V«).

te о,т.(3)

Используя формулу (1), подставляя в нее выражения (2) и (3), после несложных преобразований получим выражение для коэффициента взаимного различия контролируемого и эталонного сигналов сложной параллельной структуры:

5Cfyg.

5

0

5

0

5

0

5

0

5где мощность эталонного сигнала;

Pk - мощность контролируемого сигнала; . - ; . -,.- :

Q(r)- )ute;.

тотная расстройка между средними частотами спектров эталонного и контролируемого сигналов;

... ()T ;.- г .

Уъ1 :: :. 1- Из (4)можно вынести зависимость коэффициента g от следующих параметров:

и Q/ftte-: относительная нестабильность несущей частоты сигнала:

QI V степень искаже - ния начальных фаз составляющих сложного сигнала;

бЬ551 Alk /A j- неравномерность уровней составляющих сложного сигнала;

04 Pk - мощность контролируемого сигнала.- . ,: .. . . ...

Поставленная цель достигается тем, что в устройство для контроля аналоговых объектов, содержащее блок формирования управляющих и стимулирующих сигналов, блок формирования эталонных сигналов, коммутатор, сумматор, аналого-цифровой преобразователь, первую схему сравнения, блоки вывода информации и памяти допустимых отклонений от эталонных сигналов, первый выход которого соединен с первым входом первой схемы сравнения, а вход связан с управляющим входом коммутатора и управляющим выходом блока формирования управляющих и стимулирующих сигналов, выход окончания цикла контроля и тактовый выход которого подключены соответственно к управляющему и тактовому входам блока вывода информации, а выход стимулирующих сигналов - к входу блока формирования эталонных сигналов и к выходу устройства для соединения с входом объекта контроля, второй вход первой схемы сравнения связан с выходом аналого- цифрового преобразователя, который

служит первым информационным выходом устройства, выход блока вывода информации является вторым информационным выходом устройства, введены два блока умножения, преобразователь частоты, фазовращатель, формирователь сетки частот, два интегратора, два блока возведения в квадрат, блок нормирования, ключ схемы сравнения с второй по М-ю и М регистров, выходы которых соединены с информационными входами блока вывода информации, а входы - с выходами соответствующих схем сравнения, первые и вторые входы схем сравнения с второй по М-ю связаны соответственно с выходом аналого-цифрового преобразователя и с выходами с второго по М-й блока памяти допустимых отклонений от эталонных сигналов, вход аналого-цифрового преобразователя соединен с выходом ключа, информационный вход которого связан с выходом блока нормирования, а управляющий вход - с выходом.окончания цикла измерения блока формирования управляющих и стимулирующих сигналов, ус-1 тановочный выход которого подключен к входам сброса первого и второго интеграторов, выходы которых соединены с входами первого и второго блоков возведения в квадрат, выходы которых связаны с входами первого и второго слагаемых сумматора, выход которого подключен к первому входу .блока нормализации, второй вход которого соединен с первым выходом блока формирования эталонных сигналов, второй вход которого связан с управляющим входом преобразователя частоты, опорный вход которого подключен к выходу коммутатора, информационные входы которого соединены с выходами формирователя сетки частот, выход преобразователя частоты связан с входом фазовращателя и с входом первого, сомножителя первого блока умножения, выход фазовращателя подключен к входу первого сомножителя второго блока умножения, входы вторых сомножителей обоих блоков умножения соединены с входом устройства для подключения объекта контроля, выходы первого и второго блоков умножения связаны с информационными входами первого и второго интеграторов; блок формирования управляющих и стимулирующих сигналов содержит формирователь стробирующих импульсов, формирователь стимулирующих сигналов, счетчик, перемножитель частоты импульсов и элемент задержки, выход которого соединен с входом перемножителя частоты импульсов, выход которого связан с тактовым выходом блока, первый выход формирователя стробирующих импульсов подключен

ко входам элемента задержки и формирова- теля стимулирующих сигналов/к счетному входу счетчика и к установочному выходу блока, вход запуска через кнопку Пуск - к 5 шине питания, а второй выход - к выходу окончания цикла измерения блока, информационный выход счетчика соединен с уп- равляющим выходом блока, а выход переполнения - с выходом окончания цикла

0 контроля блока и с входом остановки формирователя стробирующих импульсов; блок вывода информации содержит регистр сдвига, группы элементов И, группу элементов ИЛИ, элемент ИЛИ и шифратор, выход

5 которого Является выходом блока, а входы С соединены с входами элемента ИЛИ и с / выходами элементов ИЛИ группы, входы каждого элемента ИЛИ группы связаны с выходами элементов И соответствующей

0 группы, первые входы всех. элементов И всех групп соединены с информационными входами блока, а вторые входы элементов И каждой группы подключены к выходу соот- ветствующего разряда регистра сдвига, вхо5 ды разрешения, тактовый и остановки которого соединены соответственно с управляющим, тактовым входами блока и с выходом элемента ИЛИ.

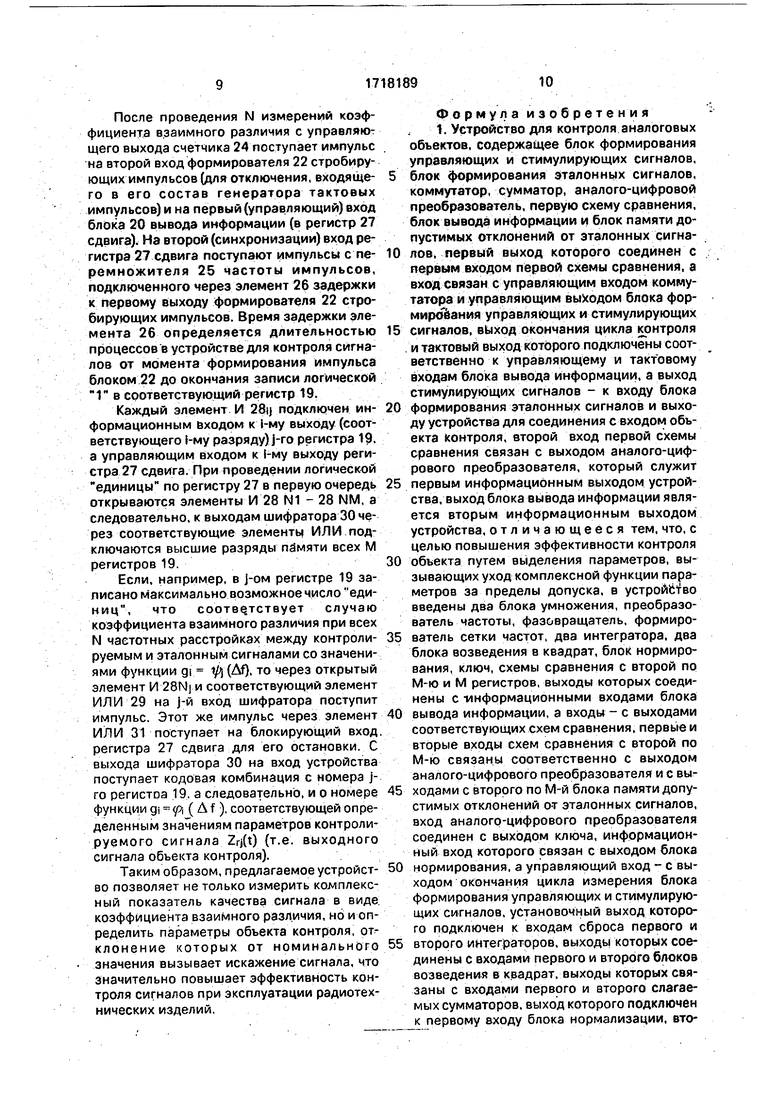

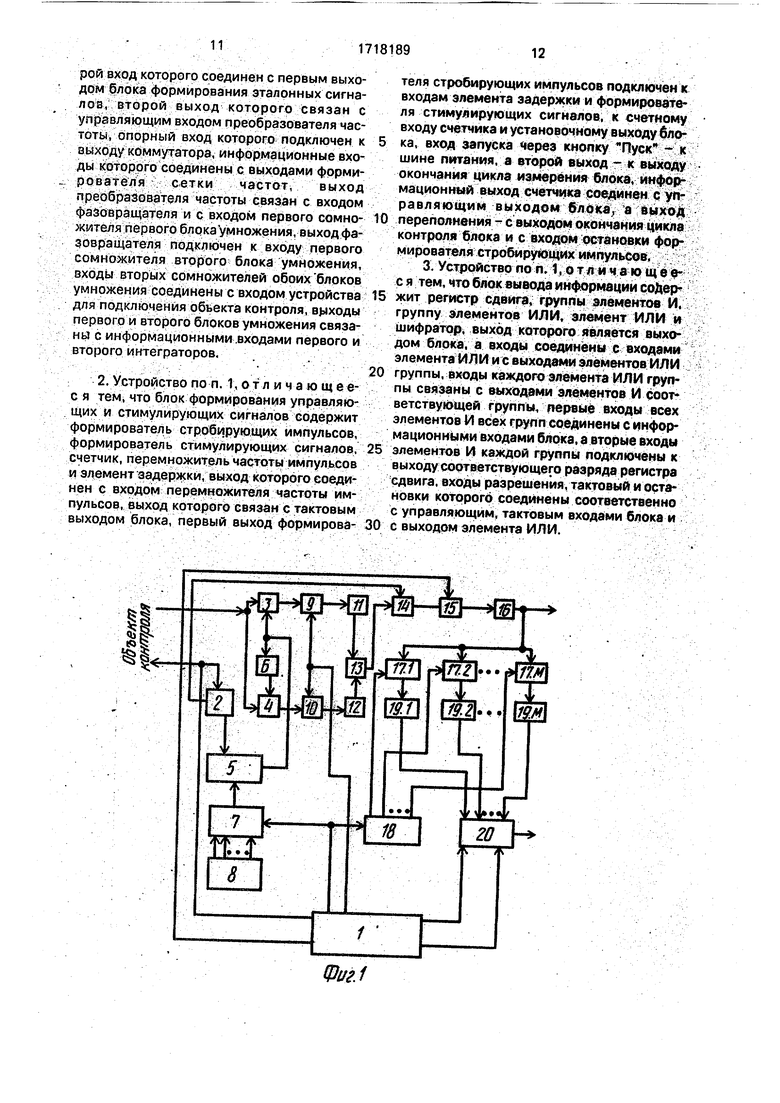

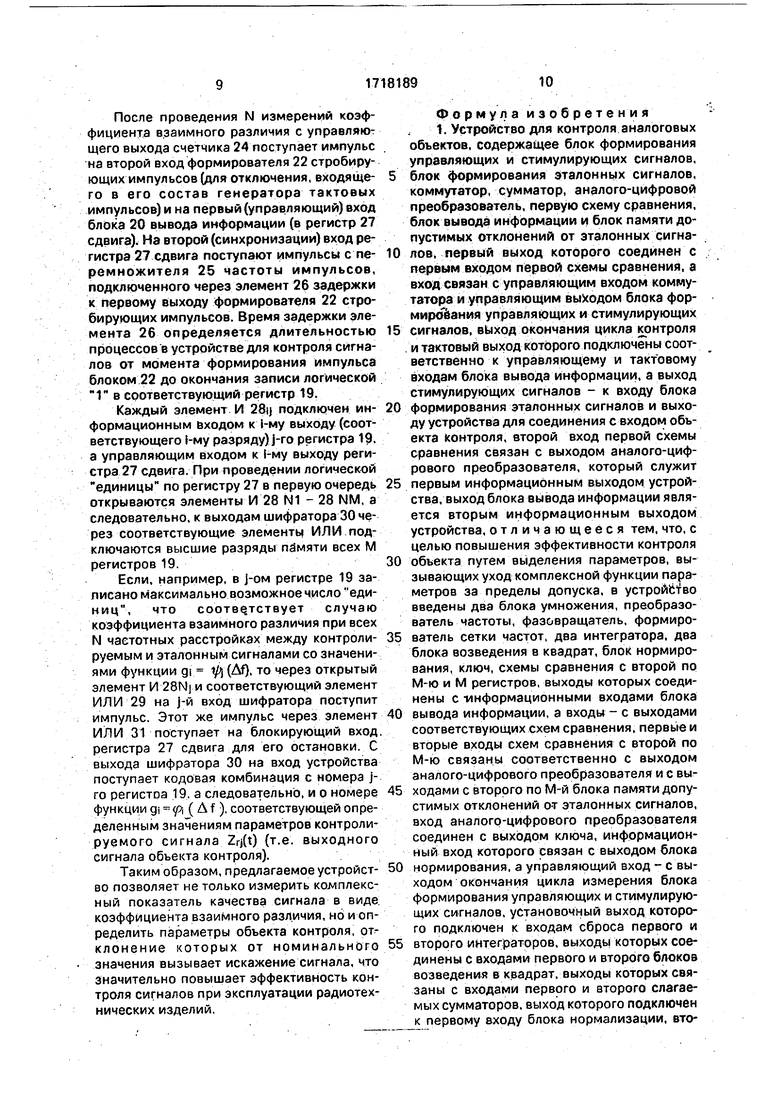

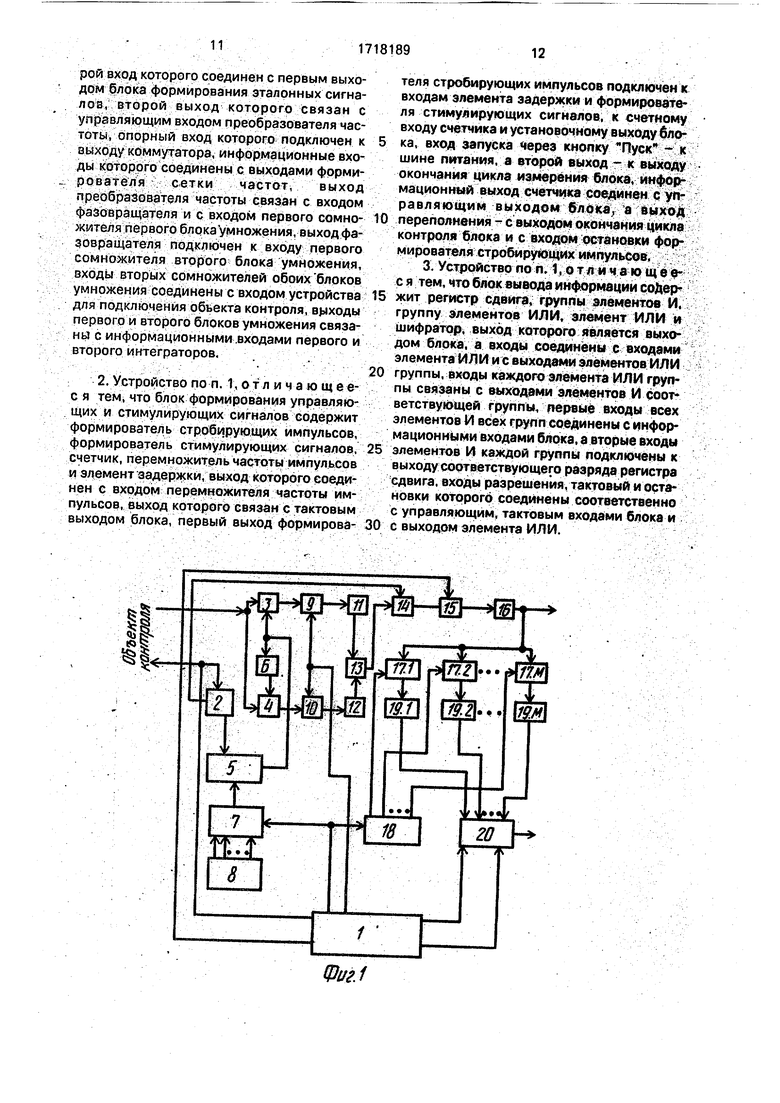

На фиг. 1 представлена структурная

0 электрическая схема устройства; на фиг. 2 - то же, блока формирования сигналов; на фиг. 3 - то же, блока вывода информации.

Устройство для контроля аналоговых параметров содержит блок 1 формирования

5 управляющих и стимулирующих сигналов, блок 2 формирования эталонных сигналов, блоки 3 и 4 умножения, преобразователь 5 частоты, фазовращатель 6, коммутатор 7. формирователь 8 сетки частот, интеграторы

0 9 и 10, блоки 11 и 12 возведения в квадрат, сумматор 13, блок 14 нормирования, ключ 15, аналого-цифровой преобразователь 16, схему 17 сравнения, блок 18 памяти допу стимых отклонений от эталонных сигналов,

5 М регистров 19, блок 20 вывода информации. Блок 1 формирования управляющих и . стимулирующих сигналов содержит кнопку

, формирователь 22 стробирующих импульсов, формирователь 23 стимулирую0 щих сигналов, счетчик 24, перемножитель 25 частоты импульсов и элемент 26 задержки. Блок 20 вывода информации состоит из регистра 27 сдвига, группы элементов 28 И, группы элементов 29 ИЛИ, шифратора 30 и 5 дополнительного элемента 31 ИЛИ.

Устройство работает следующим образом.

Перед началом работы формирователь

22стробирующих импульсов, формирователь 23 стимулирующих сигналов и блок 2

формирования эталонных сигналов находятся в исходном (выключенном) состоянии. Счетчик 24 и М регистров 19 обнулены. В ячейках блока 18 памяти допустимых отклонений от эталонных сигналов записана ин- формация о значениях коэффициента взаимного различия для N частотных сдвигов {Ati}, I 1,2, 3,... N между контролируемым и эталонным сигналом и М значений параметров контролируемого сигнала. Вы- ходы ячеек памяти допустимых отклонений от эталонных сигналов, соответствующие контролируемому сигналу Zrkj(tXl 1.,. 2,... М), с определенными значениями параметров объединены и подключены к второму входу соответствующего блока 17 сравнения.

При нажатии кнопки 21 Пуск напряжение подается на вход формирователя 22 стробирующйх импульсов, запускается генератор тактовых импульсов (не показан), По команде с формирователя 22 стробирующйх импульсов формирователь 23 стимулирующих сигналов вырабатывает управляющий низкочастотный сигнал (для дискретной двоичной системы передачи ин- формации это может быть телеграфная посылка О или 1), поступающий одновременно на входы блока 2 формирователя эталонных сигналов и объект контроля (не показан).

Контролируемый сигнал Zrk(t), прошедший через все такты исследуемого объекта контроля, поступает на входы блоков 3 и 4 умножения, С выхода блока 2 формирования эталонных сигналов эталонный сигнал Zra(t) (идеальный, т.е. без искажений, обусловленных отклонениями параметров реального объекта контроля от номинальных значений) через преобразователь 5 частоты поступает на другие входы блока Зумноже- ния непосредственно, а с блока 4 умножения --через фазовращатель 6, который осуществляет формирование сигнала Zra(t), сопряженного по Гильберту с эталонным- сигналом Zrsft),

На второй вход преобразователя 5 частоты через коммутатор 7 с выхода формирователя 8 сетки частот подается сигнал одной из гетеродинных частот fi (где I - 1, 2, 3... N; N - число гетеродинных частот на выходе формирователя 8). Выбор необходимой гетеродинной частоты осуществляется при подаче на первый управляющий вход коммутатора 7 соответствующей кодовой комбинации с информационного выхода счетчика 24, вход которого подключен к первому выходу формирователя 22 стробирующйх импульсов.

Сигналы, полученные в результате перемножения с выходов блоков 3 и 4, поступают на первые входы интеграторов 9 и 10, предварительно установленных в начальное состояние импульсом с первого выходы формирователя 22. После интегрирования в течение времени, равного длительности элемента сигнала tЈ О. Т, сигналы с выхода интеграторов 9 и 10 поступают через блоки 11 и 12 возведения в квадрат на соответствующие входы сумматора 13. С выхода сумматора 13 сигнал поступает на первый вход нормирующего блока 14. второй вход которого соединен с вторым выходом блока 2 формирователя эталонных сигналов. С нормирующего блока 14 сигнал поступает на информационный вход ключа 15, в котором при поступлении на его стробирующий вход импульсов с первого выхода формирователя 22 осуществляется отсчет результата измерения коэффициента взаимного различия контролируемого и эталонного сигналов, описываемого выражением (1). Стробирующий импульс с второго выхода формирователя 22 поступает также на третьи входы блоков 3 и 4 умножения для сброса накопленной в них энергии.

Напряжение с выхода ключа 15, подаваемое на информационный вход аналого- цифрового преобразователя 16, в зависимости от измеренного значения ей преобразуется в соответствующий двоичный код, поступающий на первые входы блоков 17.1-17.М сравнения. К вторым входам блоков 17.1-17.М сравнения подключены соответствующие выходы блока 18 памяти допустимых отклонений от эталонных сигналов. При поступлении с информационного выхода счетчика 24 на вход блока 18 памяти допустимых отклонений от эталонных сигналов кодовой комбинации, соответствующей номеру i - гетеродинной частоты на входе преобразователя 5, к выходам блока 18 памяти допустимых отклонений от эталонных сигналов подключаются ячейки памяти, в которых записана информация об уровнях коэффициента взаимного различия, соответствующих различным зна чениям параметров контролируемого сигнала и определенной частотной расстройке Afi между эталонным и контролируемым сигналами.

Если результат измерения коэффициента gi с выхода преобразователя равен уровню коэффициента взаимного различия, записанного в одной или нескольких ячейках блока 19 памяти допустимых отклонений эталонных сигналов, то на выходе соответствующих блоков 17 сравнения появляется сигнал логической 1, который поступит в соответствующие регистры 19.

После проведения N измерений коэффициента взаимного различия с управляют щего выхода счетчика 24 поступает импульс на второй вход формирователя 22 стробиру- ющих импульсов (для отключения, входящего в его состав генератора тактовых импульсов) и на первый (управляющий) вход блока 20 вывода информации (в регистр 27 сдвига). На второй (синхронизации) вход регистра 27 сдвига поступают импульсы с перемножителя 25 частоты импульсов, подключенного через элемент 26 задержки к первому выходу формирователя 22 стро- бирующих импульсов. Время задержки элемента 26 определяется длительностью процессов в устройстве для контроля сигналов от момента формирования импульса блоком 22 до окончания записи логической 1 в соответствующий регистр 19.

Каждый элемент И 28ij подключен информационным входом к 1-му выходу (соответствующего i-му разряду) j-ro регистра 19, а управляющим входом к i-му выходу регистра 27 сдвига. При проведении логической единицы по регистру 27 в первую очередь открываются элементы И 28 N1 - 28 NM, а следовательно, к выходам шифратора 30 через соответствующие элементы ИЛИ подключаются высшие разряды памяти всех М регистров 19.

Если, например, в j-ом регистре 19 записано максимально возможное число единиц, что соответствует случаю коэффициента взаимного различия при всех N частотных расстройках между контролируемым и эталонным сигналами со значениями функции gi. $ (Af), то через открытый элемент И 28N и соответствующий элемент ИЛИ 29 на j-й вход шифратора поступит импульс. Этот же импульс через элемент ИЛИ 31 поступает на блокирующий вход, регистра 27 сдвига для его остановки. С выхода шифратора 30 на вход устройства поступает кодовая комбинация с номера j- го регистоа 19, а следовательно, и о номере функции gi -де (A f ), соответствующей определенным значениям параметров контроли- руемого сигнала Zrj(t) (т.е. выходного сигнала объекта контроля).

Таким образом, предлагаемое устройство позволяет не только измерить комплексный показатель качества сигнала в виде: коэффициента взаимного различия, но и определить параметры объекта контроля, отклонение которых от номинального значения вызывает искажение сигнала, что значительно повышает эффективность контроля сигналов при эксплуатации радиотехнических изделий.

Ф ор мул а и з обр е т е ни я 1. Устройство для контроля аналоговых объектов, содержащее блок формирования управляющих и стимулирующих сигналов, 5 блок формирования эталонных сигналов, коммутатор, сумматор, аналого-цифровой преобразователь, первую схему сравнения, блок вывода информации и блок памяти допустимых отклонений от эталонных сигна0 лов, первый выход которого соединен с первым входом первой схемы сравнения, а вход связан с управляющим входом коммутатора и управляющим выходом блока формирования управляющих и стимулирующих

5 сигналов, выход окончания цикла контроля .и тактовый выход которого подключены соответственно к управляющему и тактовому входам блока вывода информации, а выход стимулирующих сигналов - к входу блока

0 формирования эталонных сигналов и выходу устройства для соединения с входом объекта контроля, второй вход первой схемы сравнения связан с выходом аналого-цифрового преобразователя, который служит

5 первым информационным выходом устройства, выход блока вывода информации является вторым информационным выходом устройства, отличающееся тем, что, с целью повышения эффективности контроля

0 объекта путем выделения параметров, вызывающих уход комплексной функции параметров за пределы допуска, в устроило введены два блока умножения, преобразователь частоты, фазовращатель, формиро5 ватель сетки частот, два интегратора, два блока возведения в квадрат, блок нормирования, ключ, схемы сравнения с второй по М-ю и М регистров, выходы которых соединены с -информационными входами блока

0 вывода информации, а входы - с выходами соответствующих схем сравнения, первые и вторые входы схем сравнения с второй по М-ю связаны соответственно с выходом аналого-цифрового преобразователя и с вы5 ходами с второго по М-й блока памяти допустимых отклонений от эталонных сигналов, вход аналого-цифрового преобразователя соединен с выходом ключа, информационный вход которого связан с выходом блока

0 нормирования, а управляющий вход - с выходом окончания цикла измерения блока формирования управляющих и стимулирующих сигналов, установочный выход которого подключен к входам сброса первого и

5 второго интеграторов, выходы которых соединены с входами первого и второго блоков возведения в квадрат, выходы которых связаны с входами первого и второго слагаемых сумматоров, выход которого подключен к первому входу блока нормализации, второй вход которого соединен с первым выходом блока формирования эталонных сигналов, второй выход которого связан с управляющим входом преобразователя частоты, опорный вход которого подключен к выходу коммутатора, информационные входы которого соединены с выходами формирователя сетки частот, выход преобразователя частоты связан с входом фазовращателя и с входом первого сомножителя первого блока умножения, выход фазовращателя подключен к входу первого сомножителя второго блока умножения, входы вторых сомножителей обоих блоков умножения соединены с входом устройства для подключения объекта контроля, выходы первого и второго блоков умножения связаны с информационными .входами первого и второго интеграторов.

2. Устройство по п. 1,отличающее- с я тем, что блок формирования управляющих и стимулирующих сигналов содержит формирователь стробирующих импульсов, формирователь стимулирующих сигналов, счетчик, перемножитель частоты импульсов и элемент задержки, выход которого соединен с входом перемножителя частоты импульсов, выход которого связан с тактовым выходом блока, первый выход формирова-

теля стробирующих импульсов подключен к входам элемента задержки и формирователя стимулирующих сигналов, к счетному входу счетчика и установочному выходу бло0

5

0

5 0

ка, вход запуска через кнопку Пуск - к шине питания, а второй выход - к выходу окончания цикла измерения блока, информационный выход счетчика соединен с уп- равляющим выходом блока, а выход переполнения - с выходом окончания цикла контроля блока и с входом остановки формирователя стробирующих импульсов,

3. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что блок вывода информации содержит регистр сдвига, группы элементов И, группу элементов ИЛИ, элемент ИЛИ и шифратор, выход которого является выходом блока, а входы соединены с входами элемента ИЛИ и с выходами элементов ИЛИ группы, входы каждого элемента ИЛИ группы связаны с выходами элементов И соответствующей группы, первые входы всех элементов И всех групп соединены с информационными входами блока, а вторые входы элементов И каждой группы подключены к выходу соответствующего разряда регистра сдвига, входы разрешения, тактовый и остановки которого соединены соответственно с управляющим, тактовым входами блока и с выходом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГОВЫХ ОБЪЕКТОВ | 2004 |

|

RU2262128C1 |

| Устройство для контроля параметров | 1988 |

|

SU1665390A1 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1989 |

|

SU1608591A1 |

| УСТРОЙСТВО КОМПЛЕКСНОЙ ОЦЕНКИ ТЕХНИЧЕСКОГО СОСТОЯНИЯ МНОГОКАНАЛЬНЫХ ТЕЛЕКОММУНИКАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2368935C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОЭЛЕКТРОННЫХ ОБЪЕКТОВ | 2003 |

|

RU2239218C1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для измерения защищенности сигналов от помех | 1989 |

|

SU1658399A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СРЕДСТВ СВЯЗИ | 2006 |

|

RU2325684C2 |

| Устройство для измерения защищенности сигнала от помех | 1988 |

|

SU1570006A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СИГНАЛОВ | 2007 |

|

RU2354055C1 |

Изобретение относится к измерению аналоговых параметров и может быть использовано в системах автоматического контроля параметров. Цель изобретения - повышение эффективности контроля объекта за счет выделения его параметров, откло- нение От номинальных значений которых вызывает уход значения комплексной фуж- ции параметров за пределы допуска. Устройство для .контроля аналоговых параметров содержит блок формирования управляющих и стимулирующих сигналов, блок формирования эталонных сигналов, блок памяти допустимых отклонений от эталонных сигналов, аналого-цифровой преобразователь, схему сравнения, сумматор и блок вывода информации. Для решения поставленной задачи в устройство введены тракт измерения коэффициента взаимного различия, состоящий из фазовращателя, двух блоков умножения, двух интеграторов, двух блоков возведения в квадрат, подключенных к входам сумматора, блока нормирования и ключа, формирователь сетки частот, коммутатор и преобразователь частоты - для идентификации контролируемых параметров. 2 з.п. ф-лы, 3 ил. : v ЫГ fe

0Й/

вшдяМ

; . : -

% 1

§

Дг

J гггт

Ш20

21

гг

2SS

50

г&

U

Я.

| Механизация и автоматизация управления, 1987, № 3, с | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Устройство для контроля аналоговых параметров | 1976 |

|

SU561171A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-03-07—Публикация

1989-12-05—Подача