10

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля работоспособности фазированной антенной решетки | 1986 |

|

SU1363093A1 |

| Устройство для контроля работоспособности фазированной антенной решетки | 1980 |

|

SU926607A1 |

| Устройство для контроля работоспособности фазированных антенных решеток | 1978 |

|

SU785801A1 |

| Способ контроля работоспособности фазированной антенной решетки | 1985 |

|

SU1345143A1 |

| Устройство для встроенного контроля дискретно-коммутационной антенной решетки с @ -диодными фазовращателями и со строчно-столбцевым фазированием | 1991 |

|

SU1781641A1 |

| Способ встроенного контроля фазированной антенной решетки | 1989 |

|

SU1810841A1 |

| Фазированная антенная решетка для импульсной радиолокационной станции | 1985 |

|

SU1841201A1 |

| Устройство управления полупроводниковыми фазовращателями | 1977 |

|

SU750586A1 |

| Устройство распределения и фазирования сверхвысокочастотного сигнала | 2018 |

|

RU2699041C1 |

| СПОСОБ КОНТРОЛЯ ДИАГРАММНЫХ ПАРАМЕТРОВ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ РАДИОПЕЛЕНГАТОРА | 1996 |

|

RU2117308C1 |

Изобретение относится к средствам контроля и может быть использовано для контроля работоспособности фазированной антенной решетки (ФАР). Цель изобретения - повышение достоверности контроля. Устройство содержит трансформатор 4 тока, временной селектор 5, преобразователь 6 время - код, блок 7 питания pin-диодов 3, на которых выполнен фазовращатель 2 контролируемой ФАР 1, вычислитель 8 фаз, анализатор 9 работоспособности, индикатор 10, синхронизатор 11 и блок 12 рассасывающего напряжения. Об исправности или неисправности pin-диода З судят по допусковому контролю длительности импульса тока в цепи рассасывающего напряжения. Это позволяет определять неисправность pin-диода З не только типа обрыв, но и типа короткое замыкание, что повышает достоверность контроля. 2 ил.

о

СП

о

ю

Ј

;

Изобретение относится к средствам контроля и может быть использовано для контроля работоспособности фазированной антенной решетки (ФАР).

Цель изобретения - повышение досто- верности контроля.

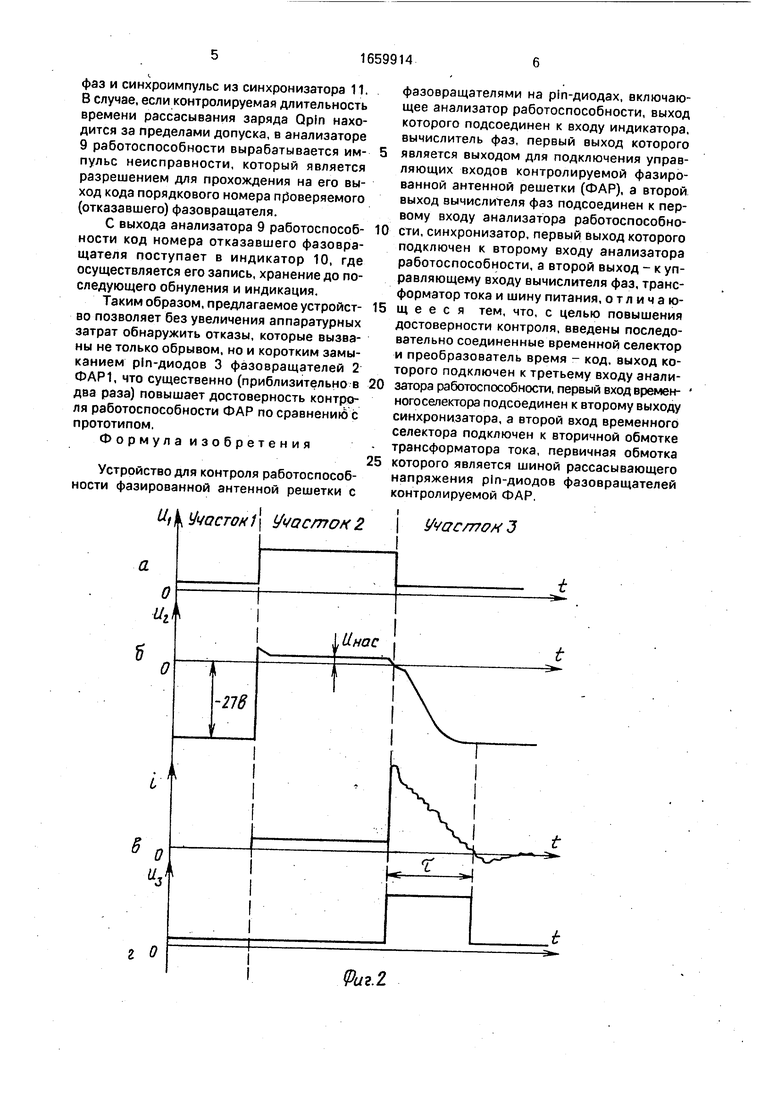

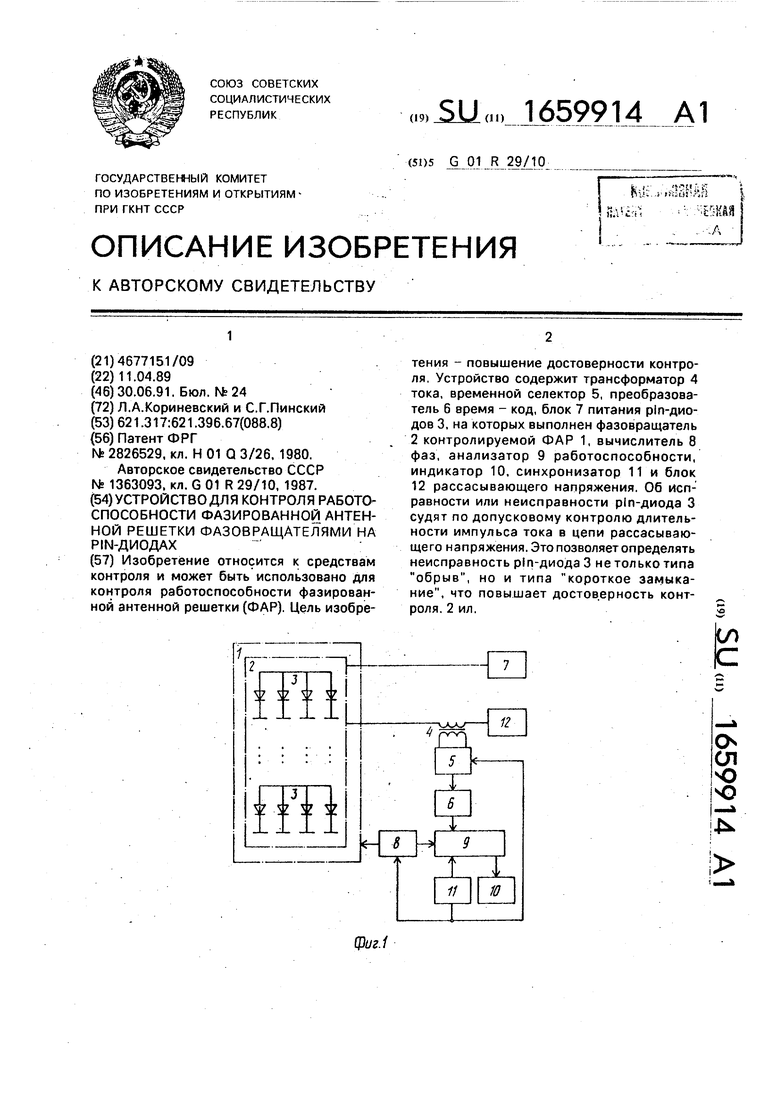

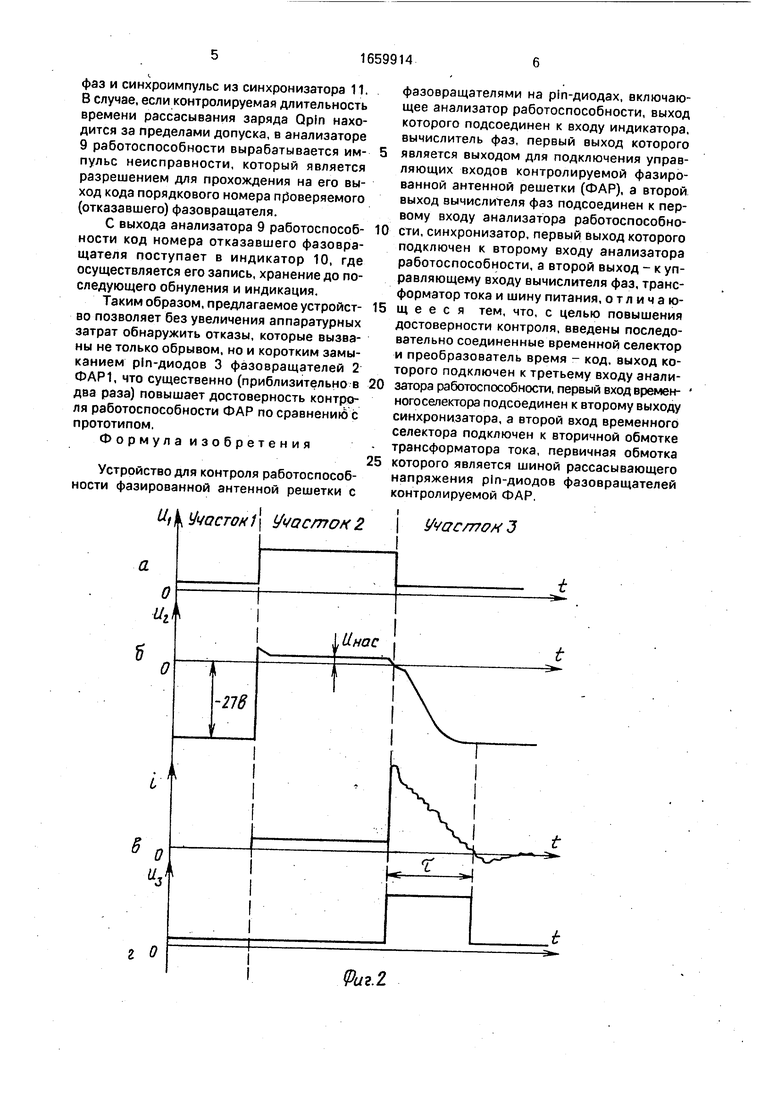

На фиг.1 приведена структурная электрическая схема устройства для контроля работоспособности ФАР с фазовращателями на pin-диодах; на фиг.2-временные диаграм- мы напряжений и токов в цепях устройства.

Устройство для контроля работоспособности фазированной антенной решетки 1 с фазовращателями 2 на pin-диодах З содержит трансформатор 4 тока, временной се- лектор 5, преобразователь 6 время - код, блок 7 питания pin-диодов, вычислитель 8 фаз, анализатор 9 работоспособности, индикатор 10, синхронизатор 11 и блок 12 рассасывающего напряжения. Выход блока питания 7 по шине питания подключен к фазовращателям 2 ФАР1, а выход блока 12 рассасывающего напряжения - к фазовращателям 2 через первичную обмотку трансформатора 4 тока. Первый выход вы- числителя 8 фаз является выходом для подключения управляющих входов контролируемой ФАР1, а второй выход соединен с первым входом анализатора 9 работоспособности. Первый выход синхронизатора 11 соединен с вторым входом анализатора 9 работоспособности, а второй выход синхронизатора 11 подключен к управляющему входу вычислителя 8 фаз и первому входу временного селектора 5, вто- рой вход которого подключен к вторичной обмотке трансформатора 4 тока. Выход временного селектора 5 соединен с входом преобразователя 6 время - код, выход которого подключен к третьему входу анализатора 9 работоспособности. Выход анализатора 9 работоспособности подключен к входу индикатора 10.

Устройство для контроля работоспособности ФАР работает следующим образом.

В режиме Контроль вычислитель 8 фаз по специальной программе вырабатывает управляющие сигналы, поступающие на управляющие входы ФАР 1 и обеспечивающие поочередное включение и выключение проверяемых pin-диодов З фазовращателей 2 ФАР1 с частотой управляющих импульсов синхронизатора 11 (временная диаграмма Ui(t) на фиг.2,а).

При включении проверяемого разряда на pin-диод З поступает напряжение поло- жительного смещения и по шине питания от блока 7 питания протекает ток I 0 + lynp, где 0- ток покоя ФАР; упр - ток управления проверяемого разряда (pin-диода З).

Прохождение тока упр через pin-диод вводит его в режим насыщения, создавая на нем падение напряжения Унас (временная диаграмма U2(t) на фиг.2,б, участок 2). При этом на pin-диоде накапливается довольно значительный электрический заряд Qpin, составляющий величину порядка десятков-сотен нанокулон,

Время переключения pin-диода из открытого состояния в закрытое определяется временем рассасывания накопленного заряда Qpin. При выключении проверяемого pin-диода фазовращателя напряжение отрицательной полярности от блока 12 рассасывающего напряжения через первичную обмотку трансформатора 4 тока подается на соответствующий pin-диод (временная диаграмма U2(t) на фиг.2,б, участки 1 и 3), обеспечивая ускоренное рассасывание заряда Qpin. При этом по шине рассасывающего напряжения (первичной обмотке трансформатора 4 тока) от положительного электрода pin-диода к блоку рассасывающего напряжения начинает протекать ток разряда, вызывающий во вторичной цепи трансформатора 4 тока экспоненциальный импульс тока длительностью (временная диаграмма i(t) на фиг.2,в), определяемой временем рассасывания электрического заряда Qpin. Этот импульс во временном селекторе 6 выделяется и преобразуется в прямоугольный импульс напряжения логического уровня (временная диаграмма Ua(t) на фиг.2,г), длительность которого, пропорциональная величине накопленного электрического заряда Qpin, позволяет характеризовать работоспособность проверяемого разряда (pin-диода З) фазовращателя 2 ФАР1.

Если проверяемый разряд фазовращателя 2 состоит из нескольких параллельно включенных pin-диодов, то величина уменьшения длительности на выходе временного селектора будет определять количество диодов, у которых произошел отказ в виде обрыва. В случае отказа, заключающегося в обрыве всех диодов проверяемого разряда, или короткого замыкания одного из диодов фазовращателя накапливаемый заряд Qpin 0 и импульс на выходе временного селектора 6 будет отсутствовать.

Длительность выходного импульса временного селектора 5 с помощью преобразователя 6 время - код преобразуется в параллельный цифровой код, который подается на анализатор 9 работоспособности,} где осуществляется его допусковый контроль. При этом на анализатор 9 работоспособности поступает код порядкового номера контролируемого фазовращателя из вычислителя 8

фаз и синхроимпульс из синхронизатора 11.

8случае, если контролируемая длительность времени рассасывания заряда Qpln находится за пределами допуска, в анализаторе

9работоспособности вырабатывается импульс неисправности, который является разрешением для прохождения на его выход кода порядкового номера проверяемого (отказавшего) фазовращателя.

С выхода анализатора 9 работоспособности код номера отказавшего фазовращателя поступает в индикатор 10, где осуществляется его запись, хранение до последующего обнуления и индикация.

Таким образом, предлагаемое устройство позволяет без увеличения аппаратурных затрат обнаружить отказы, которые вызваны не только обрывом, но и коротким замыканием pin-диодов З фазовращателей 2 ФАР1, что существенно (приблизительно в два раза) повышает достоверность контроля работоспособности ФАР по сравнению с прототипом.

Формула изобретения

Устройство для контроля работоспособности фазированной антенной решетки с

ЩЬ Участок 1 Участок 2 УчастемЗ

фазовращателями на pin-диодах, включающее анализатор работоспособности, выход которого подсоединен к входу индикатора, вычислитель фаз, первый выход которого

является выходом для подключения управляющих входов контролируемой фазированной антенной решетки (ФАР), а второй выход вычислителя фаз подсоединен к первому входу анализатора работоспособности, синхронизатор, первый выход которого подключен к второму входу анализатора работоспособности, а второй выход - к управляющему входу вычислителя фаз, трансформатор тока и шину питания, отличающ е е с я тем, что, с целью повышения достоверности контроля, введены последовательно соединенные временной селектор и преобразователь время - код. выход которого подключен к третьему входу анали- затора работоспособности, первый вход времен- ногоселектора подсоединен к второму выходу синхронизатора, а второй вход временного селектора подключен к вторичной обмотке

трансформатора тока, первичная обмотка которого является шиной рассасывающего напряжения pin-диодов фазовращателей контролируемой ФАР.

Риг.2

| Способ изготовления кольцевых изделий | 2024 |

|

RU2826529C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля работоспособности фазированной антенной решетки | 1986 |

|

SU1363093A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-06-30—Публикация

1989-04-11—Подача